Урок 8.3 – Логические элементы

8.3. Логические элементы

Все, абсолютно все электронные компоненты, обрабатывающие цифровые сигналы, состоят из небольшого набора одинаковых «кирпичиков». В микросхемах малой степени интеграции могут быть единицы и десятки таких элементов, а в современных процессорах их может быть очень и очень много. Они называются логические элементы. Логическим элементом называется электрическая схема, предназначенная для выполнения какой-либо логической операции с входными данными. Логический элемент — элемент, осуществляющий определенные логические зависимость между входными и выходными сигналами. Входные данные представляются здесь в виде напряжений различных уровней, и результат логической операции на выходе — также получается в виде напряжения определенного уровня. Логические элементы обычно используются для построения логических схем вычислительных машин, дискретных схем автоматического контроля и управления.

Тем не менее, принцип работы цифровой логики остается неизменным – на входе логического элемента (входов может быть несколько) должен быть цифровой сигнал (сигналы, если входов несколько), который однозначно определяет сигнал на выходе логического элемента.

Конечно, логические элементы строятся, в свою очередь, из уже рассмотренных в предыдущих уроках резисторов, транзисторов и других электронных компонентов, но с точки зрения разработки цифровых схем именно логический элемент является их «элементарной» частицей.

При анализе работы логических элементов используется так называемая булева алгебра . Начала этого раздела математики было изложено в работах Джорджа Буля – английского математика и логика 19-го века, одного из основателей математической логики. Основами булевой алгебры являются высказывания, логические операции, а также функции и законы. Для понимания принципов работы логических элементов нет необходимости изучать все тонкости булевой алгебры, мы освоим ее основы в процессе обучения с помощью таблиц истинности.

Еще несколько замечаний. Логические элементы (как, впрочем, и другие элементы электронных схем) принято обозначать так, чтобы входы были слева, а выходы справа. Число входов может быть, вообще говоря, любым, отличным от нуля. Реальные цифровые микросхемы могут иметь до 8 входов, но мы ограничимся двумя – этого достаточно для понимания. Условные обозначения соответствуют отечественному ГОСТу, в других стандартах они могут быть иными.

Реальные цифровые микросхемы могут иметь до 8 входов, но мы ограничимся двумя – этого достаточно для понимания. Условные обозначения соответствуют отечественному ГОСТу, в других стандартах они могут быть иными.

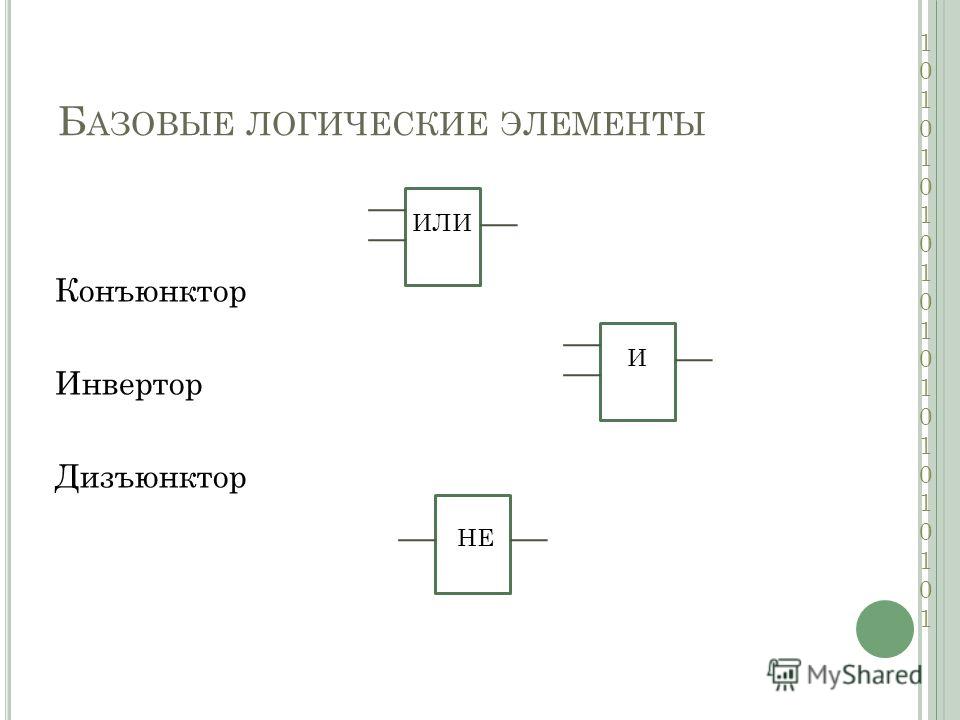

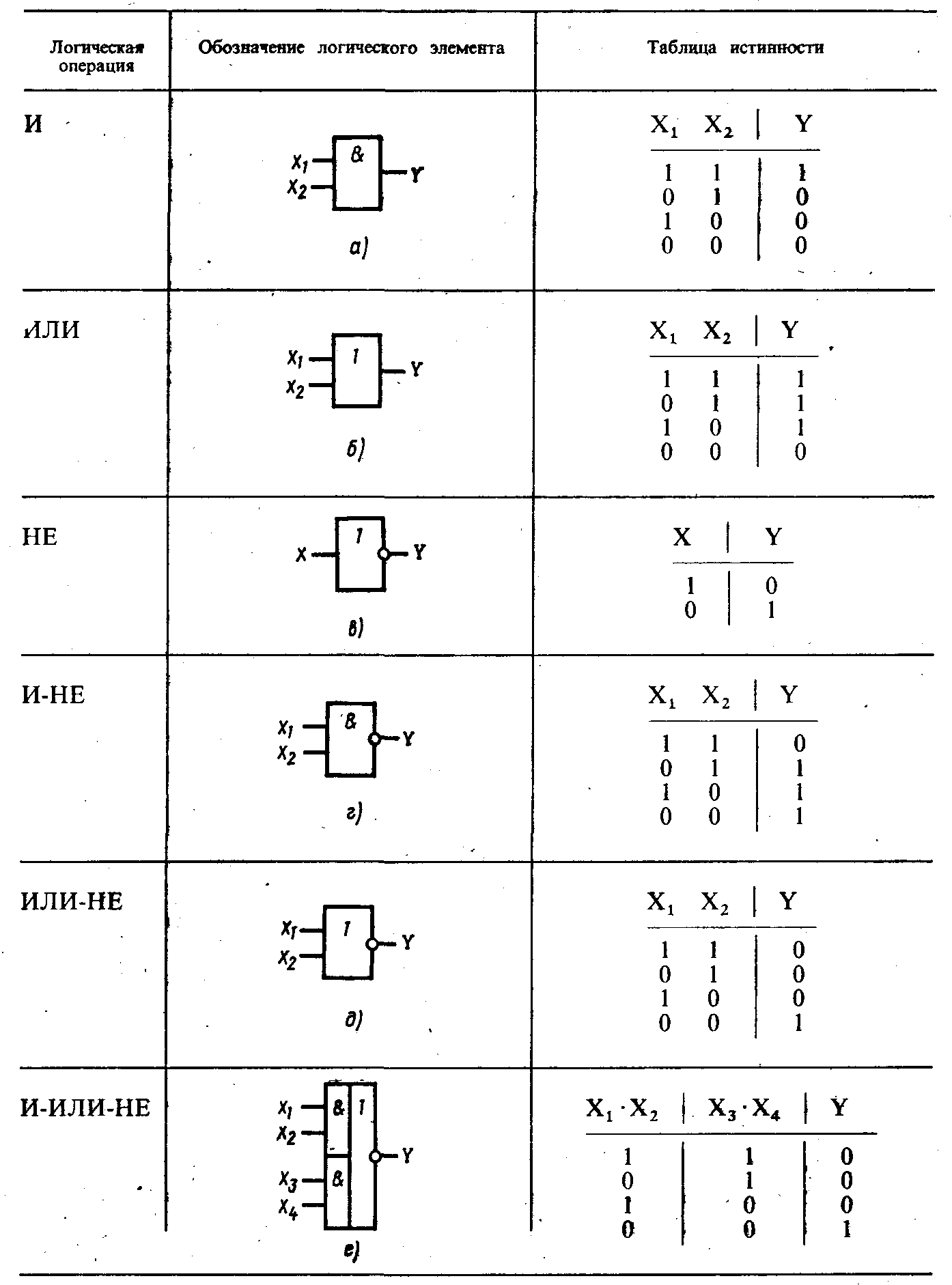

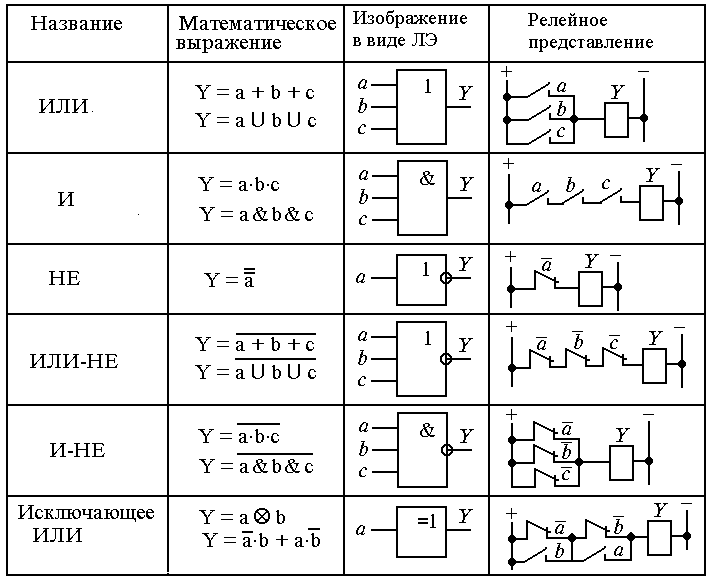

Какие же бывают логические элементы?

Логические элементы имеют один или несколько входов и один или два (обычно инверсных друг другу) выхода. Значения «нулей» и «единиц» выходных сигналов логических элементов определяются логической функцией, которую выполняет элемент, и значениями «нулей» и «единиц» входных сигналов, играющих роль независимых переменных. Существуют элементарные логические функции, из которых можно составить любую сложную логическую функцию.

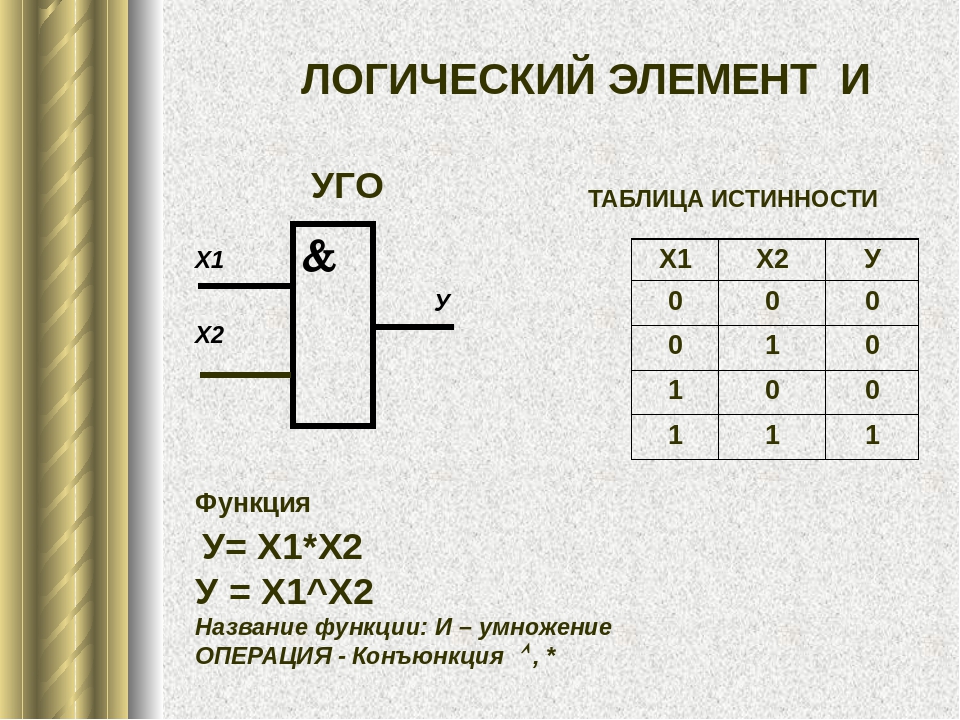

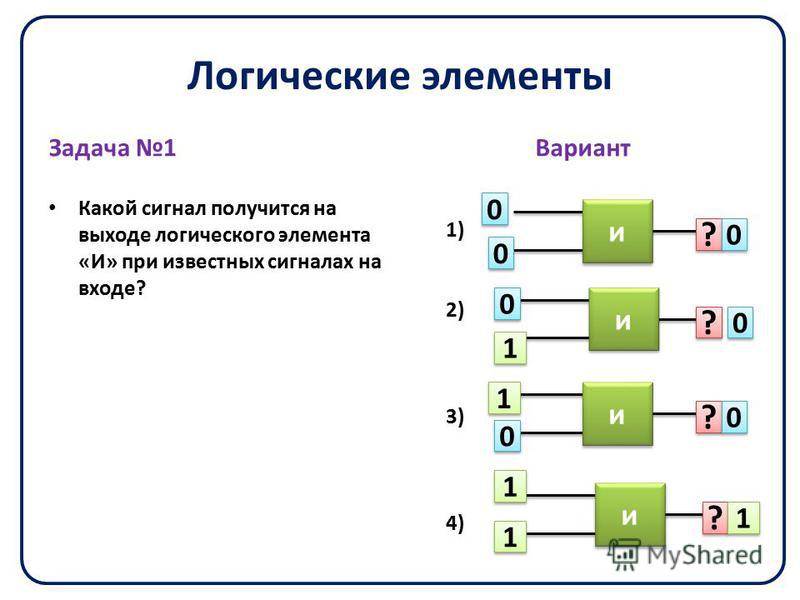

Элемент «И» (AND), он же конъюнктор, выполняет операцию логического умножения:

Условное обозначение – Таблица истинности

Здесь изображен логический элемент «2И» (цифра перед буквой «И» означает число входов). Знак & (амперсант) в левом верхнем углу прямоугольника указывает, что это логический элемент «И». Первые две буквы обозначения DD1.2 указывают на то, что это цифровая микросхема (Digital), цифра слева от точки указывает номер микросхемы на принципиальной схеме, а цифра справа от точки – номер логического элемента в составе данной микросхемы. Одна микросхема может содержать несколько логических элементов.

Первые две буквы обозначения DD1.2 указывают на то, что это цифровая микросхема (Digital), цифра слева от точки указывает номер микросхемы на принципиальной схеме, а цифра справа от точки – номер логического элемента в составе данной микросхемы. Одна микросхема может содержать несколько логических элементов.

Состояние входов в таблице обозначаются «0» и «1» («ложь» и «истина»). Из таблицы видно, что выход «Y» будет иметь состояние «1» только в том случае, когда на обоих входах «Х1» и «Х2» будут «1». Это легко запомнить: умножение на «0» всегда дает «0».

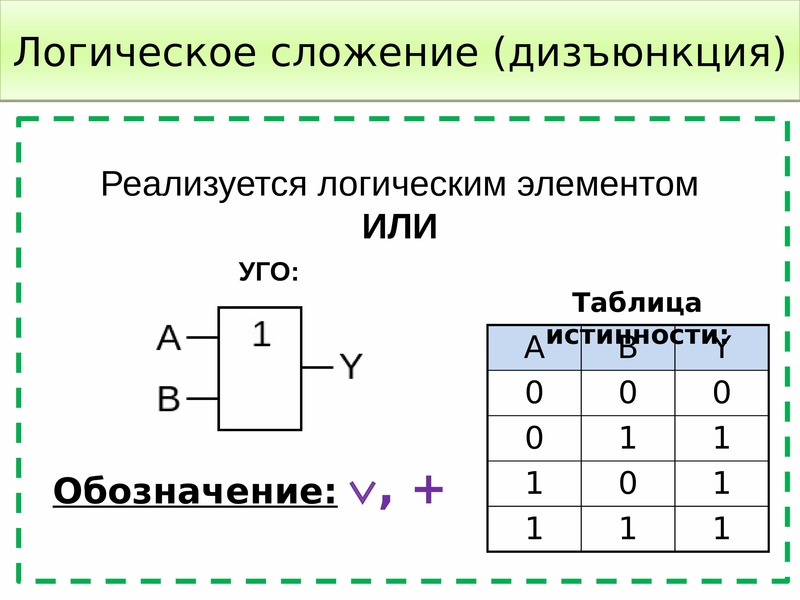

Элемент «ИЛИ» (OR), он же дизъюнктор, выполняет операцию логического сложения:

Условное обозначение – Таблица истинности

Состояние «1» на выходе будет всегда, пока есть хотя бы одна «1» на входах.

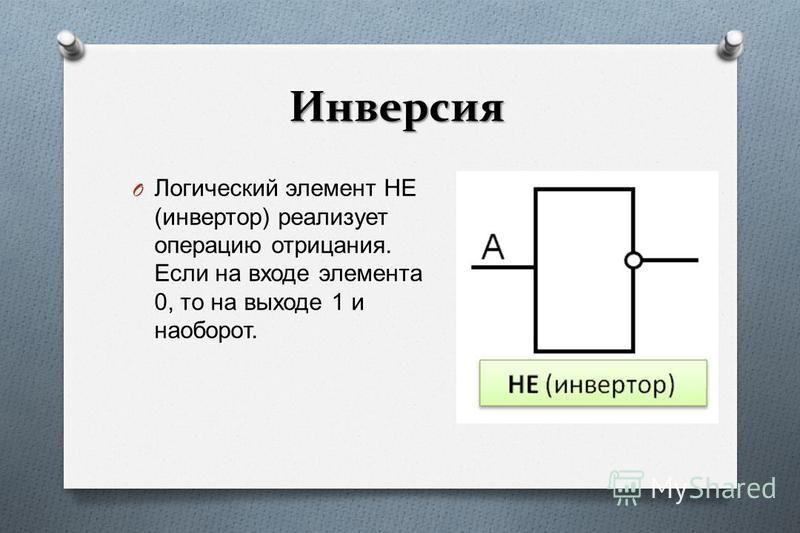

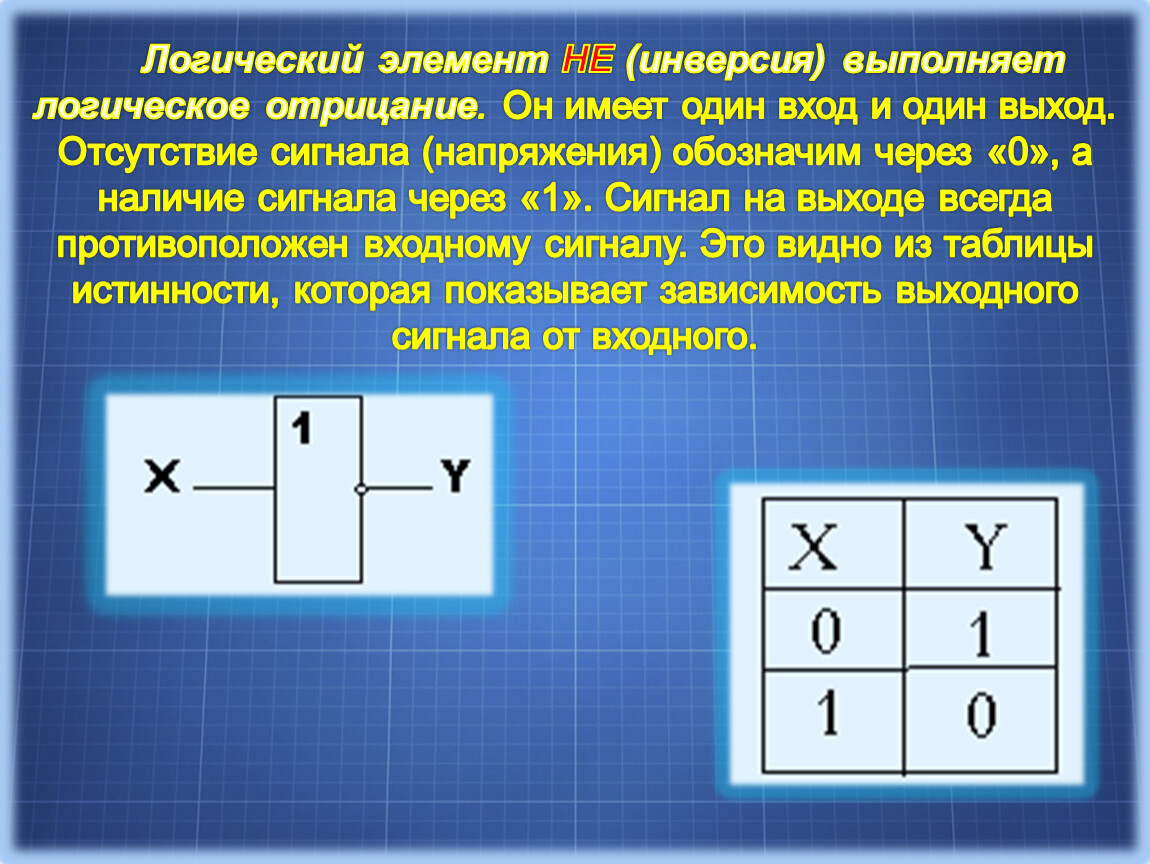

Элемент «НЕ» (NOT), он же инвертор, выполняет операцию логического отрицания:

Условное обозначение – Таблица истинности

Состояние на входе обратно состоянию на входе.

Вот из этих трех элементов строятся все цифровые устройства!

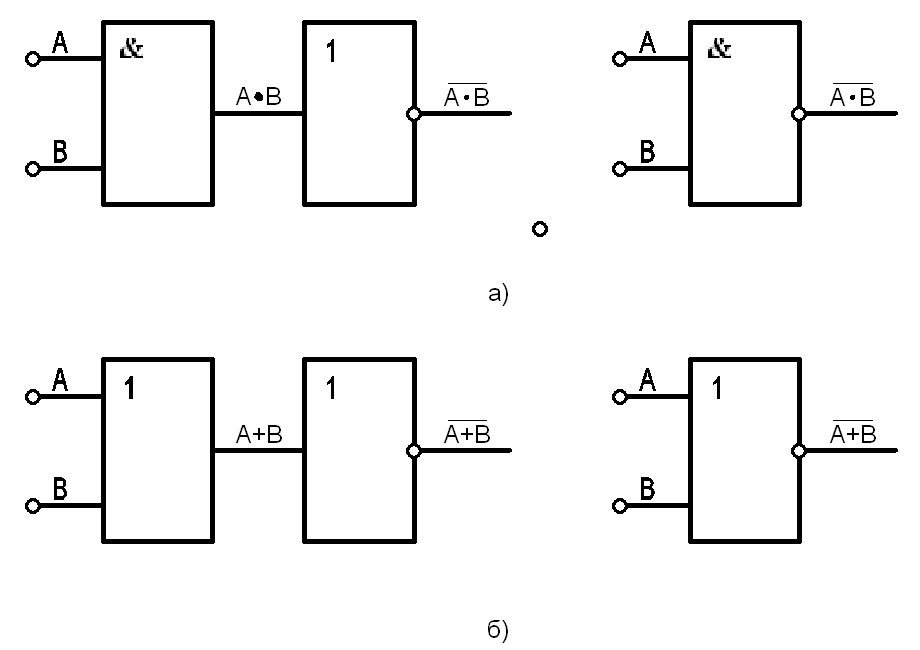

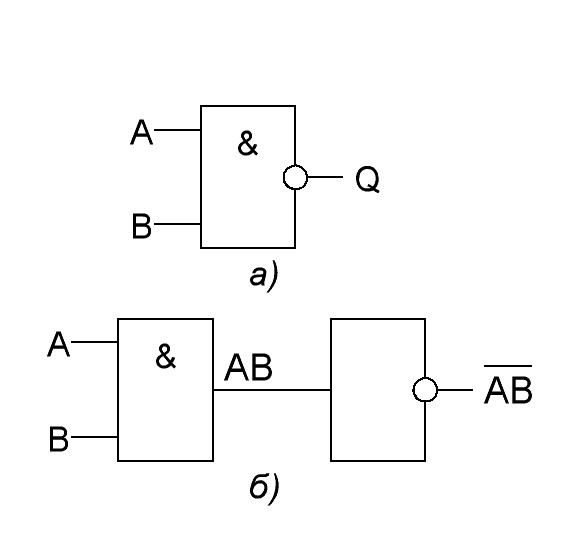

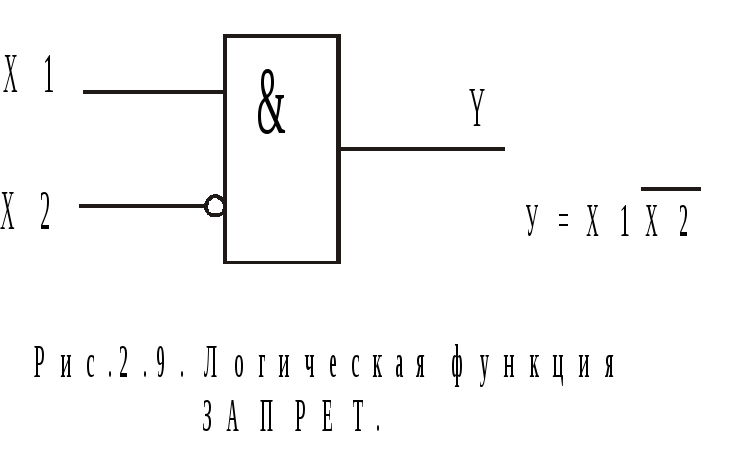

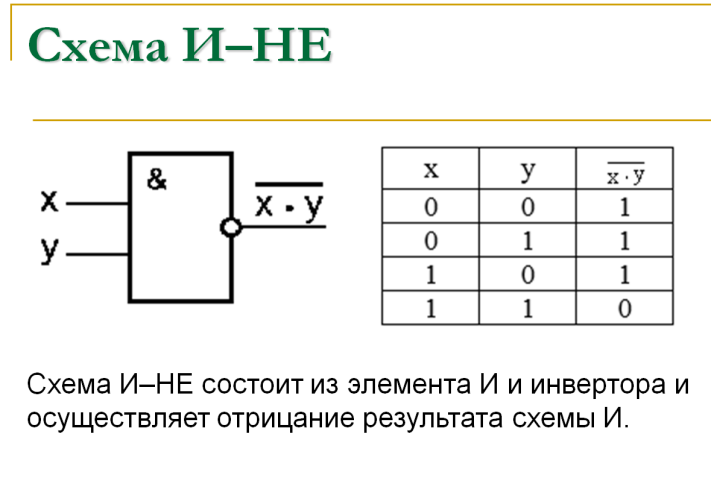

Рассмотрим еще три логических элемента, которые можно получить, комбинируя уже рассмотренные. В силу исторически сложившихся схемотехнических решений эти скомбинированные схемы тоже считаются логическими элементами.

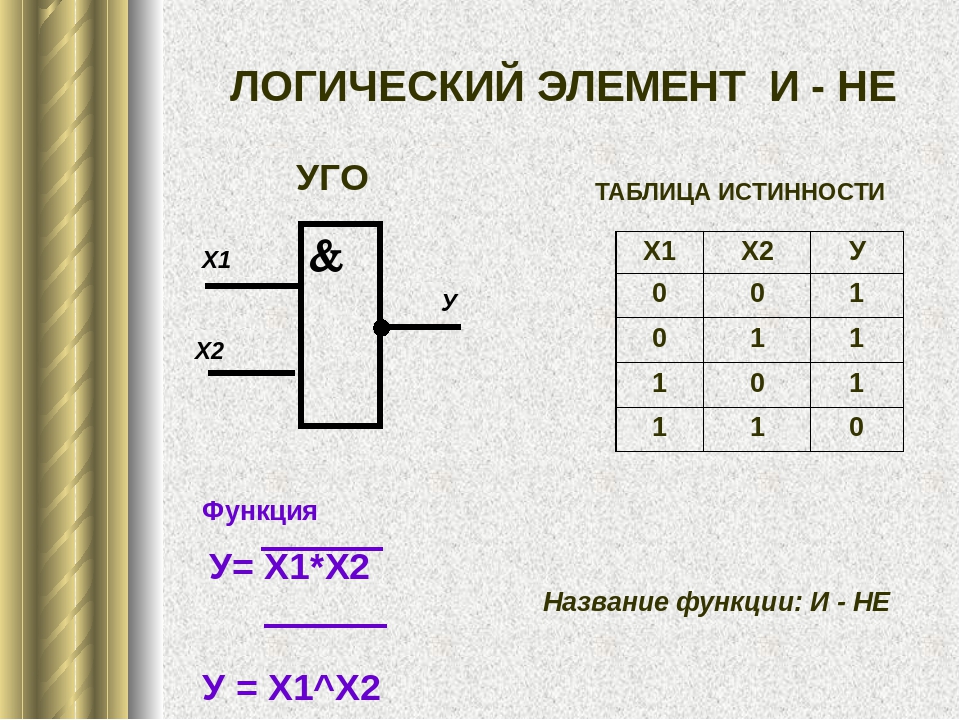

Элемент «И-НЕ» (NAND), конъюнктор с отрицанием:

Условное обозначение – Таблица истинности

Элемент И-НЕ работает точно так же как «И», только выходной сигнал противоположен. Там где у элемента «И» на выходе должен быть «0», у элемента «И-НЕ» будет единица. И наоборот.

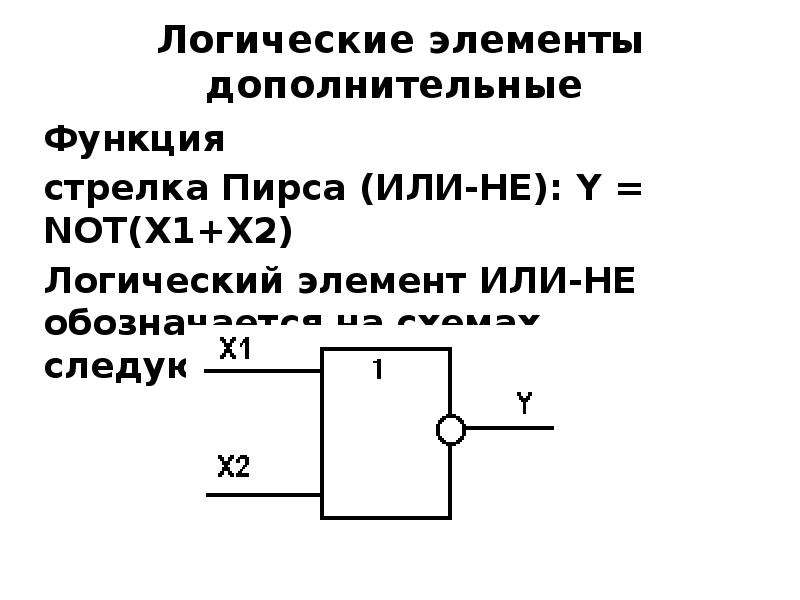

Элемент «ИЛИ-НЕ» (NOR), дизъюнктор с отрицанием:

Условное обозначение – Таблица истинности

Элемент работает так же как и «ИЛИ», но с инверсией выхода.

Элемент «Исключающее ИЛИ» (XOR), сумматор по модулю 2:

Условное обозначение – Таблица истинности

В этом элемента «1» на выходе будет только тогда, когда на входах разные состояния.

На таких элементах строят сумматоры двоичных многоразрядных чисел. Для этого используется еще один дополнительный выход, на котором при появлении на входах двух «1» появляется сигнал переноса разряда.

Мы рассмотрели логические элементы, которые применяются в цифровой технике для построения логических схем любого уровня сложности, но рассмотренные нами элементы не могут делать одну крайне важную работу – они не умеют хранить информацию. Для хранения используется более сложный класс устройств, называемый элементами с памятью или конечными автоматами. В этот класс входят триггеры, регистры, счетчики, шифраторы (дешифраторы), мультиплексоры (демультиплексоры) и сумматоры. Некоторый из этих устройств мы рассмотрим в следующем уроке.

Логические элементы

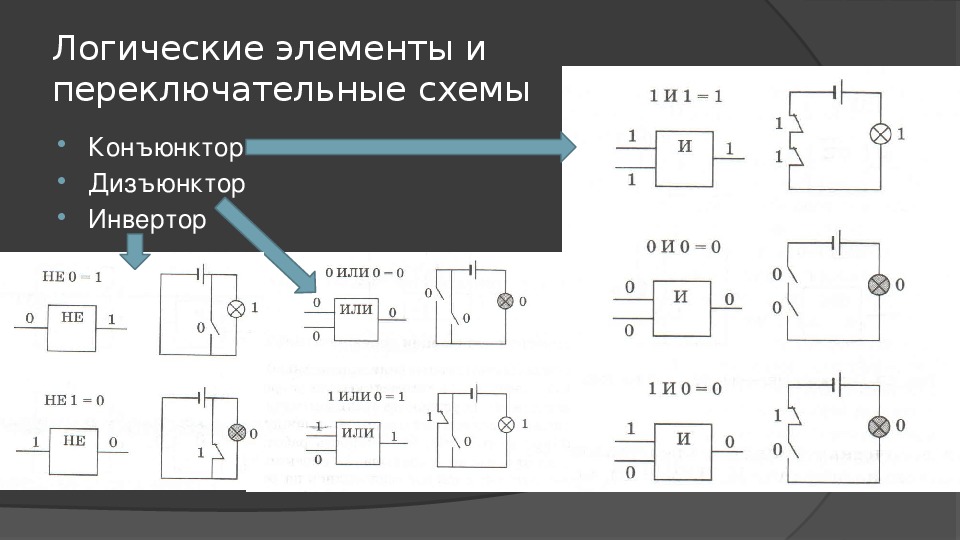

Мы с вами знаем следующие

логические операции: конъюнкция (логическое умножение), дизъюнкция (логическое

сложение) и инверсия (отрицание). Все эти операции используются в алгебре

логики.

Сегодня на уроке мы с вами узнаем, что такое логический элемент, познакомимся с такими логическими элементами, как конъюнктор, дизъюнктор и инвертор. А также научимся находить выходные данные исходя из предоставленной электронной схемы.

Алгебра логики является незаменимым элементом в конструировании автоматических устройств, разработке аппаратных и программных средств информационных и коммуникационных технологий.

Мы с вами уже знаем, что любую информацию можно представить в дискретной форме. Дискретная форма – это форма представления, при которой информация преподнесена в виде фиксированного набора отдельных значений. То есть, например, последовательностью нулей и единиц. В свою очередь,

В свою очередь, логический

элемент – это дискретный преобразователь, который выдаёт после обработки

двоичных сигналов значение одной из логических операций.

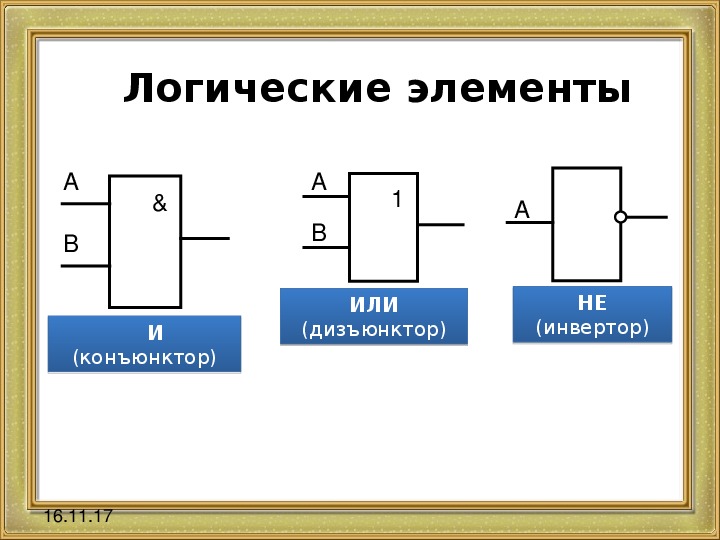

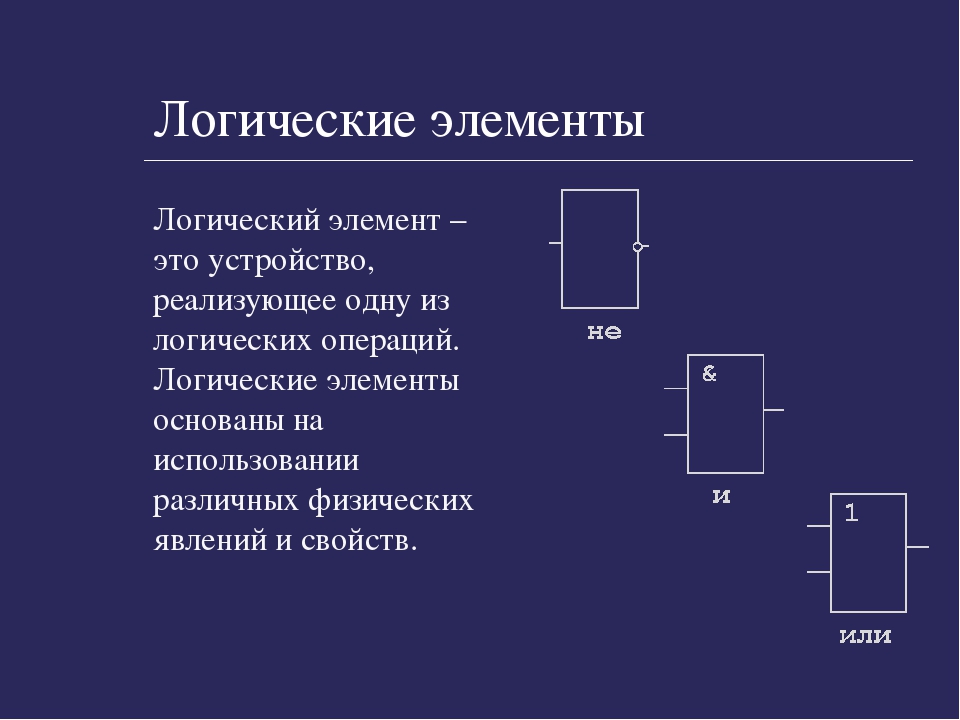

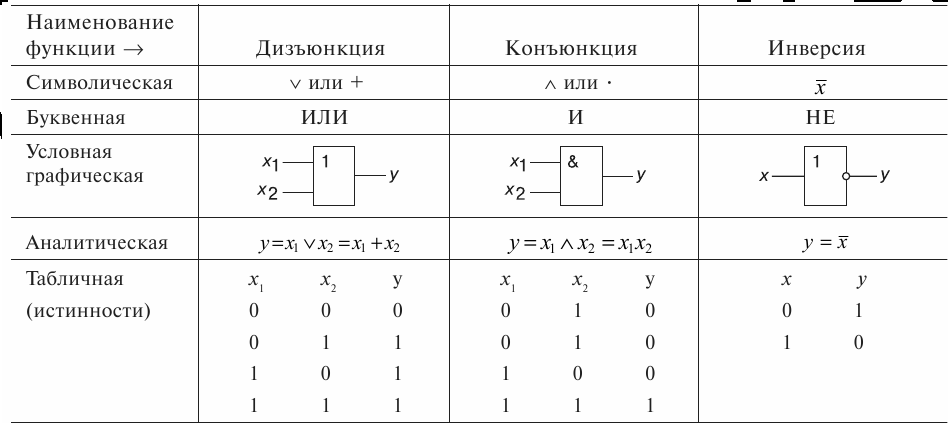

Перед вами представлены условные обозначения (схемы) логических элементов, с помощью которых реализуется логическое умножение, логическое сложение и отрицание. Давайте разберёмся с каждой схемой отдельно.

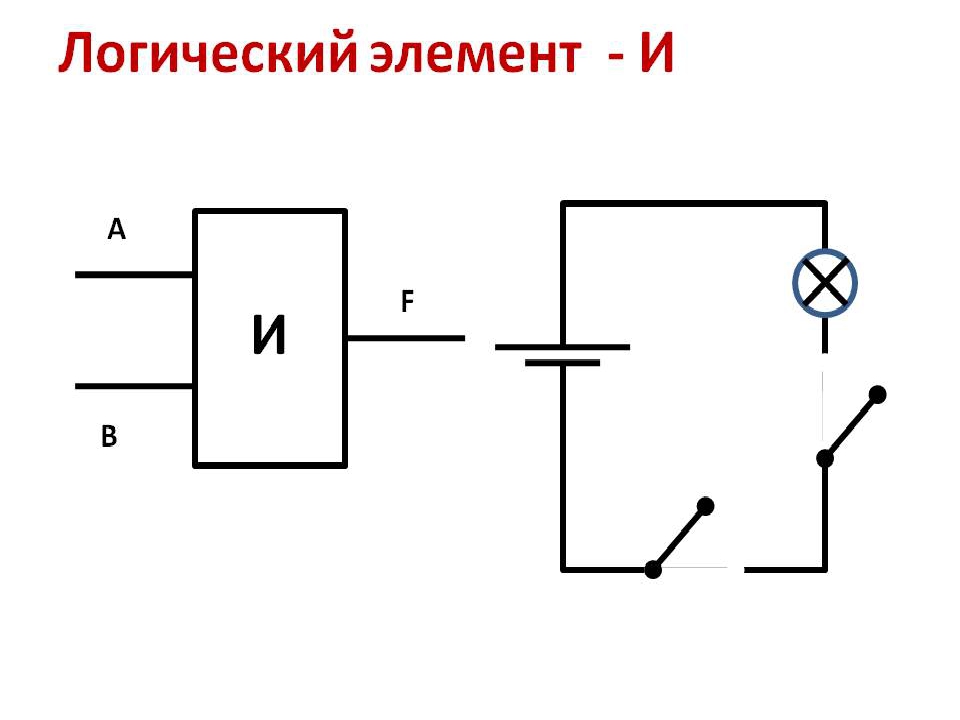

Итак, первый логический элемент И (конъюнктор). С его помощью реализуется операция логического умножения. Рассмотрим его.

А – это входные данные первого элемента, B – второго, F – выходные данные. Вспомним таблицу истинности для конъюнкции.

Всевозможные входные данные А и B нам даны в первых двух столбцах. В третьем нам дан результат при выполнении конъюнкции – выходные данные. То есть значение F. Таким образом, можно сказать, что единица на выходе получится тогда и только тогда, когда на всех входах будут единицы. Или же, другими словами, в результате мы можем получить для F единицу тогда и только тогда, когда А и B равны единице.

Следующий логический

элемент – ИЛИ (дизъюнктор).

Как вы уже, наверное, догадались, с его помощью реализуется операция логического сложения. И снова обратимся к таблице истинности для дизъюнкции.

В первых двух столбцах даны всевозможные входные данные для А и B. В третьем выходные данные, которые будут равны F. Исходя из этой таблицы можно сказать, что на выходе мы получим единицу тогда, когда хотя бы на одном входе будет единица. То есть, если А или B будет равно единице, то F также будет равно единице.

И последний логический элемент – НЕ (инвертор).

С его помощью реализуется операция отрицания.

Здесь всё просто. Снова нам понадобится таблица истинности для инверсии. Если на входе у нас элемент ноль, то на выходе будет единица, и наоборот. То есть, если А = 0, то F будет равно 1. И, если А = 1, то F = 0.

Также необходимо знать,

что все компьютерные устройства, которые производят операции над двоичными

числами, и ячейки, в которых хранятся данные, представляют собой электронные

схемы. Они же в свою очередь состоят из отдельных логических операций.

Они же в свою очередь состоят из отдельных логических операций.

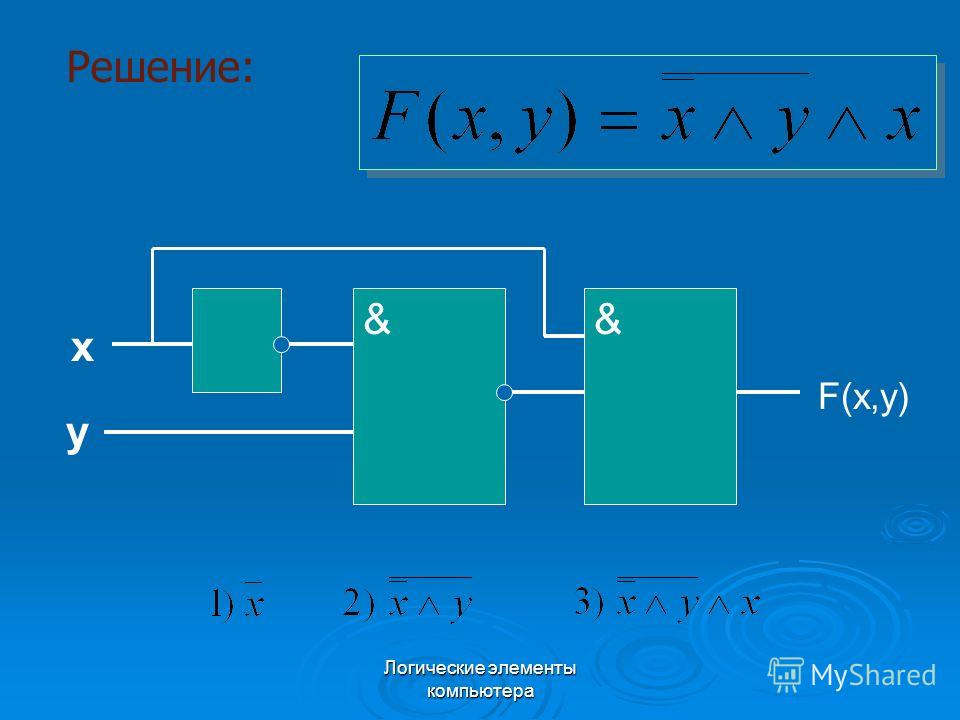

А сейчас давайте попробуем проанализировать несколько электронных схем и узнать, какой сигнал получится на выходе.

Смотрим на первую схему.

В ней используется только один элемент А. Снова будем использовать таблицу истинности. В первый столбец внесём входные данные ноль и один. Во второй столбец будем вносить данные, которые получаются при конъюнкции, в третьей – при инверсии. Он же будет являться столбцом, который будет обозначать выходные данные.

Мы видим, что от А идут две прямые. Это говорит о том, что одни и те же данные будут идти в двух направлениях. Первая операция – конъюнкция. При конъюнкции получим те же данные, что и в самом начале.

Далее идёт операция отрицания. При исходных данных, равных нулю получаем единицу, и наоборот, при исходных данных, равных единице получаем ноль.

Таким образом в итоге мы

получили Ā.

Рассмотрим ещё одну схему.

Она немного сложнее первой. Снова будем использовать таблицу истинности. Она будет состоять из 8 столбцов. В первых двух будут находится входные данные А и B. В третьем конъюнкция А, в четвёртом – конъюнкция B. В пятые и шестые столбцы запишем отрицания конъюнкций А и B соответственно. Для упрощения отрицания конъюнкций А и B запишем как Ā и . В седьмом будет находится конъюнкция Ā и . И в последнем отрицание конъюнкции Ā и .

Таким образом мы с вами переписали все операции со схемы в таблицу истинности. Нам осталось только заполнить таблицу соответствующими данными. Итак, при конъюнкции двух А мы получим такие же данные как и в первом столбце. Перепишем их.

Аналогично поступим и с конъюнкцией двух B. Только данные будем брать со второго столбца.

Пятый столбец – Ā. Преобразуем

данные, находящиеся в третьем столбце. Необходимо помнить, что при исходных

данных, равных нулю, мы получим единицу. А при исходных данных, равных единице,

получим ноль.

Необходимо помнить, что при исходных

данных, равных нулю, мы получим единицу. А при исходных данных, равных единице,

получим ноль.

Аналогично и с шестым столбцом, а данные будем брать с четвёртого.

Седьмой столбец – это конъюнкция Ā и . Данные будем брать из пятого и шестого столбцов. Мы с вами помним, что на выходе получим единицу тогда и только тогда, когда на всех входах будут единицы. Заполним таблицу.

И последняя операция – отрицание конъюнкции Ā и . Исходные данные будем брать из седьмого столбца. И снова нужно знать, что если исходные данные равны нулю, то на выходе мы получим один, и наоборот, если исходные данные равны единице, то на выходе получим ноль.

Таким образом мы с вами узнали, какие получатся выходные данные в нашей схеме. То есть данные из восьмого и есть наша F.

Если мы построим выражение исходя из таблицы истинности, то получим следующее:

И снова рассмотрим схему,

но более простую.

Для начала составим логическое выражение. Будем идти справа налево. Последний логических элемент, который к нас изображён – это инвертор. В него поступают сигналы от дизъюнктора. В свою очередь в дизъюнктор поступают данные от входа А и входа Бэ. В результате мы получим следующее:

А сейчас давайте на основании этого логического выражения составим таблицу истинности и узнаем, какие данные получатся на выходе.

Таблица будет состоять из 4 столбцов. В первые два вносим исходные данные А и B соответственно. Далее мы будем выполнять дизъюнкцию, а затем инверсию. Это и будет являться заголовками наших столбцов.

Итак, первая операция – дизъюнкция. Мы с вами знаем, что на выходе мы получим единицу тогда, когда хотя бы на одном входе будет единица. Данные будем брать из первого и второго столбцов. Заполним третий столбец.

Для того, чтобы внести

данные в четвёртый столбец, нам нужно брать входные данные из третьего. Если у

нас входные данные равны нулю, то на выходе мы получим единицу, а если входные

данные равны единицы, то на выходе будет ноль. Снова заполним таблицу.

Если у

нас входные данные равны нулю, то на выходе мы получим единицу, а если входные

данные равны единицы, то на выходе будет ноль. Снова заполним таблицу.

В четвёртом столбце находятся выходные данные для нашего выражения F.

А сейчас давайте рассмотрим пример, в котором мы сами научимся строить электронную схему исходя из логического выражения. А также найдём выходные данные с помощью таблицы истинности.

Итак, наше выражение выглядит следующим образом:

Сначала будет выполняться конъюнкция А и B. Изобразим А и B.

От них проведём две прямых и нарисуем прямоугольник, который будет обозначать конъюнктор. Поставим внутри соответствующий знак.

Далее у нас идёт дизъюнкция конъюнкции А и B с C. Изобразим C.

Затем проведём от неё ломанную.

От конъюнктора также проведём прямую. И снова нарисуем прямоугольник, который

будет изображать дизъюнктор. Снова поставим внутри соответствующий знак.

Снова поставим внутри соответствующий знак.

Нам осталось изобразить инвертор. Проведём от правой стороны дизъюнктора прямую и на пересечении дизъюнктора и прямой нарисуем незакрашенный кружок. Над выходной прямой напишем букву F.

Мы построили электронную схему. Теперь осталось построить таблицу истинности и найти выходные данные.

Таблица будет состоять из 6 столбцов. В первых трёх запишем всевозможные входные данные для А, B и C.

Четвёртый столбец – конъюнкция А и B, пятый дизъюнкция конъюнкции А и B и переменной C. Шестой инверсия всего выражения.

Теперь осталось заполнить таблицу данными.

При конъюнкции на выходе единица будет тогда и только тогда, когда на всех входах будут единицы. Для заполнения четвёртого столбца будем брать данные из первого и второго. Внесём данные в соответствии с данными.

Пятый столбец –

дизъюнкция. Данные будем брать из третьего и четвёртого столбцов. Заполним

столбец в соответствии с правилом: на выходе будет единица тогда, когда хотя бы

на одном входе будет единица.

Заполним

столбец в соответствии с правилом: на выходе будет единица тогда, когда хотя бы

на одном входе будет единица.

И последний, шестой столбец – инверсия. Данные будем брать из пятого столбца. Если на входе у нас элемент ноль, то на выходе будет единица, и наоборот. Заполним столбец.

Данные этого столбца являются выходными данными построенной нами электронной схемы.

А теперь давайте исходя из таблицы истинности составим выражение, а исходя из выражения – построим электронную схему.

Нам дана таблица истинности, в которой записаны входные данные и операции, которые необходимо выполнить. Все операции указаны в порядке выполнения их в выражении. Для начала давайте заполним таблицу и найдём выходные данные.

Первая операция –

дизъюнкция А и B. На выходе будет единица

тогда, когда хотя бы на одном входе будет единица. Заполним четвёртый столбец

исходя из данных первого и второго столбцов.

Вторая операция – инверсия C. Заполним пятый столбец исходя из данных третьего столбца. Необходимо помнить, что если входные данные равны нулю, то на выходе мы получим единицу. А если входные данные равны единице, то на выходе мы получим ноль. Внесём данные.

И последний столбец – конъюнкция дизъюнкции А или B и инверсии C. При выполнении конъюнкции мы с вами знаем, что на выходе единица будет тогда и только тогда, когда все входные данные равны единице. Заполним шестой столбец исходя из данных третьего и четвёртого столбцов.

Можно заметить, что всё наше выражение записано в шапке последнего шестого столбца. То есть, мы получим следующее:

Нам осталось построить электронную схему.

Запишем А и B и проведём от них прямые к прямоугольнику, который будет обозначать дизъюнктор. Обозначим это соответствующим символом.

Теперь нам нужно

изобразить инвертор. Для этого от C

идут ломанные к конъюнктору. А на пересечение прямой, которая выходит из

конъюнктора изобразим кружок, который и будет изображать отрицание.

Для этого от C

идут ломанные к конъюнктору. А на пересечение прямой, которая выходит из

конъюнктора изобразим кружок, который и будет изображать отрицание.

Теперь проводим кривые от дизъюнктора и конъюнктора к новому прямоугольнику. Он будет изображать конъюнктор. Обозначим его соответствующим знаком.

Проводим прямую из правой стороны крайнего конъюнктора, которая будет обозначать выходные данные. Обозначим её буквой F.

Мы выполнили с вами задание, в котором записали выражение исходя из таблицы истинности и построили электронную схему.

А сейчас пришла пора подвести итоги урока.

Сегодня мы с вами познакомились с такими логическими элементами, как конъюнктор, дизъюнктор и инвертор.

Научились исходя из схемы

при помощи таблицы истинности определять, какие данные должны получиться на

выходе, а также научились строить электронные схемы по данному выражению и

таблице истинности.

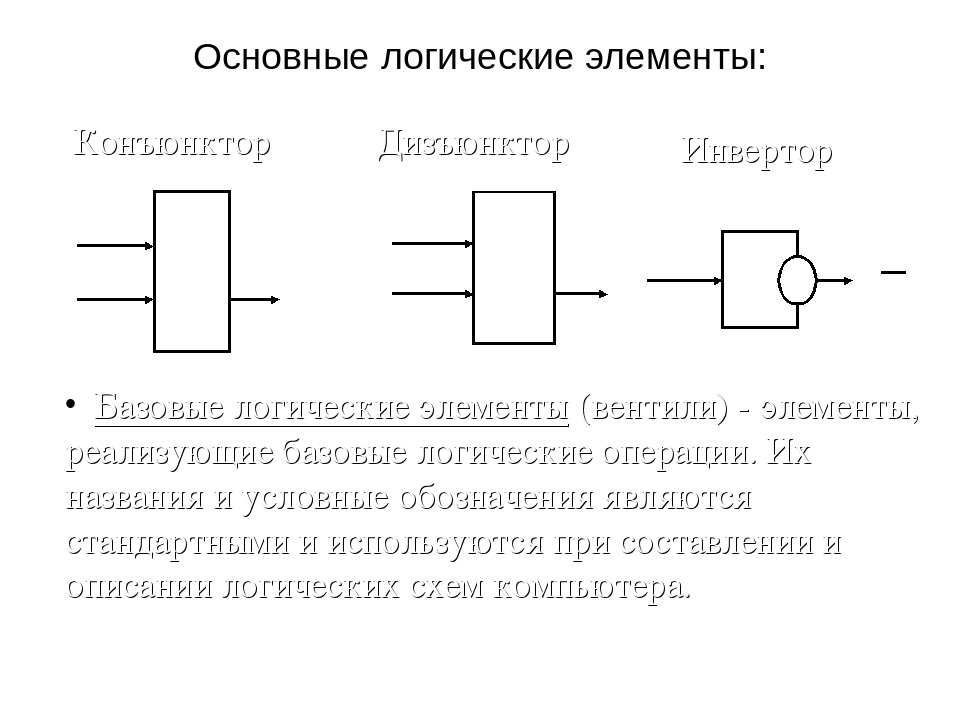

Базовые логические элементы

Базовые логические элементы “И”, “ИЛИ”, “НЕ”.

Алгебра логики – это математический аппарат, с помощью которого записывают, вычисляют, упрощают и преобразовывают логические высказывания.

Создателем алгебры логики является английский математик Джордж Буль (19 век), в честь которого она названа булевой алгеброй высказываний.

| Логическое высказывание – это любое повествовательное предложение, в отношении которого можно однозначно сказать, истинно оно или ложно. |

Например,

предложение «6 – четное число» – высказывание, так как оно истинное.

Математический аппарат алгебры

логики очень удобен для описания того, как функционируют аппаратные средства

компьютера, поскольку основной системой счисления в компьютере является

двоичная, в которой используются цифры 1 и 0, а значений логических переменных

тоже два: 1 и 0.

| Логический элемент компьютера — это часть электронной логической схемы, которая реализует элементарную логическую функцию. |

Логическими элементами

компьютеров являются электронные схемы И, ИЛИ, НЕ, И-НЕ, ИЛИ-НЕ и др.

(называемые также вентилями), а также триггер.

С помощью этих схем можно реализовать

любую логическую функцию, описывающую работу устройств компьютера.

Работу логических элементов описывают

с помощью таблиц истинности.

Базовые логические элементы И, ИЛИ, НЕ

Схема И реализует конъюнкцию (логическое умножение) двух или более

логических значений.

Эл. | |

Таблица истинности | ||

х | y | х и у |

0 | 0 | 0 |

0 | 1 | 0 |

1 | 0 | 0 |

1 | 1 | 1 |

Единица на выходе

схемы И будет тогда и только тогда, когда на всех входах будут единицы. у (читается

как «х и у»).

у (читается

как «х и у»).

Операция конъюнкции на

функциональных схемах обозначается знаком & (читается как «амперсэнд»),

являющимся сокращенной записью английского слова and.

Схема ИЛИ реализует дизъюнкцию (логическое сложение) двух или более логических значений.

Эл. схема | |

Таблица истинности | ||

х | y | х или у |

0 | 0 | 0 |

0 | 1 | 1 |

1 | 0 | 10 |

1 | 1 | 1 |

Когда хотя бы на

одном входе схемы ИЛИ будет единица, на ее выходе также будет единица.

Знак «1» на схеме — от устаревшего

обозначения дизъюнкции как «>=!» (т.е. значение дизъюнкции равно единице,

если сумма значений операндов больше или равна 1). Связь между выходом

z этой схемы и входами х и у описывается соотношением z = х или у.

Схема НЕ (инвертор) реализует операцию отрицания.

| |||||||||

Связь между входом х этой схемы и выходом z можно записать соотношением Z = ,

где х читается как «не х» или «инверсия.

Если на входе схемы 0, то на выходе 1. Когда на входе 1 на выходе

0.

Логические элементы

Логические элементыЛогические элементы

Логическим элементом

называется электрическая схема,

выполняющая какую-либо логическую

операцию (операции) над входными

данными, заданными в виде уровней

напряжения, и возвращающая

результат операции в виде

выходного уровня напряжения. Так

как операнды логических операций

задаются в двоичной системе

счисления, то логический элемент

воспринимает входные данные в виде

высокого и низкого уровней

напряжения на своих входах.

Соответственно, высокий уровень

напряжения (напряжение логической

1) символизирует истинное значение

операнда, а низкий (напряжение

логического 0) – ложное. Значения

высокого и низкого уровней

напряжения определяются

электрическими параметрами схемы

логического элемента и одинаковы

как для входных, так и для выходных

сигналов. Обычно, логические

элементы собираются как отдельная

интегральная микросхема. К числу

логических операций, выполняемых

логическими элементами относятся

конъюнкция (логическое умножение,

И), дизъюнкция (логическое сложение,

ИЛИ), отрицание (НЕ) и сложение по

модулю 2 (исключающее ИЛИ).

Рассмотрим основные типы

логических элементов.

Обычно, логические

элементы собираются как отдельная

интегральная микросхема. К числу

логических операций, выполняемых

логическими элементами относятся

конъюнкция (логическое умножение,

И), дизъюнкция (логическое сложение,

ИЛИ), отрицание (НЕ) и сложение по

модулю 2 (исключающее ИЛИ).

Рассмотрим основные типы

логических элементов.

Элемент И

Логический элемент И выполняет операцию логического умножения (конъюнкция) над своими входными данными и имеет от 2 до 8 входов и один выход (как правило, выпускаются элементы с двумя, тремя, четырьмя и восемью входами). На рис. 1. изображены условные графические обозначения (УГО) логических элементов И с двумя, тремя и четырьмя входами соответственно. Элементы И обозначаются как NИ, где N – количество входов логического элемента (например, 2И, 3И, 8И и т.д.).

| Рис. 1 |

Элемент ИЛИ

Логический элемент ИЛИ

выполняет операцию логического

сложения (дизъюнкция) над своими

входными данными и, также как и

логический элемент И, имеет от 2 до 8

входов и один выход. На рис. 2.

изображены УГО логических

элементов ИЛИ с двумя, тремя и

четырьмя входами соответственно.

Элементы ИЛИ обозначаются также,

как и элементы И (2ИЛИ, 4ИЛИ и т.д.).

На рис. 2.

изображены УГО логических

элементов ИЛИ с двумя, тремя и

четырьмя входами соответственно.

Элементы ИЛИ обозначаются также,

как и элементы И (2ИЛИ, 4ИЛИ и т.д.).

| Рис. 2 |

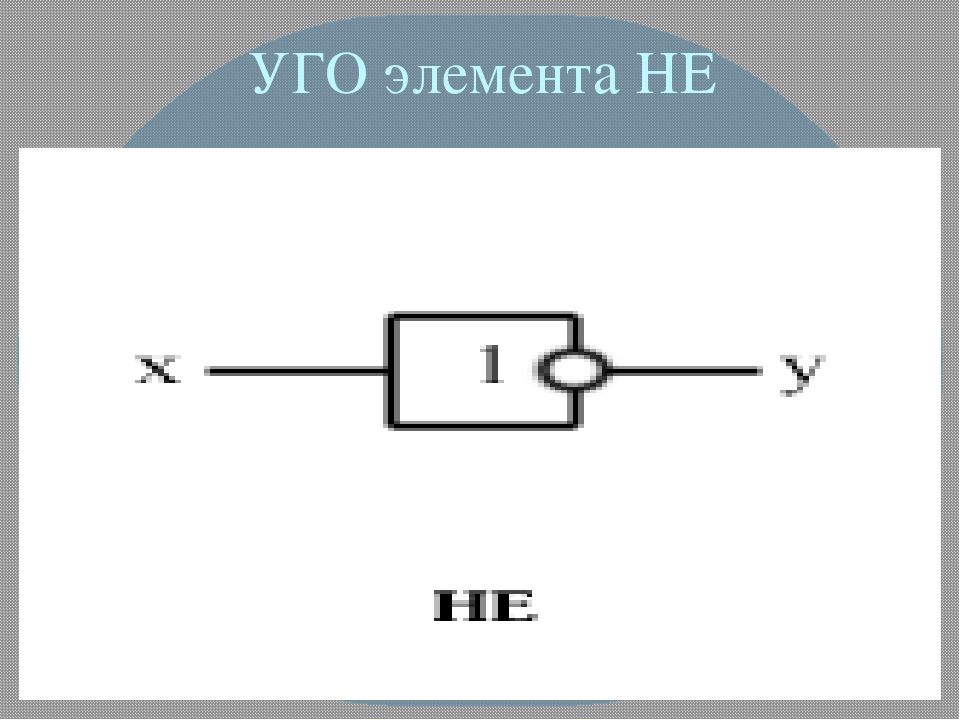

Элемент НЕ (инвертор)

Логический элемент НЕ выполняет операцию логического отрицания над своими входными данными и имеет один вход и один выход. Иногда его называют инвертор, так как он инвертирует входной сигнал. На рис. 3 изображено УГО элемента НЕ.

| Рис. 3 |

Элемент И-НЕ

Логический элемент И-НЕ

выполняет операцию логического

умножения над своими входными

данными, а затем инвертирует

(отрицает) полученный результат и

выдаёт его на выход. Таким образом,

можно сказать, что логический

элемент И-НЕ – это элемент И с

инвертором на выходе. УГО элемента 3И-НЕ

приведено на рис. 4.

Таким образом,

можно сказать, что логический

элемент И-НЕ – это элемент И с

инвертором на выходе. УГО элемента 3И-НЕ

приведено на рис. 4.

| Рис. 4 |

Элемент ИЛИ-НЕ

Логический элемент ИЛИ-НЕ выполняет операцию логического сложения над своими входными данными, а затем инвертирует (отрицает) полученный результат и выдаёт его на выход. Таким образом, можно сказать, что логический элемент ИЛИ-НЕ – это элемент ИЛИ с инвертором на выходе. УГО элемента 3ИЛИ-НЕ приведено на рис. 5.

| Рис. 5 |

Элемент сложения по модулю 2

Этот логический элемент

выполняет логическую операцию

сложения по модулю 2 и, как правило,

имеет 2 входа и один выход. Такой

элемент, в основном, используется в

схемах аппаратного контроля. УГО

элемента приведено на рис. 6.

Такой

элемент, в основном, используется в

схемах аппаратного контроля. УГО

элемента приведено на рис. 6.

| Рис. 6 |

Комбинационные логические элементы

Существуют и более сложные логические элементы, выполняющие несколько логических операций над своими входными данными. Например, элемент 2И-ИЛИ, УГО и схема которого приведено на рис. 7, сначала выполняет операцию логического умножения над парами операндов x1, x2 и x3, x4, а затем выполняет операцию логического сложения над полученными результатами, т.е. y = x1x2 + x3x4. Можно придумать и более сложные комбинационные логические элементы, например 3-2И-ИЛИ-НЕ (рис. 8).

| Рис. 7 |

Рис. 8 8 |

Универсальные логические элементы

Универсальные логические элементы могут использоваться для выполнения разнообразных операций над своими входными данными. Конкретная операция зависит от того, какие сигналы поданы на управляющие входы. Чтобы синтезировать такой универсальный логический элемент, обычно пользуются СКНФ или СДНФ, как и в синтезе комбинационных логических схем.

Электрические принципиальные схемы логических элементов

При рассмотрении

электрических принципиальных схем

логических элементов пользуются

термином тип логики. Тип логики

определяет элементную базу, на

которой собран логический элемент,

а также отражает некоторые

особенности отдельных элементов

этой элементной базы и

характеристики самого логического

элемента. Наиболее распространены

следующие типы логик: ТТЛ, ДТЛ, МОП,

КМОП, также существуют типы логик

ЭСЛ, РЕТЛ и некоторые другие. Тип

логики ТТЛ

(транзисторно-транзисторная

логика) определяет элементную базу,

на которой собран логический

элемент, как состоящую

преимущественно из транзисторов,

причём транзисторы используются и

на входе, и на выходе логического

элемента (отсюда и название –

транзисторно-транзисторная). Тип

логики ДТЛ (диодно-транзисторная

логика) определяет элементную базу

как состоящую преимущественно из

транзисторов и диодов (диоды на

входе, транзисторы – на выходе). Типы

логик МОП

(металл-оксид-полупроводник) и КМОП

определяет элементную базу как

состоящую из транзисторов МДП

(металл-диэлектрик-полупроводник),

причём микросхемы этого типа имеют

очень низкую потребляемую

мощность, засчёт особенностей МДП

транзисторов оперировать малыми

токами и имеющими очень малый ток

утечки.

Тип

логики ТТЛ

(транзисторно-транзисторная

логика) определяет элементную базу,

на которой собран логический

элемент, как состоящую

преимущественно из транзисторов,

причём транзисторы используются и

на входе, и на выходе логического

элемента (отсюда и название –

транзисторно-транзисторная). Тип

логики ДТЛ (диодно-транзисторная

логика) определяет элементную базу

как состоящую преимущественно из

транзисторов и диодов (диоды на

входе, транзисторы – на выходе). Типы

логик МОП

(металл-оксид-полупроводник) и КМОП

определяет элементную базу как

состоящую из транзисторов МДП

(металл-диэлектрик-полупроводник),

причём микросхемы этого типа имеют

очень низкую потребляемую

мощность, засчёт особенностей МДП

транзисторов оперировать малыми

токами и имеющими очень малый ток

утечки.

Рассмотрим электрические принципиальные схемы логического элемента И-НЕ с n входами – ДТЛ (рис. 9) и логического элемента И-НЕ с n входами – ТТЛ (рис. 10).

Рис. 9 9 |

| Рис. 10 |

На рисунках +U обозначает положительный потенциал источника питания, а -U – отрицательный.

Рассмотрим сначала работу

схемы на рис. 9. Если к одному из

входных диодов приложено

напряжение логического 0, то этот

диод открыт и на базу транзистора

подаётся напряжение логического 0.

Транзистор закрывается и на выходе y устанавливается напряжение

логической 1. Только когда ко всем

входным диодам будет приложено

напряжение логической 1 транзистор

откроется и на выходе установится

напряжение логического 0.

Оставшиеся каскады на транзисторах

выполняют функцию усиления сигнала

и инвертирования. При подаче на

вход второго транзистора

напряжения логического 0, он

закроется, подключив базы

транзисторов оконечного каскада

через резисторы к плюсу и к минусу

источника питания. Один из

транзисторов оконечного каскада

откроется, а другой – закроется и на

выходе установится напряжение

логической 1. При подаче на второй

транзистор напряжения логической 1,

он откроется. Теперь открытый и

закрытый транзисторы оконечного

каскада поменяются местами и на

выходе установится напряжение

логического 0.

При подаче на второй

транзистор напряжения логической 1,

он откроется. Теперь открытый и

закрытый транзисторы оконечного

каскада поменяются местами и на

выходе установится напряжение

логического 0.

Теперь рассмотрим работу схемы на рис. 10. Вызывает некоторый интерес необычный транзистор на входе и схема его включения. Такие многоэмиттерные транзисторы всегда используются на входах логических элементов ТТЛ. Сам транзистор выполняет логическую операцию И. При подаче на один из входов напряжения логического нуля, транзистор открывается и, таким образом, на коллекторе устанавливается напряжение логического 0. Напряжение логической 1 будет на коллекторе только тогда, когда на всех входах будет напряжение логической 1. Подобный транзистор можно рассматривать как много n-p переходов, а соответственно, как много диодов. Таким образом такое включение транзистора в цепь эквивалентно диодной сборке на входе логического элемента И на рис. 9.

Применение логических элементов

Логические элементы могут

использоваться как

самостоятельные части схемы, так и

входить в состав более сложной

цифровой комбинационной схемы или

схемы с памятью. Как

самостоятельные части схемы,

логические элементы могут

применяться в качестве управляющей

логики какого-либо устройства, а

также в качестве генератора

прямоугольных импульсов с

подключённой ёмкостью или

кварцевым резонатором. В качестве

комбинационных схем логические

элементы используются в составе

микросхем БИС и СБИС, а также в

дешифраторах и шифраторах,

выполненных в виде отдельных

микросхем. Также, логические

элементы могут входить в состав

схем с памятью (триггеры, регистры,

счётчики и т.д.), выполненных в виде

отдельной микросхемы или в составе

других микросхем.

Как

самостоятельные части схемы,

логические элементы могут

применяться в качестве управляющей

логики какого-либо устройства, а

также в качестве генератора

прямоугольных импульсов с

подключённой ёмкостью или

кварцевым резонатором. В качестве

комбинационных схем логические

элементы используются в составе

микросхем БИС и СБИС, а также в

дешифраторах и шифраторах,

выполненных в виде отдельных

микросхем. Также, логические

элементы могут входить в состав

схем с памятью (триггеры, регистры,

счётчики и т.д.), выполненных в виде

отдельной микросхемы или в составе

других микросхем.

Элементы Исключающее ИЛИ/Исключающее ИЛИ-НЕ/Нечётность/Чётность

| Библиотека: | Базовые |

| Введён в: | 2.0 Beta 1 для Исключающее ИЛИ/Нечётность/Чётность; 2.0 Beta 6 для Исключающее ИЛИ-НЕ |

| Внешний вид: |

Поведение

Элементы Исключающее ИЛИ, Исключающее ИЛИ-НЕ, Нечётность и Чётность вычисляют соответствующую функцию от значений на входах и выдают результат на выход.

По умолчанию, неподключенные входы игнорируются – то есть, если входы действительно не имеют ничего подключенного к ним – даже провода. Таким образом, вы можете добавить 5-входовый элемент, но подключить только два входа, и он будет работать как 2-входовый элемент; это избавляет вас от необходимости беспокоиться о настройке количества входов каждый раз при создании элемента. (Если все входы не подключены, то на выходе значение ошибки X.) Некоторые пользователи, однако, предпочитают, чтобы Logisim настаивал, чтобы все входы были подключены, поскольку это соответствует реальным элементам. Вы можете включить это поведение, выбрав меню Проект > Параметры…, перейдя на вкладку Моделирование, и выбрав вариант Ошибка для неопределённых входов

для Выход элемента при неопределённости

.

Двухвходовая таблица истинности для элементов следующая.

| x | y | Исключающее ИЛИ | Исключающее ИЛИ-НЕ | Нечётность | Чётность |

|---|---|---|---|---|---|

| 0 | 0 | 0 | 1 | 0 | 1 |

| 0 | 1 | 1 | 0 | 1 | 0 |

| 1 | 0 | 1 | 0 | 1 | 0 |

| 1 | 1 | 0 | 1 | 0 | 1 |

Как вы можете видеть, элементы Нечётность и Исключающее ИЛИ ведут себя одинаково в случае двух входов; аналогично, элементы Чётность и Исключающее ИЛИ-НЕ ведут себя одинаково. Но если входов с определённым значением больше двух, то элемент Исключающее ИЛИ будет давать на выходе 1, когда единица строго на одном входе, тогда как элемент Нечётность даст на выходе 1, когда единица на нечётном количестве входов. Элемент Исключающее ИЛИ-НЕ будет давать на выходе 1, когда входов с единицей строго не один, тогда как элемент Чётность даст 1, когда входов с единицей чётное количество. Элементы Исключающее ИЛИ и Исключающее ИЛИ-НЕ имеют атрибут, названный Многовходовое поведение, который позволяет настроить их на использование поведения элементов Нечётность и Чётность.

Если на каких-либо входах значение ошибки (например, если противоречивые значения поступают на один и тот же провод) или плавающее значение, то на выходе будет значение ошибки.

Многобитные версии каждого элемента будут выполнять свои однобитные преобразования над входами поразрядно.

Примечание: многие специалисты утверждают, что поведение фигурного элемента Исключающее ИЛИ должно соответствовать поведению элемента Нечётность, но по этому вопросу нет согласия. Поведение Logisim по умолчанию для элемента Исключающее ИЛИ основано на стандарте IEEE 91. Это также согласуется с интуитивным пониманием термина Исключающее ИЛИ: официант, спрашивающий, хотите вы гарнир из картофельного пюре, моркови, зеленого горошка, или шинкованной капусты, примет только один выбор, а не три, независимо от того, что вам могут сказать некоторые специалисты. (Должен признать, однако, что я не подвергал это заявление серьезным испытаниям.) Вы можете настроить элементы Исключающее ИЛИ и Исключающее ИЛИ-НЕ на использование одного из вариантов, меняя его атрибут Многовходовое поведение

.

Контакты (предполагается, что компонент направлен на восток)

- Западный край (входы, разрядность соответствует атрибуту Биты данных)

Входы компонента. Их будет столько, сколько указано в атрибуте Количество входов.

Заметьте, что если вы используете фигурные элементы, то западный край элементов Исключающее ИЛИ и Исключающее ИЛИ-НЕ будет искривлён. Тем не менее, входные контакты расположены вряд. Logisim отрисовывает короткие отрезки чтобы показать это; если вы перекроете отрезок, программа будет без предупреждений предполагать, что вы не хотели перекрыть его. При использовании “Вида для печати”, эти отрезки не будут отрисованы, если не подключены к проводам.

- Восточный край (выход, разрядность соответствует атрибуту Биты данных)

Выход элемента, значение на котором вычисляется на основании текущих значений на входах, как описано выше.

Атрибуты

Когда компонент выбран, или уже добавлен, клавиши от 0 до 9 меняют его атрибут Количество входов

, комбинации от Alt-0 до Alt-9 меняют его атрибут Биты данных

, а клавиши со стрелками меняют его атрибут Направление

.

- Направление

- Направление компонента (его выхода относительно его входов).

- Биты данных

- Разрядность входов и выходов компонента.

- Размер элемента

- Определяет, следует отрисовывать широкую или узкую версию компонента. Это не влияет на количество входов, которое определяется атрибутом Количество входов; правда, если количество входов превышает 3 (для узкого компонента) или 5 (для широкого), то элемент будет отрисовываться с “крыльями”, чтобы вместить запрошенное количество входов.

- Количество входов

- Определяет, сколько контактов на западном крае будет иметь компонент.

- Многовходовое поведение (только для Исключающее ИЛИ и Исключающее ИЛИ-НЕ)

- Когда входов три или более, то значение на выходе элементов Исключающее ИЛИ и Исключающее ИЛИ-НЕ будет основано или на том, что 1 строго на одном входе (по умолчанию), или на нечётном количестве входов.

Поведение Инструмента Нажатие

Нет.

Поведение Инструмента Текст

Нет.

Назад к Справке по библиотеке

8. Понятие о логических элементах и микропроцессорах

8.1. Логические элементы

Логические элементы (узлы) предназначены для выполнения различных логических (функциональных) операций над дискретными сигналами при двоичном способе их представления (1; 0).

Преимущественное распространение получили логические элементы потенциального типа. В них используются дискретные сигналы, нулевому значению «0» которых соответствует уровень низкого потенциала, а единичному значению «1» – уровень высокого потенциала (отрицательного или положительного).

Потенциальные логические элементы нашли исключительное применение в интегральном исполнении в виде микросхем.

Микросхема – это электронный узел, блок или устройство, изготовленное с высокой степенью миниатюризации, в которой каждый электронный компонент представляет собой не отдельно взятый транзистор, диод, резистор, конденсатор и т. д., а их неразъемное схемное соединение. Количество элементов, входящих в микросхему, может достигать тысяч и более элементов.

Применение микросхем легло в основу современного направления электроники – микроэлектроники, которая решает проблемы повышения надёжности, уменьшения массогабаритных показателей и стоимости электронной аппаратуры.

Логические биполярные микросхемы чаще всего выполняются на транзисторах типа n-p-n c напряжением питания Eк > 0, причём «1» – соответствует закрытое состояние транзистора, а «0» – открытое. Процесс перехода транзистора из одного состояния в другое достаточно быстрый.

Все схемы цифровой техники выполняются на логических интегральных микросхемах.

Работу логического элемента можно описать зависимостью логического значения выходного сигнала F от совокупности логических значений входных сигналов x. Такую зависимость принято представлять таблицей истинности.

Для любых логических преобразований достаточно иметь три элементарных логических элемента, выполняющих следующие операции: логическое сложение (логическое ИЛИ), логическое умножение (логическое И) и логическое отрицание (логическое НЕ).

Логический элемент ИЛИ – имеет несколько входов и один общий выход. Элемент ИЛИ осуществляет логическое сложение (дизъюнкцию).

F = x1 x2, или F = x1 + x2

где F – функция; x1……xn – аргументы (переменные двоичные сигналы на входе).

Его условное обозначение показано на рис. 67, а, а электрическая схема на полупроводниковых диодах – на рис. 67, б.

Функция F = 0, когда все ее аргументы равны нулю, и F = 1 при одном, нескольких или всех аргументах, равных единице. Значение F = 1 на выходе создается передачей входного сигнала вследствие отпирания соответствующего диода. К диодам, для которых входной сигнал равен нулю, прикладывается обратное напряжение, и они находятся в закрытом состоянии.

F = x1 x2 … xn или F = x1 + x2 +…+ xn.

Логический элемент И – имеет несколько входов и один выход. Элемент И осуществляет логическое умножение (конъюнкцию).

F = x1 x2 или F = x1x2

Его условное обозначение показано на рис. 68, а, а электрическая схема на полупроводниковых диодах – на рис. 68, б.

F = x1 x2… xn или F = x1x2… xn.

Функция F = 0, когда хотя бы один из ее аргументов равен нулю и F = 1 при всех аргументах, равных единице.

Логический элемент И является схемой совпадения: сигнал «1» на выходе появляется при совпадении сигналов «1» на всех входах. Отличие схемы И (рис. 68, б) от схемы ИЛИ (рис. 67, б) заключается в изменении полярности включения диодов и наличии резистора R1, подключенного к шине «+» источника питания. При всех входных сигналах, равных единице, на катодах диодов имеется положительный потенциал относительно общей точки и все диоды закрыты. На выходе схемы создается напряжение ER2 / (R1+R2), определяющее F = 1. При нулевом значении сигнала хотя бы на одном из входов соответствующий диод будет проводить ток и шунтировать резистор R2, выполняющий роль нагрузки. Напряжение на выходе при этом определяется падением напряжения на открытом диоде и близко к нулю (F = 0). На рис. 68, б показан вариант, когда x1 = 0 и ток проводит диод VD1. Увеличение числа входов с нулевым значением сигнала приводит только к увеличению числа проводящих диодов, а функция F остается равной нулю.

Логический элемент НЕ – имеет один вход и один выход. Элемент НЕ выполняет операцию отрицания (инверсии), в связи с чем его часто называют логическим инвертором. Им реализуется функция

.

Сигнал x = 0 на входе соответствует F = 1 и, наоборот, при x = 1 F = 0. Логический элемент НЕ представляет собой ключевую схему на транзисторе (рис 69, б), его условное обозначение показано на рис. 69, а.

При x = 0 (UВХ = 0) транзистор закрыт, напряжение Uкэ Eк, т. е. F = 1. При x = 1 (Uвх = Uвх.отп) транзистор открыт, напряжение Uкэ = = Uкэ.откр 0, т. е. F = 0. Открытое состояние транзистора обеспечивается заданием тока базы, вводящего транзистор в режим насыщения.

На практике часто используется расширенный набор логических элементов.

К ним относятся логические элементы:

ИЛИ-НЕ (стрелка Пирса), реализующий функцию

;

И-НЕ (штрих Шеффера), реализующий функцию:

.

Рабочие свойства логических элементов определяет ряд параметров:

– быстродействие – время задержки между сменой состояний входного и выходного сигналов;

– нагрузочная способность или коэффициент разветвления – число входов, которые можно подключить к одному выходу;

– помехоустойчивость – максимально допустимый уровень напряжения помехи, не вызывающий ложного переключения;

– степень генерирования помех – интенсивность колебаний тока при переключении элементов;

– мощность рассеяния – мощность потерь энергии в элементах.

Логические элементы

Глава 1. КОМБИНАЦИОННЫЕ СХЕМЫ И ЦИФРОВЫЕ АВТОМАТЫ

1.1. Логические элементы

Различают комбинационные схемы и цифровые автоматы. В комбинационных схемах состояние на выходе в данный момент времени однозначно определяется состояниями на входах в тот же момент времени. Комбинационными схемами, например, являются логические элементы И, ИЛИ, НЕ и их комбинации. В цифровом автомате состояние на выходе определяется не только состояниями на входах в данный момент времени, но и предыдущим состоянием системы. К цифровым автоматам относятся триггеры.

Логическими элементами называются элементы, выполняющие логические операции И, ИЛИ, НЕ и комбинации этих операций. Указанные логические операции можно реализовать с помощью контактно-релейных схем и с помощью электронных схем. В настоящее время в подавляющем большинстве применяется электронные логические элементы, причем электронные логические элементы входят в состав микросхем. Имея в распоряжении логические элементы И, ИЛИ, НЕ, можно сконструировать цифровое электронное устройство любой сложности. Электронная часть любого компьютера состоит из логических элементов.

Система простых логических функций, на основе которой можно получить любую логическую функцию, называется функционально полной.

Отсюда следует, что для построения логического устройства любой сложности достаточно иметь однотипные логические элементы, например, И-НЕ или ИЛИ-НЕ.

Логические элементы могут работать в режимах положительной и отрицательной логики. Для электронных логических элементов в режиме положительной логики логической единице соответствует высокий уровень напряжения, а логическому нулю – низкий уровень напряжения. В режиме отрицательной логики логической единице соответствует низкий уровень напряжения, а логическому нулю – высокий.

Для контактно-релейных схем в режиме положительной логики логической единице соответствует замкнутый контакт ключа или реле, а логическому нулю – разомкнутый. Светящийся индикатор (лампочка, светодиод) соответствует логической единице, а несветящийся – логическому нулю.

Логические элементы, реализующие для режима положительной логики операцию И, для режима отрицательной логики выполняют операцию ИЛИ, и наоборот. Так, например, микросхема, реализующая для положительной логики функции элемента 2И-НЕ, будет выполнять для отрицательной логики функции элемента 2ИЛИ-НЕ.

Как правило, паспортное обозначение логического элемента соответствует функции, реализуемой “положительной логикой”. Логические элементы И, ИЛИ, НЕ имеют один выход, число входов логических элементов И, ИЛИ может быть любым начиная с двух. Логические элементы И и ИЛИ, выпускаемые в составе микросхем, обычно имеют 2, 3, 4, 8 входов. В названии элемента первая цифра указывает число входов.

Прежде всего, рассмотрим реализацию логических элементов с помощью контактно-релейных схем. Рассмотрим логический элемент 2И. Он выполняет операцию логического умножения. На рисунке 1.1,а приведена контактно-релейная схема логического элемента 2И для режима положительной логики.

Обозначение логического элемента 2И на принципиальных схемах показано на рисунке 1.1,б. Знак & (амперсант) в левом верхнем углу прямоугольника указывает, что это логический элемент И. Первые две буквы обозначения DD1.2 указывают на то, что это цифровая микросхема, цифра слева от точки указывает номер микросхемы на принципиальной схеме, а цифра справа от точки – номер логического элемента в составе данной микросхемы.

Функционирование логического элемента обычно задают таблицей истинности. Контактно-релейная схема логического элемента 2И (режим положительной логики) позволяет легко составить таблицу истинности этого элемента. Так как микросхема имеет для подачи входных сигналов два входа, то возможны 22=4 различных комбинации входных сигналов. Необходимо проанализировать состояние лампочки при различных положениях тумблеров Sa1, Sa2, т.е. рассмотреть 4 различных комбинации состояний тумблеров (рис. 1.1,в).

Введение понятия активного логического уровня существенно облегчает анализ функционирования сложных цифровых устройств. Активным логическим уровнем на входе элемента (логический нуль, логическая единица) называется такой уровень, который однозначно задает состояние на выходе элемента независимо от логических уровней на остальных входах элемента. Активный логический уровень на одном из входов элемента определяет уровень на его выходе. Уровни, обратные активным, называются пассивными логическими уровнями.

Активным логическим уровнем для элементов И является логический нуль. Пусть, например, имеем логический элемент 8И. Необходимо проанализировать 28=256 различных состояний для составления таблицы истинности этого элемента. Воспользуемся понятием активного логического уровня. Если хотя бы на одном из входов этого элемента будет активный логический уровень, то состояние на выходе элемента определено однозначно и нет необходимости анализировать состояния на остальных входах элемента.

Таким образом, таблицу истинности логического элемента 8И можно свести к двум строчкам: на выходе этого элемента будет логическая единица, если на всех входах будут сигналы логической единицы и на выходе будет логический нуль, если хотя бы на одном из входов элемента будет сигнал логического нуля.

Логический элемент 2ИЛИ выполняет логическую операцию логического сложения у=х1+х2. Контактно-релейная схема элемента приведена на рисунке 1.2,а, а его условное обозначение – на рисунке 1.2,б. Знание контактно-релейной схемы элемента позволяет составить таблицу истинности (рис.1.2,в). Лампочка будет гореть, если замкнуты контакты хотя бы одного тумблера, т.е. активным логическим уровнем для элементов ИЛИ является уровень логической единицы.

Логический элемент НЕ выполняет операцию отрицания, и для этого элемента проще составить сразу таблицу истинности, а не вычерчивать сначала контактно-релейную схему, а затем по ней составлять таблицу истинности. Для логических элементов И и ИЛИ проще сначала вычертить контактно-релейную схему, а уже потом составлять таблицу истинности.

Напомним алгоритм работы электромагнитного реле с нормально замкнутыми контактами: при отсутствии электрического тока через обмотку реле контакты реле замкнуты, а при протекании достаточного тока через обмотку реле контакты реле разомкнуты. Контактно релейная схема элемента НЕ приведена на рисунке 1.3а, а его условное обозначение – на рисунке 1.3б.

Проанализируем работу контактно-релейной схемы логического элемента НЕ (рис. 1.3а). Если контакты ключа Sa1 разомкнуты, то через обмотку К электромагнитного реле ток протекать не будет. Контакты К1.1 (цифра слева от точки указывает номер реле на принципиальной схеме, а цифра справа – номер контактной группы данного реле) будут замкнуты (электромагнитное реле с нормально замкнутыми контактами). Электрическая лампочка HL1 в этом случае будет гореть, что для режима положительной логики будет означать логическую единицу. При замкнутых контактах ключа Sa1 (на входе элемента логическая единица) через обмотку реле протекает ток, достаточный для размыкания контактов К1.1, поэтому лампочка перестает гореть (логический нуль). В результате анализа мы получили, что сигнал на выходе элемента противоположен сигналу на входе, т.е. если на входе элемента сигнал логической единицы, то на выходе элемента сигнал логического нуля и наоборот (рис. 1.3,в).

При анализе работы логических элементов следует помнить о режиме их работы (режим положительной или отрицательной логики). Логические элементы, реализующие для режима положительной логики операцию И, для

режима отрицательной логики выполняют операцию ИЛИ и наоборот. Решим следующую задачу.

Задача. Какую логическую операцию выполняет контактно-релейная схема, приведенная на рисунке 1.4.

Правильным ответом в этой задаче будет следующий. Указанная контактно-релейная схема выполняет операцию 3И для режима положительной логики и 3ИЛИ для режима отрицательной логики (решение обосновать самостоятельно).

В практической работе широко используются комбинации логических элементов и особенно элементы И-НЕ и ИЛИ-НЕ. Рассмотрим подробнее контактно-релейную схему элемента 2ИЛИ-НЕ, приведенную на рисунке 1.5,а. Условное обозначение элемента на принципиальных схемах показано на рисунке 1.5,б. Заполним таблицу истинности, приведенную на рисунке 1.5в. Если оба ключа разомкнуты (Х1=0, Х2=0), то лампочка HL1 горит, что соответствует логической единице на выходе элемента (Y=1). Замкнем контакты ключа Sa1 (Х1=1), оставляя ключ Sa2 разомкнутым (Х2=0). Лампочка HL1 в этом случае не горит (Y=0). Если замкнут хотя бы один ключ, то лампочка не горит. Следовательно, активным логическим уровнем на входе элемента ИЛИ-НЕ является уровень логической единицы.

Для двух аргументов логического элемента возможны 16 логических функций. В данном пособии рассматриваются логические функции: логическое И, логическое ИЛИ, логическое НЕ, логическое И-НЕ, логическое ИЛИ-НЕ, сумма по модулю 2.

В таблице 1.1 приведены условные обозначения элементов 2И, 2ИЛИ, НЕ, 2И-НЕ, 2ИЛИ-НЕ, исключающее ИЛИ (сумма по модулю 2), условные обозначения выполняемых этими элементами логических операций, таблицы их истинности и контактно-релейные схемы. При анализе контактно-релейной схемы элемента исключающее ИЛИ необходимо учитывать, что положения переключателей SA1 и SA2 в таблице 1.1 соответствуют логическим единицам (верхнее положение подвижного контакта переключателя соответствует логической единице), т.е. Х1=1 и Х2=1. Лампочка HL1 горит лишь в том случае, когда подвижный контакт одного из переключателей находится в верхнем положении, а подвижный контакт второго переключателя в нижнем положении. Из анализа работы данной контактно-релейной схемы получаем таблицу истинности элемента исключающее ИЛИ.

Рассмотрим решение следующей задачи: имея в распоряжении логические элементы 2И-НЕ, сконструировать устройство, реализующее операцию 3ИЛИ-НЕ для режима положительной логики. Эту задачу решим в два этапа. Сначала сконструируем устройство, выполняющее операцию 3И-НЕ для режима положительной логики (рис. 1.6,а), а потом на входах и выходе элемента 3И-НЕ установим логические элементы НЕ (рис. 1.6,б).

По мере развития вычислительной техники электронные логические элементы совершенствовались. Рассмотрим принципиальную схему логического элемента 2И (рис. 1.7,а), построенного на диодах и резисторах. Для простоты рассмотрения будем считать, что напряжение логического «0» на входе элемента равно 0 В, а напряжение логической «1» – 5 В. Внутреннее сопротивление вольтметра значительно больше сопротивления резистора R1.

Вспомним особенности вольтамперной характеристики полупроводникового кремниевого диода небольшой мощности. При обратном напряжении ток, протекающий через диод, составляет десятые доли микроампера. Напряжение на диоде при протекании через него в прямом направлении тока в десятки миллиампер, равно приблизительно 0,7-0,8 В. Определим примерно параметры логических уровней на выходах данного элемента, если на входе действуют логические уровни с указанными ранее параметрами. Если на оба входа поданы напряжения логических «1», то токи через диоды VD1 и VD2 не протекают, и напряжение на выходе элемента при условии, что сопротивление нагрузки значительно больше сопротивления резистора R1, будет примерно равно напряжению питания. Если хотя бы один из входов элемента соединить с минусовым проводом источника питания, то на выходе элемента в случае кремниевых диодов будет напряжение 0,7 – 0,8 В (зависит от сопротивления резистора R1 и напряжения источника питания).

Примечание: для рассмотренного логического элемента логическая «1» на входе будет, если вход никуда не подключен или подключен к плюсовому выводу источника питания.

На рисунке 1.7,б приведена схема простого и удобного в работе стенда для исследования диодно-резистивного логического элемента 2И. Светодиоды VD3 – VD5 являются индикаторами логических сигналов на входах и выходе логического элемента. Вольтметр V позволяет определить напряжения логической единицы и логического нуля. Для диодно-резистивного логического элемента 2И напряжение логического нуля на выходе примерно 0,7-0,8 В, а напряжение логической единицы чуть меньше напряжения на зажимах источника питания (определяется соотношением сопротивлений резистора R1 и нагрузки).

На рисунках 1.8,а и 1.8,б приведены схемы для исследования диодно-резистивного логического элемента 2ИЛИ. Для этого элемента напряжение логического нуля на выходе равно 0 В, а напряжение логической единицы равно напряжению питания минус 0,7-0,8 В.

Следующим этапом совершенствования элементной базы цифровой техники было создание логических элементов диодно-транзисторной логики.

Рассмотрим принципиальную схему логического элемента 2И-НЕ диодно-транзисторной логики (рис. 1.9,а).

Для понимания принципа работы логического элемента 2И-НЕ диодно-транзисторной логики необходимо знать, какой вид имеет зависимость тока коллектора транзистора от напряжения база-эмиттер при постоянном напряжении эмиттер- коллектор. Эта характеристика имеет примерно такой же вид, как и прямая ветвь вольтамперной характеристики полупроводникового диода. Для кремниевых транзисторов при напряжении база-эмиттер (в прямом направлении) менее 0,5 В ток в цепи коллектор-эмиттер практически равен нулю при любых допустимых напряжениях коллектор-эмиттер (транзистор закрыт, сопротивление между коллектором и эмиттером закрытого транзистора VТ1 может достигать единиц МОм). При незначительном увеличении напряжения база-эмиттер (в прямом направлении) более 0,5 В ток коллектора значительно увеличивается, говорят, что транзистор открывается.

Диоды VD1, VD2 и резистор R1 (рис. 1.9,а) образуют логический элемент 2И. Роль инвертора выполняет транзистор VT1. Если транзистор закрыт, то ток в цепи: плюс источника питания, резистор R2, коллектор-эмиттер транзистора VT1, минус источника питания не протекает и напряжение между эмиттером и коллектором транзистора будет равно напряжению на зажимах источника питания. Диоды VД3, VД4 необходимы для надежного закрытия транзистора VТ1, когда хотя бы на одном из входов элемента было напряжение логического нуля.

Если на обоих входах Х1, Х2 присутствуют сигналы логических единиц, транзистор VT1 открывается током базы, протекающим по цепи: плюс источника питания, резистор R1, диоды VD3, VD4, переход база-эмиттер транзистора VT1, минус источника. На выходе элемента будет напряжение 0,1-0,2 В, что соответствует логическому нулю.

На рисунке 1.9,б приведен вариант логического элемента 2И-НЕ на транзисторах. Инвертор на транзисторе VT1 не обеспечивает большую нагрузочную способность, поэтому в качестве инверторов применяют более сложные схемы. Сложный инвертор в микросхемах транзисторно-транзисторной логики будет рассмотрен чуть позже. Сейчас остановимся на принципе работы инверторов, схемы которых приведены на рисунке 1.10.

Рассмотрим делитель напряжения (делитель напряжения источника питания) образованного резистором R3 и цепью коллектор-эмиттер транзистора VТ1 (рис.1.10,а). Если на входе элемента логическая единица (подвижный контакт переключателя SA1 в верхнем положении), то транзистор VT1 открыт и в его коллекторной цепи протекает ток. Напряжение между коллектором и эмиттером транзистора составляет десятые доли вольта (не более 0,4 В). При логическом нуле на входе элемента транзистор закрыт и напряжение на выходе элемента равно напряжению питания, что соответствует логической единице.

На рисунках 1.10,б и 1.10,в приведены схемы инверторов с использованием полевых транзисторов. Напомним устройство и принцип действия полевых транзисторов. Существуют следующие виды полевых транзисторов: полевые транзисторы с управляющим p-n переходом, полевые транзисторы с изолированным затвором со встроенным каналом, полевые транзисторы с изолированным затвором с индуцированным каналом.

Полевые транзисторы называются также униполярными, одноканальными. Полевой транзистор в отличие от биполярного имеет большое входное сопротивление по цепи управления. Ток в выходной цепи полевого транзистора управляется напряжением, в то время как в биполярном транзисторе ток в выходной цепи транзистора управляется током во входной цепи транзистора. Таким образом, мощность управления в полевом транзисторе значительно меньше, чем в биполярном.

Полевой транзистор имеет 3 вывода: исток, сток, затвор. Исток – это вывод полевого транзистора, от которого основные носители заряда идут в канал. Сток – это вывод полевого транзистора, к которому идут основные носители заряда из канала. Затвор – это вывод полевого транзистора, на который подается управляющее напряжение относительно истока или относительно стока.

Наибольшее распространение имеют схемы включения транзистора с общим истоком, когда управляющее напряжение подается на затвор относительно истока.

В вычислительной технике в качестве электронных ключей широко используются полевые транзисторы с изолированным затвором с индуцированным каналом. Рассмотрим устройство и принцип действия полевого транзистора с изолированным затвором с индуцированным каналом n-типа (рис. 1.11). В полупроводнике p-типа сделаны два кармана с проводимостью n-типа. Знак n+ указывает на большую концентрацию электронов, что делается для уменьшения сопротивлений выводов стока и истока. Металлический затвор изолирован от кристалла полупроводника.

При напряжении затвор-исток, равном нулю, в цепи сток-исток ток не протекает при любых допустимых напряжениях сток-исток, так как образуются два p-n перехода, причем верхний подключен в обратном направлении.

Подадим на затвор относительно истока положительный потенциал. В полупроводниках p-типа имеются неосновные носители заряда (электроны). Рассмотрим движение электронов и дырок в слое полупроводника p-типа, прилежащем к затвору. Для упрощения рассмотрения соединим область p-типа с выводом истока. Под действием электрического поля, обусловленного наличием напряжения затвор – исток, дырки будут двигаться вправо, а электроны влево, т.е. в полупроводнике в приграничной к затвору области концентрация дырок уменьшается, а концентрация электронов увеличивается. При определенном напряжении затвор-исток в указанной области концентрация электронов станет больше концентрации дырок, наступит инверсия проводимости, т.е. в приграничной к затвору области появится слой полупроводника n-типа. В этом случае в цепи сток-исток протекает ток, т.к. между выводами стока и истока появился канал n-типа. Этот канал называется индуцированным (наведенным).

Для понимания принципа работы логических элементов на полевых транзисторах необходимо знать, что собой представляет стоко-затворная характеристика полевого транзистора. Стоко-затворная характеристика полевого транзистора в схеме включения с общим истоком (исток является общим для входной и выходной цепи) – это зависимость тока стока от напряжения затвор-исток при постоянном напряжении сток-исток. Эта характеристика полевого транзистора с изолированным затвором с индуцированным каналом n-типа приведена на рисунке 1.12. Особенности стоко-затворных характеристик полевых транзисторов с изолированным затвором с индуцированным каналом позволяют использовать эти транзисторы в качестве электронных ключей. Сравним основные характеристики электронного ключа на полевом транзисторе с характеристиками механического ключа. Сопротивление разомкнутого механического ключа можно считать бесконечно большим (пока не наступит электрический пробой), сопротивление ключа на полевом транзисторе порядка 10 МОм. Когда контакты механического ключа замкнуты сопротивление между контактами составляет сотые доли ома, для такого же состояния полевого транзистора сопротивление между стоком и истоком сотни Ом.

Если на входе инвертора, схема которого приведена на рисунке 1.10,б, напряжение логической единицы, то сопротивление между выводами сток и исток транзистора мало. Сопротивление резистора R1 выбирают значительно больше сопротивления между стоком и истоком открытого полевого транзистора и, следовательно, напряжение на выходе элемента будет близко к нулю вольт. При логическом нуле на входе логического элемента НЕ полевой транзистор будет закрыт, и на выходе элемента будет напряжение, примерно равное напряжению источника питания. Это обусловлено тем, что сопротивление резистора R1 выбирают во много раз меньше сопротивления между стоком и истоком закрытого транзистора.

Рассмотрим принцип работы инвертора (логического элемента НЕ) КМОП (комплиментарный, металл, окисел, полупроводник) структуры (рис. 1.10,в). Комплиментарный означает дополняющий друг друга по типу проводимости. Микросхемы КМОП имеют транзисторы как с каналом p-типа, так и с каналом n-типа. Учтем, что сопротивление между выводами сток-исток открытого транзистора – 200-300 Ом, а сопротивление между выводами сток-исток закрытого транзистора более 10 МОм.

Выберем напряжение питания 9 В. Пусть на вход Х подано напряжение логического «0», тогда транзистор VТ2 будет закрыт, а транзистор VТ1 открыт, так как потенциал затвора транзистора VТ1 относительно истока этого же транзистора равен минус 9В. На выходе элемента логическая единица.

Подадим на вход Х напряжение, соответствующее логической единице. Для рассмотренного случая это + 9 В относительно общего провода. В этом случае транзистор VТ2 будет открыт, а транзистор VТ1 – закрыт и на выходе элемента будет напряжение логического нуля.

Рассмотрим основные параметры, которыми характеризуются цифровые микросхемы.

Помехоустойчивость Uп, макс – наибольшее значение напряжения помехи на входе микросхемы, при котором еще не происходит изменения уровней ее выходного напряжения.

Напряжение логической единицы U1 – значение высокого уровня напряжения для “положительной” логики и значение низкого уровня напряжения для “отрицательной” логики.

Напряжение логического нуля U0 – значение низкого уровня напряжения для “положительной” логики и значение высокого уровня напряжения для “отрицательной” логики.

Пороговое напряжение логической единицы U1пор – наименьшее значение высокого уровня напряжения для “положительной” логики или наибольшее значение низкого уровня напряжения для “отрицательной” логики на входе микросхемы, при котором она переходит из одного устойчивого состояния в другое.

Пороговое напряжение логического нуля U0пор – наибольшее значение низкого уровня напряжения для “положительной” логики или наименьшее значение высокого уровня напряжения для “отрицательной” логики на входе микросхемы, при котором она переходит из одного устойчивого состояния в другое.

Входной ток логической единицы I1вх – измеряется при заданном значении напряжения логической единицы.

Входной ток логического нуля I0вх – измеряется при заданном значении напряжения логического нуля.

Выходной ток логической единицы I1вых – измеряется при заданном значении напряжения логической единицы.

Выходной ток логического нуля I0вых– измеряется при заданном значении напряжения логического нуля.

Ток потребления в состоянии логической единицы I1пот – значение тока, потребляемого микросхемой от источников питания при логических единицах на выходах всех элементов.

Ток потребления в состоянии логического нуля I0пот – значение тока, потребляемого микросхемой от источников питания при логических нулях на выходах всех элементов.

Средний ток потребления Iпот. ср. – значение тока, равное полусумме токов, потребляемых цифровой микросхемой от источников питания в двух устойчивых различных состояниях.

Потребляемая мощность в состоянии логической единицы Р1пот – значение мощности, потребляемой микросхемой от источника питания при логических единицах на выходах всех элементов.

Потребляемая мощность в состоянии логического нуля Р0пот – значение мощности, потребляемой микросхемой от источника питания при логических нулях на выходах всех элементов.

Средняя потребляемая мощность Рпот. ср.– полусумма мощностей, потребляемых микросхемой от источников питания в двух устойчивых различных состояниях.

Время перехода интегральной микросхемы из состояния логической единицы в состояние логического нуля t1,0 – интервал времени, в течение которого напряжение на выходе микросхемы переходит от напряжения логической единицы к напряжению логического нуля, измеренный на уровнях напряжения 0,1 и 0,9 от амплитуды импульса.

Время перехода интегральной микросхемы из состояния логического нуля в состояние логической единицы t0,1 – интервал времени, в течение которого напряжение на выходе микросхемы переходит от напряжения логического нуля к напряжению логической единицы, измеренный на уровнях напряжения 0,1 и 0,9 от амплитуды импульса.

Время задержки распространения сигнала при включении t1,0зд, р – интервал времени между входным и выходным импульсами при переходе напряжения на выходе микросхемы от напряжения логической единицы к напряжению логического нуля, измеренный на уровне 0,5 амплитуды.

Время задержки распространения сигнала при выключении t0,1зд, р – интервал времени между входным и выходным импульсами при переходе напряжения на выходе микросхемы от логического нуля к логической единицы, измеренный на уровне 0,5 амплитуды.

Среднее время задержки распространения сигнала tзд, р.с.– интервал времени, равный полусумме времени задержки распространения сигнала при включении и выключении цифровой микросхемы.

Коэффициент объединения по входу Коб – число входов микросхемы, по которым реализуется логическая функция.

Коэффициент разветвления по выходу Краз – число единичных нагрузок, которые можно одновременно подключить к выходу микросхемы (единичной нагрузкой является один вход основного логического элемента данной серии интегральных микросхем).

Коэффициент объединения по выходу Коб.вых – число соединяемых между собой выходов интегральной микросхемы, при котором обеспечивается реализация соответствующей логической операции.

Сопротивление нагрузки Rн – значение активного сопротивления нагрузки, подключаемой к выходу интегральной микросхемы, при котором обеспечивается заданное значение выходного напряжения (выходного тока) или заданное усиление.

Емкость нагрузки Сн – максимальное значение емкости, подключенной к выходу интегральной микросхемы, при котором обеспечиваются заданные частотные и иные параметры.

Синхронизация работы отдельных узлов ЭВМ и других устройств цифровой техники осуществляется периодическими последовательностями прямоугольных импульсов напряжения. Импульсом напряжения называют отклонение напряжения от первоначального значения в течение короткого промежутка времени. Последовательность импульсов, мгновенные значения которых повторяются через равные промежутки времени, называют периодической последовательностью импульсов. Участок импульса, на котором происходит изменение напряжения от начального уровня до конечного, называют фронтом импульса, а участок, на котором напряжение возвращается к исходному уровню, называется срезом импульса. Длительностью фронта импульса считают время нарастания напряжения от 0,1 Uм до 0,9 Uм, а длительностью среза – время изменения напряжения от 0,9 Uм до 0,1 Uм, где Uм – амплитуда импульса. Когда говорят о длительности импульса, то необходимо указывать, на каком уровне от амплитуды импульса проводились измерения: на уровне 0,1 Uм или 0,5 Uм. Частота следования импульсов – это число импульсов в одну секунду. Период следования импульсов – это минимальное время, через которое повторяются мгновенные значения напряжения. Интервал времени между окончанием одного импульса и началом следующего называется паузой. Величину, равную отношению периода следования импульсов к длительности импульса, называют скважностью импульсов. Периодическая последовательность прямоугольных импульсов при скважности 2 называется меандром. Прямоугольный импульс напряжения иногда рассматривают как совокупность двух перепадов напряжения. Перепады напряжения – это быстрые изменения напряжения между двумя уровнями. Перепад называют положительным, если напряжение изменяется от низкого уровня к высокому, и отрицательным, если напряжение изменяется от высокого уровня к низкому. Перепад напряжения, у которого длительность равна нулю, называется скачком напряжения.

На рисунке 1.13 показано, как определяется длительность фронта входного импульса tф, время перехода интегральной микросхемы из состояния логической единицы в состояние логического нуля t1,0, время перехода интегральной микросхемы из состояния логического нуля в состояние логической единицы t0,1, время задержки распространения при включении t1,0зд, р, время задержки распространения при выключении t0,1зд, р .

Что такое логический вентиль (AND, OR, XOR, NOT, NAND, NOR и XNOR)? Определение с сайта WhatIs.com

Логический вентиль – это устройство, которое действует как строительный блок для цифровых схем. Они выполняют основные логические функции, которые являются фундаментальными для цифровых схем. В большинстве электронных устройств, которые мы используем сегодня, есть логические вентили. Например, логические вентили могут использоваться в таких технологиях, как смартфоны, планшеты или устройства памяти.

В схеме логические вентили будут принимать решения на основе комбинации цифровых сигналов, поступающих с их входов.Большинство логических вентилей имеют два входа и один выход. Логические вентили основаны на булевой алгебре. В любой момент каждый терминал находится в одном из двух двоичных состояний: ложно или истинно . Ложь представляет 0, а истина представляет 1. В зависимости от типа используемого логического элемента и комбинации входов двоичный выход будет отличаться. Логический вентиль можно представить себе как выключатель света, в котором в одном положении выход выключен – 0, а в другом – включен – 1. Логические вентили обычно используются в интегральных схемах (IC).

Базовые логические вентилиСуществует семь основных логических вентилей: И, ИЛИ, ИСКЛЮЧАЮЩЕЕ ИЛИ, НЕ, И-НЕ, ИЛИ-ИЛИ и ИСКЛЮЧАЮЩЕЕ ИЛИ.

И | ИЛИ | XOR | НЕ | NAND | NOR | XNOR

Логический элемент И назван так потому, что, если 0 называется «ложным», а 1 называется «истинным», элемент действует так же, как логический оператор «И». На следующем рисунке и в таблице показаны символы схемы и логические комбинации для логического элемента И. (В символе входные клеммы слева, а выходные клеммы справа.) Выход «истина», когда оба входа «истина». В противном случае вывод будет «ложным». Другими словами, выход равен 1 только тогда, когда оба входа один И два равны 1.

И ворота

| Вход 1 | Ввод 2 | Выход |

| 1 | ||

| 1 | ||

| 1 | 1 | 1 |

Логический элемент ИЛИ получил свое название от того факта, что он ведет себя по образцу логического включающего “или”.«Выход -« истина », если один или оба входа равны« истина ». Если оба входа« ложь », то выход« ложь ». Другими словами, для выхода будет 1, по крайней мере, вход один ИЛИ два должны быть 1.

OR ворота

| Вход 1 | Ввод 2 | Выход |

| 1 | 1 | |

| 1 | 1 | |

| 1 | 1 | 1 |

Логический элемент XOR ( исключающее ИЛИ ) вентиль действует так же, как логическое «или / или».«Выходной сигнал« истина », если один из входов, но не оба, являются« истиной ». Выходной сигнал« ложь », если оба входа« ложь »или если оба входа« истина ». Другой способ взглянуть на это Схема должна следить за тем, чтобы на выходе было 1, если входы разные, и 0, если входы одинаковые.

Вентиль XOR

| Вход 1 | Ввод 2 | Выход |

| 1 | 1 | |

| 1 | 1 | |

| 1 | 1 |

Логический преобразователь , иногда называемый вентилем НЕ , чтобы отличать его от других типов электронных инверторных устройств, имеет только один вход.Он меняет логическое состояние на обратное. Если на входе 1, то на выходе 0. Если на входе 0, то на выходе 1.

Инвертор или НЕ вентильЛогический элемент И-НЕ работает как логический элемент И, за которым следует логический элемент НЕ. Он действует как логическая операция «и» с последующим отрицанием. На выходе будет «ложь», если оба входа «истина». В противном случае на выходе будет «истина».

вентиль NAND

| Вход 1 | Ввод 2 | Выход |

| 1 | ||

| 1 | 1 | |

| 1 | 1 | |

| 1 | 1 |

Логический элемент ИЛИ представляет собой комбинацию логического элемента ИЛИ, за которым следует инвертор.Его выход будет «истина», если оба входа «ложь». В противном случае вывод будет «ложным».

NOR ворота

| Вход 1 | Ввод 2 | Выход |

| 1 | ||

| 1 | ||

| 1 | ||

| 1 | 1 |

Логический элемент XNOR (исключающее ИЛИ) – это комбинированный вентиль XOR, за которым следует инвертор.Его вывод – «истина», если входы одинаковые, и «ложь», если входы разные.

Ворота XNOR

| Вход 1 | Ввод 2 | Выход |

| 1 | ||

| 1 | ||

| 1 | ||

| 1 | 1 | 1 |

Сложные операции могут выполняться с использованием комбинаций этих логических вентилей.Теоретически нет ограничений на количество ворот, которые могут быть объединены в одно устройство. Но на практике существует ограничение на количество ворот, которые могут быть упакованы в данное физическое пространство. Массивы логических вентилей находятся в цифровых ИС. По мере развития технологии ИС требуемый физический объем для каждого отдельного логического элемента уменьшается, и цифровые устройства того же или меньшего размера становятся способными выполнять все более сложные операции с постоянно увеличивающейся скоростью.

Состав логических вентилей

Высокий или низкий двоичные состояния представлены разными уровнями напряжения.Логическое состояние терминала может и обычно часто изменяется по мере того, как схема обрабатывает данные. В большинстве логических вентилей низкое состояние составляет приблизительно ноль вольт (0 В), а высокое состояние – приблизительно пять вольт положительного напряжения (+5 В).

Логические вентили могут быть выполнены из резисторов и транзисторов или диодов. Резистор обычно можно использовать как подтягивающий или понижающий резистор. Подтягивающие и понижающие резисторы используются, когда есть какие-либо неиспользуемые входы логического элемента для подключения к логическому уровню 1 или 0.Это предотвращает ложное переключение ворот. Подтягивающие резисторы подключены к Vcc (+ 5 В), а подтягивающие резисторы подключены к земле (0 В).

Обычно используются логические вентили TTL и CMOS. ИС TTL или транзисторно-транзисторной логики будут использовать биполярные переходные транзисторы типа NPN и PNP. КМОП, или дополнительные металл-оксидно-кремниевые ИС, построены из полевых транзисторов типа MOSFET или JFET. ИС TTL обычно обозначают как микросхемы серии 7400, в то время как ИС КМОП часто обозначают как микросхемы серии 4000.

Основные логические ворота с таблицами истинности