Ацп двойного интегрирования (интегрирующий ацп).

Упрощенная схема АЦП, работающего в два основных такта (АЦП двухтактного (двойного) интегрирования), приведена на рис. 7.13.

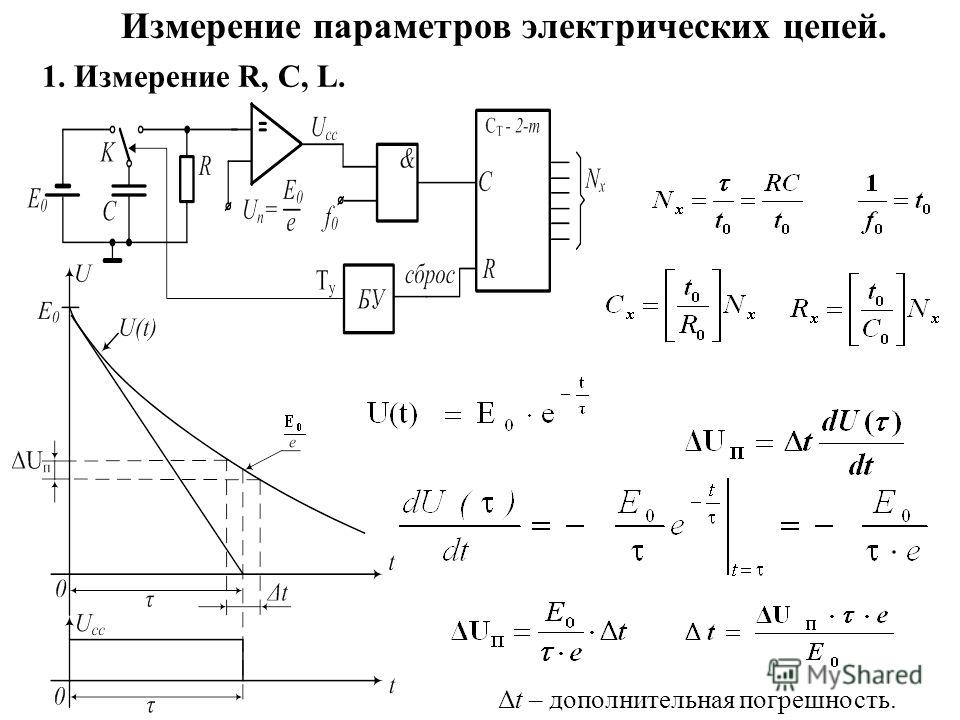

Преобразование проходит две стадии: стадию интегрирования и стадию счета. В начале первой стадии ключ S1 замкнут, а ключ S2 разомкнут. Интегратор И интегрирует входное напряжение Uвх. Время интегрирования входного напряжения t1

постоянно.

В качестве таймера используется счетчик с коэффициентом пересчета Kсч, так что:

(7.1)

К моменту окончания интегрирования выходное напряжение интегратора составляет

(7.2)

где Uвх.ср. – среднее за время t1 входное напряжение.

интегрирования ключ S1 размыкается, а ключ S2 замыкается и опорное напряжение Uоп поступает на вход интегратора. При этом выбирается опорное напряжение, противоположное по знаку входному напряжению. На стадии счета выходное напряжение интегратора линейно уменьшается по абсолютной величине, как показано на рис. 7.14. Стадия счета заканчивается, когда выходное напряжение интегратора переходит через нуль. При этом компаратор К переключается и счет останавливается.

Интервал времени, в котором проходит стадия счета, определяется уравнением

(7.3)

Подставив значение Uи(t1) из (7.2) в (7.3) с учетом того, что

(7.4)

где n

2 – содержимое счетчика после окончания стадии счета, получим результат (7. 5)

5)

Из этой формулы следует, что отличительной особенностью метода многотактного интегрирования является то, что ни тактовая частота, ни постоянная интегрирования RC не влияют на результат. Необходимо только потребовать, чтобы тактовая частота в течение времени t1+t2 оставалась постоянной. Это можно обеспечить при

использовании простого тактового генератора, поскольку существенные временные

или температурные дрейфы частоты происходят за время несопоставимо большее, чем время преобразования.

При выводе выражений (7.1)…(7.5) мы видели, что в окончательный результат входят не мгновенные значения преобразуемого напряжения, а только значения, усредненные за время

Способ двойного интегрирования позволяет хорошо подавлять сетевые помехи.

АЦП двойного

интегрирования относится к наиболее

медленно работающим преобразователям. Однако, высокая точность, низкий уровень

шумов и низкая стоимость делают их

незаменимыми для применения в щитовых

приборах, мультиметрах, цифровых

термометрах и т.п. Этому способствует

также то, что результаты преобразования

в интегрирующих АЦП часто представляются

в десятичном коде или же в удобном виде

для представления цифр десятичной

системы счисления.

Однако, высокая точность, низкий уровень

шумов и низкая стоимость делают их

незаменимыми для применения в щитовых

приборах, мультиметрах, цифровых

термометрах и т.п. Этому способствует

также то, что результаты преобразования

в интегрирующих АЦП часто представляются

в десятичном коде или же в удобном виде

для представления цифр десятичной

системы счисления.

АЦП многотактного

интегрирования имеют ряд недостатков.

Во-первых, нелинейность переходной

статической характеристики операционного

усилителя, на котором выполняют

интегратор, заметным образом сказывается

на интегральной нелинейности характеристики

преобразования АЦП высокого разрешения.

Для уменьшения влияния этого фактора

АЦП изготавливают многотактными.

Например, 13-разрядный AD7550 выполняет

преобразование в четыре такта. Другим

недостатком этих АЦП является то

обстоятельство, что интегрирование

входного сигнала занимает в цикле

преобразования только приблизительно

третью часть. Две трети цикла преобразователь

не принимает входной сигнал.

Эти недостатки во многом устранены в конструкции сигма-дельта АЦП

7.15).

7.15).Для формирования выходного кода такого преобразователя необходимо каким-либо образом преобразовать последовательность бит на выходе компаратора в виде

унитарного кода в последовательный или параллельный двоичный позиционный код.

В простейшем случае

это можно сделать с помощью двоичного

счетчика. При использовании двоичного

счетчика в качестве преобразователя

потока битов, поступающих с выхода

компаратора, необходимо выделять

фиксированный цикл преобразования,

длительность которого равна произведению Kсч fтакт.

После его окончания должно производиться

считывание результата, например, с

помощью регистра-защелки и обнуление

счетчика. В этом случае с точки зрения

помехоподавляющих свойств сигма-дельта

АЦП близки к АЦП многотактного

интегрирования. Более эффективно с этой

точки зрения применение в сигма-дельта

АЦП цифровых фильтров с конечной

длительностью переходных процессов.

Сравнение сигма-дельта АЦП с АЦП многотактного интегрирования показывает значительные преимущества первых. Прежде всего, линейность характеристики преобразования сигма-дельта АЦП выше, чем у АЦП многотактного интегрирования равной стоимости. Это объясняется тем, что интегратор сигма-дельта АЦП работает в значительно более узком динамическом диапазоне, и нелинейность переходной характеристики усилителя, на котором построен интегратор, сказывается значительно меньше. Емкость конденсатора интегратора у сигма-дельта АЦП значительно меньше (десятки пикофарад), так что этот конденсатор может быть изготовлен прямо на кристалле ИМС. Как следствие, сигма-дельта АЦП практически не имеет внешних элементов, что существенно сокращает площадь, занимаемую им на плате, и снижает уровень шумов.

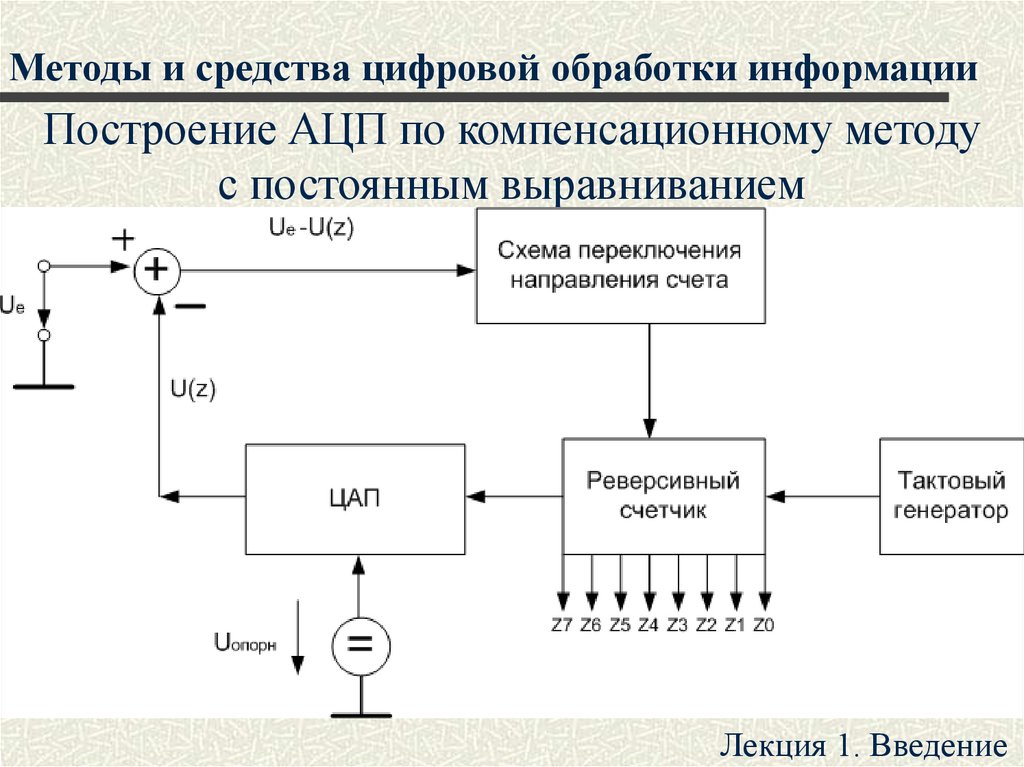

АЦП

дифференциального кодирования (рис. 7.16) содержат реверсивный

счётчик,

код с которого поступает на вспомогательный

ЦАП. Входной сигнал и сигнал со

вспомогательного ЦАП сравниваются на

компараторе.

АЦП дифференциального кодирования обычно являются хорошим выбором для оцифровки сигналов реального мира, так как большинство сигналов в физических системах не склонны к скачкообразным изменениям.

Рис. 7.16. АЦП дифференциального кодирования.

К- аналоговый компаратор, РС- реверсивный счетчик, ГТИ- генератор тактовых импульсов, ЦАП- цифро-аналоговый преобразователь.

АЦП двойного интегрирования (интегрирующий АЦП) — Студопедия

Поделись с друзьями:

Упрощенная схема АЦП, работающего в два основных такта (АЦП двухтактного (двойного) интегрирования), приведена на рис. 7.13.

Преобразование проходит две стадии: стадию интегрирования и стадию счета. В начале первой стадии ключ S1 замкнут, а ключ S2 разомкнут. Интегратор И интегрирует входное напряжение Uвх. Время интегрирования входного напряжения t1

постоянно.

В качестве таймера используется счетчик с коэффициентом пересчета Kсч, так что:

(7.1)

К моменту окончания интегрирования выходное напряжение интегратора составляет

(7.2)

где Uвх.ср . – среднее за время t1 входное напряжение. После окончания стадии

После окончания стадии

интегрирования ключ S1 размыкается, а ключ S2 замыкается и опорное напряжение Uоп поступает на вход интегратора. При этом выбирается опорное напряжение, противоположное по знаку входному напряжению. На стадии счета выходное напряжение интегратора линейно уменьшается по абсолютной величине, как показано на рис. 7.14. Стадия счета заканчивается, когда выходное напряжение интегратора переходит через нуль. При этом компаратор К переключается и счет останавливается.

Интервал времени, в котором проходит стадия счета, определяется уравнением

(7.3)

Подставив значение U

(7.4)

где n2 – содержимое счетчика после окончания стадии счета, получим результат

(7.5)

Из этой формулы следует, что отличительной особенностью метода многотактного интегрирования является то, что ни тактовая частота, ни постоянная интегрирования RC не влияют на результат. Необходимо только потребовать, чтобы тактовая частота в течение времени t1+t2 оставалась постоянной. Это можно обеспечить при

Необходимо только потребовать, чтобы тактовая частота в течение времени t1+t2 оставалась постоянной. Это можно обеспечить при

использовании простого тактового генератора, поскольку существенные временные

или температурные дрейфы частоты происходят за время несопоставимо большее, чем время преобразования.

При выводе выражений (7.1)…(7.5) мы видели, что в окончательный результат входят не мгновенные значения преобразуемого напряжения, а только значения, усредненные за время t1. Поэтому переменное напряжение ослабляется тем сильнее, чем выше его частота.

Способ двойного интегрирования позволяет хорошо подавлять сетевые помехи.

АЦП двойного интегрирования относится к наиболее медленно работающим преобразователям. Однако, высокая точность, низкий уровень шумов и низкая стоимость делают их незаменимыми для применения в щитовых приборах, мультиметрах, цифровых термометрах и т.п. Этому способствует также то, что результаты преобразования в интегрирующих АЦП часто представляются в десятичном коде или же в удобном виде для представления цифр десятичной системы счисления.

Понравилась статья? Добавь ее в закладку (CTRL+D) и не забудь поделиться с друзьями:

архитектур АЦП | Аналоговые устройства

Скачать PDF

Abstract

Интегрирующие аналого-цифровые преобразователи (АЦП) обеспечивают аналого-цифровое преобразование с высоким разрешением и хорошим подавлением шума. Эти АЦП идеально подходят для оцифровки сигналов с узкой полосой пропускания и используются в таких приложениях, как цифровые мультиметры и панельные измерители. Они часто включают в себя драйверы ЖК-дисплеев или светодиодов и могут использоваться автономно без хоста микроконтроллера. В следующей статье объясняется, как работают интегрированные АЦП. Обсуждения включают одно-, двух- и многоскатные преобразования. Кроме того, будет обсуждаться углубленный анализ интегрирующей архитектуры. Наконец, сравнение с другими архитектурами АЦП поможет понять и выбрать интегрирующиеся АЦП.

Наконец, сравнение с другими архитектурами АЦП поможет понять и выбрать интегрирующиеся АЦП.

Встроенные аналого-цифровые преобразователи (АЦП) обеспечивают высокое разрешение и могут обеспечить хорошее подавление частоты линии и шумов. Начав с вездесущего 7106, эти преобразователи существуют уже довольно давно. Интегрирующая архитектура обеспечивает новый, но простой подход к преобразованию аналогового сигнала с узкой полосой пропускания в его цифровое представление. Преобразователи этого типа часто включают встроенные драйверы для ЖК-дисплеев или светодиодных дисплеев и используются во многих портативных приборах, включая цифровые панельные измерители и цифровые мультиметры.

Однотактная архитектура АЦП

Простейшая форма интегрирующего АЦП использует архитектуру с одним наклоном (рис. 1а и 1б). Здесь интегрируется неизвестное входное напряжение, и значение сравнивается с известным эталонным значением. Время, необходимое интегратору для отключения компаратора, пропорционально неизвестному напряжению (T INT /V IN ). В этом случае известное опорное напряжение должно быть стабильным и точным, чтобы гарантировать точность измерения.

В этом случае известное опорное напряжение должно быть стабильным и точным, чтобы гарантировать точность измерения.

Рис. 1а и 1б. Односкатная архитектура.

Одним из недостатков этого подхода является то, что точность также зависит от допусков значений R и C интегратора. Таким образом, в производственной среде небольшие различия в значениях каждого компонента изменяют результат преобразования и затрудняют достижение воспроизводимости измерений. Чтобы преодолеть эту чувствительность к значениям компонентов, используется двухскатная интегрирующая архитектура.

Двухтактная архитектура АЦП

Двухтактный АЦП (DS-ADC) интегрирует неизвестное входное напряжение (V IN ) в течение фиксированного периода времени (T INT ), затем «деинтегрирует» (T DEINT ) с использованием известного опорное напряжение (V REF ) в течение переменного периода времени (см. рис. 2).

Рис. 2. Двухскатная интеграция.

2. Двухскатная интеграция.

Основное преимущество этой архитектуры по сравнению с односкатной состоит в том, что окончательный результат преобразования нечувствителен к ошибкам в значениях компонентов. То есть любая ошибка, вызванная значением компонента во время цикла интегрирования, будет устранена во время фазы деинтеграции. В форме уравнения:

Vin × T INT = V REF × T DEINT

или

T DEINT = T INT × (V IN / V REF )

Из этого уравнения мы видим, что время деинтеграции пропорционально отношению V IN / V REF . Полная блок-схема преобразователя с двойным наклоном показана на рисунке 3.

Рис. 3. Преобразователь с двойным наклоном.

Например, чтобы получить 10-битное разрешение, вы должны интегрировать 1024 (2 10 ) тактовых циклов, затем деинтеграция до 1024 тактовых циклов (что дает максимальное преобразование 2 × 2 10 циклов). Для большего разрешения увеличьте количество тактов. Этот компромисс между временем преобразования и разрешением присущ этой реализации. Можно ускорить время преобразования для заданного разрешения при умеренных изменениях схемы. К сожалению, все улучшения смещают часть точности на согласование, внешние компоненты, инжекцию заряда и т. д. Другими словами, все методы ускорения имеют больший бюджет ошибок. Даже в простом преобразователе на рис. 1 необходимо учитывать множество потенциальных источников ошибок (подавление источника питания [PSR], подавление синфазного сигнала [CMR], конечное усиление, проблемы перенапряжения, насыщение интегратора, скорость компаратора, колебания компаратора). , «переворот», диэлектрическая абсорбция, ток утечки конденсатора, паразитная емкость, инжекция заряда и т. д.).

Для большего разрешения увеличьте количество тактов. Этот компромисс между временем преобразования и разрешением присущ этой реализации. Можно ускорить время преобразования для заданного разрешения при умеренных изменениях схемы. К сожалению, все улучшения смещают часть точности на согласование, внешние компоненты, инжекцию заряда и т. д. Другими словами, все методы ускорения имеют больший бюджет ошибок. Даже в простом преобразователе на рис. 1 необходимо учитывать множество потенциальных источников ошибок (подавление источника питания [PSR], подавление синфазного сигнала [CMR], конечное усиление, проблемы перенапряжения, насыщение интегратора, скорость компаратора, колебания компаратора). , «переворот», диэлектрическая абсорбция, ток утечки конденсатора, паразитная емкость, инжекция заряда и т. д.).

Многоуровневые интегрирующие АЦП

Нормальный предел разрешения двухполосной архитектуры основан на скорости компаратора ошибок (при этом предполагается, что ошибки по постоянному току системы были сведены к минимуму за счет проектирования с высоким коэффициентом усиления по постоянному току, а также высокими значениями PSR и CMR буфера, интегратора). и компаратор). Для 20-битного преобразователя (примерно 1 часть на миллион) и тактовой частоты 1 МГц время преобразования составит около 2 секунд. Скорость линейного изменения, наблюдаемая компаратором ошибок, составляет около 2 В/10 6 разделить на 1 микросекунду. Это примерно 2 мкВ/мкс. При такой малой скорости нарастания компаратор ошибок позволил бы интегратору выйти далеко за пределы точки срабатывания на значительную величину. Этот выброс (измеряемый на выходе интегратора) называется «остатком». Этот метод грубой силы вряд ли позволит получить 20-битный преобразователь.

и компаратор). Для 20-битного преобразователя (примерно 1 часть на миллион) и тактовой частоты 1 МГц время преобразования составит около 2 секунд. Скорость линейного изменения, наблюдаемая компаратором ошибок, составляет около 2 В/10 6 разделить на 1 микросекунду. Это примерно 2 мкВ/мкс. При такой малой скорости нарастания компаратор ошибок позволил бы интегратору выйти далеко за пределы точки срабатывания на значительную величину. Этот выброс (измеряемый на выходе интегратора) называется «остатком». Этот метод грубой силы вряд ли позволит получить 20-битный преобразователь.

Вместо этого мы могли бы преобразовать первые 10 старших битов (один цикл интегрирования/деинтегрирования), а затем усилить остаток на 2 5 , затем снова деинтегрируйте, затем амплифицируйте остаток на 2 5 , а затем дезинтегрируйте в последний раз. Если остаток правильно амплифицирован (т. е. инжекция заряда и другие ошибки невелики), этот метод может быть весьма эффективным для увеличения разрешения и сокращения времени преобразования. Обратите внимание, что фактические показания: (Сумма времени первого распада × 2 10 ) минус (сумма времени второго распада × 2 5 ) плюс (сумма времени третьего распада × 2 0 ).

Обратите внимание, что фактические показания: (Сумма времени первого распада × 2 10 ) минус (сумма времени второго распада × 2 5 ) плюс (сумма времени третьего распада × 2 0 ).

Углубленный анализ архитектуры

Авто-ноль

В нашем предыдущем анализе мы исходили из идеального преобразователя. На практике схема будет иметь смещение, которое дрейфует со временем и температурой. Чтобы свести к минимуму это влияние, преобразователи с двойным наклоном используют фазу с автоматическим обнулением. Во время автообнуления измеряется и сохраняется на внешнем конденсаторе напряжение смещения буферного операционного усилителя, интегратора и компаратора. Таким образом, цикл интегрирования фактически начинается с обнуления смещения.

Отклонение линии

Одним из наиболее привлекательных свойств DS-ADC является подавление нежелательных сигналов 50/60 Гц. Если цикл интегрирования длится ровно время T , то все частоты N × 1/T полностью отбрасываются (теоретически). Таким образом, для T = 100 мс частоты, кратные 10 Гц, отбрасываются. Фактическое ограничение этого отклонения связано с конечным размахом интегратора (поскольку мы не хотим, чтобы он насыщался) и неизбежным «колебанием» самой частоты 50/60 Гц. В течение длительного периода времени 50/60 Гц можно усреднить, чтобы получить чрезвычайно точную временную базу. Однако через короткое время он дрожит на несколько герц. Это ограничит фактическое подавление линии примерно до 40-60 дБ.

Таким образом, для T = 100 мс частоты, кратные 10 Гц, отбрасываются. Фактическое ограничение этого отклонения связано с конечным размахом интегратора (поскольку мы не хотим, чтобы он насыщался) и неизбежным «колебанием» самой частоты 50/60 Гц. В течение длительного периода времени 50/60 Гц можно усреднить, чтобы получить чрезвычайно точную временную базу. Однако через короткое время он дрожит на несколько герц. Это ограничит фактическое подавление линии примерно до 40-60 дБ.

Анализ бюджета ошибок

DS-ADC имеют несколько членов в бюджете ошибок. В первую очередь это связано с высокой точностью, на которую они рассчитаны.

Усилители должны иметь высокое подавление синфазного сигнала (CMR), подавление источника питания (PSR) и высокое конечное усиление (чтобы буфер мог адекватно управлять своей резистивной нагрузкой, а интегратор — емкостной нагрузкой). Полномасштабный интегральный ток [V IN (макс.) / R INT ] обычно составляет 20-100 микроампер. Это значение представляет собой компромисс между низким энергопотреблением и преодолением эффектов тока утечки печатной платы. Некоторые инженеры пытались использовать усилители класса B для этих операционных усилителей, чтобы сэкономить ток питания. Однако необходимо тщательно проанализировать неизбежное перекрестное искажение, так как оно может быть больше, чем все другие ошибки.

Это значение представляет собой компромисс между низким энергопотреблением и преодолением эффектов тока утечки печатной платы. Некоторые инженеры пытались использовать усилители класса B для этих операционных усилителей, чтобы сэкономить ток питания. Однако необходимо тщательно проанализировать неизбежное перекрестное искажение, так как оно может быть больше, чем все другие ошибки.

Компаратор должен реагировать в течение доли тактового цикла на довольно слабый сигнал. Сигнал зависит от скорости нарастания во время деинтеграции (I / C = V REF / (R INT × C INT )). По мере увеличения разрешения этот сигнал может быть меньше милливольта/микросекунды. Непреднамеренный гистерезис должен быть сведен к минимуму, так как он вызывает «переворот». Переворот определяется как разница между почти положительным значением полной шкалы и почти отрицательным значением полной шкалы. Параметр обычно указывается в технических характеристиках DS и проверяется простым приложением полного положительного напряжения, затем приложением полного отрицательного напряжения, а затем суммированием результатов.

Один из наиболее полезных методов снижения погрешности заключается в замыкании входных клемм и выполнении измерения. Если в конструкции АЦП в качестве накопителей используются прямые/обратные счетчики, то погрешность измерения можно легко вычесть из результата преобразования входного сигнала (V IN ). Этот метод не всегда приемлем, поскольку он удваивает время преобразования, если калибровка выполняется перед каждым преобразованием. Однако он может исправить гораздо больше ошибок, чем просто ошибку смещения (например, задержку внутреннего компаратора (ов), инжекцию заряда и т. д.).

Внешние компоненты

Пользователь должен снабдить микросхему резистором (для преобразования входного напряжения в ток), конденсатором интегратора и конденсатором автонуля. Оба конденсатора нуждались в исключительной DA (диэлектрической абсорбции). Модель конденсатора интегратора, показанная на рис. 4, показывает конденсатор, состоящий из высокоомных компонентов серии R’C’ (вызванных релаксацией диэлектрика) параллельно с основным конденсатором. Эти последовательные RC-элементы заставляют конденсатор вести себя так, как если бы у него была «память». Например, предположим, что конденсатор был заряжен до 1000 вольт в течение неопределенного времени, а затем закорочен на 10 постоянных времени (SW1 переместился в положение 1). Когда переключатель перемещается в положение 3, конденсатор «расслабляется» до напряжения, отличного от нуля вольт, из-за эффекта «памяти». Это явление в конечном счете ограничивает точность, разрешение и переходную характеристику преобразователя.

Эти последовательные RC-элементы заставляют конденсатор вести себя так, как если бы у него была «память». Например, предположим, что конденсатор был заряжен до 1000 вольт в течение неопределенного времени, а затем закорочен на 10 постоянных времени (SW1 переместился в положение 1). Когда переключатель перемещается в положение 3, конденсатор «расслабляется» до напряжения, отличного от нуля вольт, из-за эффекта «памяти». Это явление в конечном счете ограничивает точность, разрешение и переходную характеристику преобразователя.

Рис. 4. Модель интегрирующего конденсатора.

по сравнению с другими архитектурами АЦП

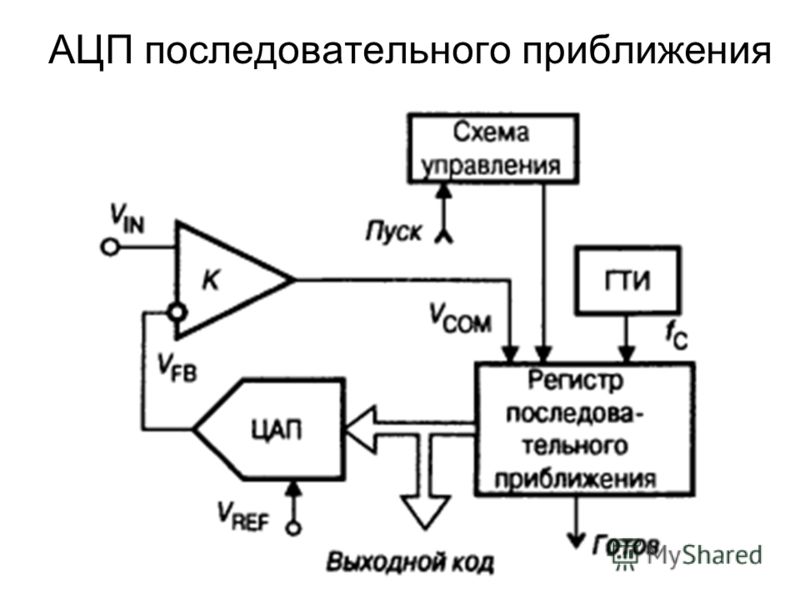

Теперь мы рассмотрим интегрирующий АЦП в сравнении с SAR и сигма-дельта АЦП. Архитектуры флэш-памяти и конвейерных АЦП будут игнорироваться, поскольку они редко (если вообще когда-либо) конкурируют с более медленной интегрирующей архитектурой.

по сравнению с последовательным приблизительным регистром (SAR) ADC

Как SAR, так и интегрированная архитектура хорошо работают с сигналами с низкой пропускной способностью. АЦП последовательного приближения имеет гораздо более широкий диапазон полосы пропускания, поскольку они легко могут преобразовывать сигналы на скоростях в низком диапазоне МГц, в то время как интегрирующая архитектура ограничена примерно 100 выборками в секунду. Обе архитектуры имеют низкое энергопотребление. Поскольку АЦП последовательного приближения могут отключаться между преобразованиями, эффективное энергопотребление аналогично интегрирующему АЦП (первого порядка). Самая большая разница между двумя преобразователями заключается в подавлении синфазного сигнала и количестве необходимых внешних компонентов. Поскольку пользователь устанавливает время интегрирования, нежелательные частоты, такие как 50 Гц или 60 Гц, могут быть эффективно вырезаны. АЦП SAR не позволяет этого. Кроме того, поскольку интегрирование в основном представляет собой метод усреднения, интегрирующий АЦП обычно имеет лучшие шумовые характеристики. АЦП последовательного приближения имеет шум на границе кода, и паразитный шум, который преобразуется, будет иметь более неблагоприятное воздействие на АЦП последовательного приближения, чем на интегрирующий АЦП.

АЦП последовательного приближения имеет гораздо более широкий диапазон полосы пропускания, поскольку они легко могут преобразовывать сигналы на скоростях в низком диапазоне МГц, в то время как интегрирующая архитектура ограничена примерно 100 выборками в секунду. Обе архитектуры имеют низкое энергопотребление. Поскольку АЦП последовательного приближения могут отключаться между преобразованиями, эффективное энергопотребление аналогично интегрирующему АЦП (первого порядка). Самая большая разница между двумя преобразователями заключается в подавлении синфазного сигнала и количестве необходимых внешних компонентов. Поскольку пользователь устанавливает время интегрирования, нежелательные частоты, такие как 50 Гц или 60 Гц, могут быть эффективно вырезаны. АЦП SAR не позволяет этого. Кроме того, поскольку интегрирование в основном представляет собой метод усреднения, интегрирующий АЦП обычно имеет лучшие шумовые характеристики. АЦП последовательного приближения имеет шум на границе кода, и паразитный шум, который преобразуется, будет иметь более неблагоприятное воздействие на АЦП последовательного приближения, чем на интегрирующий АЦП.

Интегрирующий АЦП легко преобразует сигналы низкого уровня. Поскольку линейное изменение интегратора задается значением интегрирующего резистора, довольно легко согласовать диапазон входного сигнала с АЦП. Большинство РСА ожидают большой сигнал на входе АЦП. Таким образом, для слабых (т. е. мВ) сигналов требуется предварительная схема согласования сигналов.

Для интегрирующего АЦП требуется больше внешних компонентов, чем для SAR. Для SAR обычно требуется пара обходных конденсаторов. Для интегрирующего АЦП требуются хорошие интегрирующие и опорные конденсаторы, а также интегрирующий резистор с малым дрейфом. Кроме того, опорное напряжение часто имеет нестандартное значение (например, 100 мВ или 409 мВ).0,6 мВ), поэтому часто используется схема делителя опорного напряжения.

по сравнению с сигма-дельта АЦП

Сигма-дельта АЦП использует передискретизацию для получения очень высокого разрешения. Он также допускает входную полосу пропускания в диапазоне низких МГц. Подобно интегрирующему АЦП, эта архитектура может иметь отличное подавление линии. Он также обеспечивает решение с очень низким энергопотреблением и позволяет преобразовывать сигналы низкого уровня. В отличие от интегрирующего АЦП, сигма-дельта не требует никаких внешних компонентов. Кроме того, он не требует настройки или калибровки благодаря своей цифровой архитектуре. Из-за характера передискретизации и того факта, что сигма-дельта включает в себя цифровой фильтр, фильтр сглаживания часто не требуется на входе. Преобразователи сигма-дельта обычно доступны с разрешением от 16 до 24 бит, в то время как интегрированные АЦП ориентированы на диапазон от 12 до 16 бит. Благодаря своей простой архитектуре и зрелости интегрированные АЦП довольно недороги, особенно на 12-разрядном уровне. Однако при 16 битах сигма-дельта также обеспечивает недорогое решение.

Подобно интегрирующему АЦП, эта архитектура может иметь отличное подавление линии. Он также обеспечивает решение с очень низким энергопотреблением и позволяет преобразовывать сигналы низкого уровня. В отличие от интегрирующего АЦП, сигма-дельта не требует никаких внешних компонентов. Кроме того, он не требует настройки или калибровки благодаря своей цифровой архитектуре. Из-за характера передискретизации и того факта, что сигма-дельта включает в себя цифровой фильтр, фильтр сглаживания часто не требуется на входе. Преобразователи сигма-дельта обычно доступны с разрешением от 16 до 24 бит, в то время как интегрированные АЦП ориентированы на диапазон от 12 до 16 бит. Благодаря своей простой архитектуре и зрелости интегрированные АЦП довольно недороги, особенно на 12-разрядном уровне. Однако при 16 битах сигма-дельта также обеспечивает недорогое решение.

АЦП с одним наклоном и двойным наклоном

В этом руководстве мы обсудим АЦП типа наклона или типа интеграции. В последнем уроке мы обсудили последовательное приближение и АЦП флэш-памяти. Существует два типа АЦП наклона, такие как одиночный наклон и двойной наклон. Во-первых, мы обсудим одинарную диаграмму, а после этого мы увидим работу интегрирующего АЦП с двойной характеристикой.

В последнем уроке мы обсудили последовательное приближение и АЦП флэш-памяти. Существует два типа АЦП наклона, такие как одиночный наклон и двойной наклон. Во-первых, мы обсудим одинарную диаграмму, а после этого мы увидим работу интегрирующего АЦП с двойной характеристикой.

АЦП с наклоном Введение

АЦП с одинарным и двойным наклоном представляют собой типы, которые оцифровывают аналоговые сигналы с использованием интегральных схем, а интегральные схемы разработаны с использованием операционных усилителей. В этом типе мы генерируем пилообразный сигнал, используя операционный усилитель в качестве интегратора. Выходной сигнал пилообразной формы сравнивается с аналоговым входным сигналом с помощью схемы компаратора для формирования цифрового выходного сигнала.

Они обладают высокой разрешающей способностью, но гораздо медленнее по скорости преобразования, чем другие аналого-цифровые преобразователи. Его основное применение в мультиметре. В статье рассказывается о работе одиночных и двойных АЦП, преимуществах, недостатках и приложениях.

АЦП с двойным наклоном предпочтительнее аналого-цифрового преобразователя с одним наклоном. Для ясного представления о двухтактном АЦП мы сначала изучим однофазный. Он состоит из интегратора и компаратора.

Входное напряжение подается на положительную клемму компаратора, в то время как опорное напряжение получается после интегрирования через интегратор. Оба напряжения сравниваются через компаратор. Входное напряжение является функцией времени t. Опорное напряжение продолжает интегрироваться до тех пор, пока выходное напряжение компаратора не станет равным входному напряжению.

Общее выходное напряжение интегратора задается как

VO=1/RC (-Vref) dt

В уравнении видно, что опорное напряжение отрицательно, поэтому наклон интегрированного выходного напряжения получается быть положительным.

Выходное напряжение интегратора в любой момент времени определяется как

VO=T*Vref/RC

В момент времени T выходное напряжение эквивалентно входному напряжению. Таким образом, мы можем сказать

Таким образом, мы можем сказать

Vin=T*Vref/RC

Поскольку опорное напряжение, резистор R и конденсатор C фиксированы для данного аналого-цифрового преобразователя, входное напряжение прямо пропорционально времени.

Принципиальная схема

Ниже приведена схема аналогово-цифрового преобразователя с одним наклоном:

Он состоит из интегратора, компаратора, вентиля И и счетчика, который дает нам двоичные выходы. Выход компаратора передается на вентиль И. Всякий раз, когда на выходе компаратора высокий уровень, что означает, что когда опорное напряжение меньше входного напряжения, тактовые импульсы передаются на счетчик через логический элемент И, и счетчик начинает счет.

Принцип работы

Перед преобразованием аналогового входа в двоичный выход счетчик обнуляется. Входное напряжение и интегрированное опорное напряжение подаются на компаратор. Когда начинается преобразование, исходное опорное напряжение меньше входного. На выходе компаратора высокий уровень и из-за этого на счетчик поступают тактовые импульсы, а счетчик работает и считает. Таким образом, когда интегральное опорное напряжение становится равным приложенному входному напряжению, компаратор меняет свое состояние с высокого на низкое. Выход логического элемента И становится низким, счетчик больше не получает тактовых импульсов и останавливает счет. Как бы то ни было, отсчет, имеющийся на счетчике, будет пропорционален входному напряжению.

Таким образом, когда интегральное опорное напряжение становится равным приложенному входному напряжению, компаратор меняет свое состояние с высокого на низкое. Выход логического элемента И становится низким, счетчик больше не получает тактовых импульсов и останавливает счет. Как бы то ни было, отсчет, имеющийся на счетчике, будет пропорционален входному напряжению.

Цепь также сопровождается переключателем, известным как Переключатель сброса. Он закрывается на короткое время, когда выход компаратора низкий, и гарантирует, что на конденсаторе нет остаточного заряда, чтобы избежать ошибок. Это процесс, посредством которого аналого-цифровой преобразователь с одной крутизной преобразует заданный аналоговый сигнал в цифровой выходной сигнал.

Графическое представление

Графическое представление отображает влияние входного напряжения и сопротивления на графике.

Отношение Vin и T.

На приведенном выше графике показано время, необходимое для интегрирования по отношению к приложенному входному напряжению. Опорное напряжение и RC постоянны, поэтому наклон, т. е. Vref/RC, постоянен. Входное напряжение влияет только на время. Чем выше входное напряжение, тем больше времени потребуется для процесса интегрирования, а наклон останется прежним.

Опорное напряжение и RC постоянны, поэтому наклон, т. е. Vref/RC, постоянен. Входное напряжение влияет только на время. Чем выше входное напряжение, тем больше времени потребуется для процесса интегрирования, а наклон останется прежним.

Как видно из графика, этот АЦП имеет один наклон, что и привело к его названию АЦП с одним наклоном.

Влияние RC

Если входное напряжение фиксировано, а R или C изменяются, наклон изменяется. Несмотря на постоянный вклад, мы добьемся разного времени интегрирования. Допустим, если значение R уменьшить, то время, необходимое схеме интегратора для достижения входного напряжения по величине, также уменьшится.

Это значение RC изменяется со временем из-за внешних факторов, таких как температура и т. д., что является основной причиной его низкой точности и приводит нас к его решению, которое представляет собой аналого-цифровой преобразователь с двойным наклоном.

АЦП с двойной фазой

Интегратор аналого-цифрового преобразователя с двойной фазой имеет переключатель на входной стороне, который может подключаться либо к опорному напряжению, либо к входному напряжению. Первоначально при преобразовании переключатель подключается к входному напряжению, а интегратор интегрирует входное напряжение, пока его выход не сравняется с приложенным напряжением.

Первоначально при преобразовании переключатель подключается к входному напряжению, а интегратор интегрирует входное напряжение, пока его выход не сравняется с приложенным напряжением.

Если выходное напряжение равно V1, а T1 — это время, то V1 задается как:

VO= -1/RC Vin dt V1=-T1*Vin/RC

По истечении времени T1 коммутатор подключается к эталонному напряжению, и соответствующее напряжение интегрируется. На диаграмме видно, что заданное опорное напряжение отрицательное, но обычно оно больше, чем входное напряжение.

При подаче отрицательного задания интегратор интегрирует в положительном направлении и продолжает интегрировать до тех пор, пока выходное напряжение не станет равным нулю. Затраченное время представлено T2.

По истечении времени T1 выход интегратора равен

VO= -1/RC -Vref dt + Vinitial

Что для времени T2 можно записать как

VO= -T2*(-Vref)/RC + V1

Где V1 – начальное напряжение на конденсаторе и VO полное выходное напряжение на интеграторе за общее время T1+T2.

Если мы заменим V1 на его значение в приведенном выше уравнении, то

VO= T2*(Vref)/RC +(-T1*Vin/RC)

Выход будет равен нулю после T1+T2. Уравнение принимает вид

T2*(Vref)/RC +(-T1*Vin/RC)=0 T2=T1*Vin/Vref

В двухтактном АЦП T1 и опорное напряжение постоянны, поэтому время T2 прямо пропорционально входному напряжению. Если входное напряжение изменяется, T2 также изменяется. Это представлено на графике ниже.

Двойной наклон Принцип работы

Выход интегратора подключается к отрицательной клемме компаратора, а положительная клемма компаратора подключается к земле. В начале преобразования входное напряжение подключается к интегратору. Интегратор интегрирует его в отрицательном направлении. При сравнении с землей инвертирующий вывод отрицателен по отношению к неинвертирующему выводу, поэтому выходной сигнал компаратора становится высоким. Как и в случае с одинарным наклоном, сигнал И затем подает тактовые импульсы на n-битный счетчик и начинает счет с нуля, пока переполнение не станет равным 1.