Что такое ПЛИС и с чего начать изучение FPGA Altera

С чего начать изучение FPGA Altera?

Что такое ПЛИС?

Современные ПЛИС – программируемые логические микросхемы, выполняемые по технологии от 10 нм и содержащие большое количество логических элементов. Элементы могут выполнять простые логические операции «И», «ИЛИ» и др. или реализовывать функции умножителей, сумматоров, мультиплексоров и более сложных устройств.

FPGA – это микросхемы, в которых производителем не определены связи между логическими элементами. Разработчику необходимо самому определять взаимосвязи, назначение выводов и пути прохождения сигналов. В этом заключается большой плюс ПЛИС, так как следствием такого подхода становятся исключительно гибкая архитектура и быстродействие полученной электронной схемы. Но за это приходится платить увеличенным временем разработки устройства.

Как определить срок хранения и срой службы импортных микросхем?

По этим причинам ПЛИС нашли широкое применение в радиоэлектронной аппаратуре, устройствах высокоскоростной параллельной обработки сигналов, микропроцессорной технике.

С чего начать?

К большому сожалению, литературы на русском языке, описывающей принципы функционирования, программирования FPGA практически нет. Нет и чёткого понимания, даже у специалистов, когда применять ПЛИС, а когда программируемый микроконтроллер в повседневных задачах (не связанных с управлением космическими аппаратами или опасным промышленным производством).Начать нужно с главного вопроса – какие задачи вы планируете решать с использованием FPGA?

Если вы разрабатываете шину передачи данных для своего устройства или конструируете плату обработки сигналов с разложением в ряд Фурье, то ПЛИС — это то, что необходимо. Прекрасным решением является и построение отказоустойчивых систем с быстрым временем реакции на основе ПЛИС в системах автоматики.

Это лишь некоторые примеры, позволяющие оценить мощь и гибкость FPGA. Поэтому главными критериями при выборе определим быстродействие и оригинальную архитектуру, ради которых стоит пойти на дополнительные трудозатраты.

Что означают сокращения PCN, EOL, NRND в data sheet импортных электронных компонентов?

Приняв по тем или иным причинам твёрдое решение освоить ПЛИС, встают следующие вопросы – с чего начать и насколько это затратно?По поводу денежных затрат – микросхемы начального уровня, средства программирования и отладки ненамного дороже микроконтроллеров. Освоение сред разработки и языков программирования нисколько не сложнее тех же МК. Всё вышесказанное относится к продукции компании Altera, которую и рассмотрим более детально.

Средства разработки и отладки

Возникает справедливый вопрос: а как же проектировать и отлаживать такой «зоопарк» различных серий и их версий? Altera позаботилась об этом, создав единую среду проектирования и отладки Quartus.К достоинствам продукта относятся:

- Возможность создания проекта на языках VHDL, Verilog или в графическом редакторе.

- Ведение всей фоновой работы по созданию конфигурационного файла ПЛИС, включая разводку в кристалле.

- Загрузка конфигурационного файла в ПЛИС и внутрисхемная отладка.

Для загрузки и отладки проектов в микросхемах поставляются программаторы в двух исполнениях – для LPT и USB портов.

Начало работы с FPGA Altera

Оптимальным для работы с продуктами Altera будет следующий алгоритм действий:1. Чётко сформулировать задачу, для решения которой предполагается использование ПЛИС

- Определите необходимое количество входов/выходов

- Уровень напряжения

- Перечень логических операций

- Допустимую задержку прохождения сигнала от входа на выход

- Другие параметры, критичные при выполнении задачи.

Ознакомиться с документацией на ПЛИС, скачав руководство с сайта производителя.

3. Скачать по этой ссылке и установить среду разработки Quartus.

Для продуктов Quartus Prime Lite Edition, Quartus II Web Edition, ModelSlim-Intel FPGA Starter Edition лицензия не требуется. Бесплатной версии вполне хватит для ознакомления со средой. Изучить среду разработки, пользуясь встроенной справкой и документацией на сайте Altera.

4. Приобрести ПЛИС Altera и программатор с параллельным или usb-портом.

5. Разработать и отладить проект своего устройства на ПЛИС.

Собрать электрическую схему, загрузить проект в микросхему, проверить полученный результат. При необходимости внести изменения в проект, воспользоваться возможностями внутрисхемной отладки.

Заявка на поставку импортных ПЛИС Altera

Получить подробную информацию о поставляемых брендах и условиях сотрудничества можно тут: https://import.el-ra.ru

Кроме этого, мы выполняем полный комплекс услуг по организации проверки и испытаниям электронных компонентов импортного производства, включая входной контроль, проверку на работоспособность, а также специальные проверки, механические и климатические испытания.

Получить подробную информацию о поставляемых брендах и условиях сотрудничества можно тут: https://import.el-ra.ru

Кроме этого, мы выполняем полный комплекс услуг по организации проверки и испытаниям электронных компонентов импортного производства, включая входной контроль, проверку на работоспособность, а также специальные проверки, механические и климатические испытания.

Если вы заинтересованы в работы с нами, то заполните форму по ссылке: www.el-ra.ru/zayavka

Курс по ПЛИС фирмы Altera

| Актуальность | Идёт набор |

|---|---|

| Стоимость | По запросу |

| Продолжительность | 72 часа |

| Группа | от 8 до 10 человек |

| Начало занятий | По мере формирования группы |

Цель программы – повышение профессионального уровня работников высокотехнологичных производств в рамках имеющейся квалификации в разработке электронных устройств на базе программируемых логических интегральных схем фирмы Altera.

Обращаем внимание, что ввиду специфики обучения по данному курсу сборные группы не обучаются. Слушатели курса должны быть работниками одной организации или одной отрасли.

Разработка электронных устройств производится с использованием систем автоматизированного проектирования (САПР), выраженное в качественном изменении профессиональных компетенций, необходимых для выполнения следующих видов деятельности:

- разработка, тестирования и отладка эл. устройств с использованием языков проектирования аппаратуры;

- применения современных программируемых интегральных микросхем классов CPLD, FPGA. SOPC;

- выбор методологии и маршрутов проектирования, знакомство с основными возможностями современных САПР.

В результате освоения программы слушатели должны приобрести следующие знания, умения и навыки, необходимые для качественного изменения компетенций, указанных выше.

Результаты освоение курса

Выпускники знают

- основы методики проектирования средств вычислительной техники с использованием языковых средств представления проектов;

- типовые синтаксические конструкции некоторых языков проектирования;

- принципы представления типовых дискретных устройств на языке проектирования аппаратуры;

- архитектуру современных ПЛИС и SOPC, особенности кристаллов фирмы Altera;

- основные возможности систем автоматизированного проектирования фирмы Altera;

Выпускники умеют

- описывать и моделировать специализированные цифровые устройства средней сложности;

- разрабатывать с использованием базовой системы проектирования с привлечением САПР сторонних фирм;

- имплементировать цифровые устройства в микросхемы программируемой логики фирмы Altera;

Выпускники владеют

- ПО для разработки, моделирования и синтеза дискретных устройств на базе их языкового описания;

- навыками разработки эффективных маршрутов проектирования в рамках набора САПР;

- методиками внутрикристальной отладки проектов средствами соответствующих САПР.

Категория слушателей – работники высокотехнологичных производств в рамках имеющейся квалификации в разработке электронных устройств, имеющие высшее профессиональное образование.

Форма обучения – очная, с отрывом от работы.

Учебный план

| № п/п | Наименование разделов | Всего часов | В том числе | |

|---|---|---|---|---|

| Лекции | Практические и лабораторные занятия | |||

| 1 | Основы языка VHDL | 34 | 18 | 16 |

| 2 | Архитектура современных ПЛИС и SOP | 12 | 12 | 0 |

| 3 | Системы проектирования для ПЛИС | 26 | 12 | 14 |

| Итого: | 72 | 42 | 30 | |

| Итоговая аттестация | Выполнение проверочной работы | |||

| № п/п | Наименование разделов | Всего часов | В том числе | |

|---|---|---|---|---|

| Лекции | Практические и лабораторные занятия | |||

| 1 | Основы языка VHDL | 34 | 18 | 16 |

1. 1 1 |

Краткая характеристика языков проектирования аппаратуры. Принципы интерпретации поведения в моделирующих системах. | 2 | 0 | |

| 1.2 | Язык VHDL. Базовые концепции языка. Структурное представление проекта. Время, сигналы. Дельта-циклы. | 2 | 4 | |

| 1.3 | Язык VHDL. Структура программы. Типы данных, операции. | 2 | 2 | |

| 1.4 | Язык VHDL. Параллельные операторы. | 2 | 2 | |

| 1.5 | Язык VHDL. Последовательные операторы языка. | 2 | 2 | |

1. 6 6 |

Язык VHDL. Описание типовых дискретных устройств. Комбинационные схемы, регистры, счетчики. | 2 | 2 | |

| 1.7 | Язык VHDL. Описание типовых дискретных устройств (автоматы). Подпрограммы, пакеты. | 2 | 2 | |

| 1.8 | Язык VHDL. Способы построения операционных устройств: микропрограммные потоковые и конвейерные реализации. | 2 | 2 | |

| 1.9 | Краткая характеристика других языков. | 2 | ||

| 2 | Архитектура современных ПЛИС и SOP | 12 | 12 | 0 |

2. 1 1 |

Архитектура SPLD. Классификация и обзор рынка PLD(Xilinx, ALTERA, Actel, Atmel,..). | 2 | ||

| 2.2 | Архитектура FPGA фирмы Altera | 2 | ||

| 2.3 | Архитектура SOPC фирмы Altera | 2 | ||

| 2.4 | Архитектура аналоговых ПЛИС. Работа с PSOC. | 4 | ||

| 2.5 | Тенденции развития и применения архитектуры SOPC. | 2 | ||

| 3 | Системы проектирования для ПЛИС | 26 | 12 | 14 |

3. 1 1 |

Методология проектирования. Маршруты проектирования. | 2 | 2 | |

| 3.2 | Знакомство с новыми возможностями современных САПР (Quartus II). | 2 | 2 | |

| 3.3 | JTAC-интерфейс и граничное сканирование. | 2 | 2 | |

| 3.4 | Современные подходы к тестированию. | 2 | 2 | |

| 3.5 | Верификации в современных САПР. Внутрикристальная отладка. Signal Tap | 2 | 4 | |

| 3.6 | Средства структурной реализации распространенных задач ЦОС. |

2 | 2 | |

Контактная информация

Запись на курс

Университетская программа Altera

О компании

|

Корпорация Altera — один из крупнейших разработчиков заказных интегральных микросхем (ИС), программируемых логических интегральных микросхем (ПЛИС) и систем на кристалле (СнК). Компания занимается разработкой проектов микросхем на основе языков описания аппаратуры, таких как VHDL и SystemVerilog. Также компания ведет разработку программного обеспечения, предоставляющего пользователям возможность разработки собственных аппаратных и аппаратно-программных средств в рамках маршрута проектирования на базе интегральных микросхем, разрабатываемых компанией. В июне 2015 года была приобретена и стала структурным подразделением корпорации Intel. |

Университетская программа (Altera University Program)

Кафедра 304 с 2013 года участвует в Университетской программе корпорации Altera, в рамках которой корпорацией предоставляются аппаратные платформы (стенды), программное обеспечение и методические материалы для проведения лекционных, практических работ по разработке цифровых устройств различной сложности на базе ПЛИС, создаваемых корпорацией.

Предоставляемое аппаратное и программное обеспечение используется для изучения студентами бакалавриата и магистратуры, осуществляющих обучение на кафедре, принципов разработки цифровой схемотехники, разработки специализированных вычислительных систем с использованием языков описания аппаратуры, работы с периферийными устройствами, разработки программного обеспечения встраиваемых систем, а также изучения архитектуры и организации современных вычислительных систем.

Программное обеспечение

Quartus® Software — Интегрированная среда разработки цифровых интегральных схем, осуществляющая интеграцию программного обеспечения, разрабатываемого как самой компанией, так и сторонними разработчиками программного обеспечения, необходимого для реализации полного маршрута проектирования цифровых интегральных схем.

Quartus® Simulation Tools — Программное обеспечение, входящее в состав Quartus Software и предназначенное для создания пользователем тестовых входных воздействий для модели цифровых устройств с использованием графического редактора.

Qsys System Integration Tool — Программное обеспечение, входящее в состав Quartus Software и используемое для проектирования и реализации встраиваемых компьютерных систем, включающих в свой состав процессоры, интерфейсы памяти и различные варианты интерфейсов ввода/вывода.

ModelSim® Simulation Software — Программное обеспечение компании Mentor Graphics, являющееся широко используемым инструментом логического моделирования цифровых схем с целью их проверки и отладки. Входит в состав Quartus Software и включает в себя библиотеки для ПЛИС компании Altera.

Altera® Monitor Program — Программное обеспечение, предоставляющее возможности компиляции и отладки программ на языке Ассемблера и языке C для процессоров ARM® Cortex®-A9 и Nios® II.

Аппаратные платформы для обучения и разработки

Более подробные сведения о аппаратных платформах (стендах), используемых в рамках Университетской программы корпорации Altera, можно узнать на сайте производителя (на английском языке), кликнув на изображение интересующего стенда.

| Учебный стенд DE1 на базе ПЛИС Altera семейства Cyclone II (в количестве 10 штук) | |

Учебный стенд DE1 является базовым стендом и идеальным средством для разработки цифровых устройств на базе интегральных микросхем. Стенд может использоваться как для изучения основ цифровой схемотехники и организации вычислительных систем, так и для изучения принципов работы интерфейсов устройств хранения данных, принципов работы со звуковым драйвером и COM-портом. В состав стенда входит:

|

|

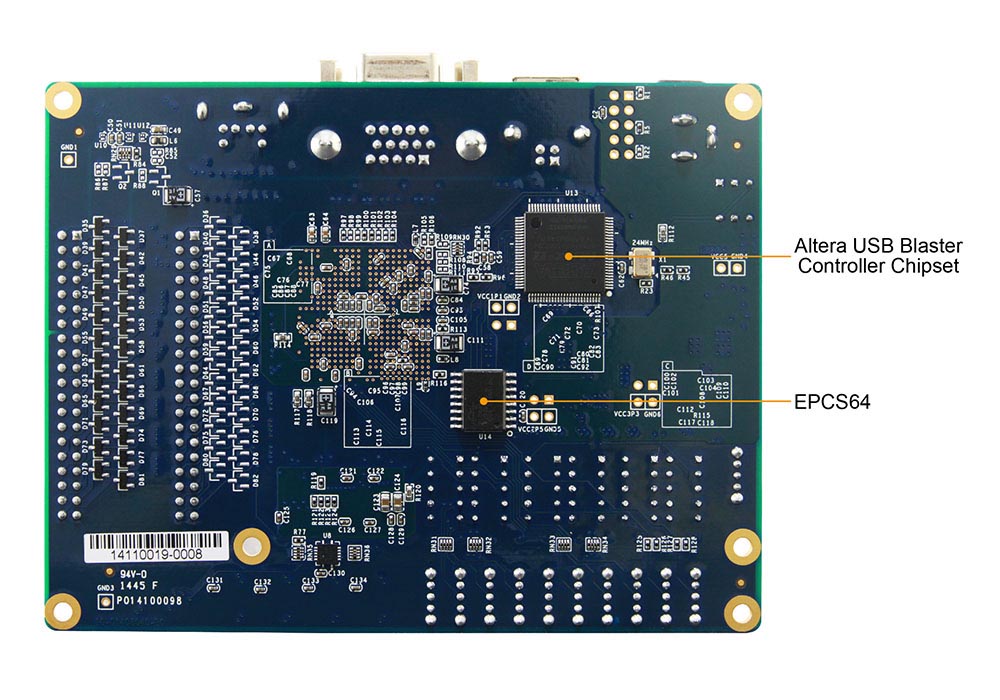

| Учебный стенд DE2-115 на базе ПЛИС Altera семейства Cyclone IV (в количестве 6 штук) | |

Учебный стенд DE2-115, основным компонентом которого является микросхема ПЛИС EP4CE115 семейства Cyclone IV компании Altera, является средством для обучения процессу разработки сложных цифровых вычислительных систем и устройств обработки данных на базе ПЛИС. Обладая по сравнению с со стендом DE1 большим набором периферийных компонентов и разъемов (Gigabit Ethernet, USB, ТВ-декодер и др.), а также более ресурсоемкой ПЛИС, стенд DE2-115 позволяет реализовывать цифровые устройства широкого круга применения, в том числе системы обработки аудио- и видеоинформации, высокоскоростные сетевые устройства и многоядерные микропроцессорные системы. В состав стенда входит: Обладая по сравнению с со стендом DE1 большим набором периферийных компонентов и разъемов (Gigabit Ethernet, USB, ТВ-декодер и др.), а также более ресурсоемкой ПЛИС, стенд DE2-115 позволяет реализовывать цифровые устройства широкого круга применения, в том числе системы обработки аудио- и видеоинформации, высокоскоростные сетевые устройства и многоядерные микропроцессорные системы. В состав стенда входит:

|

|

| Учебный стенд DE1-SoC на базе ПЛИС Altera семейства Cyclone V SoC (в количестве 11 штук) | |

|

|

Учебный стенд DE1-SoC представляет собой надежную платформу для разработки аппаратных средств, построенную вокруг системы на кристалле (СнК), включающей в себя современный двухядерный микропроцессор ARM® Cortex®-A9 и область программируемой логики, обеспечивающую максимальную гибкость. В состав стенда входит:

|

ПЛИС Altera. Часть 6: сборка схемы и загрузка конфигурации

Это заключительная часть цикла посвященная программируемой логике и среде разработки Quartus компании Altera (Intel).

Ссылки на предыдущие части:

ПЛИС Altera. Часть 1: установка и настройка среды разработки

ПЛИС Altera. Часть 2: проектирование цифровой схемы

ПЛИС Altera. Часть 3: первая компиляция проекта

ПЛИС Altera. Часть 4: доработка схемы и плата CTRL-CPLD-EPM570

ПЛИС Altera. Часть 5: Quartus Pin Planner

В первой части рассказывалось о загрузке и установке Quartus. О создании пустого проекта с помощью мастера.

Во второй части рассматривалось проектирование цифровой схемы, определялась последовательность шагов для создания конфигурации ПЛИС.

В третьей части выполнялась настройка главного модуля проекта, был выполнен анализ и синтез схемы. Разбирались наиболее вероятные ошибки, которые могут быть выявлены при анализе и синтезе.

Четвертая часть была полностью посвящена электрической части проекта: доработка схемы проекта и знакомство с платой CTRL-CPLD-EPM570.

В пятой части рассказывается как связать цифровую схему проекта с физическими выводами микросхемы ПЛИС. Это третий этап создания конфигурации.

Это третий этап создания конфигурации.

Напоминаю, что процесс создания конфигурации предусматривает следующие этапы:

- проектирование цифровой схемы;

- анализ созданной схемы на наличие ошибок;

- привязка входов и выходов схемы к конкретным выводам ПЛИС;

- компиляция проекта и создание двоичных файлов для конфигурирования ПЛИС;

- конфигурирование ПЛИС посредством USB Blaster.

Шестая часть описывает последние два этапа процесса: компиляцию проекта и загрузку конфигурации в микросхему. Большая часть этой статьи посвящена настройке Quartus «Programmer».

Заключительная компиляция

Выполнение полной компиляции запускается с помощью кнопки «Start Compilation» на стандартной панели инструментов Quartus. Данная кнопка идет одиннадцатой справа, она выделена на следующем рисунке.

Также можно использовать меню Processing → Start Compilation.

Выполнение полной компиляции начинается с процесса анализа проекта и синтеза предварительной схемы коммутации блоков ПЛИС – «Analysis & Synthesis». Затем следует «Fitter», который выполняет размещение блоков синтезированной схемы на кристалле ПЛИС с учетом заданных: диапазона рабочих температур, энергопотребления схемы связанного с используемым стандартом ввода‑вывода, диапазона допустимых временных задержек указанных в проекте и многих других параметров. Для простых проектов подходят значения перечисленных параметров по умолчанию.

Затем следует «Fitter», который выполняет размещение блоков синтезированной схемы на кристалле ПЛИС с учетом заданных: диапазона рабочих температур, энергопотребления схемы связанного с используемым стандартом ввода‑вывода, диапазона допустимых временных задержек указанных в проекте и многих других параметров. Для простых проектов подходят значения перечисленных параметров по умолчанию.

Обобщенный отчет о результатах работы «Fitter» (Fitter → Summary) выводится по окончании всего процесса компиляции.

В основном, данный отчет не отличается от аналогичного отчета выводимого по завершении «Analysis & Synthesis». Добавляются лишь соотношения использованных и доступных ресурсов выбранной микросхемы ПЛИС: логических элементов и выводов. Эта информация выделена на рисунке выше.

После «Fitter»

свою работу выполняет «Assembler»,

который осуществляет генерацию файлов

для загрузки в ПЛИС. Самая интересная

часть отчета «Assembler» – это раздел

«Generated Files». В этом разделе

перечисляются файлы созданные ассемблером,

с указанием полного пути до них. Файл с

расширением «.pof» содержит

конфигурацию ПЛИС, подготовленную для

загрузки с помощью программатора.

Изображение данного раздела приведено

ниже.

В этом разделе

перечисляются файлы созданные ассемблером,

с указанием полного пути до них. Файл с

расширением «.pof» содержит

конфигурацию ПЛИС, подготовленную для

загрузки с помощью программатора.

Изображение данного раздела приведено

ниже.

Заключительный этап компиляции – это «TimeQuest Timing Analyzer». Данный инструмент осуществляет проверку синтезированного дизайна на соответствие заданным в проекте временным ограничениям. Например, проверка возможности работы схемы на определенной частоте. В Вашем проекте нет таких ограничений, так как схема управляется человеком непосредственно и не предполагает работы на запредельных частотах. Тем не менее, отсутствие данных ограничений Quartus считает серьезным недостатком, о чем он и сообщает пользователю сразу двумя критическими предупреждениями: «Critical Warning: Synopsys Design Constraints File file not found: ‘firstproject.sdc’. A Synopsys Design Constraints File is required by the TimeQuest Timing Analyzer to get proper timing constraints. Without it, the Compiler will not properly optimize the design.» Именно поэтому пункт «TimeQuest Timing Analyzer» в отчете о компиляции выделен красным шрифтом.

Without it, the Compiler will not properly optimize the design.» Именно поэтому пункт «TimeQuest Timing Analyzer» в отчете о компиляции выделен красным шрифтом.

Помимо критических предупреждений Вам будет выдано и несколько (около трех) обычных предупреждений такого содержания: «Warning: No clocks defined in design.». Они также связаны с «TimeQuest Timing Analyzer». В проекте не определены параметры тактового сигнала схемы, так как схема не предполагает работу с таким сигналом. Следовательно, Вы можете смело игнорировать эти предупреждения, как и предыдущие два.

Кроме перечисленных, также будут выведены несколько уже знакомых коммерческих предупреждений.

При наличии других критических предупреждений, или даже ошибок, необходимо внимательно изучить содержание окна «Messages» и отчет о компиляции. Разделы отчета содержащие информацию об ошибках будут выделены красным шрифтом. Так же, можно повторно выполнить соответствующий этап компиляции с помощью меню Processing → Start, для того чтобы сократить число сообщений в окне «Messages» или для проверки сделанных исправлений. Пункты меню Processing → Start: Start Fitter, Start Assembler и Start TimeQuest Timing Analyzer запускают одноименные задачи процесса полной компиляции проекта.

Пункты меню Processing → Start: Start Fitter, Start Assembler и Start TimeQuest Timing Analyzer запускают одноименные задачи процесса полной компиляции проекта.

Окно сообщений успешно откомпилированного проекта с некритичным числом предупреждений приводится на следующем рисунке.

После успешно выполненной компиляции проекта можно переходить к заключительному этапу: сборке схемы и загрузке синтезированной конфигурации в ПЛИС.

Сборка схемы и подключение программатора

Прежде чем подать питание на ПЛИС и загрузить в нее проект необходимо собрать спроектированную схему. Подключать что‑либо к ПЛИС «на горячую» нельзя!

Проектирование схемы было завершено в четвертой части серии статей. Для удобства эта схема приводится повторно.

Номера выводов ПЛИС указаны согласно настройкам в «Pin Planner» сделанным в пятой части серии.

После завершения сборки можно подключать программатор Altera USB Blaster. Altera/Intel рекомендует подключать программатор соблюдая следующую последовательность действий:

- отключить питание от платы «CTRL‑CPLD‑EPM570»;

- подключить программатор к USB порту включенного компьютера;

- соединить включенный программатор с гнездом «JTAG» платы с ПЛИС;

- включить питание платы с ПЛИС.

После выполнения этих действий можно загружать конфигурацию в ПЛИС.

Внимание! И при подключении программатора к плате с ПЛИС и при его отключении необходимо предварительно выключать питание платы!

При первом подключении к компьютеру программатора USB Blaster необходимо будет установить соответствующий драйвер. Все необходимые драйвера имеются в дистрибутиве Quartus. При установке Quartus они копируются в следующую директорию: «altera\13.1\quartus\drivers\usb-blaster». Имеются драйвера как для 32‑х так и для 64‑разрядных ОС Windows. Установка драйвера выполняется вручную, путем выбора директории с драйвером для автоматического поиска и установки необходимых файлов. Либо прямым указанием файла «usbblstr.inf».

Отсоединять программатор необходимо в обратной последовательности:

- отключить питание платы с ПЛИС;

- отсоединить программатор от гнезда «JTAG» платы;

- отключить программатор от USB порта компьютера.

Сам программатор должен быть включен при любых манипуляциях с разъемом JTAG. Такая последовательность действий обусловлена тем, что у оригинального программатора Altera USB Blaster есть проблема с питанием выходного буфера, из‑за которой он может быть выведен из строя при включении/отключении питания программатора соединенного с платой ПЛИС.

На этом работа с электрической часть проекта завершена. Можно переходить к загрузке конфигурации.

Quartus Programmer: настройка программатора

Для загрузки конфигурации используется инструмент «Programmer» среды Quartus. Этот инструмент можно вызвать с помощью меню Tools → Programmer. Либо посредством соответствующей кнопки на стандартной панели инструментов. Кнопка идет четвертой справа на панели. Она выделена на рисунке ниже.

При запуске «Programmer» откроется новое окно, вид которого приводится на следующем рисунке.

Первое, на что необходимо обратить внимание — это кнопка «Hardware Setup…» в верхнем левом углу окна «Programmer». На рисунке она обозначена цифрой 1. С ее помощью выполняется выбор программатора. Модель используемого программатора выводится в текстовом поле справа от кнопки (цифра 2 на рисунке). Сейчас там присутствует надпись «No Hardware», это означает что программатор требует настройки.

На рисунке она обозначена цифрой 1. С ее помощью выполняется выбор программатора. Модель используемого программатора выводится в текстовом поле справа от кнопки (цифра 2 на рисунке). Сейчас там присутствует надпись «No Hardware», это означает что программатор требует настройки.

Нажмите кнопку «Hardware Setup…» чтобы открыть одноименное окно. Изображение окна приводится ниже.

Данное окно содержит две вкладки: «Hardware Settings» и «JTAG Settings».

«JTAG Settings» используется для настройки доступа к серверам JTAG. Можно как добавлять удаленные сервера, к которым присоединяются конфигурируемые ПЛИС, так и настраивать доступ к серверу JTAG запущенному на Вашем компьютере.

Quartus «Programmer» работает по клиент‑серверной модели. В ней есть сервер — это специальная служба «jtagserver», которая запускается вместе с «Programmer» и непосредственно работает с программатором. И есть клиент — «Programmer», который обеспечивает пользовательский интерфейс для выбора и загрузки конфигурации ПЛИС. Клиент и сервер могут располагаться на разных компьютерах, которые могут находиться на разных концах света. Таким образом, можно организовать удаленную работу со схемой в лаборатории собранной на базе дорогой платы разработчика (например, платы на базе Stratix III в среднем стоят более 4 000 долларов).

Клиент и сервер могут располагаться на разных компьютерах, которые могут находиться на разных концах света. Таким образом, можно организовать удаленную работу со схемой в лаборатории собранной на базе дорогой платы разработчика (например, платы на базе Stratix III в среднем стоят более 4 000 долларов).

При локальной работе достаточно проверить статус сервера на вкладке «JTAG Settings». В списке «JTAG Servers» должен быть как минимум один сервер «Local» и «Connection Status», состояние подключения до него, «OK».

Если список серверов пуст, то скорее всего, возникла проблема с самим программатором: он перестал отвечать на запросы службы «jtagserver». В таком случае необходимо:

- закрыть окно «Hardware Setup»;

- подключить/переподключить программатор;

- открыть окно «Hardware Setup» и проверить наличие сервера «Local», состояние подключения к серверу (смотрите рисунок ниже).

Вторая вкладка — «Hardware Settings», она открывается по умолчанию. Эта вкладка используется для выбора конкретного программатора из множества доступных. Содержимое вкладки представлено на рисунке ниже.

Эта вкладка используется для выбора конкретного программатора из множества доступных. Содержимое вкладки представлено на рисунке ниже.

Доступные программаторы перечисляются в блоке «Available hardware items». Устройства в этот список добавляются пользователем вручную или самой средой автоматически. Автоматическое обнаружение доступно не для всех моделей программаторов. Вручную требуется добавлять либо устаревшие модели устройств, соединяющиеся с компьютером через LPT‑порт (это ByteBlaster II и ByteBlasterMV), либо «EthernetBlaster», который работает с компьютером как удаленный JTAG сервер. USB Blaster добавляется автоматически, поэтому пользователю достаточно проверить наличие USB программатора в списке.

Выбор программатора для прошивки ПЛИС осуществляется с помощью выпадающего списка, справа от надписи «Currently selected hardware». Программатор можно выбрать из списка непосредственно, либо выполнив двойной клик левой кнопкой мыши на соответствующем элементе столбца «Hardware» в «Available hardware items». В обоих случаях значение «No Hardware» заменится названием выбранного программатора. Вид вкладки после выполнения настройки приведен на рисунке выше.

В обоих случаях значение «No Hardware» заменится названием выбранного программатора. Вид вкладки после выполнения настройки приведен на рисунке выше.

Теперь можно закрыть окно «Hardware Setup». В результате, в окне «Programmer» надпись «No Hardware», рядом с кнопкой «Hardware Setup», сменится названием выбранного программатора.

Quartus Programmer: Device Chain

Все остальные настройки производятся в основном окне «Programmer». В верхней части окна, помимо «Hardware Setup» для настройки доступны еще два параметра: «Mode» и «Enable real-time ISP to allow background programming (for MAX II and MAX V) devices».

Параметр «Mode» определяет режим загрузки конфигурации в ПЛИС. По умолчанию установлен режим JTAG, его и необходимо использовать. Так как «Passive Serial Programming» и «Active Serial Programming» не совместимы с MAX II, а «In-Socket Programming» не поддерживается USB Blaster’ом.

Второй параметр — «Enable real-time ISP to allow background programming (for MAX II and MAX V) devices» активирует загрузку новой конфигурации на лету, без отключения ПЛИС от схемы на время прошивки. Новая конфигурация, в таком случае, будет применена только после перезагрузки ПЛИС по питанию. Эта возможность сокращает время простоя устройств на базе ПЛИС серии MAX, но действительно полезна только в промышленном применении. Поэтому данный параметр можно оставить в состоянии по умолчанию — отключенным.

Новая конфигурация, в таком случае, будет применена только после перезагрузки ПЛИС по питанию. Эта возможность сокращает время простоя устройств на базе ПЛИС серии MAX, но действительно полезна только в промышленном применении. Поэтому данный параметр можно оставить в состоянии по умолчанию — отключенным.

Большую часть окна занимают две панели: «Device Tree» и «Device Chain». На рисунке выше они обозначены окружностями с цифрами 1 и 2 соответственно. Их отображение можно включить (выключить) с помощью меню View → Show Device Tree и View → Show Device Chain.

Часть настроек панелей установлены Quartus автоматически. В «Device Tree», в колонку «File» подставляется имя файла конфигурации, созданного во время последней компиляции. А в «Device Chain» из этого же файла подставляется модель используемой микросхемы.

Панель «Device Chain» (цифра 2) используется для наглядного представления упрощенной схемы соединения ПЛИС и программатора. На ней отображаются только линии приема и передачи данных. Эта информация может оказаться полезной в случае конфигурирования сложных схем на базе нескольких ПЛИС. Дело в том, что JTAG‑интерфейс позволяет строить цепочки из последовательно соединенных (линиями TDI — TDO) устройств. Такое подключение позволяет использовать один программатор для конфигурирования всех устройств цепочки. «Device Chain» позволяет сориентироваться в порядке соединения этих устройств.

Эта информация может оказаться полезной в случае конфигурирования сложных схем на базе нескольких ПЛИС. Дело в том, что JTAG‑интерфейс позволяет строить цепочки из последовательно соединенных (линиями TDI — TDO) устройств. Такое подключение позволяет использовать один программатор для конфигурирования всех устройств цепочки. «Device Chain» позволяет сориентироваться в порядке соединения этих устройств.

Плата «CTRL‑CPLD‑EPM570» несет на своем борту только одну микросхему, поэтому схема «Device Chain» предельно проста и, обычно, не требует вмешательства пользователя. Если же в «Device Chain» нет ни одного устройства, то можно попробовать добавить его с помощью автоматического поиска устройств на JTAG‑интерфейсе. Автоматический поиск запускается с помощью кнопки «Auto Detect» (третья сверху), расположенной в столбце кнопок у левого края окна. Данная кнопка активна только в том случае, когда в «Hardware Setup» настроен программатор.

При выполнении автоматического поиска заодно будет проверена работа JTAG‑интерфейса в целом. Если устройства не будут обнаружены, то «Programmer» предложит запустить отладку JTAG подключения, которая позволяет пользователю вручную выполнять команды на интерфейсе. При возникновении такой проблемы необходимо проверить соединение программатора с платой «CTRL‑CPLD‑EPM570» и наличие питания на микросхеме ПЛИС (включена ли плата). После устранения проблем необходимо повторно запустить поиск устройств.

Если устройства не будут обнаружены, то «Programmer» предложит запустить отладку JTAG подключения, которая позволяет пользователю вручную выполнять команды на интерфейсе. При возникновении такой проблемы необходимо проверить соединение программатора с платой «CTRL‑CPLD‑EPM570» и наличие питания на микросхеме ПЛИС (включена ли плата). После устранения проблем необходимо повторно запустить поиск устройств.

Обнаруженные устройства добавляются и на схему «Device Chain», и в список «Device Tree».

Quartus Programmer: Device Tree

В «Device Tree» настраивается сам процесс конфигурирования/программирования устройств. Эта панель оформлена в виде таблицы из двенадцати колонок: «File», «Device», «Checksum», «Usercode», «Program/Configure», «Verify», «Blank-Check», «Examine», «Security Bit», «Erase», «ISP CLAMP», «ISP File». Автоматически заполняются первые четыре колонки.

Первое на что необходимо обратить внимание в этой таблице — это колонка «File». В ней обязательно должен быть указан файл конфигурации, синтезированной при компиляции проекта. Колонка может быть пустой в случае, если в «Device Chain» а, соответственно, и в «Device Tree» нет ни одного устройства. Тогда, необходимо добавить устройство с помощью автоматического обнаружения.

В ней обязательно должен быть указан файл конфигурации, синтезированной при компиляции проекта. Колонка может быть пустой в случае, если в «Device Chain» а, соответственно, и в «Device Tree» нет ни одного устройства. Тогда, необходимо добавить устройство с помощью автоматического обнаружения.

«File» будет содержать значение , если устройство было добавлено пользователем с помощью автоматического поиска или вручную. В этом случае файл необходимо добавить вручную с помощью кнопки «Change File…», которая располагается через две кнопки ниже кнопки «Auto Detect». Тоже действие можно выполнить и с помощью меню Edit → Change File…

Кнопка «Change File…» становится доступна только при выборе микросхемы ПЛИС в «Device Chain» или «Device Tree». Таким образом, для добавления файла потребуется сначала выбрать микросхему в «Device Chain», а за тем нажать на кнопку «Change File…». Порядок действий и сама кнопка обозначены на следующем рисунке.

Для добавления файла используется стандартное диалоговое окно Windows. Необходимо найти и выбрать с его помощью файл «firstproject.pof».

Необходимо найти и выбрать с его помощью файл «firstproject.pof».

По умолчанию, файлы конфигурации сохраняются в папке «output_files» в основной директории проекта. Если требуемого файла там нет, то необходимо свериться с отчетом о полной компиляции проекта. Для этого потребуется закрыть окно «Programmer» и открыть раздел «Assembler» → «Generated Files» отчета компиляции в основном окне Quartus. Сам отчет о компиляции можно открыть с помощью меню Processing → Compilation Report. Если раздел «Assembler» отсутствует в отчете, то это означает что данный этап не был выполнен. Запустите полную компиляцию и добавьте полученный файл конфигурации в «Device Tree».

После добавления файла «firstproject.pof» панель «Device Tree» обретет вид аналогичный рисунку, который приведен в начале раздела. Из файла были автоматически подставлены значения в колонки «File», «Device», «Checksum» и «Usercode». А именно:

- в File» были добавлены две новые строки: CFM и UFM;

- наименование модели микросхемы ПЛИС в «Device» уточнено;

- в «Checksum» было добавлено значение контрольной суммы хранящейся в файле конфигурации;

- в «Usercode» подставлен JTAG код устройства.

CFM (Configuration Flash Memory) и UFM (User Flash Memory) это две части внутренней Flash‑памяти MAX II. CFM используется исключительно для хранения конфигурации, откуда она автоматически вычитывается при каждом включении микросхемы. UFM может быть использована для хранения пользовательских данных. Объем UFM составляет 8 Кбит.

Значение «Checksum» рассчитывается только для конфигурационных данных в pof‑файле (для всего файла вычисляется CRC). Эта информация используется для сравнения конфигурации в pof‑файле с конфигурацией загруженной в ПЛИС.

«Usercode» — JTAG‑код автоматически сгенерированный Quartus или указанный пользователем вручную в настройках проекта. Автоматически генерируемый код меняется при компиляции, после каждого редактирования цифровой схемы. Таким образом, автоматический JTAG‑код позволяет различать разные версии одной конфигурации.

Остальные столбцы определяют режимы и параметры процесса работы с конфигурацией, которые настраиваются пользователем. Большинство параметров может быть применено отдельно к CFM или UFM.

Большинство параметров может быть применено отдельно к CFM или UFM.

Назначение каждого параметра рассматривается ниже.

«Program/Configure» — загрузка конфигурации из pof‑файла или буфера «Programmer» в ПЛИС. Можно прошить каждый из блоков CFM и UFM внутренней памяти по отдельности или оба разом.

«Verify» — вычитывание конфигурации ПЛИС и ее сравнение (по Checksum) с конфигурацией в pof‑файле. Если обнаружены различия, то проверка завершается с ошибкой.

«Blank-Check» — проверить, записана ли в памяти ПЛИС какая‑либо конфигурация. Если в устройство загружена конфигурация, то проверка завершается с ошибкой.

«Examine» — считать конфигурацию из ПЛИС в буфер «Programmer». После, загруженную конфигурацию можно сохранить в новый pof‑файл.

«Security Bit» — защищает ПЛИС от чтения конфигурации. При попытке чтения возвращаются некорректные значения, обычно — 0xFF. По этой причине функция «Verify» также перестает работать. Сбросить защиту можно только загрузив в ПЛИС конфигурацию без использования «Security Bit» или выполнив «Erase».

«Erase» — удаление данных конфигурации с ПЛИС.

«ISP CLAMP» — фиксация состояния каждого вывода ПЛИС на высоком, низком логическом уровне или в высокоимпендансном состоянии во время ее конфигурирования. Состояние выводов можно настраивать независимо друг от друга. С помощью данного режима можно выставить на выводах ПЛИС комбинацию сигналов сигнализирующих о том что микросхема находится в состоянии перепрошивки. Полезно для устройств на базе нескольких ПЛИС.

«IPS File» (I/O Pin State файл) — это файл описывающий состояние каждого вывода ПЛИС для режима ISP CLAMP. Без его наличия использование режима ISP CLAMP невозможно.

Загрузка и сохранение конфигурации

Для выполнения каких‑либо действий с конфигурацией ПЛИС необходимо выбрать это действие в списке «Device Tree», а именно — проставить галочку в соответствующем столбце. После, в ряду кнопок у левого края окна станет доступна кнопка «Start» (первая сверху). Нажатием на данную кнопку запускается выполнение выбранного действия. Прогресс выполнения и итоговый статус можно отследить по строке прогресса в верхнем правом углу окна «Programmer» (справа от надписи «Progress:»). Сообщения, выводимые в процессе работы «Programmer», можно увидеть в основном окне Quartus на панели «Messages», вкладка «System».

Таким образом, для сохранения загруженной в ПЛИС конфигурации достаточно выбрать действие «Examine» в «Device Tree» и нажать кнопку «Start». Значение в поле «File» скрывается при выборе «Examine».

После нажатия на «Start» в строке прогресса будет выводится как, собственно, прогресс чтения конфигурации, так и его результат. При достижении 100% (Successful) в поле «File» будет подставлено имя временного файла «untitled1.pof». Для сохранения «untitled1.pof» необходимо выбрать его в списке и нажать кнопку «Save File» у левого края окна (четвертая снизу). Будет открыт стандартный диалог открытия/сохранения файла.

Вид окна «Programmer» и описанная последовательность действий обозначены на рисунке выше.

Загрузка конфигурации производится аналогично:

- выбрать действие — «Program/Configure»;

- нажать кнопку «Start»;

- дождаться 100% (Successful) в строке прогресса.

Не забудьте в поле «File» указать верный файл конфигурации перед прошивкой. Заменить файл на необходимый можно с помощью кнопки «Change File…».

На рисунке выше видно, что в столбце «Program/Configure» поставлена только одна галочка — в строке CFM. Так как проект не содержит информации для UFM, то выбирать для прошивки эту часть памяти не обязательно.

Сам процесс прошивки в «Programmer» состоит из следующей последовательности действий: Erase, Blank-Check (если выбрано), Program/Configure и Verify. При ошибке на любой из стадий процесс будет прерван.

Лог процесса прошивки выводится в основное окно Quartus на панели «Messages», вкладка «System».

Прервать выполнение процесса чтения/записи можно и вручную, с помощью кнопки «Stop» (вторая сверху). Данная кнопка становится доступна только на время выполнения чтения/записи конфигурации.

Всего, у левого края окна «Programmer» расположено десять кнопок. Часть из них была рассмотрена выше. Ниже описывается назначение оставшихся пяти кнопок:

- «Delete» — активна только при выборе устройства в «Device Chain» или файла в «Device Tree». Удаляет выбранное устройство и связанный с ним pof‑файл из «Programmer».

- «Add File…» — активна всегда. Используется для добавления pof‑файла в «Device Tree». В «Device Chain» будет автоматически добавлено соответствующее устройство. При добавлении нового файла существующие файлы не удаляются из списка «Device Tree».

- «Add Device…» — активна всегда. Используется для ручного добавления устройств в «Device Chain». При нажатии на кнопку открывается диалоговое окно, в котором можно выбрать одну или несколько микросхем по их маркировке.

- «Up» и «Down» — активны только тогда, когда в «Programmer» добавлено несколько микросхем ПЛИС. Используются для изменения порядка устройств в цепочке JTAG.

Все кнопки продублированы одноименными пунктами в меню «Edit» главного меню окна «Programmer».

Настройки «Device Tree» и «Device Chain» можно сохранить в общем файле с расширением cdf, который располагается в «output_files» в основной директории проекта. В проекте firstproject этот файл называется «firstproject.cdf». Относительный путь до него выводится в квадратных скобках в шапке окна «Programmer». Настройки сохраняются с помощью меню File → Save или File → «Save as». Также, «Programmer» будет предлагать сохранить файл cdf при попытке закрыть его окно, в случае если в настройки были внесены изменения.

Заключение

На этом изучение Quartus «Programmer» завершено. Осталось лишь подключить программатор к плате «CTRL‑CPLD‑EPM570». Включить саму плату. Настроить «Programmer» и загрузить конфигурацию в ПЛИС. При этом конфигурация счетчика в микросхеме будет заменена конфигурацией Вашего проекта и схема из трех независимых логических элементов готова к работе.

В результате получится устройство аналогичное изображенному на фотографии. Теперь можно опробовать работу каждого логического элемента на практике.

Пришло время подвести итоги.

В шестой части серии статей о Quartus был разобран процесс полной компиляции проекта, подключение и настройка USB Blaster. Большая часть статьи посвящена настройке Quartus «Programmer».

Сама серия на этом завершается. В статьях были затронуты основы цифровой схемотехники. Рассмотрены ключевые функции ПО Quartus. Инструмента, которым пользуются и профессионалы. Поздравляю всех дошедших до финала!

Полученные знания можно использовать для освоения проектирования цифровых схем. Начать, лучше всего, с комбинационных схем и основ математической логики. Так как комбинационные схемы строятся из базовых логических элементов. После, можно перейти к схемам с памятью — последовательным схемам. Последовательные схемы это цифровые схемы объединяющие комбинационные схемы и ячейки памяти — триггеры. Последовательные и комбинационные схемы являются фундаментом для проектирования более сложных цифровых схем: сумматоров, схем сдвига, конвейеров и т. п. А обзаведясь таким багажом знаний Вы сможете проектировать специализированные микросхемы прямо у себя дома! Первый шаг сделан.

Вконтакте

Программирование последовательных ПЗУ по JTAG

Микросхемы FPGA фирмы Altera выпускаются по технологии SRAM, в процессе работы конфигурация FPGA хранится в ячейках ОЗУ.

Поскольку конфигурационное ОЗУ является энергозависимым, его необходимо загружать каждый раз после включения питания.

В процессе разработки и отладки менять конфигурацию FPGA приходится часто, для этого, как правило, используют загрузку по JTAG-интерфейсу с помощью специальных аппаратных средств — загрузочных кабелей.

После завершения процесса разработки и отладки автономного устройства на основе FPGA необходимо обеспечить его энергонезависимость. Для конфигурации FPGA в автономных устройствах используются два способа: загрузка из внешнего параллельного ПЗУ или микропроцессора (режим Passive Parallel) и загрузка из последовательного конфигурационного ПЗУ (режимы Passive serial и Active Serial) [1]. Фирма Altera выпускает последовательные конфигурационные ПЗУ, поддерживающие различные режимы конфигурации. Выпускаются и однократно программируемые, и репрограммируемые конфигурационные ПЗУ. Репрограммируемые конфигураторы могут быть прошиты непосредственно на плате целевого устройства по последовательному интерфейсу.

Все семейства FPGA фирмы Altera поддерживают режим конфигурации Passive Serial. В процессе отладки устройств этот режим может эмулироваться любым загрузочным кабелем фирмы Altera. Источником тактового сигнала в этом режиме является конфигурационное ПЗУ или загрузочный кабель. Для обеспечения этого режима можно использовать следующие конфигурационные ПЗУ: EPC1441, EPC1, EPC2, EPC4, EPC8, EPC16. Последние три микросхемы образуют семейство Enhanced-конфигураторовкроме режима Passive Serial эти микросхемы поддерживают также режим Fast Passive Parallel.

Микросхемы EPC1441 и EPC1 являются однократно программируемыми (One-Time Programmable, OTP). Для прошивки этих микросхем служит автономный программатор ASAP2. Микросхемы EPC2, EPC4, EPC8, EPC16 — репрограммируемые. Они могут быть запрограммированы непосредственно в целевом устройстве по JTAG-интерфейсу.

Фирма Altera предлагает несколько загрузочных кабелей для конфигурации FPGA и внутрисхемного программирования конфигурационных ПЗУ — MasterBlaster, USB Blaster, ByteBlaster MV и ByteBlaster II. Эти устройства различаются по способу подключения к персональному компьютеру и обладают различными возможностями.

Новые семейства FPGA фирмы Altera — Cyclone, Cyclone II и Stratix II—кроме режимов Passive Parallel и Passive Serial поддерживают еще один режим конфигурации — Active Serial. Режим Active Serial поддерживается последовательными конфигурационными ПЗУ EPCS1, EPCS4, EPCS16, EPCS64. Невысокая цена этих конфигураторов делает их применение весьма оправданным, особенно при серийном выпуске устройств. Далее в статье под «последовательными конфигурационными ПЗУ» будем понимать именно эти конфигураторы с интерфейсом Active Serial.

Режим Active Serial имеет две отличительные особенности:

- источником тактового сигнала конфигурации (DCLK) является FPGA;

- конфигурационное ПЗУ программируется через те же выводы, через которые оно загружает проект в FPGA.

Последовательные конфигурационные ПЗУ с интерфейсом Active Serial могут быть запрограммированы в целевом устройстве с помощью загрузочных кабелей USB Blaster или ByteBlaster II или с помощью внешнего микропроцессора, реализующего программно интерфейс Active Serial (фактически это хорошо известный интерфейс SPI).

Однако применение последовательных конфигурационных ПЗУ со своим собственным интерфейсом программирования вносит в процесс отладки ряд неудобств. Разработчик вынужден либо каждый раз перепрограммировать конфигуратор для того, чтобы загрузить в FPGA отлаживаемый проект, либо использовать два разных интерфейса: JTAG для загрузки отлаживаемого проекта в FPGA и Active Serial для программирования последовательного конфигурационного ПЗУ.

Чтобы упростить процесс отладки, фирма Altera предлагает альтернативный метод программирования последовательных конфигурационных ПЗУ с интерфейсом Active Serial. Этот метод заключается в использовании JTAG-интерфейса и для загрузки конфигурации в FPGA, и для программирования последовательных конфигурационных ПЗУ [2].

Суть метода заключается в следующем: для программирования конфигурационного ПЗУ в FPGA по JTAG-интерфейсу загружается специально подготовленный проект — Serial FlashLoader (SFL). SFL представляет собой мост между интерфейсами JTAG и Active Serial и преобразует поток данных, поступающих по JTAG-интерфейсу, в формат, необходимый для программирования последовательного конфигурационного ПЗУ.

Применение этого метода позволяет использовать для программирования последовательных конфигурационных ПЗУ любой загрузочный кабель фирмы Altera, а также несколько упростить разрабатываемое устройство (поскольку отпадает необходимость устанавливать отдельный разъем для программирования конфигуратора).

Поддержка такого метода программирования последовательных конфигурационных ПЗУ осуществляется в САПР Quartus II начиная с версии 4.1 Service Pack 1.

Оба метода программирования последовательных конфигурационных ПЗУ представлены на рис. 1.

Рис. 1. Методы программирования последовательных конфигурационных ПЗУ

Преимущества и недостатки обоих методов

программирования последовательных конфигурационных ПЗУ представлены в таблице.

Таблица. Методы программирования последовательных конфигурационных ПЗУ

Процесс программирования последовательных конфигурационных ПЗУ по JTAG-интерфейсу включает три этапа.

Этап 1. Создание файла для программирования по JTAG-интерфейсу.

Для программирования последовательных конфигурационных ПЗУ по JTAG-интерфейсу используются файлы в форматах JTAG Indirect Configuration (jic) или JAM Standard Test And Programming Language, STAPL (jam).

Jic-файл формируется в САПР Quartus II путем преобразования файла для конфигурации FPGA — SRAM Object File (sof).

Преобразование происходит следующим образом:

- В меню «File» выбирается пункт «Convert Programming Files».

- В открывшемся окне (рис. 2) в поле «Programming file type» выбирается формат «JTAG Indirect Configuratuon File (.jic)».

- В поле «Configuration device» из списка выбирается используемая в устройстве микросхема последовательного конфигурационного ПЗУ.

- В поле «File name» вводится имя выходного jic-файла.

- В секции «Input file to convert» активизируется раздел «SOF Data» и указывается входной sof-файл для преобразования (кнопка «Add File»). При этом в разделе «SOF Data» отображается тип целевой микросхемы FPGA (информация о нем содержится в sofфайле).

- В секции «Input file to convert» активизируется раздел «Flash Loader» и выбирается используемая в устройстве микросхема FPGA (кнопка «Add Device»).

- После того как выполнены все установки, запускается процесс преобразования (кнопка «Ok»).

Рис. 2. Преобразование sof-файла в формат JTAG Indirect Configuration (jic)

При желании разработчик может преобразовать jic-файл в формат JAM STAPL. Для преобразования нужно сделать следующее:

- В САПР Quartus II открыть окно программатора (меню «Tools», пункт «Programmer»).

- Выбрать jic-файл в качестве входного (кнопка «Add File»).

- В меню «File» выбрать пункт «Create/Update», затем во всплывающем меню выбрать «Create JAM, SVF or ISC File».

Окно создания jam-файла представлено на рис. 3.

Рис. 3. Преобразование jic-файла в формат JAM STAPL

Структура полученных в результате таких преобразований jic- или jam-файлов представлена на рис. 4. Файл состоит из двух секций. Первая содержит Serial FlashLoader (или SFL образ) — мост между интерфейсами JTAG и Active Serial. SFL-образ создается в пакете Quartus II автоматически в процессе преобразования sof-файла в формат JTAG Indirect Configuration (jic). Вторая секция содержит блок данных для прошивки последовательного конфигурационного ПЗУ, который переносится в jic-файл из sof-файла.

Рис. 4. Структура jic/jam-файла

Рассмотрим ситуацию, когда в устройстве используется несколько микросхем FPGA (каждая со своим собственным конфигурационным ПЗУ), которые образуют JTAG-цепочку . В этом случае для каждой FPGA нужно создать ее собственный jic-файл. Если разработчик желает использовать формат JAM STAPL, то при преобразовании он может объединить jic-файлы для всех микросхем цепочки в один выходной jam-файл, который позволит запрограммировать все последовательные конфигурационные ПЗУ, подключенные к микросхемам FPGA, образующим цепочку.

Этап 2. Загрузка SFL-образа в FPGA и программирование последовательного конфигурационного ПЗУ.

Для прошивки последовательных конфигурационных ПЗУ по JTAG-интерфейсу с использованием jic-файла нужно воспользоваться программатором из состава пакета Quartus II (меню «Tools», пункт «Programmer»). В окне программатора нужно открыть jic-файл (кнопка «Add File»). При этом будут отображены типы целевых FPGA и конфигуратора.

Операции «Program/Configure» в окне программатора должны быть активизированы для обоих устройств — и FPGA, и последовательного конфигурационного ПЗУ. Если микросхема FPGA не будет сконфигурирована как мост между интерфейсами JTAG и Active Serial (то есть не будет содержать SFL-образа), то попытка запрограммировать последовательное конфигурационное ПЗУ будет безуспешной.

Для того чтобы запрограммировать конфигурационные ПЗУ для нескольких FPGA, образующих JTAG-цепочку, надо в окне программатора открыть jic-файлы для соответствующих микросхем цепочки и активизировать операции «Program/Configure» для каждого файла.

Если в программаторе пакета Quartus II открыть jam-файл, то активизация режима «Program/Configure» для этого файла автоматически вызовет нужную последовательность действий — сначала произойдет загрузка образа SFL в FPGA, затем программирование конфигуратора (другими словами, активизировать процессы загрузки и программирования по отдельности в этом случае не нужно).

При использовании jam-файла разработчик может пользоваться не только программатором пакета Quartus II, но и любым JAM-плеером, поддерживающим STAPL (такой плеер может быть реализован как на персональном компьютере, так и во встраиваемом микропроцессоре на целевой плате).

На рис. 5 представлена ситуация, когда в целевом устройстве имеется JTAG-цепочка из двух FPGA — EP1C20 и EP1C6. Для прошивки конфигуратора первой из этих FPGA сформирован jam-файл, для второй — jic-файл. Для того чтобы изменить содержимое конфигурационного ПЗУ, подключенного к EP1C6 (в нашем случае это EPCS4SI8), нужно активизировать операции «Program/Configure» только для jic-файла (в этом случае при выполнении программирования микросхема EP1C20 будет «прозрачной» для JTAG- интерфейса).

Рис. 5. Программирование последовательных конфигурационных ПЗУ по JTAG-интерфейсу в пакете Quartus II (FPGA образуют JTAG-цепочку)

Этап 3. Реконфигурация FPGA (загрузка нового проекта, прошитого в конфигурационное ПЗУ)

Для того чтобы после окончания процесса программирования последовательного конфигурационного ПЗУ загрузить новый проект в FPGA, нужно на вход nCONFIG подать импульс низкого логического уровня либо просто выключить и включить питание устройства. При этом будет активизирован процесс конфигурации в режиме Active Serial, и проект, записанный в ПЗУ, загрузится в FPGA, заменяя находящийся там в момент программирования ПЗУ Serial FlashLoader.

Схема включения FPGA семейств Cyclone и Cyclone II и последовательного конфигурационного ПЗУ представлена на рис. 6. Состояние входов MSEL[1..0] FPGA определяет режим конфигурации Active Serial. Во время загрузки SFL-образа в FPGA состояние входов MSEL[1..0] игнорируется, так как загрузка конфигурации в FPGA по JTAG-интерфейсу имеет наивысший приоритет. После завершения процесса программирования новый проект будет загружаться в FPGA в режиме Active Serial.

Рис. 6. Включение FPGA семейств Cyclone и Cyclone II для реализации программирования последовательного конфигурационного ПЗУ по JTAG-интерфейсу

Литература- AlteraConfiguration Handbook. http://www.altera.com/literature/hb/cfg/config_handbook.pdf.

- Using the Serial FlashLoader With the Quartus II Software. Altera Application Note 370. http://www.altera.com/literature/an/an370.pdf.

Как я могу использовать HPS контактов платы разработки altera FPGA?

Как я могу создать свою собственную функцию слоя MAC для доступа к чипу Ethernet вместо использования функции altera IP? Моя плата-DE1-SoC с чипом cyclone V 5CSEMA5F31C6. Контакты для доступа к чипу Ethernet сделаны так, чтобы быть HPS контактами, которым я не могу назначить свои собственные сигналы.

macos fpga ethernet intel-fpgaПоделиться Источник yanqiangliu 13 июля 2015 в 06:45

2 ответа

- Linux не может обнаружить Altera FPGA

Ну, у меня есть бластер Altera FPGA и USB. Я скачал quartus, но он не обнаруживает FPGA, я попробовал с urjtag, и он работает нормально. Я попробовал запустить его с sudo, но опять то же самое. Помогите пожалуйста

- Как напечатать номер с помощью VGA Verilog и платы Altera DE2?

Я использую Altera DE2 FPGA board и verilog, спроектировал простой CPU, используя их. Мне нужно напечатать значение регистра, используя выход VGA платы. Как я должен это сделать?

1

Это возможно и для циклона V. У меня есть свой собственный Ethernet IP, работающий на стороне fpga на плате DE1-SOC с использованием контактов HPS. Я использовал их через функцию мультиплексирования контактов компонента hps. Вы должны настроить их и сделать hps boot кодом предварительного загрузчика для этой конфигурации. Однако вы не можете использовать функцию DDR (следовательно, вы не можете достичь 1 Гбит / с) в циклоне v (об этом сказала Altera). Для этого процесса вы должны установить мультиплексирование выводов, сгенерировать Qsys и скомпилировать Quartus. Этот процесс создает папку spl_bsp. Затем вы должны создать карту SD с образом, предоставленным Altera (образ содержит все требуемые разделы). После этого вы сможете сделать предварительный загрузчик: 1) bsp-generate-files.exe –settings ./software/spl_bsp/settings.bsp –bsp-dir ./hps_isw_handoff/soc_system_hps_0 2) cd software/spl_bsp/ 3) сделать 4) сделайте uboot 5) alt-boot-disk-util.exe-p preloader-mkpimage.bin-a write-d e // e-дисковод карты SD 6) cp uboot-socfpga/u-boot.img /cygdrive/e

Наконец, поместите карту SD в комплект ПЛИС и запрограммируйте FPGA. HPS загружается с карты SD, и матрица мультиплексирования контактов настраивает контакты для вывода.

Поделиться rcayssials 31 октября 2016 в 11:36

0

Это возможно на новом Arria 10 SoC, но не в Cyclone V. Arria 10 имеет общие операции ввода-вывода, которые настраиваются для HPS или FPGA.

Поделиться phox 21 июля 2015 в 19:26

Похожие вопросы:

Altera OpenCL параллельное выполнение в FPGA

Я уже некоторое время изучаю Altera OpenCL, чтобы улучшить тяжелые вычислительные программы, переместив вычислительную часть в FPGA. Мне удалось выполнить пример векторного сложения, предоставленный…

Как соединить части ракеты-чипа, чтобы поставить на altera FPGA

Я пытаюсь сопоставить ракетный чип riscv с Altera cyclone 2 FPGA. Я могу генерировать символьные файлы (с помощью программного обеспечения Altera Quartus 2) из файла Top.DefaultFPGAConfig.v с такими…

Altera FPGA vs Raspberry PI для обнаружения LED с помощью камеры

Я хочу применить компьютерное зрение к автономному роботу-автомобилю, чтобы позиционировать себя, обнаруживая источники света (LED)на поле. У меня есть Altera FPGA и Raspberry PI. Оба будут…

Linux не может обнаружить Altera FPGA

Ну, у меня есть бластер Altera FPGA и USB. Я скачал quartus, но он не обнаруживает FPGA, я попробовал с urjtag, и он работает нормально. Я попробовал запустить его с sudo, но опять то же самое….

Как напечатать номер с помощью VGA Verilog и платы Altera DE2?

Я использую Altera DE2 FPGA board и verilog, спроектировал простой CPU, используя их. Мне нужно напечатать значение регистра, используя выход VGA платы. Как я должен это сделать?

ищу Альтера HPS для FPGA пользовательский компонент руководящего принципа интеграции, используя библиотеке Qsys

Я ищу руководство по интеграции пользовательских компонентов от HPS до FPGA с помощью Qsys. У меня есть плата De0 nano SoC. Я новичок в программировании ПЛИС SoC. Я все еще не мог найти материал или…

Программирование EP2C35F672C6 FPGA приобрести

Я новичок в разработке совета директоров FPGAs &. В этом семестре, я был введен в Кварт II, VHDL, а также FPGAs. Я загрузил несколько основных конструкций на плату DE2 , на которой есть…

Я хочу использовать ram в своей FPGA Altera DE1-SOC, правильно ли я иду?

Поэтому я создал этот модуль, который, как предполагается, представляет собой RAM, на котором я сохраняю некоторые данные в соответствии с результатами на моем верхнем модуле. module RAM_OUT…

Как разделить память (из SDRAM) между HPS и FPGA в Cyclone-V?

Я хочу поделиться памятью между HPS и FPGA в циклоне-V. Я создал экземпляр интерфейса sdram_slave в Qsys(Platform Designer) с помощью avalon master и всего остального. Я хочу отправить базовый адрес…

FPGA to HPS связь в VHDL с FIFO

Я пытаюсь реализовать связь между моим FPGA и HPS на Совете по развитию Altera DE10nano. Для редактирования vhdl я использую программное обеспечение Quartus Prime. В то время как связь работает в…

Система питания ПЛИС ALTERA ARRIA 10 FPGA и ARRIA 10 SOC: проверенные решения для управления питанием

19 Июл 2017Автор статьи

Афшин Одабай (Afshin Odabaee)

(Опубликовано в журнале «Вестник Электроники» №1 2016)

Скачать статью в формате PDF (267 КБ)

Введение

Наборы для тестирования ПЛИС позволяют разработчикам систем выполнять оценку ПЛИС, не создавая собственной системы. На рис. 1 и 2 представлены платы разработки, предназначенные для выпускаемых компанией Altera новых 20-нм ПЛИС — Arria 10 FPGA и Arria 10 SoC. Эти платы, испытанные и проверенные компанией Altera, являются примером профессионального проектирования, обеспечивающего целостность сигналов и эффективную систему управления питанием.

Рис. 1. Демонстрационная плата Arria 10 GX FPGA

Рис. 2. Демонстрационная плата Arria 10 SoC

Управление питанием ПЛИС

Для достижения оптимальной производительности разработчикам необходимо тщательно выбирать решения для системы питания ПЛИС последнего поколения, которой и является Arria 10. Хорошо продуманная система питания может значительно уменьшить размер печатной платы, ее вес и сложность, а также снизить затраты энергии на ее охлаждение. Например, питание ядра Arria 10 (0,95 В, 105 A) может быть обеспечено импульсным DC/DC-преобразователем, имеющим ряд функций, позволяющих добиться максимального энергосбережения системы:

- Интегрированный в DC/DC-преобразователь 6-битный параллельный интерфейс VID в сочетании с подсистемой SmartVID позволяет уменьшить количество энергии, потребляемой ПЛИС, как в статическом, так и в динамическом режиме.

- Чрезвычайно малое значение сопротивления по постоянному току (DCR) датчика тока DC/DC-преобразователя улучшает эффективность и минимизирует потери мощности на индуктивности, а температурная компенсация отслеживает ее нагрев.

В таблице 1 представлен перечень основных шин питания (производства компании Linear Technology), используемых в отладочной плате Arria 10 — GX FPGA. Для ознакомления с полным перечнем источников, применяемых в данных отладочных платах, перейдите по ссылке www.linear.com/altera и выберите раздел Arria.

Таблица 1. Перечень элементов, использованных для построения системы питания демонстрационной платы Arria 10 GX FPGA

Моделирование системы питания с помощью LTpowerPlanner и LTpowerCAD

Как быть, если требования к цепям питания вашего устройства иные, чем в используемом вами наборе для разработки? В таких случаях используйте средства разработки LTpowerPlanner и LTpowerCAD. Данные утилиты позволяют создавать и оптимизировать собственные цепи питания для системы. Просто начните с решений, примененных в наборе разработки, а затем с легкостью изменяйте блоки цепей питания в соответствии с имеющимися требованиями и задачами, определяйте КПД и потери, находите решение для каждого отдельного случая. Система питания для отладочного набора Arria 10 GX FPGA была смоделирована и разработана с помощью данных утилит (рис. 3). Утилита LTpowerPlanner и ее более мощная модификация — LTpowerCAD находятся в свободном доступе, их можно загрузить на www.linear.com/ltpowercad.

Рис. 3. Схема питания для демонстрационной платы Arria 10 GX FPGA, смоделированная с помощью утилиты LTpowePlanner

Руководства и другие вспомогательные материалы, предназначенные для разработки систем с использованием ПЛИС производства компании Altera, вы можете найти по ссылке www.linear.com/altera.

Комментарий специалиста

Башмаков Павел, инженер по внедрению PT Electronics, [email protected]

На протяжении многих лет компания Linear Technology (LTC) тесно сотрудничает с ведущими производителями программируемых логических интегральных схем (ПЛИС), чтобы обеспечить разработчиков высокоэффективными источниками питания для самых чувствительных систем. В портфолио Linear Technology, Вы сможете найти современные и проверенные решения для любого семейства ПЛИС, а уникальные утилиты LTpowerPlanner и LTpowerCAD сделают процесс разработки максимально простым и эффективным.

Синтез электронных схем на базе ПЛИС компании “Альтера” (Бух (картонирт)), Е. А. Федоскин

1 Mängelexemplare sind Bücher mit leichten Beschädigungen, die das Lesen aber nicht einschränken. Mängelexemplare sind durch einen Stempel als solche gekennzeichnet. Die frühere Buchpreisbindung ist aufgehoben. Angaben zu Preissenkungen beziehen sich auf den gebundenen Preis eines mangelfreien Exemplars.2 Diese Artikel unterliegen nicht der Preisbindung, die Preisbindung dieser Artikel wurde aufgehoben oder der Preis wurde vom Verlag gesenkt.Die jeweils zutreffende Alternative wird Ihnen auf der Artikelseite dargestellt. Angaben zu Preissenkungen beziehen sich auf den vorherigen Preis.

3 Durch Öffnen der Leseprobe willigen Sie ein, dass Daten an den Anbieter der Leseprobe übermittelt werden.

4 Der gebundene Preis dieses Artikels wird nach Ablauf des auf der Artikelseite dargestellten Datums vom Verlag angehoben.

5 Der Preisvergleich bezieht sich auf die unverbindliche Preisempfehlung (UVP) des Herstellers.

6 Der gebundene Preis dieses Artikels wurde vom Verlag gesenkt. Angaben zu Preissenkungen beziehen sich auf den vorherigen Preis.

7 Die Preisbindung dieses Artikels wurde aufgehoben. Angaben zu Preissenkungen beziehen sich auf den vorherigen Preis.

10Ihr Gutschein TONIE10 gilt bis einschließlich 16.08.2021. Sie können den Gutschein ausschließlich online einlösen unter www.hugendubel.de. Keine Bestellung zur Abholung in der Buchhandlung möglich. Der Gutschein gilt nur auf Tonie-Figuren, Tonie-Transporter und Lauscher und nur solange der Vorrat reicht.Der Gutschein ist nicht mit anderen Gutscheinen und Geschenkkarten kombinierbar. Eine Barauszahlung ist nicht möglich. Ein Weiterverkauf und der Handel des Gutscheincodes sind nicht gestattet.

11 Ihr Gutschein LATENIGHT gilt bis einschließlich 13.08.2021. Sie können den Gutschein ausschließlich online einlösen unter www.hugendubel.de. Keine Bestellung zur Abholung in der Buchhandlung möglich. Der Gutschein ist nicht gültig für gesetzlich preisgebundene Artikel (deutschsprachige Bücher und eBooks), Tonieboxen, tolino eReader und tolino select.Der Gutschein ist nicht mit anderen Gutscheinen und Geschenkkarten kombinierbar. Eine Barauszahlung ist nicht möglich. Ein Weiterverkauf und der Handel des Gutscheincodes sind nicht gestattet.

12 Bestellungen ins Ausland und der DHL-Paketversand sind von der portofreien Lieferung ausgeschlossen. Gültig bis 31.10.2021.

* Alle Preise verstehen sich inkl. der gesetzlichen MwSt. Informationen über den Versand und anfallende Versandkosten finden Sie hier.

La pandèmia altera el desenvolupament de les accions del PLIS del 2020 – La Veu

Les galetes (cookies) són petits fragments de text que les webs envien als navegadors i que s’emmagatzemen al dispositiu de l’usuari, ordinadors, telèfons mòbils, tauletes и т. Д.Serveixen per millorar l’experiència d’ús de la web, ja que aquests arxius permeten que el lloc web recordi informació sobre la visita que ha fet l’usuari, com les opcions preferenceides o l’idioma. D’aquesta manera la web personalitza el seu contingut i es fa més àgil i útil per l’usuari.

Al navegar per aquesta web l’usuari està acceptant que s’instal·lin galetes (cookies) al seu dispositiu que ens permeten conèixer la següent informació:

Tipus de galetes (печенье)

Aquesta web utilitza galetes (cookies) temporals de sessions i galetes (cookies) permanents.Les galetes (cookies) de sessió únicament guarden dades mentre l’usuari accept a la web. Les galetes (cookies) permanents emmagatzemen les dades al dispositiu perquè siguin availables en més d’unaession.

Segons la finalitat de les dades obtingudes la web pot utilitzar:

Galetes (печенье) tècniques

Les que permeten a l’usuari la navegació a través de la pàgina web i la utilització de les differents opcions o serveis que conté.Например, controlar el trànsit i la comunicació de dades, identiftificar la sessió, accedir a les parts web d’accés restringit, realitzar la sol·licitud d’inscripció o Participació en un esdeveniment, utilitzar elements de seguretat durant la navegació em contingit .

Galetes (cookies) de personalització

Les que permeten a l’usuari accedir a la web amb algunes característiques de caràcter general que ja estan predfinides al seu dispositiu o que el mateix usuari defineixi.Например, l’idioma, el tipus de navegador a través del qual acceptdeix a la web, el disseny de continguts seleccionat, la geolocalització del dispositiu o la configuració Regional Des d’on Accedeix.

Galetes (Cookies) d’anàlisi estadística

Les que permeten realitzar el seguiment i l’anàlisi del comportament dels usuaris als llocs web. La informació recollida s’utilitza en el mesurament de l’activitat dels llocs web i per l’elaboració de perfils de navegació dels usuaris, que permetrien millorar el servei.

Галеты (печенье) de tercers

També es poden instal·lar galetes (cookies) de tercers que gestionen i milloren els serveis oferts. Например, сервис Google Analytics.

Gestionar les galetes (cookies) al meu navegador

L’usuari pot acceptar, bloquejar or ellear les ‘cookies’ instal·lades al seu equip mitjançant la configuració de les opcions del navegador del seu dispositiu.

Si es bloqueja l’ús de galetes (cookies) al navegador és possible que alguns serveis o funcionalitats de la pàgina web no estiguin disponibles.

Реконфигурируемые компьютерные системы: от первых ПЛИС к системам жидкостного охлаждения | Левин

И.А. Каляев, И. Левин, Е.А. Семерников, В. Шмоилов. Реконфигурируемые многотрубные вычислительные структуры. Nova Science Publishers, Нью-Йорк, США, 2012 г.

Вицынь Н. Современные тенденции развития системы автоматизированного проектирования в области электронных устройств // Chip News, № 1, 1997. С. 12–15. [Н.Вицын. Современные тенденции развития CAD-систем в электронике // Chip News, № 1, 1997, с.12–15.]

В начале. Рон Уилсон, главный редактор Altera Corporation. https://www.altera.com/solutions/technology/system-design/articles/_2013/in-the-beginning.html/ (дата обращения: 04.04.2016)

https://www.altera.com/ (дата обращения: 04.04.2016)

www.xilinx.com/ (дата обращения: 04.04.2016)

www.actel.com/ (дата обращения: 04.04.2016)

Грушвицкий Р.И., Мурсаев А.Х., Угрюмов Е.П. Проектирование систем на микросхемах программируемой логики.- Петербург: БХВ-Петербург, 2002. – 636 с. [Р.И. Грушвицкий, А.Х. Мурсаев, Э. Угрумов. Системное проектирование на микросхемах программируемой логики. – Санкт-Петербург: БХВ-Петербург, 2002, 636 с.]

.Стешенко В., Шипулин С., Храпов В. Тенденции и перспективы развития ПЛИС и их применение при проектировании аппаратуры COS // Компоненты и технологии, 2000, № 8. [В. Стешенко, С. Шипулин, В. Храпов. Тенденции и перспективы развития ПЛИС и их применения для проектирования устройств DSP // Компоненты и технологии, 2000, № 8.

0

0 ) и к микропроцессору (1 шт.)

) и к микропроцессору (1 шт.)