ИНСИС – FMC125cP+

Области применения

- Ввод и обработка сигналов

- Прием-передача данных

- Накопление информации

- Управление объектом

- Лабораторное оборудование

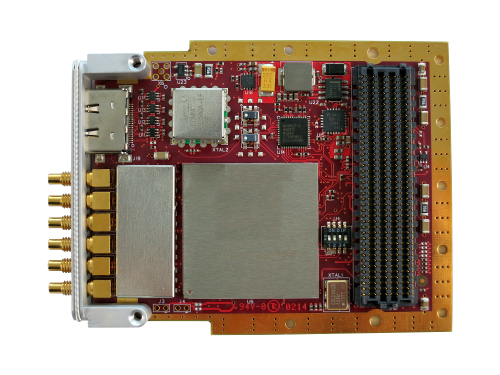

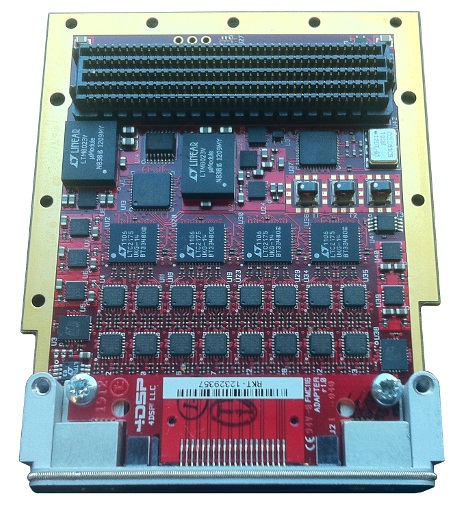

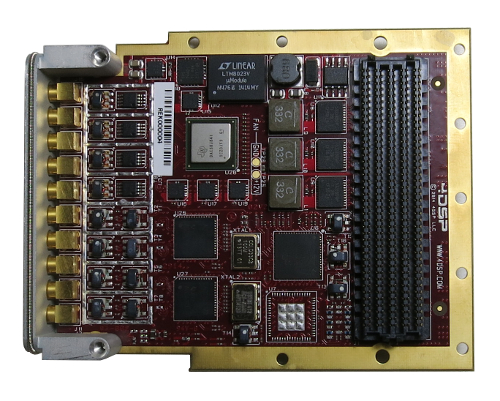

Внешний вид

Основные характеристики

- PICMG CPCI-S.0 R1.0 Модуль 3U (воздушное охлаждение)

- ANSI/VITA 57.1 несущий модуль FMC

- ПЛИС ADM Artix 7 XC7A200T-2FFG1156

- Динамическая память: SDRAM DDR3 256Mx64 до 533 МГц

- Конфигурационное ПЗУ QSPI 128 Мбит при ПЛИС

- Системный генератор: 100 МГц

- Программируемый генератор: от 10 до 810 МГц

- Коммутатор тактовых частот

- Разъем межмодульной синхронизации SYNX

- Дополнительный разъем PIOX через I2C ПЛИС

- Разъем JTAG ПЛИС

- Источник напряжения Vadj мезонинного модуля FMC, программируемый от 0,9 до 2,5 В

- Разъем XP2: поддержка тыльного ввода-вывода MGT и LVDS/LVCMOS

- Разъем XP1: питание 12 В до 4 А

- Разъем XP1: системный интерфейс PCIExpress x4, USB JTAG ПЛИС, GA0.

.3

.3

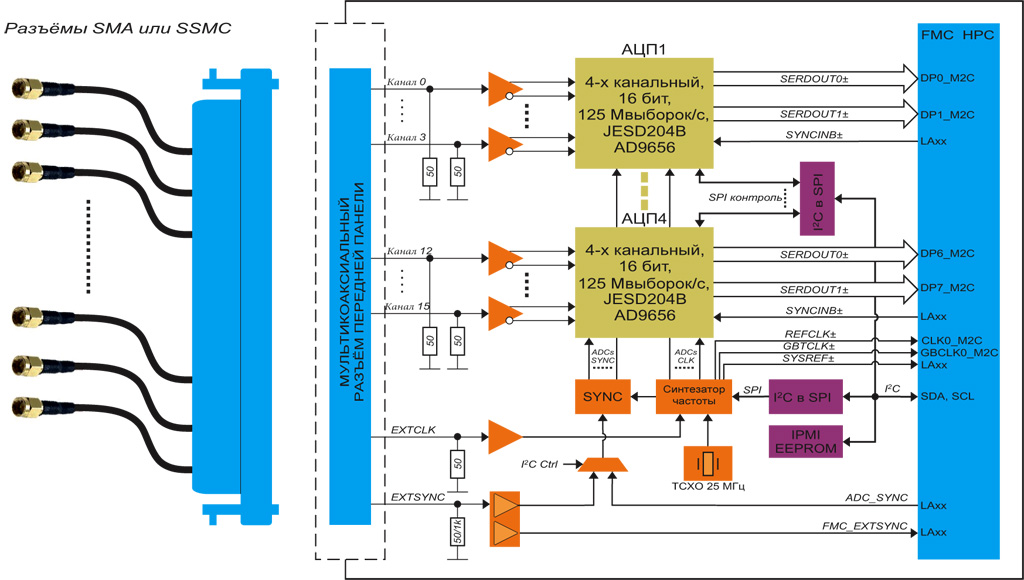

Структурная схема

Программная поддержка

- ISVI – программа визуализации и комплексного анализа сигналов для 32/64 версий Windows и Linux

- DAQ Tools – инструментальные средства разработки прикладного ПО устройств сбора данных для 32/64 версий Windows и Linux

- HDK125cP – комплект разработчика ПЛИС ADM

Модуль (несущая плата) FMC125cP предназначен для создания систем сбора и цифровой обработки сигналов на базе промышленных компьютеров, соответствующих CompactPCI Serial Specification. Модуль разработан на базе программируемой логической интегральной схемы (ПЛИС) Xilinx Artix 7 и сочетает в себе широкие возможности и разумную стоимость. Возможность установки мезонинного модуля FMC стандарта ANSI/VITA 57.1 позволяет организовать ввод-вывод необходимых пользователю сигналов, включая аналоговые, оптические и цифровые.

Модуль FMC125cP используется в системах с прямой передачей данных в память ПЭВМ, либо с накоплением данных в памяти DDR3, либо с выполнением цифровой обработки сигналов в ПЛИС. ПЛИС Artix 7 поддерживает работу мезонина FMC, а также обеспечивает поддержку SDRAM DDR3, интерфейсов PCI Express x4 v2.0. Пропускная способность интерфейса модуля с мезонинным модулем FMC достигает 80 Гбит/с через шины LVDS и 52 Гбит/с на прием-передачу через каналы GTX (восемь полнодуплексных линий).

ПЛИС Artix 7 поддерживает работу мезонина FMC, а также обеспечивает поддержку SDRAM DDR3, интерфейсов PCI Express x4 v2.0. Пропускная способность интерфейса модуля с мезонинным модулем FMC достигает 80 Гбит/с через шины LVDS и 52 Гбит/с на прием-передачу через каналы GTX (восемь полнодуплексных линий).

Система коммутации тактовых сигналов обеспечивает прием двух тактовых частот с мезонинного модуля, прием частоты от встроенного программируемого генератора-синтезатора, а также выдачу любых из принимаемых тактовых сигналов на линии мезонинного модуля и на ПЛИС.

В составе модуля предлагается пакет DAQ Tools для конкретного мезонинного модуля FMC производства АО «ИнСис». Пакет содержит прошивку ПЛИС и инструментальные средства для разработки приложений Заказчика. Стандартное ПО Xilinx подключается к интерфейсу JTAG ПЛИС через модуль USB 2.0 Digilent.

Большой объем наработанных АО «ИнСис» технических решений значительно облегчает интеграцию модуля во вновь создаваемые и существующие системы CompactPCI Serial для промышленных применений.

SFM-4D250

- Четыре канала ЦАП: 16 бит 250 МГц

- Аналоговая полоса тракта: 125 МГц

- Вход внешнего тактирования, синхронизация с FMC

- Встроенный высокостабильный опорный генератор

- Программное управление настройками схемы тактирования

- Буферизованный цифровой порт

- Поддержка двух каналов ЦАП и цифрового порта в исполнении FMC LPC

- Форм-факторFMC одиночной ширины с воздушным или кондуктивным охлаждением

Особенности

Субмодуль SFM-4D250 выполнен в соответствии со стандартом ANSI/VITA 57. 1 FMC:

FPGA Mezzanine Cards Base Standard и предназначен для использования в составе несущих модулей

стандартов: AdvancedMC

1 FMC:

FPGA Mezzanine Cards Base Standard и предназначен для использования в составе несущих модулей

стандартов: AdvancedMC

Субмодуль построен на базе 16-ти разрядныхЦАП DAC5878 фирмы Maxim, данная серия микросхем отличается низким энергопотреблением порядка 300 мВт.

Гибкая схема узла тактирования на базе ФАПЧ с малошумящим ГУН 500 МГц, управляемая

по последовательному интерфейсу SPI, позволяет работать как с источником внешнего тактирования

частотой от 10 МГц до 200 МГц, так и от встроенного высокостабильного опорного генератора с номиналом

частоты 25 МГц.

Реализованная схема синхронизации облегчает построение многоканальных систем на базе ЦАП DAC5878 фирмы Maxim, при этом поддерживается как синхронизация со стороны передней панели, либо с объединительной платы системы через разъём FMC.

Высокая производительность

Высокая пропускная способность и отличные динамические характеристики делают оптимальным использование субмодуля для широкого ряда приложений, требующих генерации сигналов сложной формы: робототехника, широкополосные системы связи, радиолокация, измерительная техника и т. д.

Аналоговая полоса тракта

Области применения

Основное предназначение субмодуля: широкополосные системы связи, радиолокация, измерительная техника и т. д.

ОЦЕНКА АНАЛОГО-ЦИФРОВОГО ПРЕОБРАЗОВАТЕЛЯ AD9265 [Analog Devices Wiki] доступный.

Содержание

ОЦЕНКА АНАЛОГО-ЦИФРОВОГО ПРЕОБРАЗОВАТЕЛЯ AD9265

Предисловие

Типовая схема измерения

Особенности

Полезные документы

Необходимое программное обеспечение

Файлы дизайна и интеграции

Необходимое оборудование

Начало работы

Настройка платы

Использование программного обеспечения для тестирования

Настройка захвата данных АЦП

Оценка и испытание

Настройка программного обеспечения контроллера SPI

Регулировка амплитуды входного сигнала

Тестирование дополнительных плат AD9265

Советы по устранению неполадок

Предисловие

В этом руководстве пользователя описывается оценочная плата AD9265-FMC-125EBZ, которая используется для оценки следующего продукта Analog Devices, Inc. : AD9265. Эти оценочные платы обеспечивают все схемы поддержки, необходимые для работы этих частей в их различных режимах и конфигурациях. Также описывается прикладное программное обеспечение, используемое для взаимодействия с устройствами.

: AD9265. Эти оценочные платы обеспечивают все схемы поддержки, необходимые для работы этих частей в их различных режимах и конфигурациях. Также описывается прикладное программное обеспечение, используемое для взаимодействия с устройствами.

Спецификация AD9265 содержит дополнительную информацию, и ее следует учитывать при использовании оценочной платы. Все документы и программные инструменты доступны на www.analog.com/sdp. Для получения дополнительной информации или вопросов отправьте электронное письмо по адресу [email protected].

Типовая схема измерения

Рисунок 1. Подключение оценочной платы — AD9265-FMC-125EBZ (слева) и

EVAL-SDP-Ch2Z SDP-h2 (справа)

Характеристики

Полнофункциональная оценочная плата для AD9265.

Интерфейс SPI для настройки и управления

Внешний, встроенный генератор и опции синхронизации AD9517

Балун/трансформатор или усилитель входного сигнала, опция

Регулятор LDO или импульсный блок питания

Интерфейсы программного обеспечения контроллера VisualAnalog® и SPI

Полезная документация

Спецификация AD9265

EVAL-SDP-Ch2Z, Плата высокоскоростного контроллера SDP-h2 для платформы разработки систем

AN-905 Замечания по применению, VisualAnalog Converter Evaluation Tool, версия 1.

0. Руководство пользователя

0. Руководство пользователя AN-878 Замечания по применению, Высокоскоростной АЦП SPI Программное обеспечение управления

AN-877 Замечание по применению, Взаимодействие с высокоскоростными АЦП через SPI

Рекомендации по применению AN-835, Общие сведения о тестировании и оценке АЦП

Руководство пользователя UG-074, Руководство пользователя для оценочной платы FIFO5 AD9265

Необходимое программное обеспечение

Контроллер SPI

Визуальный аналог

Схемы: AD9265-FMC-125EBZ RevA

Схема: AD9265-FMC-125EBZ RevA

Список материалов: AD9265-FMC-125EBZ RevA

Файл программы FPGA: ad9265_sdph2.bin

Необходимое оборудование

Источник аналогового сигнала (желательно генератор сигналов SMA 100A)

Сглаживающий фильтр

Источник тактового сигнала выборки (если не используется встроенный генератор)

Блок питания 12 В

Кабель SMA длиной 1 метр

ПК под управлением Windows®

Кабель USB – Mini-B

Плата AD9265-FMC-125EBZ

Комплект платформы разработки системы EVAL-SDP-Ch2Z

Начало работы

В этом разделе приведены процедуры быстрого запуска для использования платы AD9265-FMC-125EBZ. Описаны как стандартные, так и дополнительные настройки.

Описаны как стандартные, так и дополнительные настройки.

Настройка платы

Перед использованием программного обеспечения для тестирования настройте оценочную плату следующим образом:

Подключите оценочную плату к плате сбора данных, как показано на рис. 1.

Подключите один импульсный источник питания 12 В к плате EVAL-SDP-Ch2Z SDP-h2.

Подключите плату EVAL-SDP-Ch2Z SDP-h2 к ПК с помощью кабеля USB . (Подключить к J1)

При использовании встроенных часов на плате подключите контакты 1 и 3 к разъему P2.

На оценочной плате АЦП используйте генератор чистых сигналов с низким фазовым шумом для подачи входного сигнала на входной канал (J100). Для подключения генератора сигналов используйте экранированный коаксиальный кабель RG-58, 50 Ом, 1 м : Для достижения наилучших результатов используйте узкополосный полосовой фильтр с 50-омными оконечными нагрузками и соответствующей центральной частотой.

(Analog Devices использует полосовые фильтры TTE, Allen Avionics и K & L)

(Analog Devices использует полосовые фильтры TTE, Allen Avionics и K & L)При использовании внешнего тактового сигнала отсоедините разъем P2 и подключите генератор чистого сигнала к J201.

Использование программного обеспечения для тестирования

Настройка захвата данных АЦП

После настройки платы настройте сбор данных АЦП, выполнив следующие действия:

Запустить Visual Analog.

Рисунок 2. VisualAnalog, кнопка «Пуск»

Выберите AD9265 и дважды щелкните FFT

Рисунок 3. VisualAnalog, новое окно холста

Нажмите «Настройки» в разделе «Сбор данных АЦП».

Рисунок 4. VisualAnalog, секция захвата данных АЦП

Установите устройство на AD9265.

Перейдите к плате захвата и просмотрите папку с файлами для вызываемого образа FPGA. (ad9265_sdph2.bin)

Нажмите Program и проверьте, горит ли LED0 на SDP-h2. Затем нажмите ОК.

Рисунок 5. VisualAnalog, настройки захвата данных АЦП

Оценка и тестирование

Настройка программного обеспечения контроллера SPI

Запуск SPIController

Рисунок 6. Кнопка запуска SPIController

Если появится сообщение «Read Test Failure», выберите «Игнорировать».

Рисунок 7. 1-й сбой теста игнорирования

Нажмите «Файл» > «Cfg Open», затем найдите файл с именем «ad9265_16bit_125MSspiR03.cfg» и дважды щелкните его.

Рисунок 8. Параметры конфигурации

Опять же, если появится сообщение «Read Test Failure», выберите «Игнорировать».

Рис. 9. Ошибка второго игнорирования теста

Щелкните Конфигурация > Диалоговое окно контроллера.

Рисунок 10. Руководство по диалоговому окну контроллера

Снимите флажок SDO Active и нажмите OK.

Рисунок 11. Настройка диалогового окна контроллера

Щелкните Считать идентификатор чипа и Считать марку чипа.

Рисунок 12. Чтение идентификатора чипа и чтение раздела Марки чипа

Вернитесь к Visual Analog и нажмите кнопку воспроизведения.

Регулировка амплитуды входного сигнала

Следующим шагом является настройка амплитуды входного сигнала для каждого канала следующим образом:

Отрегулируйте амплитуду входного сигнала так, чтобы основная частота была равна -1,0 дБ полной шкалы .

Проверьте показания Fund Power на левой панели окна VisualAnalog Graph — AD9265 Average FFT (см. рис. 13), чтобы убедиться в этом.

Проверьте показания Fund Power на левой панели окна VisualAnalog Graph — AD9265 Average FFT (см. рис. 13), чтобы убедиться в этом.Рисунок 13. Графическое окно VisualAnalog

Щелкните значок диска в окне Graph , чтобы сохранить данные графика производительности в виде файла в формате .csv.

Рисунок 14. Значок диска VisualAnalog

Тестирование дополнительных плат AD9265

Сначала отключите питание платы EVAL-SDP-Ch2Z SDP-h2 перед их заменой.

Советы по устранению неполадок

Если график БПФ выглядит ненормальным, сделайте следующее:

Если вы видите нормальный уровень шума при отключении генератора сигналов от аналогового входа, убедитесь, что вы не перегружаете АЦП. При необходимости уменьшите уровень входного сигнала.

В VisualAnalog нажмите кнопку Settings в блоке Input Formatter .

Убедитесь, что формат номера настроен на правильную кодировку (по умолчанию двоичное смещение).

Убедитесь, что формат номера настроен на правильную кодировку (по умолчанию двоичное смещение).

Если БПФ выглядит нормально, но производительность низкая, проверьте следующее:

Убедитесь, что на аналоговом входе используется соответствующий полосовой фильтр.

Убедитесь, что генераторы сигналов для часов и аналогового входа чистые (низкий фазовый шум).

Слегка измените частоту аналогового входа, если используется некогерентная выборка, или используйте когерентные частоты.

Убедитесь, что файл конфигурации SPI соответствует оцениваемому продукту.

Убедитесь, что на разъемы тактового сигнала и аналогового входа не оказывается чрезмерной нагрузки/крутящего момента.

Если окно FFT остается пустым после нажатия кнопки Run , выполните следующие действия:

Убедитесь, что оценочная плата надежно подключена к плате EVAL-SDP-Ch2Z SDP-h2.

.3

.3