Цифровые микросхемы транзисторы.

Поиск по сайту

Микросхемы ТТЛ (74…).

На рисунке показана схема самого распространенного логического элемента — основы микросхем серии К155 и ее зарубежного аналога — серии 74. Эти серии принято называть стандартными (СТТЛ). Логический элемент микросхем серии К155 имеет среднее быстродействие tзд,р,ср.= 13 нс. и среднее значение тока потребления Iпот = 1,5…2 мА. Таким образом, энергия, затрачиваемая этим элементом на перенос одного бита информации, примерно 100 пДж.

Для обеспечения выходного напряжения высокого уровня U1вых. 2,5 В в схему на рисунке потребовалось добавить диод сдвига уровня VD4, падение напряжения на котором равно 0,7 В. Таким способом была реализована совместимость различных серий ТТЛ по логическим уровням. Микросхемы на основе инвертора, показанного на рисунке (серии К155, К555, К1533, К1531, К134, К131, К531), имеют очень большую номенклатуру и широко применяются.

| ТТЛ серия | Параметр | Нагрузка | ||||

|---|---|---|---|---|---|---|

| Российские | Зарубежные | Pпот. мВт. | tзд.р. нс | Эпот. пДж. | Cн. пФ. | Rн. кОм. |

| К155 КМ155 | 74 | 10 | 9 | 90 | 15 | 0,4 |

| К134 | 74L | 1 | 33 | 33 | 50 | 4 |

| К131 | 74H | 22 | 6 | 132 | 25 | 0,28 |

| К555 | 74LS | 2 | 9,5 | 19 | 15 | 2 |

| К531 | 74S | 19 | 3 | 57 | 15 | 0,28 |

| К1533 | 74ALS | 1,2 | 4 | 4,8 | 15 | 2 |

| К1531 | 74F | 4 | 3 | 12 | 15 | 0,28 |

При совместном использовании микросхем ТТЛ высокоскоростных, стандартных и микромощных следует учитывать, что микросхемы серии К531 дают увеличенный уровень помех по шинам питания из-за больших по силе и коротких по времени импульсов сквозного тока короткого замыкания выходных транзисторов логических элементов. При совместном применении микросхем серий К155 и К555 помехи невелики.

При совместном применении микросхем серий К155 и К555 помехи невелики.

| Нагружаемый выход |

Число входов-нагрузок из серий | ||

|---|---|---|---|

| К555 (74LS) | К155 (74) | К531 (74S) | |

| К155, КM155, (74) | 40 | 10 | 8 |

| К155, КM155, (74), буферная | 60 | 30 | 24 |

| К555 (74LS) | 20 | 5 | 4 |

| К555 (74LS), буферная | 60 | 15 | 12 |

| К531 (74S) | 50 | 12 | 10 |

| К531 (74S), буферная | 150 | 37 | 30 |

Выходы однокристальных, т.

| Параметр | Условия измерения | К155 | К555 | К531 | К1531 | |||||||

|---|---|---|---|---|---|---|---|---|---|---|---|---|

Мин. |

Тип. | Макс. | Мин. | Тип. | Макс. | Мин. | Тип. | Макс. | Мин. | Макс. | ||

| U1вх, В схема |

U1вх или U0вх Присутствуют на всех входах | 2 | 2 | 2 | 2 | |||||||

| U0вх, В схема |

0,8 | 0,8 | 0,8 | |||||||||

| U0вых, В схема | Uи.п.= 4,5 В | 0,4 | 0,35 | 0,5 | 0,5 | 0,5 | ||||||

| I0вых= 16 мА | I0вых= 8 мА | I0вых= 20 мА | ||||||||||

| U1вых, В схема |

Uи. п.= 4,5 В п.= 4,5 В |

2,4 | 3,5 | 2,7 | 3,4 | 2,7 | 3,4 | 2,7 | ||||

| I1вых= -0,8 мА | I1вых= -0,4 мА | I1вых= -1 мА | ||||||||||

| I1вых, мкА с ОК схема | U1и.п.= 4,5 В, U1вых=5,5 В | 250 | 100 | 250 | ||||||||

| I1вых, мкА Состояние Z схема |

U1и.п.= 5,5 В, U1вых= 2,4 В на входе разрешения Е1 Uвх= 2 В | 40 | 20 | 50 | ||||||||

| I0вых, мкА Состояние Z схема |

U1и. |

-40 | -20 | -50 | ||||||||

| I1вх, мкА схема | U1и.п.= 5,5 В, U1вх= 2,7 В | 40 | 20 | 50 | 20 | |||||||

| I1вх, max, мА | U1и.п.= 5,5 В, U1вх= 10 В | 1 | 0,1 | 1 | 0,1 | |||||||

| I0вх, мА схема |

U1и.п.= 5,5 В, U0вх= 0,4 В | -1,6 | -0,4 | -2,0 | -0,6 | |||||||

Iк. з., мА з., мА | U1и.п.= 5,5 В, U0вых= 0 В | -18 | -55 | -100 | -100 | -60 | -150 | |||||

Микросхемы счётчиков КМОП-логики – Я Студик

Цифровые микросхемы ТТЛ-серий обеспечивают построение самых различных цифровых устройств, работающих на частотах до

80 МГц, однако их существенными недостатками являются большая потребляемая мощность и низкая помехозащищѐнность. Последнее имеет важное значение при разработке систем автоматизации технологических процессов. В большинстве случаев этим системам не нужно такое высокое быстродействие, а требуется высокая помехозащищѐнность. Немаловажным параметром, с точки зрения экономической эффективности, является низкая потребляемая мощность.

Именно по этой причине современные системы автоматизации выполняются в основном на микросхемах КМОП–технологий. Поэтому рассмотрим более подробно счѐтчики, выполненные именно по этой технологии.

Поэтому рассмотрим более подробно счѐтчики, выполненные именно по этой технологии.

Микросхема К176ИЕ1 шестиразрядный двоичный счетчик, работающий в коде 1-2-4-8-16-32. Микросхема имеет два входа: вход R установки триггеров счетчика в ноль и вход С вход для подачи счетных импульсов. Установка в ноль происходит при подаче логической единицы на вход R. Переключение триггеров микросхемы происходит по спаду импульсов, подаваемых на вход С. При построении многоразрядных счѐтчиков или делителей частоты входы С последующих микросхем следует подключать к выходам 32 предыдущих.

Рис. 14. Микросхема К176ИЕ1

Рис. 15. Микросхема К176ИЕ2

Микросхема К176ИЕ2 пятиразрядный счетчик, который может работать как двоичный в коде 1-2-4-8-16 при подаче логической единицы на управляющий вход А, или как декада с подключенным к выходу декады триггером при логическом нуле на входе А. Во втором случае код работы счетчика 1-2-4-8-10, общий коэффициент деления 20. Вход R служит для установки триггеров счетчика в 0 подачей на этот вход логической 1.

Первые четыре триггера счетчика могут быть установлены в единичное состояние подачей логической единицы на входы S1 … S8, причѐм эти входы являются приоритетными над входом R.

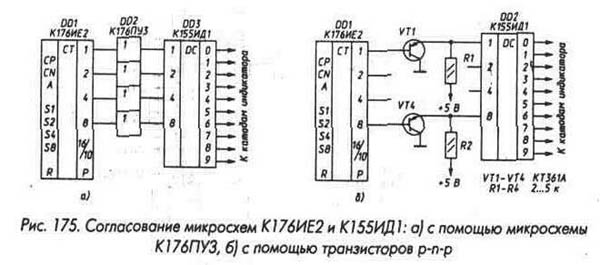

Микросхема К176ИЕ2 встречается двух разновидностей. Одна из разновидностей имеет входы СР и CN для подачи тактовых импульсов положительной и отрицательной полярности соответственно, включенные по ИЛИ. При подаче на вход СР импульсов положительной полярности на входе CN должна быть логическая единица, при подаче на вход CN импульсов отрицательной полярности на входе СР должен быть логический ноль. В обоих случаях счетчик переключается по спадам импульсов.

Другая разновидность имеет два равноправных входа для подачи тактовых импульсов (выводы 2 и 3), собранных по И. Счет происходит по спадам импульсов положительной полярности, подаваемых на любой из этих входов, причем на второй из этих входов должна быть подана логическая единица. Можно подавать импульсы и на объединенные выводы 2 и 3.

Если на вывод 3 микросхемы К176ИЕ2 подать логическую единицу, обе разновидности микросхем по входу СР (вывод 2) работают одинаково.

При логическом нуле на входе А порядок работы триггеров соответствует временной диаграмме, приведенной на рис. 16.

Рис. 16. Временная диаграмма работы микросхемы К176ИЕ2

В этом режиме на выходе Р, представляющем собой выход элемента «И-НЕ», входы которого подключены к выходам 1 и 8 счетчика, выделяются импульсы отрицательной полярности, фронты которых совпадают со спадом каждого девятого входного импульса, спады со спадом каждого десятого.

При соединении микросхем К176ИЕ2 в многоразрядный счетчик входы СР последующих микросхем следует подключать к выходам 8 или 16/10 непосредственно, на входы CN подавать логическую единицу.

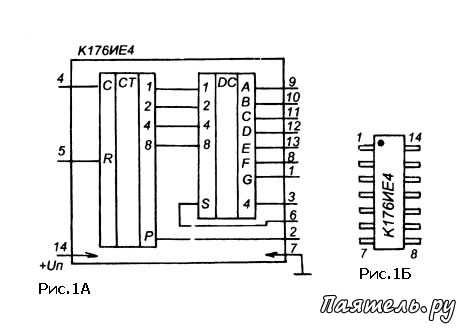

Микросхемы К176ИЕЗ и К176ИЕ4 разработаны специально для использования в электронных часах с семисегментными индикаторами.

Рис. 17. Микросхемы К176ИЕЗ и К176ИЕ4

Микросхемы имеют три входа вход R, установка триггеров счетчика в ноль, которая происходит при подаче логической единицы на этот вход, вход С – входные импульсы, переключение триггеров происходит по спаду импульсов. Сигнал на входе S управляет полярностью выходных сигналов.

Сигнал на входе S управляет полярностью выходных сигналов.

На выходах а, b, с, d, e, f, g выходные сигналы, обеспечивающие формирование цифр на семисегментном индикаторе, соответствующих состоянию счетчика. При подаче логического нуля на управляющий вход S логическая единица на выходах а, b, с, d, e, f, g соответствует включению соответствующего сегмента. Если же на вход S подать логическую единицу, включению сегментов будет соответствовать логический ноль на выходах а, b, с, d, e, f, g. Возможность переключения полярности выходных сигналов существенно расширяет область применения микросхем. Выход Р микросхемы выход переноса.

Микросхема К176ИЕЗ имеет коэффициент пересчета 6, т.е. спад имульса на выходе Р происходит при переходе счѐтчика из состояния 6 в состояние 0. Кроме того логическая единица на выходе

2 появляется при установке счетчика в состояние 2.

Микросхема К176ИЕ4 представляет собой декаду. Спад импульса на выходе Р формируется в момент перехода счетчика из состояния 9 в состояние 0, а логическая единица на выходе 4 появляется при установке счетчика в состояние 4.

Следует иметь в виду, что разводка выводов а, b, с, d, e, f, g в паспорте микросхемы и в некоторых справочниках приведена для нестандартного расположения сегментов индикаторов. На рис. 17 дана разводка выводов для стандартного расположения сегментов.

Микросхема К176ИЕ5 содержит кварцевый генератор с внешним резонатором на 32768 Гц и подключенным к нему девятиразрядным делителем частоты и шестиразрядный делитель частоты, структура микросхемы и типовая схема включения приведена на рисунке 18. К выводам Z и Z подключаются кварцевый резонатор, резисторы R1 и R2, конденсаторы С1 и С2. Выходной сигнал кварцевого генератора может быть проконтролирован на выходах K и K .

Сигнал с частотой 32768 Гц поступает на вход девятиразрядного

двоичного делителя частоты, с его выхода 9 сигнал с частотой 64 Гц может быть подан на вход 10 шестиразрядного делителя. На выходе 14 пятого разряда этого делителя формируется частота 2 Гц, на выходе 15 шестого разряда 1 Гц.

Рис. 18. Микросхема К176ИЕ5

18. Микросхема К176ИЕ5

Сигнал с частотой 64Гц может использоваться для подключения жидкокристаллических индикаторов к выходам микросхем К176ИЕЗ и К176ИЕ4. Вход R служит для сброса триггеров второго делителя и установки исходной фазы колебаний на выходах микросхемы. При подаче логической единицы на вход R на выходах 14 и

15 – логический ноль, после снятия логической единицы на этих выходах появляются импульсы с соответствующей частотой, спад первого импульса на выходе 15 происходит через 1с после снятия логической единицы.

При подаче логической единицы на вход S происходит установка всех триггеров второго делителя в состояние логической единицы, после снятия логической единицы с этого входа спад первого импульса на выходах 14 и 15 происходит практически сразу. Обычно вход S постоянно подключают к общему проводу.

Конденсаторы С1 и С2 служат для точной установки частоты кварцевого генератора. Емкость первого из них может находиться в пределах от единиц до ста пикофарад, емкость второго – 30 … 100 пФ. При увеличении емкости конденсаторов частота генерации уменьшается. Точную установку частоты удобнее производить при помощи подстроечных конденсаторов, подключенных параллельно С1 и С2. При этом конденсатором, подключенным параллельно С2, осуществляют грубую настройку, подключенным параллельно С1 точную.

При увеличении емкости конденсаторов частота генерации уменьшается. Точную установку частоты удобнее производить при помощи подстроечных конденсаторов, подключенных параллельно С1 и С2. При этом конденсатором, подключенным параллельно С2, осуществляют грубую настройку, подключенным параллельно С1 точную.

Сопротивление резистора R1 может находиться в пределах

4,7…68 МОм, однако при его значении менее 10 МОм возбуждаются не все кварцевые резонаторы.

Рис. 19. Микросхема К176ИЕ5

На микросхеме К176ИЕ5 можно выполнить ждущий мультивибратор, обладающий большой выдержкой вырабатываемого импульса.

Работа этого ждущего мультивибратора основана на задержке времени, которая обеспечивается подсчѐтом импульсов, вырабатываемых генератором.

Генератор выполнен на инверторах, предназначенных для кварцевого генератора микросхемы. Для запрета его работы логическая единица с выхода 15 микросхемы подается на вход цепочки инверторов генератора через диод VD1. При подаче импульса на

вход запуска логический ноль с выхода 15 микросхемы закрывает диод VD1, и он не мешает нормальной работе генератора.

Длительность формируемого импульса составляет 214 периода задающего генератора, который задаѐтся параметрами элементов R1, С1.

На выходе 14 счетчика формируется импульс положительной полярности вдвое меньшей длительности, на выходе 9 пачка из 32 импульсов.

Микросхемы К176ИЕ8 и К561ИЕ8 десятичные счетчики Джонсона с дешифратором. Микросхемы имеют три входа вход установки исходного состояния R, вход для подачи счетных импульсов отрицательной полярности CN и вход для подачи счетных импульсов положительной полярности СР. Установка счетчика в 0 происходит при подаче на вход R логической единицы, при этом на выходе 0 появляется логическая единица, а на выходах 1 … 9 – логический ноль.

Рис. 20. Микросхема К176ИЕ8

Переключение счетчика происходит по спадам импульсов отрицательной полярности, подаваемых на вход CN, при этом на входе СР должен быть логический ноль. Можно также подавать импульсы положительной полярности на вход СР, переключение будет происходить по их спадам. На входе CN при этом должна быть логическая единица. Временная диаграмма работы микросхемы приведена на рис. 21.

На входе CN при этом должна быть логическая единица. Временная диаграмма работы микросхемы приведена на рис. 21.

Микросхема К561ИЕ9 счетчик с дешифратором, работа которой аналогична работе микросхем К561ИЕ8 и К176ИЕ8, но коэффициент пересчета и число выходов дешифратора 8, а не 10.

Рис. 21. Временная диаграмма работы микросхемы

Рис. 22. Микросхема К561ЕИ9

Так же, как и микросхема К561ИЕ8, данная микросхема является счѐтчиком Джонсона (т.е. построена на основе сдвигающего регистра с перекрестными связями). При подаче напряжения питания и отсутствии импульса сброса триггеры этих микросхем могут установиться в произвольное состояние, не соответствующее разрешенному состоянию счетчика. Однако в указанных микросхемах есть специальная цепь формирования разрешенного состояния счетчика, и при подаче тактовых импульсов счетчик через несколько тактов перейдет в нормальный режим работы. Поэтому в делителях частоты, в которых точная фаза выходного сигнала неважна, допустимо не подавать на входы R микросхем К176ИЕ8, К561ИЕ8 и К561ИЕ9 импульсы начальной установки.

Временная диаграмма работы микросхемы приведена на рис. 23.

Рис. 23. Временная диаграмма работы микросхемы

Микросхемы К176ИЕ8, К561ИЕ8, К561ИЕ9 можно объединять в многоразрядные счетчики с последовательным переносом, соединяя выход переноса Р предыдущей микросхемы с входом CN последующей и подавая на вход СР логический ноль. Возможно также соединение старшего выхода дешифратора (7 или 9) со входом СР следующей микросхемы и подача на вход CN логической единицы. Однако такие способы соединения приводят к накоплению задержек в многоразрядном счетчике. Максимальная рабочая частота многоразрядных счетчиков не снижается относительно частоты работы отдельной микросхемы.

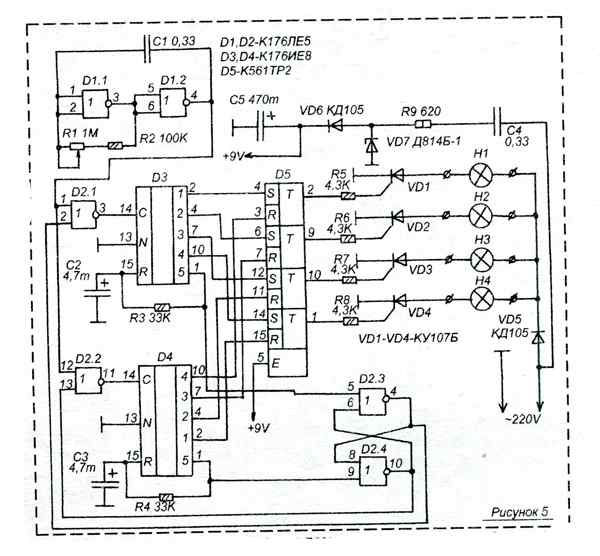

На рис. 24 приведена схема таймера с использованием микросхем К176ИЕ8 или К561ИЕ8.

В момент пуска на вход CN микросхемы DD1 начинают поступать счетные импульсы. Когда микросхемы счетчика установятся в положения, набранные на переключателях SA1, SA2, на всех входах элемента «И-НЕ» DD3 получается логическая единица, что приведет к появлению логической единицы на выходе инвертора DD4, сигнализирующей об окончании заданного временного интервала.

Микросхемы К561ИЕ8 и К561ИЕ9 удобно использовать в делителях частоты с переключаемым коэффициентом деления. На рис. 25 приведен пример двухдекадного делителя частоты. Переключателем SA1 устанавливают единицы необходимого коэффициента пересчета, переключателем SA2 десятки. При достижении счетчиками DD1, DD2

состояния, соответствующего положениям переключателей, на все входы элемента DD3.1 приходит логическая единица.

Рис. 24. Схема таймера с использованием микросхем К176ИЕ8 или К561ИЕ8

Благодаря этому триггер на элементах DD3.2 и DD3.3 устанавливается в состояние, при котором на выходе элемента DD3.3 появляется логическая единица, сбрасывающая счетчики DD1, DD2 в исходное состояние. В результате на выходе элемента DD3.1 также получается логическая единица, и следующий входной импульс устанавливает триггер DD3.2, DD3.3 в исходное состояние, сигнал сброса со входов R микросхем DD1, DD2 снимается, и описанная выше процедура повторяется.

Триггер на элементах DD3. 2 и DD3.3 гарантирует сброс микросхем DD1, DD2 при достижении счетчиком нужного состояния. При его отсутствии и большом разбросе порогов переключения микросхем DD1, DD2 по входам R возможен случай, когда одна из этих микросхем устанавливается в 0 и снимает сигнал сброса со входов R остальных микросхем ранее, чем сигнал сброса достигнет порога их переключения. Однако такой случай маловероятен, и обычно можно обойтись без триггера, точнее, без элемента DD3.2.

2 и DD3.3 гарантирует сброс микросхем DD1, DD2 при достижении счетчиком нужного состояния. При его отсутствии и большом разбросе порогов переключения микросхем DD1, DD2 по входам R возможен случай, когда одна из этих микросхем устанавливается в 0 и снимает сигнал сброса со входов R остальных микросхем ранее, чем сигнал сброса достигнет порога их переключения. Однако такой случай маловероятен, и обычно можно обойтись без триггера, точнее, без элемента DD3.2.

Рис. 25. Двухдекадный делитель частоты

Для получения коэффициента пересчета менее 10 для микросхемы К561ИЕ8 и менее 8 для К561ИЕ9 можно соединить выход дешифратора с номером, соответствующим необходимому коэффициенту пересчета, со входом R микросхемы непосредственно.

Микросхемы К561ИЕ10 и КР1561ИЕ10 содержат по два раздельных четырехразрядных двоичных счетчика, каждый из которых имеет входы СР, CN, R.

Установка триггеров счетчиков в исходное состояние происходит при подаче на вход R логической единицы. Логика работы входов СР и CN отлична от работы аналогичных входов микросхем К561ИЕ8 и К561ИЕ9. Триггеры микросхем К561ИЕ10 и КР1561ИЕ10 срабатывают по спаду импульсов на входе СР при логическом нуле на входе CN (для К561ИЕ8 и К561ИЕ9 на входе CN должна быть логическая единица).

Логика работы входов СР и CN отлична от работы аналогичных входов микросхем К561ИЕ8 и К561ИЕ9. Триггеры микросхем К561ИЕ10 и КР1561ИЕ10 срабатывают по спаду импульсов на входе СР при логическом нуле на входе CN (для К561ИЕ8 и К561ИЕ9 на входе CN должна быть логическая единица).

|

Рис. 26. Микросхема К561ИЕ10

Возможна работа по фронтам импульсов на входе CN, при этом на входе СР должна быть логическая единица (для К561ИЕ8 и К561ИЕ9 – логический ноль). Таким образом, входы СР и CN в микросхемах К561ИЕ10 и КР1561ИЕ10 объединены по схеме элемента

«И», а в микросхемах К561ИЕ8 и К561ИЕ9 – по «ИЛИ».

При соединении микросхем в многоразрядный счетчик с последовательным переносом выходы 8 предыдущих счетчиков соединяют со входами СР последующих, а на входы CN подают логический ноль.

Один счетчик микросхемы может быть использован для построения делителей частоты с коэффициентом деления от 2 до 16. Для примера на рис. 27 приведена схема счетчика с коэффициентом пересчета 10.

Для примера на рис. 27 приведена схема счетчика с коэффициентом пересчета 10.

Для получения коэффициентов пересчета 3, 5, 6, 9,12 можно воспользоваться той же схемой, соответствующим образом выбрав выходы счетчика для подключения ко входам DD2.1. Для получения коэффициентов пересчета 7, 11, 13, 14 элемент DD2.1 должен иметь три входа, для коэффициента 15 четыре входа.

Рис. 27. Схема счетчика с коэффициентом пересчета

Рис. 28. Микросхема К567ИЕ11

Микросхема К561ИЕ11 – двоичный четырѐхразрядный реверсивный счѐтчик.

Входы, выходы и режимы работы этой микросхемы были рассмотрены в разделе, посвящѐнном реверсивным счѐтчикам, поэтому остановимся только на каскадировании.

Для соединения микросхем в счетчик с последовательным переносом необходимо объединить между собой все входы С, выходы Р микросхем соединить со входами P1 следующих, а на вход P1 младшего разряда подать логический ноль. Выходные сигналы всех микросхем счетчика изменяются одновременно, однако максимальная частота работы счетчика меньше, чем отдельной микросхемы из-за накопления задержек в цепи переноса.

Особенности построения микросхемы К561ИЕ11 требуют, чтобы изменение сигнала направления счета на входе U происходило в паузе между счетными импульсами на входе С, то есть при логической единице на этом входе, или по спаду этого импульса.

Рис. 29. Схема счетчика

Рис. 30. Микросхема К176ИЕ12

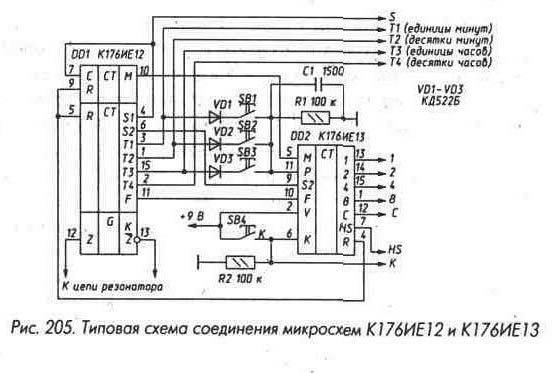

Микросхема К176ИЕ12 предназначена для использования в электронных часах или других устройствах, функционирующих по временным параметрам.

В ее состав входят кварцевый генератор G с внешним кварцевым резонатором на частоту 32768 Гц и два делителя частоты на

32768 и на 60.

При подключении к микросхеме кварцевого резонатора, по приведѐнной схеме, она обеспечивает получение частот 32768,

1024, 128, 2, 1, 1/60Гц. Импульсы с частотой 128Гц формируются на выходах микросхемы Т1 … Т4, их скважность равна 4, сдвинуты они между собой на четверть периода. Эти импульсы предназначены для коммутации знакомест индикатора часов при динамической индикации. Импульсы с частотой 1/60Гц подаются на счетчик минут, импульсы с частотой 1Гц могут использоваться для подачи на счетчик секунд и для обеспечения мигания разделительной точки, для установки показаний часов могут использоваться импульсы с частотой 2Гц. Частота 1024Гц предназначена для звукового сигнала будильника и для опроса разрядов счетчиков при динамической индикации, выход частоты 32768 Гц контрольный.

Импульсы с частотой 1/60Гц подаются на счетчик минут, импульсы с частотой 1Гц могут использоваться для подачи на счетчик секунд и для обеспечения мигания разделительной точки, для установки показаний часов могут использоваться импульсы с частотой 2Гц. Частота 1024Гц предназначена для звукового сигнала будильника и для опроса разрядов счетчиков при динамической индикации, выход частоты 32768 Гц контрольный.

Особенностью работы микросхемы является то, что первый спад на выходе минутных импульсов М появляется спустя 59 с после снятия сигнала установки нуля с входа R. Это заставляет при пуске часов отпускать кнопку, формирующую сигнал установки нуля, спустя одну секунду после шестого сигнала поверки времени. Фронты и спады сигналов на выходе М синхронны со спадами импульсов на входе С.

Сопротивление резистора R1 может иметь ту же величину, что и для микросхемы К176ИЕ5. Конденсатор С3 служит для точной подстройки частоты, С4 для грубой. В большинстве случаев конденсатор С2 может быть исключен.

Микросхема К176ИЕ13 предназначена для построения электронных часов с будильником. Она содержит счетчики минут и часов, регистр памяти будильника, цепи сравнения и выдачи звукового сигнала, цепи динамической выдачи кодов цифр для подачи на индикаторы. Обычно микросхема К176ИЕ13 используется совместно с К176ИЕ12.

Микросхема К561ИЕ14 двоичный и двоично-десятичный четырехразрядный счетчик.

Принцип его работы практически полностью повторяет принцип работы микросхемы К561ИЕ11. Отличие заключается в замене входа R на вход В вход переключения модуля счета.

Рис. 31. Микросхема К561ИЕ14

При логической единице на входе В микросхема К561ИЕ14 производит двоичный счет, так же, как и К561ИЕ11, при логическом нуле на входе В осуществляется двоично–десятичный счѐт. Назначение остальных входов, режимы работы и правила включения для этой микросхемы такие же, как и для К561ИЕ11.

Микросхема К561ИЕ16 14-разрядный двоичный счетчик с последовательным переносом.

Рис. 32. Микросхема К561ИЕ16

32. Микросхема К561ИЕ16

У микросхемы имеются два входа вход установки начального состояния R и вход для подачи тактовых импульсов С. Установка триггеров счетчика в 0 производится при подаче на вход R логической единицы, счет по спадам импульсов, подаваемых на вход С.

Счетчик имеет выходы не всех разрядов отсутствуют выходы разрядов 2 и 4, поэтому, если необходимо иметь сигналы со всех двоичных разрядов счетчика, следует использовать еще один счетчик, работающий синхронно и имеющий выходы 1, 2, 4, 8, например половину микросхемы К561ИЕ10.

Коэффициент деления одной микросхемы К561ИЕ16 составляет 214 = 16384, при необходимости получения большего коэффициента деления можно выход 8192 микросхемы соединить со входом еще одной такой же микросхемы или со входом СР любой другой микросхемы счетчика. Если вход второй микросхемы К561ИЕ16 подключить к выходу 1024 предыдущей, можно за счет уменьшения разрядности счетчика получить недостающие выходы двух разрядов второй микросхемы как показано на рис. 33.

33.

Подключая ко входу микросхемы К561ИЕ16 половину микросхемы К561ИЕ10, можно не только получить недостающие выходы, но и увеличить разрядность счетчика на единицу, что позволяет и обеспечить коэффициент деления 215 = 32768.

Рис. 33. Выходы двух разрядов

Рис. 34. Микросхема К561ИЕ16

Рис. 35. Микросхема К561ИЕ10

Микросхема К176ИЕ17 представляет собой календарь. Она содержит счѐтчик дней недели, чисел месяца и месяцев.

Рис. 36. Микросхема К561ИЕ19

Микросхема К176ИЕ18 по своему построению во многом напоминает К176ИЕ12. Ее основным отличием является выполнение выходов Т1 … Т4 с открытым стоком, что позволяет подключать сетки вакуумных люминесцентных индикаторов к этой микросхеме без согласующих ключей. Кроме того данная микросхема имеет специальный формирователь звукового сигнала, выход которого выполнен с открытым стоком и позволяет подключать излучатели с сопротивлением 50Ом и выше между этим выходом и плюсом питания без эмиттерного повторителя.

Микросхемы К176ИЕ12, К176ИЕ13, К176ИЕ17, К176ИЕ18 допускают напряжение питания такое же, как и микросхемы серии К561 – от 3 до 15В.

Микросхема К561ИЕ19 пятиразрядный сдвигающий регистр с возможностью параллельной записи информации, предназначенный для построения счетчиков с программируемым модулем счета.

Микросхема имеет пять информационных входов для параллельной записи D1 … D5, вход информации для последовательной записи D0, вход параллельной записи S, вход сброса R, вход для подачи тактовых импульсов С и пять инверсных выходов 1 … 5.

Вход R является преобладающим при подаче на него логической единицы все триггеры микросхемы устанавливаются в ноль, на всех выходах появляется логическая единица независимо от сигналов на других входах. При подаче на вход R логического нуля, а на вход S логической единицы происходит запись информации со входов D1 … D5 в триггеры микросхемы, на выходах 1 … 5 она появляется в инверсном виде.

При подаче на входы R и S логического нуля возможен сдвиг информации в триггерах микросхемы, который будет происходить по спадам импульсов, поступающих на вход С. В первый триггер информация будет записываться со входа D0.

В первый триггер информация будет записываться со входа D0.

Если соединить вход DO с одним из выходов 1 … 5, можно получить счетчик с коэффициентом пересчета 2, 4, 6, 8, 10. Для примера на рисунке 38 показана временная диаграмма работы микросхемы в режиме деления на 6, которая организуется в случае соединения входа D0 с выходом 3.

Рис. 37. Временная диаграмма работы микросхемы в режиме деления

Если необходимо получить нечетный коэффициент пересчета

3, 5, 7 или 9, следует использовать двухвходовый элемент И, входы которого подключить соответственно к выходам 1 и 2, 2 и 3, 3 и 4, 4 и 5, в выход ко входу D0. Для примера на рисунке 38 приведена схема делителя частоты на 5 и временная диаграмма его работы.

Следует иметь в виду, что использование микросхемы К561ИЕ19 в качестве сдвигающего регистра невозможно, так как она содержит цепи коррекции, в результате чего комбинации состояний триггеров, не являющиеся рабочими для счетного режима, автоматически исправляются. Наличие цепей коррекции позволяет аналогично использованию микросхем К561ИЕ8 и К561ИЕ9 не подавать импульс начальной установки на счетчик, если фаза выходных импульсов не важна.

Наличие цепей коррекции позволяет аналогично использованию микросхем К561ИЕ8 и К561ИЕ9 не подавать импульс начальной установки на счетчик, если фаза выходных импульсов не важна.

Микросхема КР1561ИЕ20 двенадцатиразрядный двоичный счетчик с коэффициентам деления 212 = 4096.

Рис. 38. Схема делителя частоты на 5 и временная диаграмма работы

Рис. 39. Микросхема КР1561ИЕ20

У нее два входа R (для установки нулевого состояния) и С (для подачи тактовых импульсов). При логической единице на входе R счетчик устанавливается в нулевое состояние, а при логическом нуле считает по спадам поступающих на вход С импульсов.

Микросхема во многом повторяет микросхему К561ИЕ16, поэтому еѐ можно использовать для деления частоты на коэффициенты, являющиеся степенью числа 2.

Рис. 40. Микросхема КР1561ИЕ21

Микросхема КР1561ИЕ21 синхронный двоичный счетчик с возможностью параллельной записи информации по спаду тактового импульса.

Подача логического нуля на вход R независимо от состояния других входов приводит к установке триггеров микросхемы в состояние нуля. Для обеспечения режима счета на входе R необходимо подать логическую единицу, тот же сигнал должен быть подан на входы разрешения параллельной записи EL, разрешения ЕС, разрешения выдачи сигнала переноса ЕР.

Для обеспечения режима счета на входе R необходимо подать логическую единицу, тот же сигнал должен быть подан на входы разрешения параллельной записи EL, разрешения ЕС, разрешения выдачи сигнала переноса ЕР.

Изменение состояния триггеров счетчика при счете происходит по фронту импульсов, подаваемых на вход С. При подаче логического нуля на вход EL микросхема переходит в режим параллельной записи информации со входов D1 … D8. Запись происходит по фронтам импульсов на входе С, что позволяет использовать микросхему в режиме сдвигающего регистра. При записи на входе R должна быть логическая единица, сигналы на входах ЕС и ЕР произвольны.

На выходе переноса Р логическая единица появляется в том случае, когда счетчик находится в состоянии 9, а на входе ЕР – логическая единица, в остальных случаях на выходе Р логический ноль. Подача логического нуля на вход ЕР запрещает выдачу логической единицы на выходе Р и счет импульсов. Подача логического нуля на вход ЕС запрещает счет, но не запрещает выдачу сигнала переноса. Сигнал запрета счета (логический ноль на входах ЕС и ЕР) действует лишь в том случае, если он полностью перекрывает по длительности импульс на входе С, в том числе он может совпадать с ним по времени.

Сигнал запрета счета (логический ноль на входах ЕС и ЕР) действует лишь в том случае, если он полностью перекрывает по длительности импульс на входе С, в том числе он может совпадать с ним по времени.

Для обеспечения параллельной записи на вход EL необходимо подать логический ноль. Информация на входы D1 … D8 может быть подана как при логической единице, так и при логическом нуле на входе С и удерживаться до момента перехода логического нуля на входе С в логическую единицу, когда и произойдет запись.

Для обеспечения счета с числа, введенного в микросхему при параллельной записи, логический ноль на входе EL должен быть изменен на логическую единицу или одновременно с переходом логического нуля в логическую единицу на входе С, или при логической единице на входе С.

На рис. 41 приведена схема соединения микросхем КР1561ИЕ21 в многоразрядный синхронный счетчик.

Рис. 41. Схема соединения микросхем КР1561ИЕ21 в многоразрядный синхронный счетчик

Как уже указывалось выше, микросхема КР1561ИЕ21 может работать в режиме сдвигающего регистра. Для обеспечения такого режима необходимо входы D1 … D8 соединить с выходами 1-2-4-8 в необходимом порядке. Для сдвига информации на один двоичный разряд по каждому тактовому импульсу в сторону старших разрядов соединение необходимо произвести в соответствии с рисунком 42.

Для обеспечения такого режима необходимо входы D1 … D8 соединить с выходами 1-2-4-8 в необходимом порядке. Для сдвига информации на один двоичный разряд по каждому тактовому импульсу в сторону старших разрядов соединение необходимо произвести в соответствии с рисунком 42.

Рис. 42. Схема соединения микросхем

КОНТРОЛЬНЫЕ ВОПРОСЫ

1. Что такое счетчик?

2. Классификация счетчиков в зависимости от класса цифровых автоматов и способа кодирования внутренних состояний.

3. Двоичный счетчик, его устройство, свойства, временные диаграммы работы.

4. Синхронные и асинхронные счетчики. Счетчики с параллельным и последовательным переносом.

5. Функция переходов JK-триггера, функция возбуждения Т-триггера.

6. Построение графа переходов и диаграмм Вейча для переходов функций возбуждений Т.

7. Принцип кодирования в коде 8421BCD.

8. Функции и схемная реализация двоично-десятичного счетчика.

9. Принцип кода Грея.

10. Применение канонического метода синтеза для построения счетчика

Грея.

11. Счетчики Джонсона. Свойства, таблица истинности.

12. Схемное решение и временные диаграммы работы счетчика. В чем состоит недостаток счетчиков Джонсона?

13. Реверсивные счетчики. Свойства, схемное решение.

14. Принцип работы микросхемы 561ИЕ11.

15. Программируемый делитель. Определение, свойства.

16. Специализированная микросхема КА561ИЕ15Б. Принцип работы, свойства. Как происходит процесс деления?

17. Преимущества микросхем КМОП-логики перед микросхемами ТТЛлогики.

18. Объясните принцип работы, свойства и схемное решение микросхем:

серии К176: К176ИЕ1, К176ИЕ2, К176ИЕ3, К176ИЕ4, К176ИЕ5, К176ИЕ8, К176ИЕ12, К176ИЕ13, К176ИЕ17, К176ИЕ18;

|

серии К561: К561ИЕ8, К561ИЕ9, К561ИЕ10, К561ИЕ11, К561ИЕ14, К561ИЕ16, К561ИЕ19;

серии КР1561: КР1561ИЕ10, КР1561ИЕ20, КР1561ИЕ21.