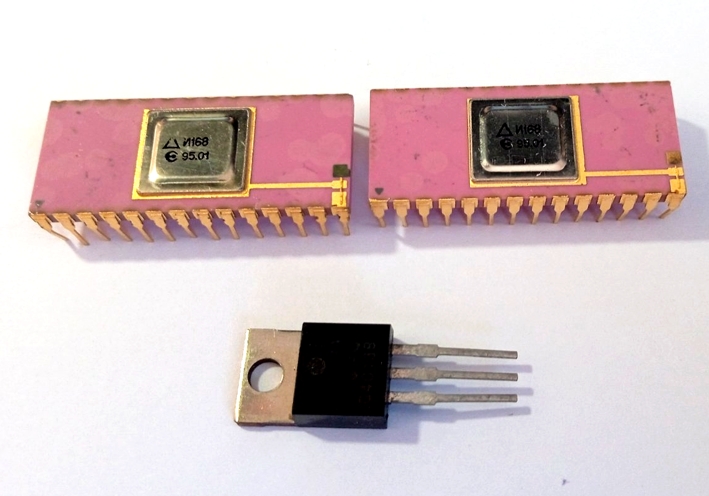

Микросхема КР580ВН59

Микросхема КР580ВН59Микросхема КР580ВН59

Микросхема КР580ВН59 -программируемый контроллер прерываний (ПКП), обслуживает до восьми запросов на прерывание микропроцессора, поступающих от внешних устройств.

Микропроцессор позволяет сократить средства программного обеспечения и реальные затраты времени при приоритетами прерываний в системах с приоритетами многих уровней. Алгоритм задания приоритета устанавливается программным путем. Приоритеты, закреплены за внешними устройствами, могут быть изменены в процессе выполнения программ.

В микросхеме предусмотрена возможность расширения числа каскадного соединения микросхем ПКП.

Назначение выводов

| Вывод | Обозначение | Тип вывода |

Функциональное назначение выводов |

| 1 | CS | Вход | Выбор микросхемы |

| 2 | WR | Вход | Запись информации |

| 3 | RD | Вход | Чтение информации |

| 4-11 | D7-D0 | Входы/выходы | Канал данных |

| 12, 13, 15 | CFS2-CAS0 | Входы/выходы | Шина каскадирования |

| 14 | GND | – | Общий |

| 16 | MS/SV | Вход | Выбор ведомой микросхемы |

| 17 | INT | Выход | Прерывание |

| 18-25 | IRQ7-IRQ0 | Вход | Запрос прерывания |

| 26 | INTA | Вход | Подтверждение прерывания |

| 27 | A0 | Вход | Адрес 0-го разряда |

| 28 | Ucc | – | Напряжение питания |

Программируемый контроллер прерываний кр580вн59 — Информатика, информационные технологии

БИС программируемого контроллера прерываний (ПКП) представляет собой устройство, реализующее до восьми уровней запросов на прерывание с возможностями программного маскирования и изменения дисциплины обслуживания прерываний. За счет каскадного включения БИС КР580ВН59 число уровней прерывания может быть расширено до 64.

За счет каскадного включения БИС КР580ВН59 число уровней прерывания может быть расширено до 64.

Упрощенная структурная схема ПКП приведена на рисунке 1,а. В состав БИС входят:

– двунаправленный 8-разрядный буфер данных (BD), предназначенный для сопряжения ПКП с системной информационной шиной;

– блок управления записью/чтением (RWCU), принимающий управляющие сигналы от МП и задающий режим функционирования ПКП;

– схема каскадного буфера-компаратора (СМР), используемая для включения в систему нескольких ПКП;

– схема управления (CU), вырабатывающая сигнал прерывания и формирующая трехбайтную команду CALL для выдачи на шину данных;

– регистр запросов прерываний (RGI), используемый для хранения всех уровней прерываний, на которые поступают запросы;

– схема принятия решений по приоритетам (PRB), индентифицирующая приоритеты запросов и выбирающая запрос с наивысшим приоритетом;

– регистр обслуживаемых прерываний (ISR), сохраняющий уровни запросов прерываний, находящихся на обслуживании ПКП;

– регистр маскирования прерываний (RGM), обеспечивающий запрещение одной или нескольких линий запросов прерывания.

Рисунок 1.

Назначения входных, выходных и управляющих сигналов ПКП приведены при описании выводов микросхемы в таблице 1.

Таблица 1. Описание выводов ПКП

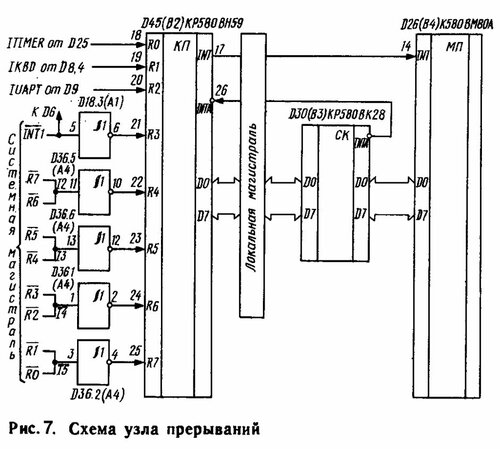

Сопряжение БИС КР580ВН59 со стандартной системой шиной показано на рисунке 1,,б.

ПКП позволяет реализовать процесс прерывания по запросам от внешних устройств или по опросу микропроцессором запросов на обслуживание внешних устройств.

При обслуживании прерываний по запросу от внешних устройств выполняется следующая последовательность операций:

1. запросы прерываний поступают на входы IR0 — IR7 и устанавливают соответствующие разряды RGI;

2. ПКП принимает запросы, оценивает их приоритеты и формирует сигнал прерывания INT;

3. МП принимает сигнал INT, если прерывания разрешены, и подтверждает прием выдачей сигнала INTA;

4. после получения сигнала INТА ПКП устанавливает разряд регистра ISR, соответствующий запросу с наивысшим приоритетом, сбрасывает соответствующий разряд регистра RGI и выдает на шину данных D(7 — 0) код команды CALL;

5. МП выдает еще два сигнала INТА, которые позволяют ПКП передать на шину данных 16-разрядный адрес подпрограммы обслуживания прерывания, причем младший байт адреса передается по первому сигналу INТА, а старший — по второму.

МП выдает еще два сигнала INТА, которые позволяют ПКП передать на шину данных 16-разрядный адрес подпрограммы обслуживания прерывания, причем младший байт адреса передается по первому сигналу INТА, а старший — по второму.

При обслуживании прерываний по опросу микропроцессор производит считывание кода номера запроса с высшим уровнем приоритета по сигналу RD. Прием запросов, маскирование и анализ приоритета выполняются так же, как и при обслуживании прерываний по запросу.

Для увеличения числа уровней прерывания ПКП могут быть объединены в систему, состоящую из ведущего и нескольких ведомых ПКП (рисунок 1,в). При обслуживании запроса, поступившего на вход ведомого ПКП, ведущий ПКП по сигналу INTA выдает на шину данных код команды CALL, а на шины СAS 0 — CAS 2 — код номера ведомого ПКП. С приходом второго и третьего сигналов INTА адрес подпрограммы обслуживания на шину данных выдает выбранный по коду на шинах CASO — CAS2 ведомый ПКП.

Установка ПКП в исходное состояние и настройка его на определенный режим обслуживания прерываний программируется двумя типами команд: командами инициализации (ICW) и командами управления операциями (OCW). Для инициализации в ПКП последовательно вводятся команды ICW1 и ICW2. В микропроцессорной системе, состоящей из нескольких ПКП, для каждого из них после двух первых команд инициализации вводится команда ICW3, задающая режим взаимодействия контроллеров. Форматы команд инициализации приведены на рисунке 2.

Для инициализации в ПКП последовательно вводятся команды ICW1 и ICW2. В микропроцессорной системе, состоящей из нескольких ПКП, для каждого из них после двух первых команд инициализации вводится команда ICW3, задающая режим взаимодействия контроллеров. Форматы команд инициализации приведены на рисунке 2.

Команда ICW1 (рисунок 2,а) сбрасывает регистры RGI, RGM и присваивает низший приоритет входу IR7. Разряд S этой команды определяет наличие одного или нескольких ПКП в системе, а разряд F (формат) — адресный интервал в 4 или 8 бит между начальными адресами подпрограмм обслуживания прерываний. Разряды А7 — А5 команды ICW1 используются для формирования младшего байта адресов подпрограмм обслуживания прерываний в соответствии с таблицей 2.

Рисунок 2.

Таблица 2. Младший байт адресов команды CALL

Команда ICW2 (рисунок 2,б) представляет собой старший байт адреса подпрограмм обслуживания прерываний, выдаваемый ПКП на шину данных в качестве третьего байта команды CALL. В команде ICW3 для ведущего ПКП (рисунок 2,в) наличие 1 в одном из разрядов указывает на подключение к соответствующему входу запроса прерывания ведущего ПКП выхода INT ведомого ПКП. В команде ICW3 для ведомого ПКП (рисунок 2,г) задается код его номера в системе.

В команде ICW3 для ведомого ПКП (рисунок 2,г) задается код его номера в системе.

Команды инициализации загружаются в ПКП из микропроцессора по команде OUT с учетом определенного значения младшего разряда адреса А0 (рисунок3). После записи команд инициализации ПКП подготовлен к приему запросов прерывания и может работать в режиме с фиксированными приоритетами запросов. В этом режиме запросы упорядочены по приоритетам и вход IR0 имеет высший приоритет, a IR7 — низший. Для задания других режимов функционирования ПКП необходимо использовать команды OCW, которые загружаются после команд инициализации в любой текущий момент времени.

Рисунок 3.

Команда управления операциями OCW1 (рисунок 3,а) осуществляет установку или сброс разрядов регистра RGM. Установка некоторого разряда регистра маскирования приводит к запрету прерывания по соответствующему входу.

Команда управления операциями OCW2 (рисунок 3,б) осуществляет сброс разряда регистра ISR и циклический сдвиг приоритета запроса. Возможные варианты команды OCW2 и выполняемые ею функции показаны в таблице 3.

Возможные варианты команды OCW2 и выполняемые ею функции показаны в таблице 3.

Таблица 3. Варианты команды OCW2

Если обслуживание запроса прерывания необходимо закончить сбросом разряда регистра ISR с высшим приоритетом, то используется команда OCW2 со значениями EOI=1 и SEOI = 0. При EOI = 1 и SEOI = 1 предназначенный для сброса уровень обслуживаемого прерывания указывается в команде разрядами D2 (L2) — DO (LO). Циклический сдвиг приоритетов задается в команде OCW2 разрядом D7(R). В циклическом режиме используется круговой порядок назначения приоритетов. Последнему обслуженному запросу присваивается низший приоритет, следующему по кругу — высший. Приоритеты остальных запросов циклически смещаются по шкале приоритетов. При R = 1 и SEOI =0 команда OCW2 присваивает низший приоритет запросу с высшим приоритетом, а при R = 1 и SEOI = 1 низший приоритет присваивается запросу, номер которого указывается разрядами D2(L2) — DO(LO). Команда OCW2 обычно записывается в ПКП в конце подпрограммы обслуживания прерывания перед командой возврата RET.

Команда управления операциями OCW3 (рисунок 3,в) позволяет задать режим специального маскирования (разряды D6, D5), режим опроса (разряд D2) и произвести считывание состояния ПКП (разряды D1, DO).

Режим специального маскирования дает возможность на некотором участке программы выборочно управлять запросами с различными приоритетами и разрешать прерывания выполняемой программы даже от входов с меньшими приоритетами. Режим специального маскирования задается командой OCW3 при ESMM = 1 и SMM = 1 и воздействует до сброса по команде с ESMM = 1 и SMM=0.

Режим опроса устанавливается по команде OCW3 при Р = 1. В этом режиме ПКП принимает запросы и формирует слово-состояние опроса, содержащее номер запроса с наивысшим приоритетом (разряды D2 — DO слова-состояния). Обслуживание запроса происходит по требованию программы, осуществляющей с помощью команды ввода IN (A0 = 0, RD = 0) чтение слова-состояния, программное декодирование его и переход к соответствующей подпрограмме обслуживания прерывания.

Считывание содержимого регистров RGI и ISR производится после загрузки в ПКП команды OCW3 соответствующими значениями ERIS и RIS (рисунок 3,в) с последующим выполнением команды ввода IN (А0 = 1, RD = 0). Считывание содержимого регистра RGM производится без предварительной загрузки OCW3 по команде IN (А0=1, RD = 0).

Практическая работа № 19

Тема: Контроллеры прямого доступа к памяти

Цель работы:Изучить структуру, назначение выводов, управляющие сигналы и схемы включения микросхемы контроллера прямого доступа к памяти (КПДП).

Задание 1. Записать назначение и состав программируемого контроллера прямого доступа к памяти КР580ВТ57.

Задание 2. Зарисовать структурную схему микросхемы КР580ВТ57.

Задание 3. Указать назначение входов/выходов микросхемы КР580ВТ57.

Задание 4.Перечислить и охарактеризовать режимы работымикросхемы КР580ВТ57.

Задание 5. Программирование режима работы КПДП.

Передать 300 байт из памяти в УВВ через канал 2 с адреса 8D2F. Продолжить передачу ещё 500 байт в режиме автозагрузки. КПДП работает в режиме нормальной записи и фиксированного приоритета. Адрес КПДП 90h.

Продолжить передачу ещё 500 байт в режиме автозагрузки. КПДП работает в режиме нормальной записи и фиксированного приоритета. Адрес КПДП 90h.

1. Сформировать УС режима

2. Запрограммировать второй канал

3. Запрограммировать третий канал

4. Написать программу инициализации КПДП

5. Нарисовать логическую схему формирования сигнала CS

Микросхема KP580BT57

Микросхема КР580ВТ57 — четырехканальный программируемый контроллер прямого доступа к памяти (ПД), предназначен для высокоскоростного обмена данными между памятью системы и периферийными устройствами путем генерации массива последовательных адресов памяти по требованию периферийного устройства

Микросхема осуществляет двунаправленный обмен данными между памятью и периферийными устройствами путем формирования в адресном канале микропроцессорной системы параметров заданного массива, адресов ячеек памяти и управляющих сигналов. Массив адресов, по которым происходит обмен данными между периферией н памятью, характеризуется начальным адресом, т. е. первым адресом начала обмена и числом циклов обращений к памяти. После предоставления системной шины со стороны процессора микросхема может осуществить обмен массивом данных между памятью и периферийными устройствами без дальнейшего вмешательства процессора.

е. первым адресом начала обмена и числом циклов обращений к памяти. После предоставления системной шины со стороны процессора микросхема может осуществить обмен массивом данных между памятью и периферийными устройствами без дальнейшего вмешательства процессора.

Каждый из четырех каналов микросхемы обеспечивает адресацию (путем инкрементирования выработанного адреса) внешней памяти массивами объемом до 16К байт с возможностью задания любого из 64К начальных адресов.

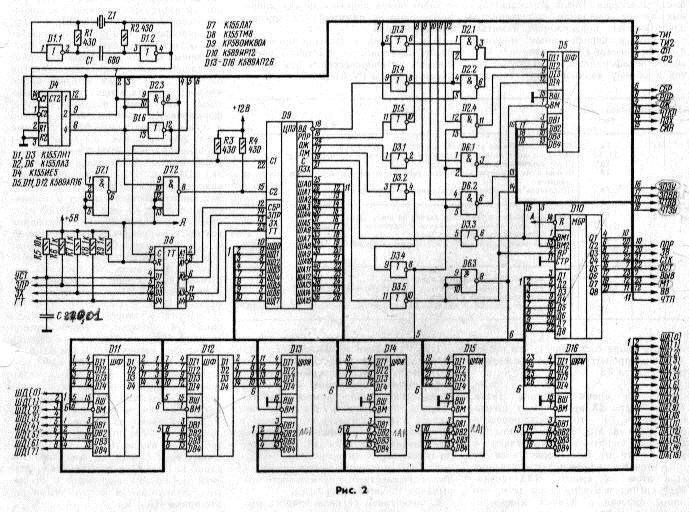

Условное графическое обозначение микросхемы приведено на рисунке 1, назначение выводов приведено в таблице 1, структурная схема показана на рисунке 2.

Каналы приема запросов ПД предназначены для приема и привязки несинхронных сигналов прямого доступа к памяти DRQ0— DRQ3, маскирования входов и выдачи сигналов подтверждения запроса прямого доступа к памяти DACK0—DACK3. Каждый канал принимает запрос через свой вход DRQ и выдает сигнал «Подтверждение запроса» ПД через соответствующий выход.

Рисунок1. Условное графическое обозначение КР580ВТ57 Условное графическое обозначение КР580ВТ57 | Таблица 1. |

Устройство управления управляет последовательностью операций в течение всех циклов ПД путем генерации соответствующих управляющих сигналов. Устройство осуществляет переход микросхемы из состояния ожидания в состояние обслуживания по сигналу HLDA, поступившему из процессора, вырабатывает и передает внешние сигналы на следующие выводы:

– выход HRQ (запрос захвата) запрашивает управление системной шиной. В системе с одной микросхемой этот выход должен быть подключен ко входу «Захват» микросхемы КР580ВМ8ОА;

– вход HLDA (подтверждение захвата) получает от КР580ВМ80А сигнал, который свидетельствует, что микросхема КР5®0ВТ57 может приступать к управлению системными шинами,

– вход С (тактовый сигнал), на который подаются тактовые импульсы С2 от тактового генератора микропроцессорной системы,

– выход STB А (стробирующий сигнал адреса) стробирует старший байт адреса памяти, передаваемый через шину данных;

– выход АЕ (разрешение адреса) указывает системе, что происходят циклы ПД. Он может быть использован в системе для блокировки адресной шины в устройствах, не участвующих в ПД;

Он может быть использован в системе для блокировки адресной шины в устройствах, не участвующих в ПД;

– выход ТС (конец счета) указывает выбранному в настоящий момент периферийному устройству, что текущий цикл ПД должен быть последним для этого массива данных. Если разряд разрешения «КС-стоп» в регистре режима (РгР) установлен в 1, то выбранный канал будет автоматически запрещен в конце этого цикла ПД, т. е. в конце передачи массива данных. Вывод активизируется (устанавливается в 1), когда содержимое 14-разрядного регистра циклов (РгЦ) в данном канале устанавливается в 0. 14разрядов РгЦ должны быть загружены числом N – 1, где N – нужное число циклов ПД;

– выход М128 (маркер по модулю 128) указывает выбранному периферийному устройству, что текущий цикл ПД является 128-м или кратным 128 от конца массива данных. Если общее число циклов ПД N делится на 128 и РгЦ загружен числом N–1, то сигнал MI28 появляется на 128-м и каждом кратном 128 цикле от конца массива данных,

– вход RDY (готовность) асинхронный и используется для удлинения циклов записи в память (чтение из памяти) путем ввода микросхемы с помощью сигнала «Готовность» в состояние ожидания, если выбранная память требует более длинных циклов,

– выводы АО–АЗ – адресные шины. Они являются трехстабильиыми выходами и устанавливают разряды 0—3 16-разрядного адреса памяти, генерируемого микросхемой во время всех циклов ПД.

Они являются трехстабильиыми выходами и устанавливают разряды 0—3 16-разрядного адреса памяти, генерируемого микросхемой во время всех циклов ПД.

Схема установки режима хранит информацию о запрограммированных режимах: автозагрузки; КС-стоп; удлиненной записи: обычной записи; циклического сдвига приоритетов; фиксированного приоритета. Кроме того, разряды 0—3 регистра установки режима разрешают работу каждого из каналов. Регистр установки режима обычно загружается после того, как установлены регистр адреса (РгА) и регистр циклов (РгЦ).

Регистр установки режима сбрасывается путем подачи сигнала иа вход RS, что приводит к запрету работы всех каналов во всех режимах и предотвращает конфликты на шинах при подаче напряжения питания.

Пользоваться каналами запрещается до тех пор, пока РгА и РгЦ не будут загружены необходимыми числами. В противном случае случайный запрос ПД (DRQ) от периферийного устройства может вызвать цикл ПД, что приведет к порче данных в памяти.

Рисунок 2. Структурная схема КР580ВТ57

Структурная схема КР580ВТ57

Состояние 1 в разряде 4 РгР устанавливает режим циклического сдвига приоритетов. В этом режиме после каждого цикла ПД (но не каждого запроса ПД) приоритет каждого канала изменяется. Канал, который только что был обслужен, будет иметь самый низкий приоритет, а остальные каналы получат приоритет, следующий по уровню, как показано в таблице 2

Таблица2. .

Если разряд 4 установлен в 0, каждый канал ПД имеет фиксированный приоритет В режиме фиксированных приоритетов канал О имеет наивысший приоритет, а канал 3 — самый низкий.

Циклический сдвиг приоритетов предотвращает монополизацию одного из каналов ПД, последовательность циклов ПД будет обслуживать различные каналы, если разрешено обслуживание более одного канала. Все операции ПД начинаются с первоначального присвоения каналу 0 наивысшего приоритета для первого цикла ПД.

Состояние 1 в разряде 5 РгР устанавливает режим удлиненной записи В этом случае продолжительность сигналов WR и WRIO увеличивается путем более ранней их активизации в цикле ПД, чтобы можно было использовать различные типы памяти и устройств ввода/вывода с различным временем доступа к памяти.

Состояние 1 в разряде 6 РгР устанавливает режим «КС-стоп», при котором после появления сигнала ТС обслуженный канал ПД оказывается запрещенным. В результате автоматически прекращаются всякие операции ПД в данном канале. Разряд разрешения для данного канала должен быть перепрограммирован для продолжения или начала следующей операции ПД.

Если разряд 6 установлен в 0, то появление сигнала ТС не запрещает дальнейшее использование канала. В этом случае сигнал информирует периферию об окончании операции ПД.

При наличии 1 в разряде 7 РгР устанавливается режим автозагрузки. Этот режим позволяет каналу 2 многократно передавать массив данных без программного вмешательства.

Разряд «Флаг обновления данных» в РгС сбрасывается аппаратно в конце этого цикла.

В разрядах 0—3 РгС аппаратно устанавливается «Флаг завершения обслуживания» по соответствующему каналу после выработки сигнала ТС.

Установка разрядов 0 – 3 регистра установки режимов разрешает работу каждого из каналов. Если разряд установлен в 0, то соответствующий канал блокируется.

Если разряд установлен в 0, то соответствующий канал блокируется.

Четыре младшие адресные шины АО—АЗ двунаправленные. В режиме программирования они являются входами, которые выбирают один из регистров микросхемы для считывания или записи информации. В режиме обслуживания они являются выходами, на которых устанавливаются младшие четыре разряда 16-разрядного адреса памяти, геенерируемого микросхемой.

Буферная схема данных (БД) представляет собой 8 разрядную двунаправленную шину с тремя состояниями, соединяющую микросхему с системной шиной данных

Двунаправленная шина данных DO—D7 с тремя состояниями. При программировании в режиме записи восемь бит данных для регистра адреса, регистра числа циклов или регистра установки режима передаются через шину данных из процессора. При чтении процессором содержимого регистра адреса, регистра числа циклов или регистра состояния каналов данные передаются в процессор также через шину данных. В течение циклов ПД (сама микросхема управляет системной шиной) она выдает старшие восемь разрядов адреса памяти (из одного из регистров адреса ЗУ). Эти разряды адреса выдаются в начале каждого цикла ПД. Затем шина данных освобождается для обмена данными между памятью и периферией в течение оставшейся части цикла ПД. Необходимым условием для обслуживания канала прямого доступа к памяти является поступление на микросхему из периферии сигнала запроса DRQ, в результате чего микросхема вырабатывает сигнал «Запрос захвата» HRQ для передачи его на процессор. При получении от микропроцессора сигнала «Подтверждение захвата» HLDA микросхема осуществляет:

Эти разряды адреса выдаются в начале каждого цикла ПД. Затем шина данных освобождается для обмена данными между памятью и периферией в течение оставшейся части цикла ПД. Необходимым условием для обслуживания канала прямого доступа к памяти является поступление на микросхему из периферии сигнала запроса DRQ, в результате чего микросхема вырабатывает сигнал «Запрос захвата» HRQ для передачи его на процессор. При получении от микропроцессора сигнала «Подтверждение захвата» HLDA микросхема осуществляет:

– управление системной шиной, подтверждение запроса периферийного устройства, которое подключено к каналу с наивысшим приоритетом,

– выдачу младших восьми разрядов адреса памяти на системные адресные шины АО—А7, а старших восьми разрядов адреса на шину данных DO—D7;

– генерацию соответствующих сигналов управления RD или WR10, RD10, WR, которые побуждают периферийное устройство получить байт данных из ячейки или передать его в ячейку памяти. За один цикл работы микросхема передает один байт данных, причем в первом цикле вырабатывается адрес ячейки, равный начальному адресу, а в каждом последующем адрес увеличивается на 1 до тех пор, пока число циклов обращений к памяти не станет равным заданному.

Микросхема управляет системной шиной и повторяет последовательность передач до тех пор, пока периферийное устройство сохраняет свой запрос. Так микросхема может передать массив данных в быстродействующее периферийное устройство или выбрать его из этого устройства в один прием. Когда указанное количество байт передано, микросхема выдает сигнал «Конец счета» ТС, информируя о завершении передачи данных.

В процессе выполнения циклов ПД (системные шины находятся под управлением микросхемы) имеются три различных режима работы:

– режим чтения ПД — обеспечивает передачу данных из памяти в периферию;

– режим записи ПД — обеспечивает передачу данных из периферии в память,

— режим проверки ПД — не включает передачу данных.

Канал ПД в режиме проверки не генерирует сигналы управления RD, WR, RD10, WR10, что предотвращает передачу данных. Однако в каждом цикле ПД микросхема осуществляет управление системной шиной и подтверждает запросы периферии.

При наличии двух и более запросов будет обслуживаться периферия с наивысшим приоритетом. Вид приоритета устанавливается в процессе программирования

Вид приоритета устанавливается в процессе программирования

Имеется два вида установки приоритета:

– фиксированный, когда канал 0 имеет наивысший приоритет, а канал 3 — самый низкий;

– циклический сдвиг приоритета, когда после каждого цикла ПД приоритет каждого канала изменяется.

В процессе функционирования микросхемы путем программирования РгР можно заблокировать (замаскировать) запрос любого канала.

В процессе функционирования в составе микропроцессорной системы микросхема может находиться в одном из следующих состояний:

–исходное,

– программирование;

– ожидание,

– обслуживание.

В исходное состояние микросхема устанавливается после включения путем подачи на ее вход SR сигнала «Установка» В этом состоянии маскируются запросы всех каналов ПД, а трехстабильные буферные схемы системной шины АО—АЗ переводятся в состояние приема информации.

В состоянии программирования микросхемы микропроцессор по системным шинам данных DO—D7 осуществляет запись в соответствующие регистры микросхемы исходных данных (начальные адреса и число циклов) и инструкции, определяющей режим работы микросхемы при циклах ПД. При этом адресат приема информации микросхемой определяется кодом на системных шинах АО—АЗ.

При этом адресат приема информации микросхемой определяется кодом на системных шинах АО—АЗ.

В состоянии ожидания микросхема находится от момента окончания программирования до получения сигнала «Подтверждение запроса захвата» HLDA или в промежутках между массивами циклов ПД в отсутствие запросов ПД.

В состоянии ожидания осуществляется прием сигналов DRQ и вырабатывается для микропроцессора сигнал «Запрос захвата» HRQ В этом состоянии системные шины находятся под управлением микропроцессора.

После получения от микропроцессора сигнала HLDA при наличии сигнала запроса DRQ микросхема вырабатывает сигнал DACK и переходит в состояние обслуживания.

В состоянии обслуживания системные шины находятся под управлением микросхемы, которая осуществляет один из запрограммированных режимов ПД и генерирует набор управляющих сигналов, необходимых для осуществления обмена данными между памятью и периферией.

Регистры микросхемы загружаются или с них считывается информация, если процессор выполняет команду записи или чтения путем обращения к микросхеме КР580ВТ57 и к соответствующим регистрам внутри микросхемы. Для этого процессору необходимо выдать соответствующие сигналы записи или чтения WR10, RD10 и на системные адресные шины выдать адрес регистра микросхемы. В это время на шину данных подается необходимая информация для записи в регистры или же через шину данных читается информация из микросхемы.

Для этого процессору необходимо выдать соответствующие сигналы записи или чтения WR10, RD10 и на системные адресные шины выдать адрес регистра микросхемы. В это время на шину данных подается необходимая информация для записи в регистры или же через шину данных читается информация из микросхемы.

Для установки состояния программирования необходимо также на микросхему подать сигнал CS = 0, получаемый обычно путем декодирования всех или некоторых старших 12 разрядов адреса А4—А15 (в зависимости от системной организации памяти и устройств ввода/вывода). Вход WR10 (или WR при общем поле памяти и УВВ) указывает на запись в регистры микросхемы, а вход RD10 (или RD) — на чтение из регистров

Разряд АЗ позволяет различить регистры каналов при А3=0, а при А3= 1 – регистр установки режима (работает только на запись), и регистр состояния каналов (работает только на чтение)

Три младших разряда АО—А2 указывают конкретный регистр канала. Если адресуется регистр установки режима или регистр состояния каналов, то разряды АО—А2 должны быть установлены в 0. Когда адресуется регистр канала, разряд АО позволяет различить регистры адреса ПД (при А = 0) и числа циклов (при А=1). Разряды А1, А2 позволяют определить номер канала. Коды выборки регистров приведены в таблице 3.

Когда адресуется регистр канала, разряд АО позволяет различить регистры адреса ПД (при А = 0) и числа циклов (при А=1). Разряды А1, А2 позволяют определить номер канала. Коды выборки регистров приведены в таблице 3.

В связи с тем, что регистры канала являются 16-разрядными, для их загрузки или чтения необходимо два программных командных цикла. В микросхеме имеется триггер, который автоматически переключает цепи во время выполнения операции чтения или записи Этот триггер определяет доступ к старшему или младшему байту регистра. Сбрасывается триггер путем подачи сигнала н вход SR, а также всякий раз при загрузке регистра установки режима.

Для обеспечения соответствующей синхронизации при обращениях к регистрам канала все команды, поступающие от процессора, должны появляться парами, причем всегда младший байт регистра должен получить доступ к_ памяти первым. Нельзя подавать сигнал CS до тех пор, пока сигнал RD 10 или WR 10 не станет активным, так как это может привести к ошибочному состоянию триггера. В системах, использующих прерывания, запросы прерывания должны быть запрещены в процессе программирования регистров канала, чтобы не было разделения парных команд записи или чтения регистров.

В системах, использующих прерывания, запросы прерывания должны быть запрещены в процессе программирования регистров канала, чтобы не было разделения парных команд записи или чтения регистров.

Таблица 3.

Внутренние операции микросхемы по переходу из состояния ожидания в состояние обслуживания могут быть выполнены в течение семи тактов. Продолжительность тактов определяется тактовой частотой микросхемы. Если микросхема не выполняет цикла ПД, то она находится в холостом такте SO до прихода сигнала запроса ПД. С приходом сигнала DRQ последний обрабатывается согласно установленному приоритету (фиксированному или циклическому) и вырабатывается сигнал HRQ. По этому сигналу микросхема переходит к такту S1. Это положение будет сохраняться до прихода с процессора сигнала «Подтверждение захвата» HLDA. Таким образом, состояние ожидания характеризуется пребыванием микросхемы в тактах SO, S1.

При получении сигнала HLDA возбуждается шина DACK канала, имеющего запрос с наиболее высоким приоритетом Таким образом осуществляется выборка канала и соответствующего периферийного устройства для цикла ПД, и микросхема переходит к такту S2. Заметим, что сигнал HLDA должен оставаться с высоким уровнем напряжения до тех пор, пока не появится сигнал PACK при одном цикле ПД или оба сигнала DACK и ТС при передаче массива. Если микросхема потеряет управление системными шинами, т е если сигнал HLDA станет равным 0, то сигнал DACK будет сохраняться до окончания текущего цикла ПД. После этого циклы ПД прекращаются до тех пор, пока микросхема снова не получит управление системными шинами

Заметим, что сигнал HLDA должен оставаться с высоким уровнем напряжения до тех пор, пока не появится сигнал PACK при одном цикле ПД или оба сигнала DACK и ТС при передаче массива. Если микросхема потеряет управление системными шинами, т е если сигнал HLDA станет равным 0, то сигнал DACK будет сохраняться до окончания текущего цикла ПД. После этого циклы ПД прекращаются до тех пор, пока микросхема снова не получит управление системными шинами

Каждый цикл ПД (состояние обслуживания) содержит не менее четырех тактов. S2, S3, S4, S5. Если время доступа к памяти и УВВ, включенных в систему, недостаточно для передачи байта в указанное число тактов, то между тактами S4 и S5 вводится один и более тактов ожидания Swi. Использование удлиненной записи может в некоторых случаях исключить такты ожидания. Если в циклах ПД осуществляется режим проверки, то сигнал RDY не требуется.

Статьи к прочтению:

- Программируемый микропроцессор

- Программная реализация алгоритмов и методов, используемых в системах управления роботами.

Системный Контроллер Прерываний Драйвер

Похожие статьи:

Тема 9. обработка прерываний в контроллере

В качестве сигналов прерывания, поступающих в контроллер прерывания, могут быть сигналы, формируемые модулями, входящими в контроллер (модуль таймера,…

Аппаратные прерывания. контроллер прерываний

Аппаратное прерывание – прерывание, выполняемое в результате запроса, поступающего от периферийного оборудования. Контроллер прерываний – устройство,…

Historie osmibitových mikropočítačů vyráběných v SSSR (2)

Obsah

1. Osmibitové mikropočítače a mikroprocesory v SSSR

2. Mikroprocesor KR580VM80A a jeho podpůrné obvody

3. Osmibitový mikropočítač Vektor-06C

4. Grafický subsystém mikropočítače Vektor -06C

5. Клоны ZX Spectra в СССР

6. Осмибитовый микросчет Hobbit

Осмибитовый микросчет Hobbit

7. Почитай Москва и Пентагон-48

8. Обследуй следователи0005

9. Odkazy na Internetu

1. Osmibitové mikropočítače a mikroprocesory v SSSR

V předchozí části seriálu o historii výpočetní techniky jsme se seznámili s jedním z prvních sériově vyráběných osmibitových mikropočítačů, které byly používány v Sovětském svazu. Jednalo se o počitače, jejichž český název po překladu zní Achát , původně Agát (v azbuce psano AGAT). Koncepce těchto micropočitačů, tj. как властные технологические продукты, так и заложенные программы выбавлены (прежде всего память ПЗУ), была заложена на в тэ добе йиж вельми разжижены и в защищены облібеныч осмибитовік микропоров0025 Apple II , который в США появлялся как фирма, так и в домашнем хозяйстве и в школах. Konstruktéři Achátu zpočatku производили производство электронных компонентов, которые были произведены в СССР, попр. dováženy z okolních zemí RVHP. Teprve o několik let později bylo možné postavit další verze Achátů (konkrétně se jedná o typy 7 a 9) na originálním osmibitovém mikroprocesoru MOS 6502 , který mimochodem v té době představoval již deset let starou technologii.

Teprve o několik let později bylo možné postavit další verze Achátů (konkrétně se jedná o typy 7 a 9) na originálním osmibitovém mikroprocesoru MOS 6502 , který mimochodem v té době představoval již deset let starou technologii.

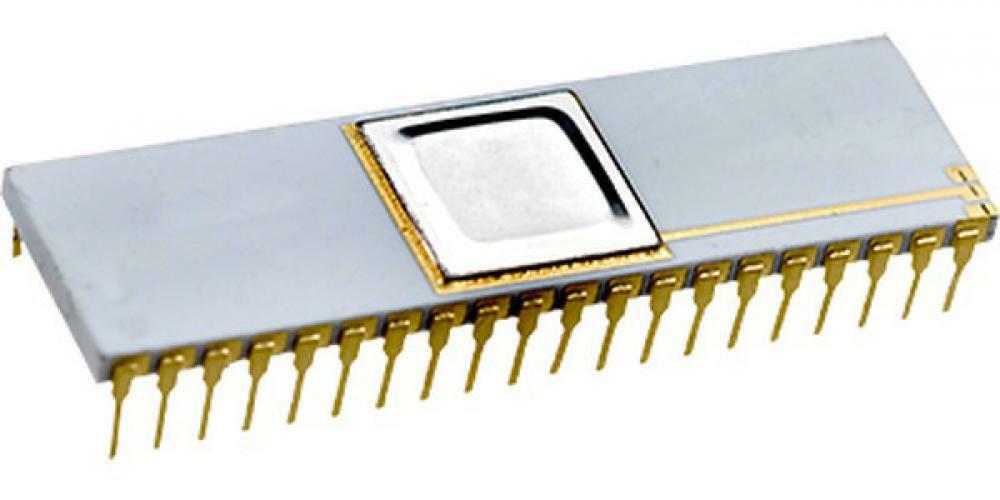

Obrázek 1: Osmibitový mikroprocesor MOS 6510, což je inovovaná varianta původního procesoru MOS 6502. Tento mikroprocesor byl použit například v mikropočítačích Commodore C64, v nichž byl využit I/O port, který je jednou z inovací MOS 6510 oproti MOS 6502.

В днешний частый сериал у той темы зстанеме – попишеме си тотиж нэктере дальши типи осмибитовыч микропочитай, которые были в ссср наврхованы и вырабаны. JEDNA SE JAK O POJítače Vyráběné oficiálně (TJ. V Některém Podniku či Výrobním Družstvu), Tak I O Počítače, U nichž byla Zveřejněna o -jevi -jeil -jela o obela -jela lej много лидов стейн забавных, как самотечные поуживани почитать). Vzhledem k Тому, že v sssr bylo navrženo a posleze i vyrobeno nejvíce typů klonů zx spectra na světě (dokonce se uvádí, je pochet varinat věnovat popisu technických parametrů některých nejznámějších, nejpoužívanějších nebo nejzajímavějších variací на тему «Speccy». Jedná se například o počitače Хоббит , Москва , Ленинград , Скорпион и Пентагон (займава секвенция джмен).

Jedná se například o počitače Хоббит , Москва , Ленинград , Скорпион и Пентагон (займава секвенция джмен).

Образец 2: Osmibitový micropočítač Achát popsaný v predchozí části tohoto series.

2. Mikroprocesor KR580VM80A a jeho podpůrné obvody

Před popisem jednotlivých typů sovětských počítačů si však ještě řekněme, jaké elektronické součástky měli konstruktéři v SSSR vůbec k dispozici. Jedním z důvodů vzniku vlastních konstrukcí osmibitových mikropočítačů v SSSR totiž bylo i to, že dovoz minipočítačů a mikropočítačů ze západních zemí do států RVHP byl po poměrně dlouhou dobu ze strategických důvodů omezen. Panovaly totiž obavy (jak se ostatně ukázalo, tak v mnoha případech oprávněné) z toho, že by se s těmito stroji prováděl reverse engineering and následně by se získané znalosti používaly při vývoji vojenskýtechnskýt. С тохото дуводу было много первых строительных советских микросчетов заложено на туземских соучастковых закладках, попрж. на součástkách dovážených ze zemí RVHP. Jednou z nejdůležitějshích souichástek v mikropočtachi je samozřejmě mikroprocesor, který v sobě sdružuje funkce aritmeticko-logické jednotky, řadiche jedhorehro rohorehro rohorehro.

на součástkách dovážených ze zemí RVHP. Jednou z nejdůležitějshích souichástek v mikropočtachi je samozřejmě mikroprocesor, který v sobě sdružuje funkce aritmeticko-logické jednotky, řadiche jedhorehro rohorehro rohorehro.

Образец 3: Осмибитовый микропроцессор КР580ВМ80А, который был в СССР изготовлен жрубой от года 1979 до самодельного концевого советского соединения.

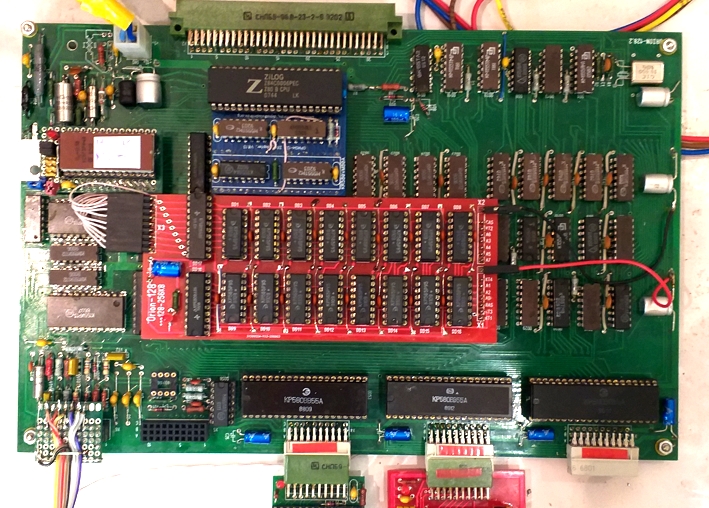

V SSSR se při konstrukci mikropočítačů, například dále popsaného Vektoru-06C či podomácku stavěného (a před nástupem klonů ZX Spectra i velmi oblíbeného) Radio-86KR , poměrně často používal osmibitový mikroprocesor nazvaný poněkud krypticky KR580VM80A ( в блоке питания КР580ВМ80А ), который был заложен на архитектурный знак микропроцессора Intel 8080A . Микропроцессор работает на частотах от 1 МГц до 2,5 МГц и разработан, как источник питания 8080ka, с тройным напряжением питания: +5В, +12В и –5В. Микропроцессор КР580ВМ80А был добавлен в четырехкомпонентный пластиковый или керамический порошок DIP (промежуточная версия заменена на

Образец 4: Далее фото микропроцессор KR580VM80A.

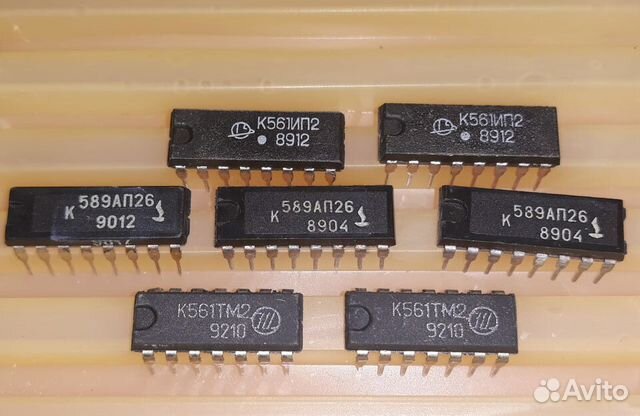

Zatímco pro zjednodušení konstrukce mikropocitačů založených na procesoru Intel 8080 byla vytvořena známá řada či stavebnice podpůrných (většinou programovatelných) obvodů, například čipy 8251, 8253, 8255 či 8257, v SSSR se vyráběly ekvivalenty těchto čipů, jejichž označení začínalo znaky KR580 nasledovaných dvojicí znaků (zkratka názvu) a наследные две машины, которые были сходны с последними двойными оригинальными чипами фирмы Intel (название же подводного обвода Intel 8251 было означено как KR580IK51 и т.д.). Нектары с эквивалентными, предварительными расчетами до jisté миры эквивалентных подпорных обводов jsou vedeny v následující tabulce:

| Чип фирмы Intel | Эквивалентный советский чип | Папка |

|---|---|---|

| 8080 | КР580ВМ80А | микропроцессор |

| 8251 | КР580ИК51 | řadič sériové linky |

| 8235 | КР580ВИ53 | программный часовач |

| 8255 | КР580ВВ55 | Тройные осмибитовые параллельные отруби ввода/вывода |

| 8257 | КР580ВТ57 | Ржадич DMA |

| 8259 | КР580ВН59 | řadič přerušení |

Образец 5: Микропроцессор KR580VM80A в керамическом заводе.

3. Осмибитови Микропочитач Вектор-06C

PRVNím Typem Počítače, Se Kterým Se dnes Seznámíme, Je Osmibitový Mikropočtichí Nazvaný VEKTOR-06266 (6 (6 (6 (6 (6 (66 (6 (6 (6 (6 (6 (6 (66 (6 (6 (6 (6 (6 (6 (6 (6 (6 (666 (666.0026 ), který byl navržen D. Temirazovem a A. Sokolovem počátkem roku 1987. Jedná se o počítač, jenž používal výše zmíněný osmibitový mikroprocesor KR580VM80A , který však mohl být nahrazen i procesorem KR580VM1 s menší spotřebou a několika dalšími vylepšeními. Tento mikropočítač měl poměrně neobvyklou architekturu – na jednu stranu jeho výpočetní výkon ani výbava podpůrnými obvody nijak nevybočovala z průměru mezi osmibitovými počítači, na stranu druhou nabízel téměř profesionální grafické režimy, které například překonávaly i možnosti nechvalně známé grafické karty CGA используется на отдельном счете IBM PC XT. Далши Зе Звлаштност Почитаче Vektor-06c Bylo to, že jeho paměť rom neobsahovala интерпретации Jazyka Basic , Pouze v ní byly obsženy zapha-japé zapé zapé zapé zapé japé zapé zapé razé-j.

Далши Зе Звлаштност Почитаче Vektor-06c Bylo to, že jeho paměť rom neobsahovala интерпретации Jazyka Basic , Pouze v ní byly obsženy zapha-japé zapé zapé zapé zapé japé zapé zapé razé-j.

Образец 6: Осмибитовый микросчетчик Вектор-06С.

Obsah paměti ROM se navíc při startu počítače překopíroval do operační paměti (RAM) a následně se ROM zcela odpojila z adresového prostoru mikroprocesoru, což při bližším pohledu není špatné řešení, protože to například umožňuje standardní cestou „opatchovat“ základní systémové rutiny, попрж. je zcela nahradit. То, что в ROM небыло обговорено интерпретировать BASICu вшак неизвестно, же по се на почитaчи Vektor-06C tento jazyk nedal použít – byl samozřejmě dostupný na paměťových médiích (tj. na kompaktních kazetách), stejně jako interaktivní vývojové prostředí programovacího jazyka FORTH , který je pro některé účely vhodnější než BASIC (ovšem způsob programování v томто jazyce si musí uživatelé postupně osvojit, protože není tak přímočarý jako v BASICu ).

Образец 7: Современный вариант почтового ящика Вектор-06С.

Jedna z několika dotupných modifikací tohoto počítače spocívala v náhradě původního procesoru KR580VM80A для осмибитового микропроцессора Zilog Z80 , попр. за его советский эквивалент KR580VM1 . Tento modifikovaný model byl dále různými způsoby upravován, například verze nazvaná Vektor Turbo+ byla založena na mikroprocesoru Z80 s hodinovou frekvencí 6 MHz nebo dokonce 12 MHz a s operační pamětí zvětšenou až na 2MB. Tyto úpravy měly vést k tomu, aby se počítače Vektor začaly používat i pro kancelářské aplikace (textové procesory, tabulkové procesory, jednouživatelské databáze), ovšem na trhu se právě v té době (jedná se o první polovinu devadesátých let minulého století) již являются особенными счетами, совместимыми с IBM PC (XT, AT), а также в том секторе, где находится счет Vektor neslavily tak velký úspěch, jak by si jejich konstruktéři a výrobci přáli.

4. Grafický subsystém mikropočítače Vektor-06C

V předchozí kapitole jsme se zmínili o tom, že se grafický subsystém počítače Vektor-06C odlišoval od grafických subsystémů mnoha dalších osmibitových mikropočítačů. Операционная память Vektoru-06C или емкость обязательная 64 kB всего была разделена на две половины. V prvních 32 кб paměti (mapovaný na adresy 0 × 000 až 0 × 7fff) Mohly být uloženy Programy, Данные, Zásobník I Proměnné operačního systému, zatímco druhý jistž vistž ristž vistž vistž ristž vistž ristž ristž ristž risthis vistž rahes vistž rahes imod visti й, za ramod, j, jisthe systém 0×8000 или 0×FFFF) как изображение видео; Днес Быхом Ржекли фреймбуфер . Tak velká kapacita video paměti je na osmibitových počítačích velmi neobvyklá a to ze dvou důvodů – obsazuje se celá polovina adresového prostoru naprosté většiny osmibitových mikroprocesorů a manipulace s tak velkým blokem paměti je nutně pomalá, což se negativně projevuje především ve hrách. Z tohoto důvodu se typeické velikosti velikosti obrazových pamětí u osmibitových micropochitačů pohybují на hodnotách okolo osmi kilobajtů.

Z tohoto důvodu se typeické velikosti velikosti obrazových pamětí u osmibitových micropochitačů pohybují на hodnotách okolo osmi kilobajtů.

Графическая подсистема Вектор-06С подпоровал два графических режима. В первом режиме, который создал битовую карту или разрешение 256×256 пикселя, можно использовать каждый пиксель, чтобы получить одно из шести изображений. Шестнактибарьевна барвова палитра была выбрана из 256 баревніх комбинаций. В другом режиме создано растровое изображение или увеличено до 512 × 256 пикселей, где каждый пиксель может быть обустроен единым барвоу на четырехугольной палитре. Tyto možnosti grafického subsystému Vektor-06C jsou skutečně osmibitovy micropočitač poněkud необвыклей, zvláště když si uvědomíme, že již zmíněná „profesionárálár0025 CGA měla jen polliční kapacitu framebufferu a navíc pevnou barvovou палету (соответственно двойная барвовая палитра, мези ниміж се было можнэ пржепинат). Графический выход был прошедшим модулятором, который был подключен к телевизору, но не может быть меньше, чем нужно, и мультичастотный монитор.

Образек 8: Реконструированный пункт Вектор-06С.

5. Klony ZX Spectra v SSSR

V perexu tohoto článku jsme si řekli na první pohled možná překvapivou informaci, že v bývalém SSSR bylo navrženo i vyráběno více typů klonů osmibitových počítačů ZX Spectrum , než kdekoli jinde na světě. Tento stav byl způsoben především tím, že originální ZX Spectrum bylo v SSSR prodáváno za neuvěřitelnou cenu téměř 40000 rublů, zatímco průměrný měsíční plat byl cca 250 rublů (kurz rublu byl nastaven na cca 10 Kčs). Jednoduchým výpočtem můžeme zjistit, že průměrně vydělávající člověk si mohl vysněné ZX Spectrum pořídit po 13 letech, což je z nethypotzešní pohledu Нелзе се теды дивит тому, же на разрозненных мистэх СССР, есть экзистенциальные покусы или конструкции по строительству стейней однодухового (по техническим станкам) а сучаснэ стейнэ универзальниго, как было ZX Spectrum . Při návrhu sovětských klonů ZX Spectra se však museli konstruktéři vypořádat například se zpočátku nedostatečnou součástkovou základnou – týkalo se to jak ekvivalentů procesorů Z80 , tak i náhrady zákaznického čipu ULA .

Образец 9: Румунский клон ZX Spectra – большие первоклассные конструкции ZX Spectra се клоны техническое вознаграждение вырабаты дослова по целому свету.

Микропроцессор Z80 можно было найти вице-типы чипов, напржиклад, один или процессор T34V (vyráběn od roku 1991), KR1858VM1 (plně kompatibilní se Z80 ), KM1582VM2 (opět plně kompatibilní, ovšem v plastickém pouzdře) a VM3 (zde existovaly oproti původnímu Z80 určité rozdíly) . ČIP ULA BYL NAHRAZOVEN BUď ELEKTRONICKýM AVELSODEM SKLádajícím SE Z JEDNODUSHOSHYCH LOGICKýCH čIPů, SOVěTSKýM ekvivalentem čipu Ula (Sověmlný -nhaSI -č -č -nhaSI -č -č -č -č -č -č -č čibu . Zatimco originalní ZX Spectrum мелкий буфер 16 КБ несколько частей 48 КБ операционная память, советские клоны небольшого веса установлены минимально 64 КБ RAM (несколько моделей больше всего). “Přebývajících” 16 kB, созданный на основе RAM, который создавал новую редакцию, копировал программы, создавал и тактировал операционные системы. Obsah paměti rom (o typické kapacitě 16 кб). ROM, ктер вшак většinou zaručovala alespoň základní funkcionalitu s původním ZX Spectrem , бесплатный интерпретатор языка BASIC.

Obsah paměti rom (o typické kapacitě 16 кб). ROM, ктер вшак většinou zaručovala alespoň základní funkcionalitu s původním ZX Spectrem , бесплатный интерпретатор языка BASIC.

Образец 10: карта, на которой есть нерабочие состояния, разделенные на части того, несколько клонов (типу) ZX Spectra v nich vzniklo.

6. Osmibitový mikropočítač Hobbit

Známým, i když z historického hlediska zdaleka ne prvním klonem ZX Spectra je osmibitový mikropočítač Hobbit (v azbuce psáno ХОББИТ ) navržený Dimitrijem Michajlovem, jehož výroba začala v roce 1990. Tento počítač byl až na nepatrné odchylky plně compatibilní s puvodním ZX Spectrem 48k . V Základní Sestavě Ossahoval Mikroprocesor Z80 S Hodinovou frekvencí 3,5 МГц, Paměť ram o kapacitě 64 Kb A Taktéž, Na Rozdíl Od Původního Speptra, Portheoví -Portheoví -Porthevů -Portheovů -Portheovů -Portheovů -Portheovů -Portheovů -Portheovů -Portheovi К чтению было можно загрузить две однократные дискеты про дискеты или 5 1/4 места, предварительно отформатировав дискету, которую читал на ПК. В 1991 году была выпущена новая версия кошелька Hobbit , который поуживала дискеты о продаже 3 1/2 места, подобная накладке особого чека Atari ST и Amiga (несколько лет спустя и счет PC AT ).

В 1991 году была выпущена новая версия кошелька Hobbit , который поуживала дискеты о продаже 3 1/2 места, подобная накладке особого чека Atari ST и Amiga (несколько лет спустя и счет PC AT ).

Образец 11: Вариант осмибитового микросчета Хоббит.

Construkce počítačů Hobbit была навржена с охледем на то, абы се тито строй мохли поуживат на школу. Tomuto účelu odpovídá například klávesnice s ruským rozložením kláves s popisky v azbuce a taktéž может propojit jednotlivé počítače mezi sebou pomocí localní sítě o kundostiza rychenosové 6 rychenosové . Na „učitelském“ počítači mohly byt vytvořeny síťové disky sdílené ostatními stroji.

Образец 12: Другой вариант оплаты Hobbit (vlevo), повсимнете си odlišného numerického bloku kláves. На правых страницах вы можете проверить Hobbitu на ZX Spectrem+ 128k.

Kromě obligátního interpretru programovacího jazyka BASIC byl na počítačích Hobbit používán i programovací jazyk FORTH , který produkoval velmi rychlé aplikace – na rozdíl od mnoha dalších implementací FORTHu se totiž prováděl překlad uživatelských programů přímo do strojového kódu микропроцессор Z80 николи tvorba bajtkódu obsahujicího instrukce virtuálního zasobníkového procesoru. Grafické I Zvukové Možnosti Tohoto Počítače Odpovídaly Původnímu ZX Spectru – График -режим Пуживаль Битмапу О.В.В.

Grafické I Zvukové Možnosti Tohoto Počítače Odpovídaly Původnímu ZX Spectru – График -режим Пуживаль Битмапу О.В.В.

Образец 13: Příručka k počítači Hobbit, jeden z nástrojů pro tento počítač a vpravo tvůrce Hobbitu.

7. Почитать Москва и Пентагон-48

Первый серийный производный домашний осмибитовый микросчетчик совместимый с ZX Spectrem в СССР был зарегистрирован по почте Москва . Tento Počítač Existoval ve dvou variantách. Varianta nazvaná Moskva 48K , která začala být vyráběna v roce 1988, byla kompatibilní se ZX Spectrem 48K (tj. se slavným „gumákem“), zatímco varianta Moskva 128K z roku 1989 byla kompatibilní se ZX Spectrem 128k , ovšem s několika rozšířeními – напржіклад был přidáno rozhraní pro ovladaní tiskáren, порт для джойстика, выход на монитор итд.

Образец 14: Jeden ze sovětských klonů ZX Spectra.

Померне Еднодухоу Управоу в запоени почта Москва-48 взникл почта Пентагон-48 . Zmíněná úправа spočívala v odstraní obvodů для генерации RGB-образа. Počítače Pentagon se dále vyvíjely (a vzhledem k poměrně stabilní uživatelské zakladně patrně i stale vyvíjejí), cž je ovšem téma, kterému se budeme věnovat v luisticistic.

Zmíněná úправа spočívala v odstraní obvodů для генерации RGB-образа. Počítače Pentagon se dále vyvíjely (a vzhledem k poměrně stabilní uživatelské zakladně patrně i stale vyvíjejí), cž je ovšem téma, kterému se budeme věnovat v luisticistic.

Образец 15: Часовые изделия синхронизирующих сигналов для генерации изображения на счете Scorpion.

Obrázek 16: Časové průběhy synchronizačních signálů při generování obrazu na počítači Pentagon

8. Obsah následující části seriálu

V následující části seriálu o historii výpočetní techniky si popíšeme (nyní již konečně do větších podrobností) některé další klony ZX Спектры, которые взлетели в СССР. Замерший завод на почтовом отделении Сергей Зоновем , который сконструировал напржиклад днес легендарный почетный дом Ленинград 1 , Leningrad 2 či Scorpion , které jsou mnohými uživateli používány dodnes, i když by v nich sir Sinclair svoje ZX Spectrum pravděpodobně nepoznal – tyto počítače mají mnohdy 1 MB RAM, externí PC klávesnici, myš, adaptér pro připojení Диск IDE, слот для карт ISA, память ROM или емкость 64 КБ с тремя операционными системами и техническими новинками. Více informací си řekneme příště.

Více informací си řekneme příště.

Образец 17: Вариант оплаты Скорпион.

Образек 18: микропочта Пентагон.

Образец 19: Jedna z variant základní desky počítače Pentagon.

Obrázek 20: Ruským hackerům se podařilo upravit loader Windows XP takovým způsobem, že je možné je nabootovat i na ZX Spectru 🙂

9. Odkazy na Internetu

- CPU world: KR580VM80A

http:// www.cpu-world.com/CPUs/8080/USSR-KR580VM80A.html - Википедия EN: KR580VM80A

http://en.wikipedia.org/wiki/KR580VM80A - Компьютер Агат

http://en.wikipedia.org/wiki/Агат_компьютер - Агат 7

http://www.old-computers.com/MUSEUM/computer.asp?st=1&c=509 - Агат 9

http://www.old-computers.com/MUSEUM/computer.asp?c=510 - Особый почет Ахат

http://www.computer-museum.ru/histussr/agat_pc.htm - Страница ностальгии по хоббитам

http://www.tarunz. org/~vassilii/Hobbit/

org/~vassilii/Hobbit/ - Хоббит (компьютер)

http://en.wikipedia.org/wiki/Hobbit_%28computer%29 - ZX Hobbit (русская)

http://zxdimsla.chat.ru/ZXHOBBIT/title.htm - Хоббит

http://www.sincuser.f9.co.uk/126/hobbit.htm - Жестокая ярость!

http://www.ysrnry.co.uk/articles/ragehard0990.htm - Жестокая ярость! (2)

http://www.ysrnry.co.uk/articles/ragehard0191.htm - Наука, технологии и экополитика в СССР (книха)

http://books.google.com/books?id=rrULmz5IVZQC&pg=PA71&dq=agat+computer&cd=6#v=onepage&q=agat%20computer&f=false - Вектор-06С

http://en.wikipedia.org/wiki/Вектор-06С - Поколения ЭВМ: От ламповых «монстров» до интегральных микросхем

http://www.bashedu.ru/konkurs/tarhov/english/generat.htm - Компьютеры и кибернетика в ЦВЕ

http://www.burundi.sk/monoskop/index.php/Computing_and_cybernetics_in_CEE - Дань советской вычислительной технике – часть I

http://www. youtube.com/watch?v=1Zx4NEAAt-E&feature=related

youtube.com/watch?v=1Zx4NEAAt-E&feature=related - Хронология компьютерной истории

http://www.computerhistory.org/timeline/ - Российский виртуальный компьютерный музей: Компьютер Стрела

http://www.computer-museum.ru/english/strela.htm - Российский виртуальный музей вычислительной техники: Автоматическая цифровая вычислительная машина общего назначения «Урал-11»

http://www.computer-museum.ru/english/ural11.htm - ES EVM

- История компьютерного оборудования в странах советского блока

http://en.wikipedia.org/wiki/History_of_computer_hardware_in_communist_countries - Rapira (языковая программа)

http://en.wikipedia.org/wiki/Rapira - Язык рапира (английский)

http://ershov.iis.nsk.su/archive/eaindex.asp?did=7653&lang=2 - Клоны Sinclair

htt://zx.interface1.net/zxclones.htmlp - Русский Самые популярные модели Spectrum (объединенные) FAQ и TECH INFO.