Что такое ПЛИС и с чего начать изучение FPGA Altera

С чего начать изучение FPGA Altera?

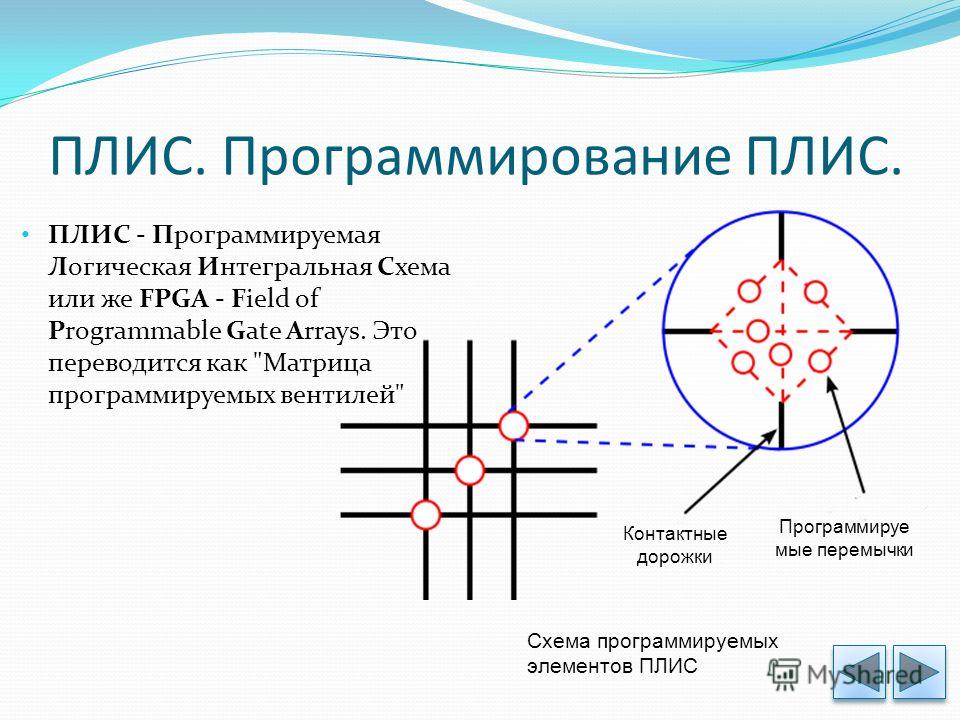

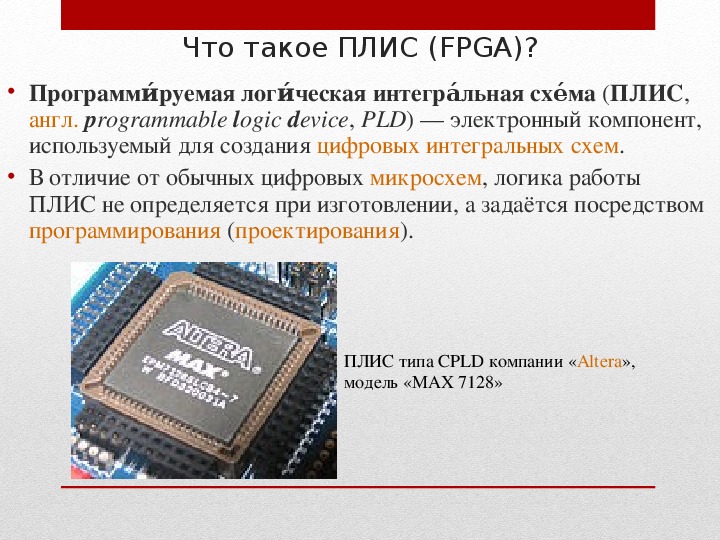

Что такое ПЛИС?

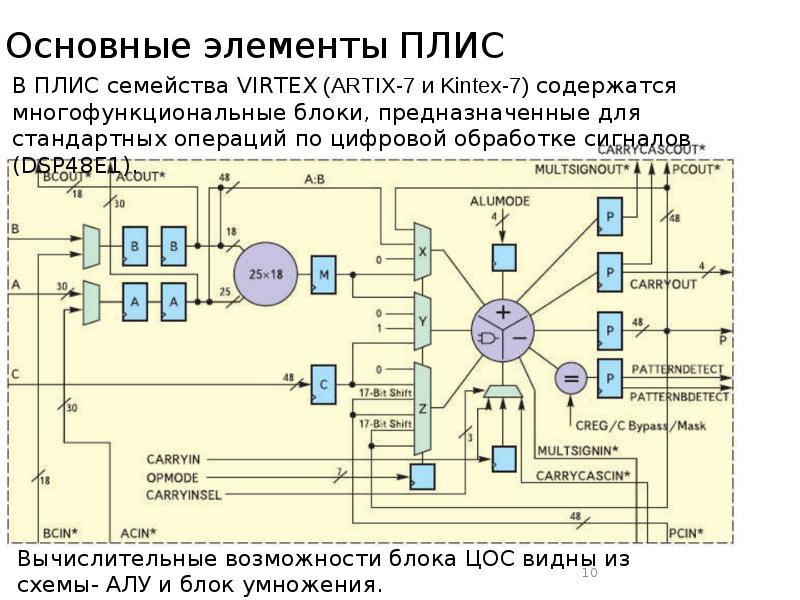

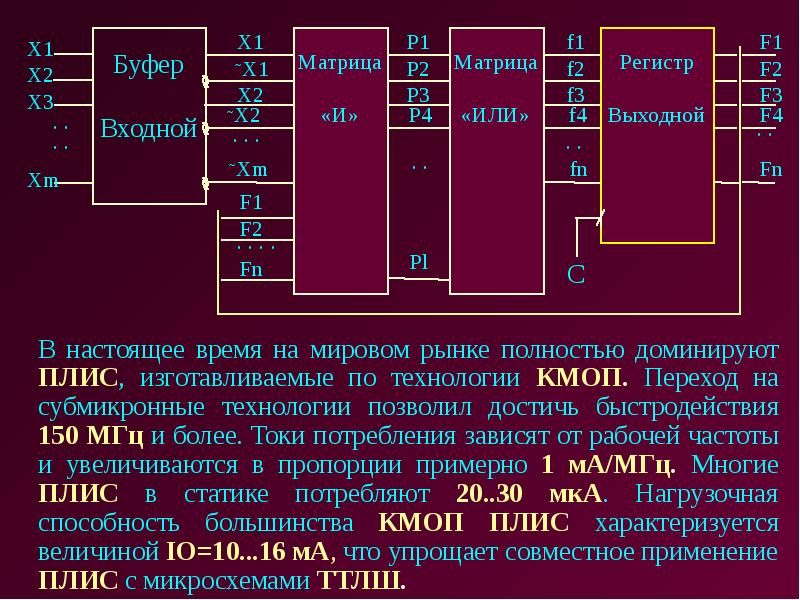

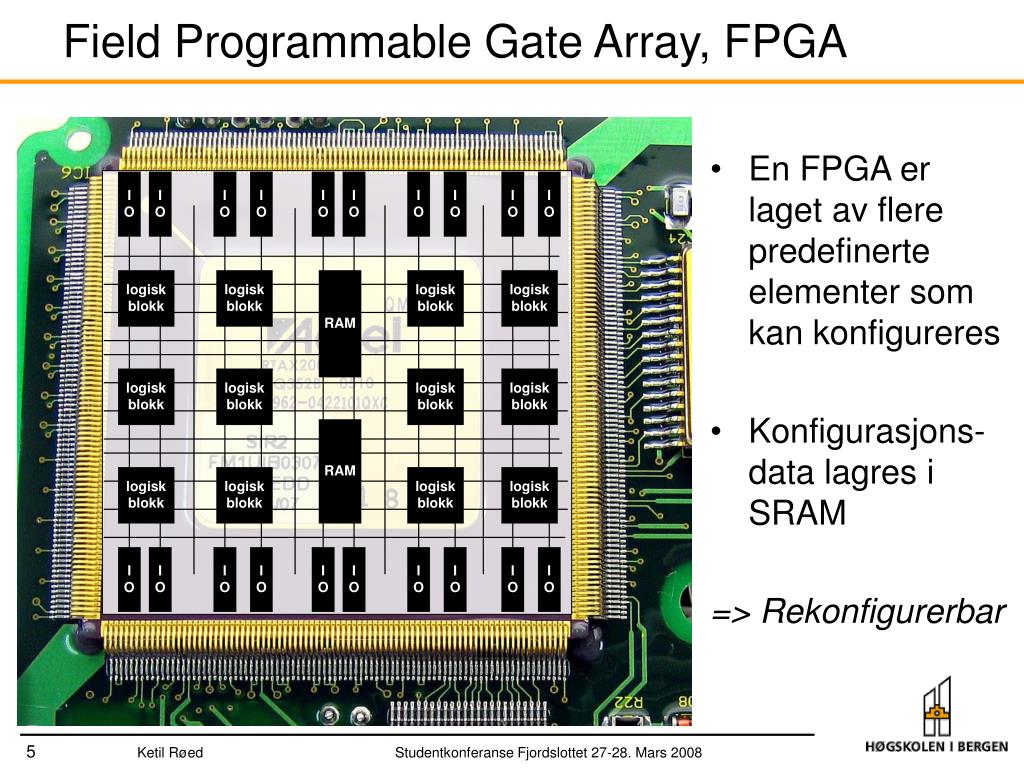

Современные ПЛИС – программируемые логические микросхемы, выполняемые по технологии от 10 нм и содержащие большое количество логических элементов. Элементы могут выполнять простые логические операции «И», «ИЛИ» и др. или реализовывать функции умножителей, сумматоров, мультиплексоров и более сложных устройств.

FPGA – это микросхемы, в которых производителем не определены связи между логическими элементами. Разработчику необходимо самому определять взаимосвязи, назначение выводов и пути прохождения сигналов. В этом заключается большой плюс ПЛИС, так как следствием такого подхода становятся исключительно гибкая архитектура и быстродействие полученной электронной схемы. Но за это приходится платить увеличенным временем разработки устройства.

Как определить срок хранения и срой службы импортных микросхем?

По этим причинам ПЛИС нашли широкое применение в радиоэлектронной аппаратуре, устройствах высокоскоростной параллельной обработки сигналов, микропроцессорной технике.

С чего начать?

К большому сожалению, литературы на русском языке, описывающей принципы функционирования, программирования FPGA практически нет. Нет и чёткого понимания, даже у специалистов, когда применять ПЛИС, а когда программируемый микроконтроллер в повседневных задачах (не связанных с управлением космическими аппаратами или опасным промышленным производством).Начать нужно с главного вопроса – какие задачи вы планируете решать с использованием FPGA?

Если вы разрабатываете шину передачи данных для своего устройства или конструируете плату обработки сигналов с разложением в ряд Фурье, то ПЛИС — это то, что необходимо. Прекрасным решением является и построение отказоустойчивых систем с быстрым временем реакции на основе ПЛИС в системах автоматики.

Это лишь некоторые примеры, позволяющие оценить мощь и гибкость FPGA. Поэтому главными критериями при выборе определим быстродействие и оригинальную архитектуру, ради которых стоит пойти на дополнительные трудозатраты.

Что означают сокращения PCN, EOL, NRND в data sheet импортных электронных компонентов?

Приняв по тем или иным причинам твёрдое решение освоить ПЛИС, встают следующие вопросы – с чего начать и насколько это затратно?По поводу денежных затрат – микросхемы начального уровня, средства программирования и отладки ненамного дороже микроконтроллеров. Освоение сред разработки и языков программирования нисколько не сложнее тех же МК. Всё вышесказанное относится к продукции компании Altera, которую и рассмотрим более детально.

Средства разработки и отладки

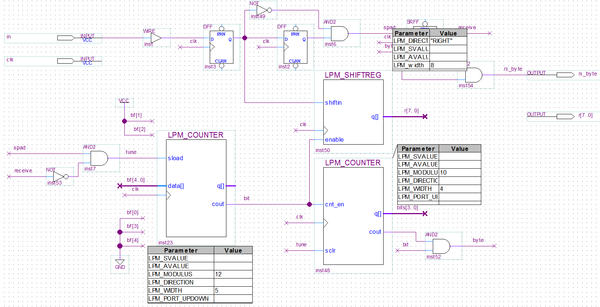

Возникает справедливый вопрос: а как же проектировать и отлаживать такой «зоопарк» различных серий и их версий? Altera позаботилась об этом, создав единую среду проектирования и отладкиК достоинствам продукта относятся:

- Возможность создания проекта на языках VHDL, Verilog или в графическом редакторе.

- Ведение всей фоновой работы по созданию конфигурационного файла ПЛИС, включая разводку в кристалле.

- Загрузка конфигурационного файла в ПЛИС и внутрисхемная отладка.

Для загрузки и отладки проектов в микросхемах поставляются программаторы в двух исполнениях – для LPT и USB портов.

Начало работы с FPGA Altera

Оптимальным для работы с продуктами Altera будет следующий алгоритм действий:1. Чётко сформулировать задачу, для решения которой предполагается использование ПЛИС

- Определите необходимое количество входов/выходов

- Уровень напряжения

- Перечень логических операций

- Допустимую задержку прохождения сигнала от входа на выход

- Другие параметры, критичные при выполнении задачи.

Ознакомиться с документацией на ПЛИС, скачав руководство с сайта производителя.

3. Скачать по этой ссылке и установить среду разработки Quartus.

Для продуктов Quartus Prime Lite Edition, Quartus II Web Edition, ModelSlim-Intel FPGA Starter Edition лицензия не требуется. Бесплатной версии вполне хватит для ознакомления со средой. Изучить среду разработки, пользуясь встроенной справкой и документацией на сайте Altera.

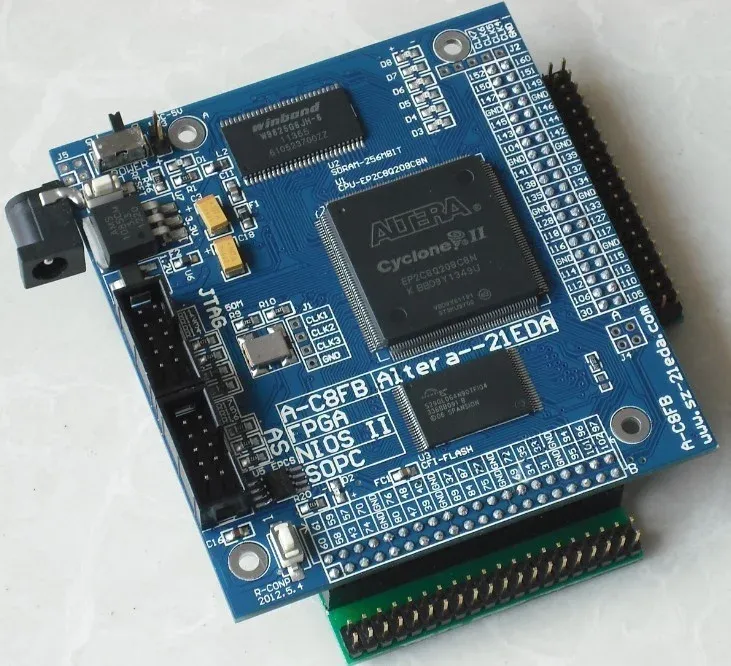

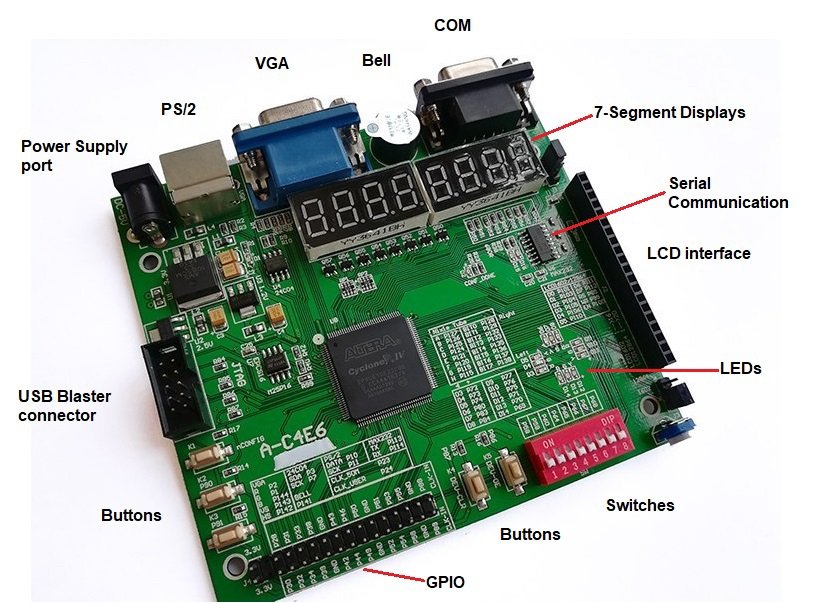

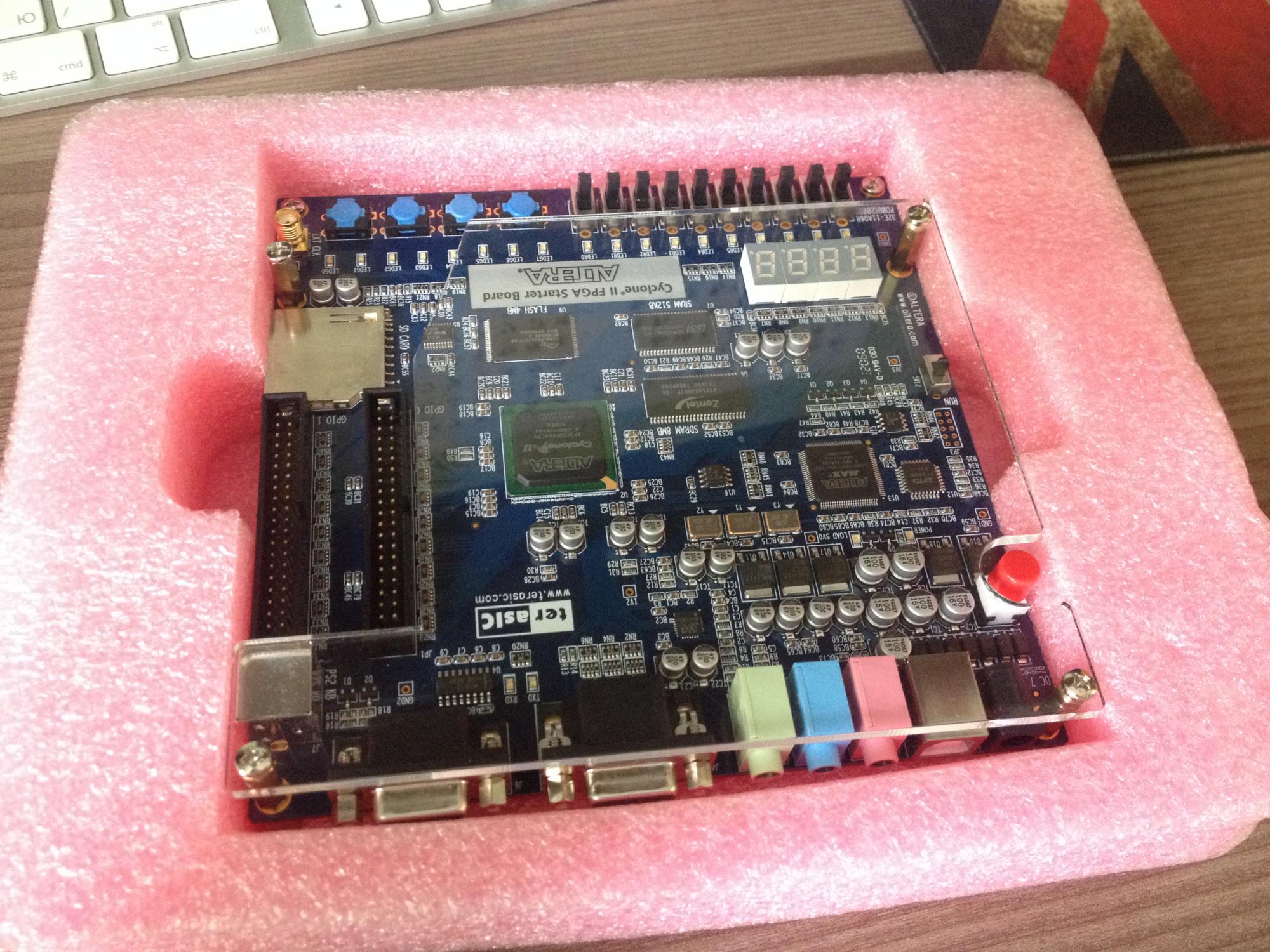

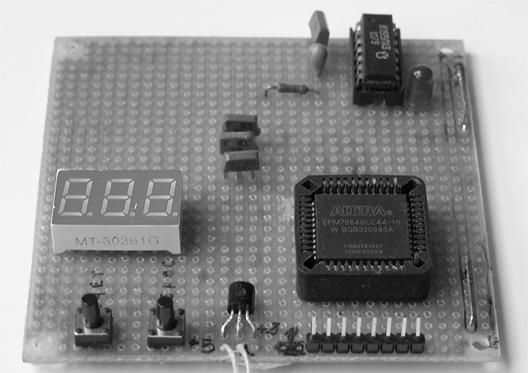

4. Приобрести ПЛИС Altera и программатор с параллельным или usb-портом.

5. Разработать и отладить проект своего устройства на ПЛИС.

Собрать электрическую схему, загрузить проект в микросхему, проверить полученный результат. При необходимости внести изменения в проект, воспользоваться возможностями внутрисхемной отладки.

Заявка на поставку импортных ПЛИС Altera

Получить подробную информацию о поставляемых брендах и условиях сотрудничества можно тут: https://import.el-ra.ru

Получить подробную информацию о поставляемых брендах и условиях сотрудничества можно тут: https://import.el-ra.ruКроме этого, мы выполняем полный комплекс услуг по организации проверки и испытаниям электронных компонентов импортного производства, включая входной контроль, проверку на работоспособность, а также специальные проверки, механические и климатические испытания.

Если вы заинтересованы в работы с нами, то заполните форму по ссылке: www.el-ra.ru/zayavka

ПЛИС. С чего начать? | IT. Как это работает?

Видео в конце…

С этого выпуска начинается изучение языка описания аппаратуры Verilog. При помощи него мы сможем разобраться со всем спектром вопросов, встающих перед разработчиками аппаратной части систем обработки информации. Вход в эту область разработки для нас будет сильно затруднен, если мы не овладеем базовыми знаниями.

Среди двух наиболее популярных языков описания аппаратуры выбор языка Verilog нельзя обосновать железобетонно, вместе с языком VHDL, они используются в равной степени. Они настолько похожи и повторяют друг друга, что очень даже хорошо совместимы между собой в одном проекте. Verilog выглядит более предпочтительным только ввиду чуть большей компактности исходного кода, а также возможности попробовать свои силы на одном из самых низких уровней описания цифровой аппаратуры. В нем есть возможность описывать схемы на транзисторном уровне.

Они настолько похожи и повторяют друг друга, что очень даже хорошо совместимы между собой в одном проекте. Verilog выглядит более предпочтительным только ввиду чуть большей компактности исходного кода, а также возможности попробовать свои силы на одном из самых низких уровней описания цифровой аппаратуры. В нем есть возможность описывать схемы на транзисторном уровне.

В составе среды разработки проектов для ПЛИС есть средство моделирования, которое необходимо при отладке, покупка отладочного комплекта желательна, но не является необходимостью.

Что такое модуль?И так, приступим. Язык Verilog обладает некоторым списком ключевых слов, которые употребляются строго из-за какой-то необходимости. Вот на этих примерах употребления мы и начнем разбираться с особенностями языка. Первое, с чем мы сталкиваемся это понятие модуля.

Рассмотрим пример описания МОП транзистора pmos типа при помощи языка Verilog. Каждое проектируемое устройство должно быть оформлено средствами языка в виде функционального модуля с конечным числом входов и выходов. Между ключевыми словами module и endmodule содержится описание модуля.

Между ключевыми словами module и endmodule содержится описание модуля.

После указания имени модуля, в круглых скобках описываются входы и выходы модуля. Ключевым словом pmos обозначен экземпляр транзистора pmos типа с именем p1. В круглых скобках описываются соединения транзистора с входами и выходами функционального модуля. Порядок следования соединений соответствует строгой схеме. Первым в списке находится исток, потом сток и последним будет затвор. Положение затвора на схеме определить совсем не сложно. Конкретное нахождение истока и стока на схеме можно запомнить простым правилом. Направление условного потока электронов идет от выходов ко входам. Все что у транзисторов подключается к выходам прямо или косвенно, будет истоком. Все что прямо или косвенно подключается к земле или питанию, будет стоком.

Проверим работоспособность

Средство моделирования поддерживает проверку работоспособности устройства, описанного на транзисторном уровне при помощи языка Verilog. При моделировании разработанного модуля создается файл с описанием модуля тестирования, который не имеет ни входов ни выходов.

При моделировании разработанного модуля создается файл с описанием модуля тестирования, который не имеет ни входов ни выходов.

Внутри модуля тестирования объявляется один или более экземпляров тестируемого модуля, проводники для передачи тестовых сигналов на модуль, а также проводники для считывания выходных сигналов тестируемого модуля. Рассмотрим пример теста транзистора pmos типа.

В модуле тестирования создается экземпляр модуля u1 , вспомогательные регистры x1, g1 для передачи тестового воздействия на экземпляр модуля u1, проводник y1 для считывания выходного сигнала модуля при воздействии тестовых сигналов. В приведенном языковом описании тестового модуля ключевое слово timescale служит для указания симулятору шага времени и точности. Шаг времени одна наносекунда задает единицу измерения времени, последующие директивы вроде числа 100 — количество единиц времени для временной задержки между изменениями тестовых воздействий. Точность служит для округления времени задержки в большую сторону до дискретного значения, число, указанное в качестве точности задает дискретность.

Точность служит для округления времени задержки в большую сторону до дискретного значения, число, указанное в качестве точности задает дискретность.

Идентификатор pmos_tb определяет имя тестового модуля. Ключевое слово wire указывает симулятору на необходимость задания проводника для считывания реакции модуля на тестовые воздействия. Ключевое слово reg служит для обозначения несуществующих в действительности регистров, связанных со входами тестируемого модуля.

Эта строка объявляет экземпляр u1 модуля и связывает входы и выходы тестируемого модуля с внутренними проводниками и регистрами тестового модуля. После ключевого слова initial задаются действия, выполняемые 1 раз при запуске теста, в указанном случае такие действия содержатся ниже между ключевыми словами begin и end. Тестовые воздействия описываются в нужном пользователю порядке и необходимыми паузами между ними. В случае отсутствия паузы между различными воздействиями симулятор принимает их строго одновременными во времени. Например, в этой строке одновременное возникновение уровня логического нуля на проводниках x1 и g1. После паузы в 100 наносекунд будет одновременная смена состояния сигналов на линиях.

Например, в этой строке одновременное возникновение уровня логического нуля на проводниках x1 и g1. После паузы в 100 наносекунд будет одновременная смена состояния сигналов на линиях.

Для моделирования цифровых устройств в комплект среды разработки входит приложение Modelsim. В использовании довольно просто. Главное это уже иметь готовые описания модуля и теста для него. Результат моделирования представлен на рисунке.

Результат моделирования pmos транзистораПри подаче уровня логического нуля на затвор транзистора происходит передача сигнала через транзистор со стока на исток. При подаче уровня логической единицы, транзистор принимает состояние высокого сопротивления, что при моделировании отмечается высокоомным состоянием Z на истоке. Это показано синим цветом. В случае nmos транзистора временные диаграммы будут выглядеть иначе.

Результат моделирования nmos транзистораВходной сигнал окажется на выходе только тогда, когда на затворе логическая единица. При подаче уровня логического нуля на затвор транзистора nmos типа, происходит его запирание, что выражается появлением Z-состояния на истоке. То есть состояния высокого сопротивления. Отсутствие проводимости.

При подаче уровня логического нуля на затвор транзистора nmos типа, происходит его запирание, что выражается появлением Z-состояния на истоке. То есть состояния высокого сопротивления. Отсутствие проводимости.

Немного усложним

На этом шаге мы слегка познакомились со средой моделирования и выяснили что означают некоторые ключевые слова языка. Давайте двинемся дальше. Опишем инвертор на транзисторном уровне. Он состоит из комплементарной пары транзисторов. Они имеют вот такое подключение и в этой схеме есть линии питания и земли.

Описание инвертора на транзисторном уровнеВ языке описания аппаратуры по большому счету два стиля описания. Это структурный и поведенческий. Поведенческий описывает поведение модуля. Структурный описывает то, из чего модуль состоит. Вот сейчас и познакомимся со структурным стилем описания модуля.

В нашем модуле кроме привычных уже ключевых слов описания входов и выходов появился список из составных частей устройства. Supply0 это проводник связанный с землей схемы. Supply1 это проводник питания схемы, она же логическая единица. Ниже два транзистора и с ними мы уже знакомы. Посмотрите внимательно порядок подключения. Исток, сток, затвор. Исток у обоих это выход схемы. У одного сток на питании, у другого на земле. Затворы обоих транзисторов подключены ко входу схемы.

Supply0 это проводник связанный с землей схемы. Supply1 это проводник питания схемы, она же логическая единица. Ниже два транзистора и с ними мы уже знакомы. Посмотрите внимательно порядок подключения. Исток, сток, затвор. Исток у обоих это выход схемы. У одного сток на питании, у другого на земле. Затворы обоих транзисторов подключены ко входу схемы.

В написании теста для инвертора теперь нет сложностей. Одна входная линия, одна выходная. Сам инвертор структурно входит в модуль теста и подключен к линиям тестирующего модуля. В секции задания уровней сигнала все тоже довольно предсказуемо. Начальное состояние ноль на входе продержится 200 наносекунд, потом сменится на единицу и продержится тысячу наносекунд.

Тест инвертораРезультат моделирования в случае отсутствия ошибок в описании модуля будет такой. Если на входе ноль, на выходе единица и если единица на входе, то ноль на выходе.

Результат моделирования инвертораДавайте еще кое-что рассмотрим один раз чтобы потом не возвращаться. Слева на рисунке изображена схема вентиля ИЛИ-НЕ с тремя входами.

Слева на рисунке изображена схема вентиля ИЛИ-НЕ с тремя входами.

С целью упрощения конструкции, иногда применяют подтягивание к питанию, что избавляет схему от множества транзисторов. Один резистор, вставленный перед питанием позволяет схеме как и прежде выполнять свои функции. Выставленные нули на всех входах закроют все транзисторы, при этом на выход пойдет напряжение питания, она же логическая единица. Любая единица на входе откроет транзистор и по закону Ома напряжение земли пойдет на выход. Резистор избавляет схему от короткого замыкания.

Подтяжка резистором к питанию описывается ключевым словом pullup.

Описание вентиля 3ИЛИ-НЕВ скобках записано, что выход схемы подтянут к питанию. Остальные элементы нам уже знакомы. Это по прежнему структурный стиль описания. Напишем модуль тестирования. Для этого нам потребуется три входных линии, одна выходная.

Тест вентиля 3ИЛИ-НЕВписываем разработанный вентиль в структуру теста и соединяем его контакты с линиями тестирующего модуля. Ниже каждые 100 наносекунд перебираем все возможные комбинации входных сигналов. Все работает согласно таблице истинности. В случае трех нулей на входе, будет единица на выходе.

Ниже каждые 100 наносекунд перебираем все возможные комбинации входных сигналов. Все работает согласно таблице истинности. В случае трех нулей на входе, будет единица на выходе.

Эта единица особенно отображается пунктиром, чтобы не забывать что она получена с питания через резистор. Пожалуй, про транзисторы хватит. Главное в этом то, что рассмотрен структурный стиль описания и несколько языковых оборотов.

К сожалению, устройство ПЛИС не такое, чтобы пробовать прошить ее схемами на транзисторном уровне. Сейчас мы только учимся моделировать результаты своего творчества. Со следующего видео мы начнем разрабатывать проекты для ПЛИС и осваивать все необходимое для понимания сути параллельных вычислений.

Продолжение следует…

Поддержите статью лайком если понравилось и подпишитесь чтобы ничего не пропускать.

Программирование FPGA, с чего начать

Цифровой дизайн не имеет ничего общего с разработкой программного обеспечения (возможно, за исключением того, что синтаксис Verilog немного похож на язык C, но выглядит только так). Таким образом, очень сложно ответить на этот тип вопросов адекватно. Но как парень, который прошел путь от разработки программного обеспечения до проектирования оборудования, я попробую. Оглядываясь назад на себя, я бы посоветовал себе тогда, если бы знал, что знаю сейчас:

Забудьте все о разработке программного обеспечения. Особенно языки программирования. Эти принципы не применяются в цифровом дизайне. Вероятно, было бы легко для парня, который проектировал процессор, программировать его на ассемблере или даже на C, но программист на ассемблере не сможет проектировать процессор.

На вашем пути обучения не склонны решать то, что кажется легкой проблемой с вашими существующими знаниями из программного обеспечения. Одним из классических примеров является «цикл». Даже если вы можете написать цикл for, скажем, в verilog – он служит другим целям. Он в основном используется для генерации кода. Это также может быть цикл for, как его видят разработчики программного обеспечения, но он ничего не даст, кроме симуляции (то есть вы не сможете программировать FPGA таким образом).

Поэтому для каждой задачи, которую вы хотите решить, не думайте, что знаете, как это сделать, вместо этого проведите исследование – проверьте книги, примеры, спросите более опытных людей и т. Д.

Самые популярные языки HDL – Verilog и VHDL. Есть также специфичные для производителя, такие как AHDL (Altera HDL). Поскольку эти языки используются для описания аппаратных компонентов, все они в значительной степени используются для выражения одного и того же в схожих модах, но с другим синтаксисом.

Некоторые люди рекомендуют изучать Verilog, потому что он выглядит как C. Да, его синтаксис представляет собой смесь C и Ada, но он не облегчает разработку программного обеспечения. На самом деле, я думаю, что это может даже ухудшить ситуацию, потому что будет искушение написать C на Verilog. Это хороший рецепт для очень плохого времени.

На самом деле, я думаю, что это может даже ухудшить ситуацию, потому что будет искушение написать C на Verilog. Это хороший рецепт для очень плохого времени.

Имея это в виду, я бы порекомендовал посмотреть с VHDL. Хотя с Verilog тоже все в порядке, если учесть вышеизложенное.

Важно помнить, что вы должны понимать, что вы выражаете на этом языке. Какое оборудование «описывается» и как оно работает.

По этой причине я бы порекомендовал вам приобрести какую-нибудь книгу по электронике в целом и такую хорошую книгу, как эта – HDL Chip Design (она же синяя книга).

Прежде чем начать что-либо делать аппаратно и использовать какие-либо специфичные для поставщика функции и т. Д., Приобретите себе симулятор. Я начинал с Verilog и использовал Icarus Verilog вместе с GTK Wave. Это бесплатные проекты с открытым исходным кодом. Используйте примеры, которые вы видите в книгах, попрактикуйтесь, создав собственные схемы, чтобы почувствовать вкус этого.

Когда вам захочется идти вперед, возьмите доску для разработки.

Методы программирования очень похожи, но есть детали, которые отличаются. Например, разные инструменты, разные опции, разные интерфейсы. Обычно, если у вас есть опыт работы с одним поставщиком, переключиться не сложно. Но вы, вероятно, хотите избежать этой дополнительной кривой обучения.

Я бы также позаботился о том, чтобы на плате были компоненты, которые вы планируете использовать или которые можно расширять. Например, если вы хотите спроектировать сетевое устройство, например, маршрутизатор, убедитесь, что на плате установлен Ethernet PHY или его можно расширить, например, через разъем HSMC и т. Д.

Платы обычно идут с хорошим справочником, руководством пользователя и примерами дизайна. Изучите их.

Вам нужно будет читать книги. В моем случае у меня не было друзей, знакомых с цифровым дизайном, и этот сайт тоже не очень помог из-за одной простой вещи – я даже не знал, как сформулировать свой вопрос.

Я лично начал с этого:

У поставщиков ПЛИС есть много поваренных книг с лучшими практиками. Изучите их вместе с эталонными конструкциями. Вот один из Альтера, например.

Пока вы просматриваете свои книги, имитируете дизайн, мигаете несколькими светодиодами на вашей плате разработки, у вас, скорее всего, возникнет много вопросов. Убедитесь, что вы не видите ответов на них на следующей странице книги или в Интернете (то есть на форуме, посвященном решетке), прежде чем задавать их здесь.

fpga — Программирование FPGA, с чего начать

Цифровой дизайн не имеет много общего с разработкой программного обеспечения (возможно, кроме того, что синтаксис Verilog немного похож на язык C, но он просто выглядит). Таким образом, очень трудно адекватно ответить на этот вопрос. Но, как парень, который прошел путь от разработки программного обеспечения до аппаратного дизайна, я дам ему шанс. Оглядываясь на себя, вот как бы я тогда посоветовал себя, если бы знал, что знаю сейчас:

Но, как парень, который прошел путь от разработки программного обеспечения до аппаратного дизайна, я дам ему шанс. Оглядываясь на себя, вот как бы я тогда посоветовал себя, если бы знал, что знаю сейчас:

Забудьте все о разработке программного обеспечения. Особенно языки программирования. Эти принципы не применяются в цифровом дизайне. Вероятно, для парня, спроектировавшего CPU для программирования его на ассемблере или даже C, было бы легко, но программист ассемблера не сможет проектировать CPU.

На вашем учебном пути не решаются проблемы, которые кажутся легкой проблемой для ваших существующих знаний из программного обеспечения. Один из классических примеров – «цикл». Несмотря на то, что вы можете написать цикл for, скажем, verilog, для других целей. Он в основном используется для генерации кода. Это может быть цикл for, как это видят разработчики программного обеспечения, но это не будет хорошо для чего-либо, кроме симуляции (т. Е. Вы не сможете запрограммировать FPGA).

Итак, для каждой задачи, которую вы хотите решить, не думайте, что вы знаете, как это сделать, сделайте исследование вместо этого – проверьте книги, примеры, спросите более опытных людей и т. д.

Самыми популярными языками HDL являются Verilog и VHDL. Существуют также специфические для вендора, такие как AHDL (Altera HDL). Поскольку эти языки используются для описания аппаратных компонентов, все они в значительной степени используются для выражения одной и той же вещи в аналогичных моделях, но с другим синтаксисом.

Некоторые люди рекомендуют изучать Verilog, потому что это похоже на C. Да, его синтаксис представляет собой сочетание C и Ada, но разработчику программного обеспечения нелегко опереться. На самом деле, я думаю, это может даже ухудшить ситуацию, потому что будет соблазн написать C в Verilog. Это хороший рецепт для очень плохого времени.

Имея это в виду, я бы рекомендовал посмотреть на VHDL. Хотя Verilog также в порядке, если учтено это.

Важно помнить, что вы должны понимать, что вы выражаете на этом языке. Какое оборудование «описано» и как оно работает.

По этой причине я бы порекомендовал вам получить книгу о электронике в целом и хорошую книгу, подобную этой: «a href =» http://rads.stackoverflow.com/amzn/click/0965193438 “> HDL Chip Design (также как синяя книга).

Прежде чем начинать что-либо делать на аппаратных средствах и использовать любые специфические для Vendor функции и т. д., сделайте себе симулятор. Я начинал с Verilog и использовал Icarus Verilog вместе с GTK Wave. Это бесплатные проекты с открытым исходным кодом. Запускайте примеры, которые вы видите в книгах, практикуйте, создавая свои собственные схемы, чтобы получить некоторый вкус.

Когда вам хочется идти вперед, получите совет по развитию. Если вы знаете, что ваш работодатель хочет пойти с Lattice, тогда получите плату Lattice.

Методы программирования очень похожи, но есть разные детали. Например, различные инструменты, разные параметры, разные интерфейсы. Обычно, если у вас есть опыт работы с одним поставщиком, его нетрудно переключить. Но вы, вероятно, хотите избежать этой дополнительной кривой обучения.

Обычно, если у вас есть опыт работы с одним поставщиком, его нетрудно переключить. Но вы, вероятно, хотите избежать этой дополнительной кривой обучения.

Я также должен убедиться, что плата поставляется с компонентами, которые вы планируете использовать или может расширяться. Например, если вы хотите создать сетевое устройство, такое как маршрутизатор, убедитесь, что плата имеет Ethernet PHY или ее можно расширить, например, через разъем HSMC и т. Д.

Платы обычно поставляются с хорошей ссылкой, руководством пользователя и примерами дизайна. Изучите их.

Вам нужно будет читать книги. В моем случае у меня не было друзей, которые знали цифровой дизайн, и этот сайт не очень помог ни из-за одной простой вещи – я даже не знал, как рассказать о моем вопросе. ВсеЯ мог придумать: «Ух, ребята, есть вещь dcfifo, и я слышал что-то о проблемах с переходом к часам, что это такое и почему мой дизайн не работает?».

Я лично начал с них:

У продавцов FPGA много кулинарных книг с лучшими практиками. Изучите их вместе с эталонными проектами. Здесь является, например, один из Altera.

Изучите их вместе с эталонными проектами. Здесь является, например, один из Altera.

Пока вы просматриваете свои книги, имитируйте дизайн, мигайте некоторыми светодиодами на доске разработки, у вас, скорее всего, будет много вопросов. Убедитесь, что вы не видите ответа на те, которые находятся на следующей странице книги или в Интернете (например, на форуме, посвященном решетке), прежде чем спрашивать их здесь.

Учимся программировать под FPGA на SystemVerilog

ПЛИС (Программируемая Логическая Интегральная Схема) — это интегральная схема, предназначенная для построения цифровых цепей из описания на специальном языке программирования. Другими словами, ПЛИС представляет собой чип, как бы содержащий в себе кучу элементов наподобие 74HCxx. Какие именно это будут логические элементы, какие между ними будут связи, и какие связи будет иметь получившаяся схема с внешним миром, определяется на этапе программирования ПЛИС.

Примечание: Насколько я смог выяснить, в русском языке на сегодняшний день термины ПЛИС и FPGA (Field-Programmable Gate Array, Программируемая Пользователем Вентильная Матрица), принято считать взаимозаменяемыми, что будет использовано далее по тексту. Однако стоит знать о существовании и альтернативной точки зрения, согласно которой FPGA (ППВМ) является одной из разновидностей ПЛИС (PLD, Programmable Logic Device).

Однако стоит знать о существовании и альтернативной точки зрения, согласно которой FPGA (ППВМ) является одной из разновидностей ПЛИС (PLD, Programmable Logic Device).

Основные сведения об FPGA

Для программирования FPGA используются языки описания аппаратуры (HDL, Hardware Description Language). Среди них наибольшей популярностью пользуются Verilog (и его диалекты, в частности SystemVerilog), а также VHDL. Языки во многом похожи, но имеют разный синтаксис и различаются в некоторых деталях. Если Verilog — это такой C мира описания аппаратуры, то VHDL — соответственно, Pascal. Насколько мне известно, VHDL несколько менее популярен, в частности, из-за его многословности по сравнению с Verilog. Из преимуществ VHDL (или недостатков, кому как) можно назвать строгую статическую типизацию. Verilog же иногда допускает неявное приведение типов. Если продолжать аналогию с C и Pascal, языки различаются не настолько сильно, чтобы не выучить их оба.

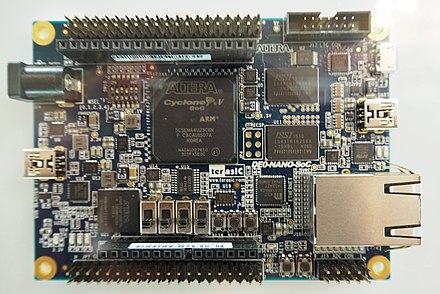

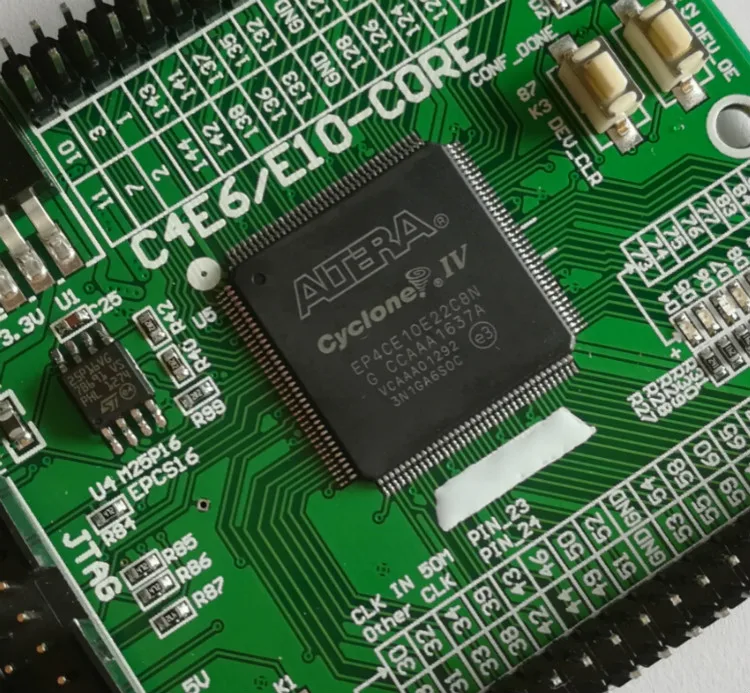

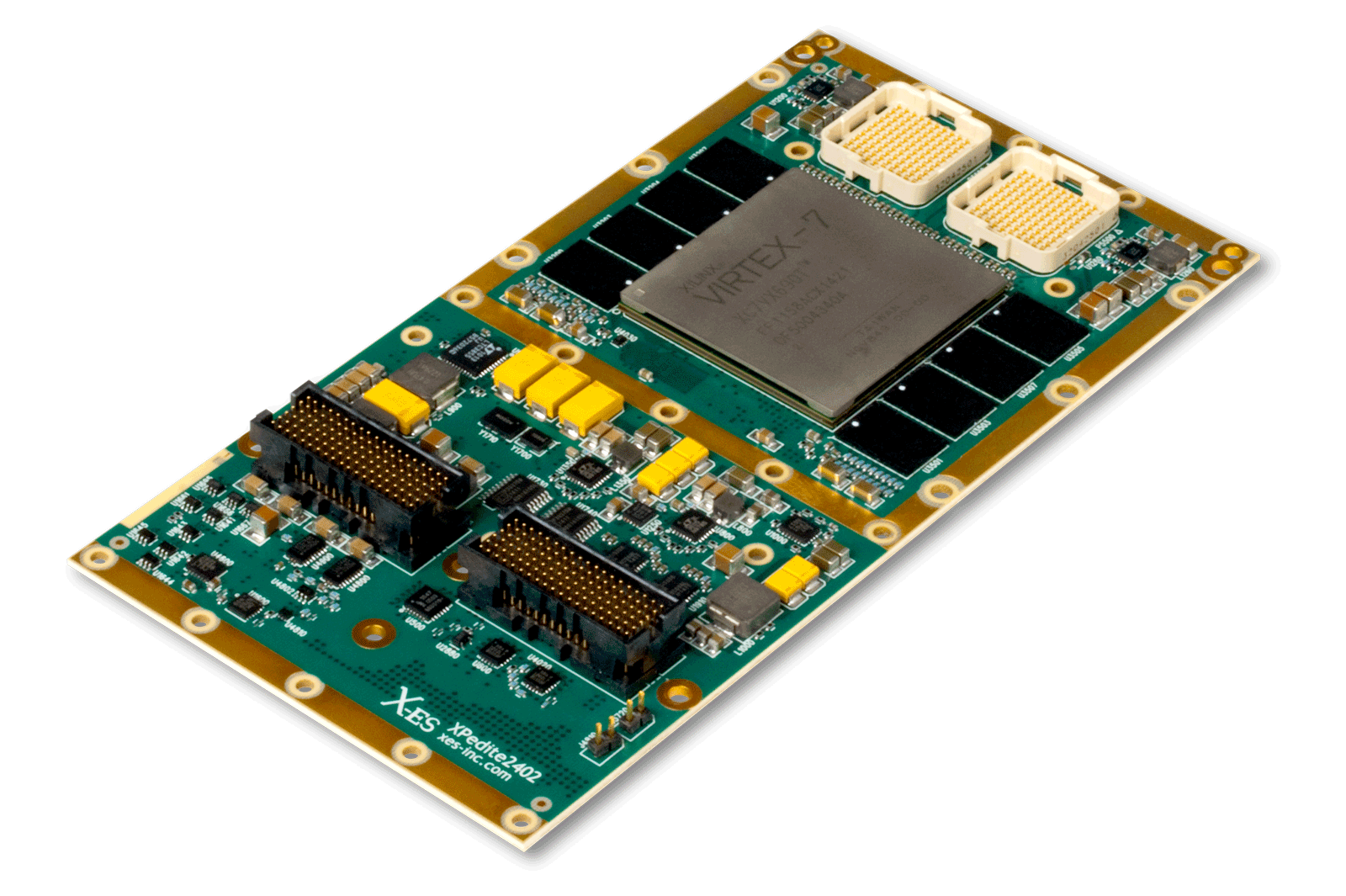

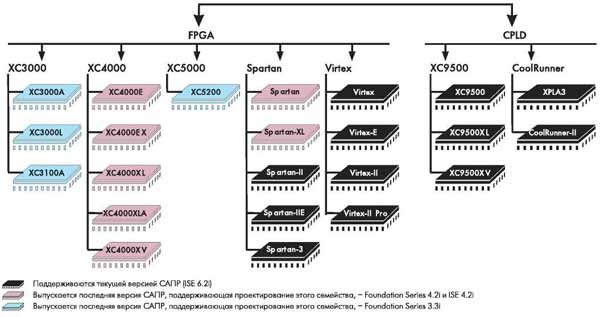

На данный момент лидирующими производителями FPGA являются компании Altera (сейчас принадлежит Intel) и Xilinx. По информации из разных источников, вместе они контролируют не менее 80% рынка. Из других игроков стоит отметить Actel (куплена Microsemi), Lattice Semiconductor, Quicklogic и SiliconBlue. С железом от Xilinx можно работать только из среды разработки от Xilinx (называется Vivado), а среда разработки от Altra (называетя Quartus) понимает только железо от Altera. То есть, полный вендор лок, и выбирая конкретную FPGA для своего проекта, вы автоматически выбираете и инструменты разработки соответствующего производителя, их техническую поддержку, документацию, условия лицензирования софта, политику касаемо прекращения поддержки железа, и так далее.

По информации из разных источников, вместе они контролируют не менее 80% рынка. Из других игроков стоит отметить Actel (куплена Microsemi), Lattice Semiconductor, Quicklogic и SiliconBlue. С железом от Xilinx можно работать только из среды разработки от Xilinx (называется Vivado), а среда разработки от Altra (называетя Quartus) понимает только железо от Altera. То есть, полный вендор лок, и выбирая конкретную FPGA для своего проекта, вы автоматически выбираете и инструменты разработки соответствующего производителя, их техническую поддержку, документацию, условия лицензирования софта, политику касаемо прекращения поддержки железа, и так далее.

FPGA часто используются в задачах, где некие вычисления хочется существенно ускорить, реализовав их прямо в железе. Например, FPGA нашли широкое применение в области обработки сигналов, скажем, в осциллографах, анализаторах спектра, логических анализаторах, генераторах сигналов, Software Defined Radio и даже некоторых мониторах. В частности, в LimeSDR используется Altera Cyclone IV, а в осциллографе Rigol DS1054Z стоит Xilinx Spartan-6, а также ProASIC 3 от компании Actel. Еще из применений, о которых я слышал, могу назвать компьютерное зрение, распознавание речи и биоинформатику. Есть и другие проекты, в частности по разработке веб-серверов и СУБД, работающих на FPGA [PDF]. Но, насколько мне известно, это направление все еще остается сильно экспериментальным.

Еще из применений, о которых я слышал, могу назвать компьютерное зрение, распознавание речи и биоинформатику. Есть и другие проекты, в частности по разработке веб-серверов и СУБД, работающих на FPGA [PDF]. Но, насколько мне известно, это направление все еще остается сильно экспериментальным.

Xilinx или Altera?

Как говорится, лучший Linux тот, который использует ваш знакомый гуру по Linux.

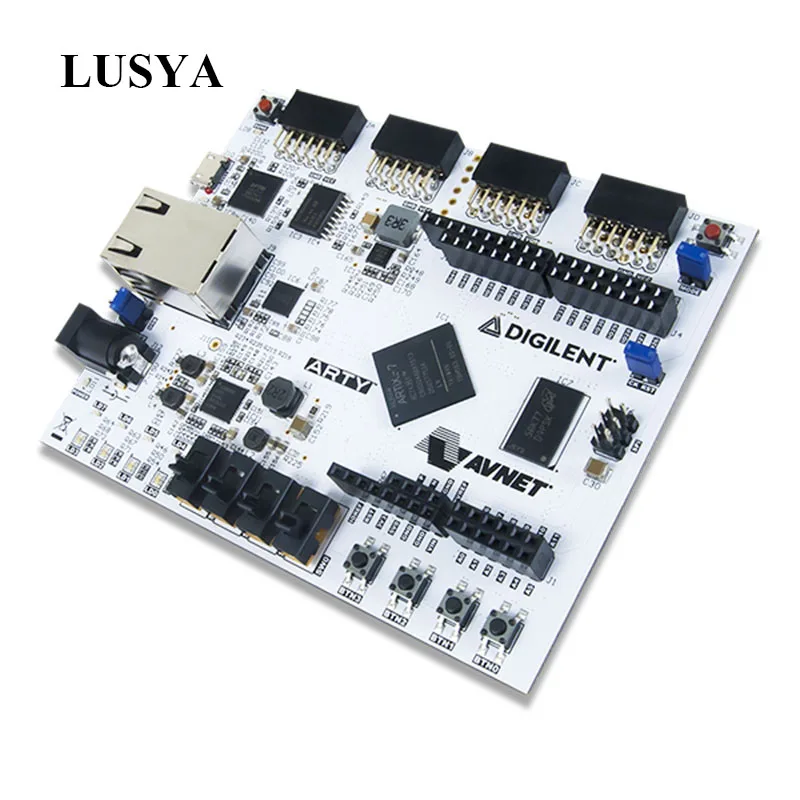

Мой знакомый гуру по FPGA в лице Дмитрия Олексюка посоветовал начать с девборды Arty Artix-7 от компании Digilent. Используемой в ней FPGA является Artix-7 от Xilinx. Сам Digilent не производит доставку в Россию, но устройство доступно и на AliExpress, хотя и с заметной наценкой (официальная цена составляет 99$). Также его продают на eBay. Это довольно мощная плата, которая, тем не менее, стоит вполне адекватных денег.

Fun fact! Если вам просто хочется попрограммировать на Verilog или VHDL, строго говоря, покупать какую-либо плату с FPGA не требуется. Первое время можно ограничиться симулятором, работа с которым будет рассмотрена далее.

Из интересных особенностей платы можно назвать расположение гнезд совместимым с Arduino-шилдами способом. Также в комплекте с платой идет вкладыш, по которому можно получить лицензию на Vivado, открывающую все его возможности. Лицензия действует один год с момента активации, а также привязана к одному компьютеру по типу ОС и MAC-адресу.

По доставке. Я слышал, что устройства с FPGA на борту имеют большие шансы не пройти таможню. Магазин на AliExpress, ссылку на который я привел выше, доставляет платы в Россию через курьерскую службу СПСР. Для прохождения таможни потребовалось заполнить онлайн-форму с паспортными данными (только данные, без фото) и контактным телефоном, как этого требует текущее российское законодательство. После этого плата была доставлена курьером прямо до двери без каких-либо вопросов.

Установка Vivado

Среда разработки Vivado доступна для скачивания на сайте Xilinx. Будьте морально готовы к тому, что перед скачиванием вам придется пройти регистрацию и заполнить довольно подробную форму о себе. Скачиваем архив под названием «Vivado HLx 2017.2: All OS installer Single-File Download». Не перепутайте случайно с каким-нибудь «Vivado Lab Solutions», это совершенно не то, что нужно. Архив весит более 20 Гб, поэтому запасаемся терпением.

Скачиваем архив под названием «Vivado HLx 2017.2: All OS installer Single-File Download». Не перепутайте случайно с каким-нибудь «Vivado Lab Solutions», это совершенно не то, что нужно. Архив весит более 20 Гб, поэтому запасаемся терпением.

Распаковываем архив, запускаем инсталлятор. Ставим Vivado HL System Edition. Полная его версия займет на диске 47 Гб. Лично я снял галочку напротив Software Development Kit и оставил поддержку только 7 Series устройств, что уменьшило размер до 12 Гб. Забегая немного вперед отмечу, что такой конфигурации оказалось вполне достаточно.

Перед запуском Vivado нужно добавить в него поддержку Arty Artix-7, так как из коробки он ничего об этой плате не знает. Делается это как-то так:

cd ~/opt/xilinx/Vivado/2017.2/data/boards/board_files

wget https://github.com/Digilent/vivado-boards/archive/master.zip

unzip master.zip

mv vivado-boards-master/new/board_files/* ./

rm -r vivado-boards-master

rm master.zip

Также скачиваем отсюда и сохраняем куда-нибудь файл Arty_Master. xdc. Он понадобится нам далее. Файл содержит описание находящихся на плате светодиодов, переключателей и так далее. Без него поморгать светодиодами на Verilog будет непросто.

xdc. Он понадобится нам далее. Файл содержит описание находящихся на плате светодиодов, переключателей и так далее. Без него поморгать светодиодами на Verilog будет непросто.

Первый проект на SystemVerilog

В Vivado говорим File → New Project… В качестве типа проекта выбираем RTL Project, ставим галочку Do not specify sources at this time. В диалоге выбора типа платы находим в списке Arty.

Первым делом добавляем к проекту скачанный ранее XDC файл. Копируем его в каталог с проектом. Затем говорим File → Add Sources… → Add or create constraints → Add Files, находим копию файла, жмем Finish. В дереве файлов проекта (Sources) в группе Constraints появится файл Arty_Master.xdc, или как вы там назвали копию. Открываем его и раскомментируем все строчки в группах Clock signal, Switches и LEDs.

Далее говорим File → Add Sources… → Add or create design sources → Create File. В типе файла выбираем SystemVerilog, в имени файла вводим что-нибудь вроде hello. Говорим Finish. Далее появится диалог Define Module, который предложит накликать интерфейс модуля. Диалог довольно бесполезный, потому что то же самое удобнее сделать прямо в коде, так что жмем Cancel.

Далее появится диалог Define Module, который предложит накликать интерфейс модуля. Диалог довольно бесполезный, потому что то же самое удобнее сделать прямо в коде, так что жмем Cancel.

В дереве исходников находим новый файл hello.sv, он будет в группе Design Sources. Открываем и пишем следующий код:

`timescale 1ns / 1psmodule hello(

input logic CLK100MHZ,

input logic [3:0] sw,

output logic [3:0] led

);

always @(posedge CLK100MHZ)

begin

if(sw[0] == 0)

begin

led <= 4’b0001;

end

else

begin

led <= 4’b0000;

end

end

endmodule

Если все было сделано правильно, на этом этапе Vivado у вас будет выглядеть как-то так (кликабельно, PNG, 71 Кб):

Компиляция программы осуществляется в два этапа — синтез (synthesis) и имплементация (implementation). На этапе синтеза программа транслируется в абстрактную цепь из логических вентилей и прочих элементов. На этапе имплементации принимается решение о том, как прошить эту цепь в конкретную железку.

На этапе имплементации принимается решение о том, как прошить эту цепь в конкретную железку.

Запустим синтез, сказав Flow → Run Synthesis, или просто нажав F11. В правом верхнем углу вы увидите индикацию того, что процесс идет. Он может занимать довольно много времени, в зависимости от вашего компьютера и сложности программы. На моем ноутбуке синтез приведенной выше программы выполнился где-то секунд за 10. Если теперь сказать Flow → Open Synthesized Design, то можно увидеть красивую картинку вроде такой:

Настало время прошить нашу плату. Говорим Flow → Run Imlementation, затем Flow → Generate Bitstream. Подключаем плату к компьютеру по USB, в Vivado говорим Flow → Open Hardware Manager → Open target → Auto Connect → Program device. Потребуется указать путь к bit-файлу. У меня он был следующим:

./first-project.runs/impl_1/hello.bit

Говорим Program. Теперь на плате горит светодиод LD4, если переключатель SW0 опущен (см приведенную выше фотографию платы). Если же переключатель поднят, светодиод не горит. Простенько, конечно, но это же «hello, world», чего вы ожидали? 🙂

Если же переключатель поднят, светодиод не горит. Простенько, конечно, но это же «hello, world», чего вы ожидали? 🙂

Симуляция

Симуляция — это виртуальное выполнение кода на Verilog или VHDL прямо на вашем компьютере, безо всяких там ПЛИС’ов. Это одновременно и отладочный инструмент, и своего рода фреймворк для покрытия кода тестами.

При знакомстве с симуляцией первое, что я обнаружил, было то, что она у меня не работает. В логах было просто:

ERROR: [XSIM 43-3409] Failed to compile generated C file […]xsim_1.c.

Google по этой ошибке находил только всякую ерунду в стиле «попробуйте отключить антивирус». В итоге решить проблему помогло добавление флага -v 2 в скрипт ~/opt/xilinx/Vivado/2017.2/bin/xelab. С его помощью я выяснил, что Clang, бинарник которого Vivado таскает за собой, падает со следующей ошибкой:

/a/long/path/to/clang: error while loading shared libraries:

libncurses.so.5: cannot open shared object file: No such file or

directory

А эта ошибка и ее решение уже описаны на Arch Wiki. Лично я просто скопировал уже существующий файл из каталога Vivado_HLS:

Лично я просто скопировал уже существующий файл из каталога Vivado_HLS:

cp ~/opt/xilinx/Vivado_HLS/2017.2/lnx64/tools/gdb_v7_2/libncurses.so.5\

~/opt/xilinx/Vivado/2017.2/lib/lnx64.o/libncurses.so.5

… после чего все заработало. Итак, а теперь, собственно, пример симуляции.

По аналогии с тем, как ранее мы создавали hello.sv, создаем новый файл hello_sim.sv в группе Simulation Sources. В файле пишем следующий код:

`timescale 1ns / 1psmodule hello_sim();

logic clck_t;

logic [3:0] sw_t;

logic [3:0] led_t;

hello hello_t(clck_t, sw_t, led_t);

initial begin

clck_t <= 0;

sw_t <= 4’b0000; #1; clck_t <= 1; #1; clck_t <= 0; #1;

assert(led_t === 4’b0001);

sw_t <= 4’b0001; #1; clck_t <= 1; #1; clck_t <= 0; #1;

assert(led_t === 4’b0000);

end

endmodule

В дереве исходников делаем правый клик по файлу, выбираем Source Node Properties. В секции Used In снимаем галочки Synthesis и Implementation. Мы же не хотим, чтобы какие-то там тесты засоряли нашу далеко не резиновую FPGA?

В секции Used In снимаем галочки Synthesis и Implementation. Мы же не хотим, чтобы какие-то там тесты засоряли нашу далеко не резиновую FPGA?

Теперь говорим Flow → Run Simulation → Run Behavioral Simulation. В итоге вы увидите что-то примерно такого плана:

Можно видеть, что когда sw[0] равен нулю, led[0] равен единице, и наоборот. При этом все изменения происходят по фронту тактового сигнала. Похоже, что программа работает корректно. Ну и на ассертах ничего не свалилось, что как бы намекает.

Заключение

Архив с описанным выше проектом можно скачать здесь. В качестве дополнительных источников информации я бы рекомендовал следующие:

- Если вас интересуют подробности по железу, обратите внимание на даташит Artix-7 [PDF], reference manual к Arty Artix-7 [PDF], а также схему платы [PDF];

- Книга Цифровая схемотехника и архитектура компьютера (Digital Design and Computer Architecture) — прекрасная книга, в которой, помимо прочего, подробно объясняются языки SystemVerilog и VHDL, а также внутреннее устройство FPGA;

- OpenCores.

org — каталог всевозможных открытых проектов под FPGA. Для скачивания исходного кода требуется регистрация. Активация аккаунта производится модераторами вручную, поэтому может занимать несколько дней;

org — каталог всевозможных открытых проектов под FPGA. Для скачивания исходного кода требуется регистрация. Активация аккаунта производится модераторами вручную, поэтому может занимать несколько дней;

А пишите ли вы под FPGA? Если да, то на каком языке и какого производителя предпочитаете?

Дополнение: Также вас могут заинтересовать статьи Головоломка с логическими вентилями и решение на HDL и Знакомимся с iCEstick и полностью открытым ПО для разработки под FPGA.

Метки: FPGA, Электроника.

FPGA. Разбираемся, как устроены программируемые логические схемы и чем они хороши

Содержание статьи

Представь, что процессор вместо того, чтобы выполнять набор инструкций, будет перестраиваться под каждую программу и превращать алгоритм непосредственно в «железо». Именно так и работают FPGA! В этой статье я расскажу, как такое возможно, и познакомлю тебя с разными способами проектирования FPGA.

Может быть, ты умеешь взламывать устройства на другом конце света или кодить крутые веб-приложения, но понимаешь ли ты, как работает твой компьютер? И речь не о том, что делает операционка, как функционирует garbage collector в Java или как устроен компилятор C++. Я говорю о самом низком, аппаратном уровне, ниже ассемблера: как работает железо.

Что происходит в микросхеме сетевой карты, когда приходит пакет Ethernet? Как этот пакет передается дальше в оперативную память компьютера через шину PCI Express? Как работают самые быстрые системы распознавания изображений на аппаратном уровне?

Для ответа на эти вопросы надо немного разбираться в цифровой логике работы микросхем ASIC, но начинать с них очень сложно и дорого, и вместо этого лучше начать с FPGA.

INFO

FPGA расшифровывается как field-programmable gate array, по-русски — программируемые пользователем вентильные матрицы, ППВМ. В более общем случае они называются ПЛИС — программируемые логические интегральные схемы.

С помощью FPGA можно в буквальном смысле проектировать цифровые микросхемы, сидя у себя дома с доступной отладочной платой на столе и софтом разработчика за пару килобаксов. Впрочем, есть и бесплатные варианты. Заметь: именно проектировать, а не программировать, потому что на выходе получается физическая цифровая схема, выполняющая определенный алгоритм на аппаратном уровне, а не программа для процессора.

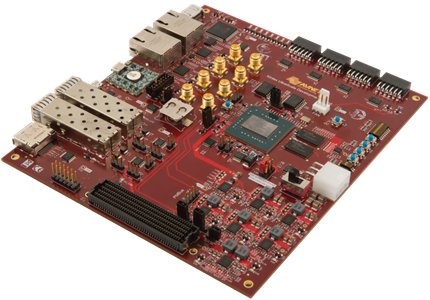

Работает это примерно так. Есть готовая печатная плата с набором интерфейсов, которые подключены к установленной на плате микросхеме FPGA, вроде крутой платы для дата-центра или отладочной платы для обучения.

Пока мы не сконфигурируем FPGA, внутри микросхемы просто нет логики для обработки данных с интерфейсов, и потому работать ничего, очевидно, не будет. Но в результате проектирования будет создана прошивка, которая после загрузки в FPGA создаст нужную нам цифровую схему. Например, так можно создать контроллер 100G Ethernet, который будет принимать и обрабатывать сетевые пакеты.

Важная особенность FPGA — возможность реконфигурации. Сегодня нам нужен контроллер 100G Ethernet, а завтра эта же плата может быть использована для реализации независимых четырех интерфейсов 25G Ethernet.

Существуют два крупных производителя FPGA-чипов: Xilinx и Intel, которые контролируют 58 и 42% рынка соответственно. Основатели Xilinx изобрели первый чип FPGA в далеком 1985 году. Intel пришла на рынок недавно — в 2015 году, поглотив компанию Altera, которая была основана в то же время, что и Xilinx. Технологии Xilinx и Altera во многом схожи, как и среды разработки. Чаще я работал с продуктами компании Xilinx, поэтому не удивляйся ее постоянному упоминанию.

FPGA широко применяются в разных устройствах: потребительской электронике, оборудовании телекома, платах-ускорителях для применения в дата-центрах, различной робототехнике, а также при прототипировании микросхем ASIC. Пару примеров я разберу чуть ниже.

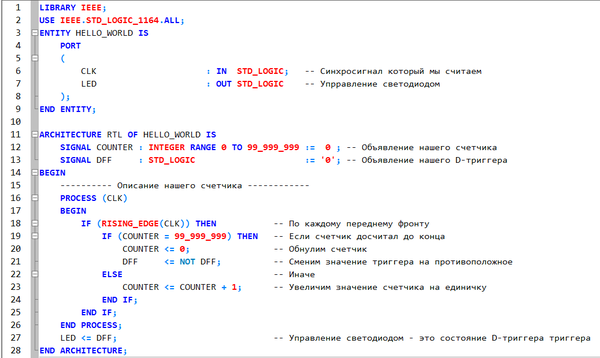

Также рассмотрим технологию, которая обеспечивает аппаратную реконфигурацию, познакомимся с процессом проектирования и разберем простой пример реализации аппаратного счетчика на языке Verilog. Если у тебя есть любая отладочная плата FPGA, ты сможешь повторить это самостоятельно. Если платы нет, то все равно сможешь познакомиться с Verilog, смоделировав работу схемы на своем компе.

Если у тебя есть любая отладочная плата FPGA, ты сможешь повторить это самостоятельно. Если платы нет, то все равно сможешь познакомиться с Verilog, смоделировав работу схемы на своем компе.

Принцип работы

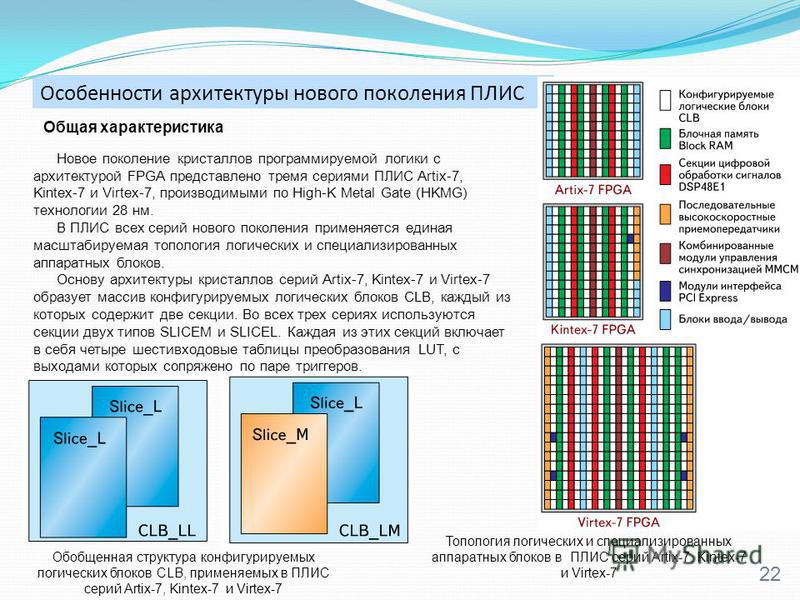

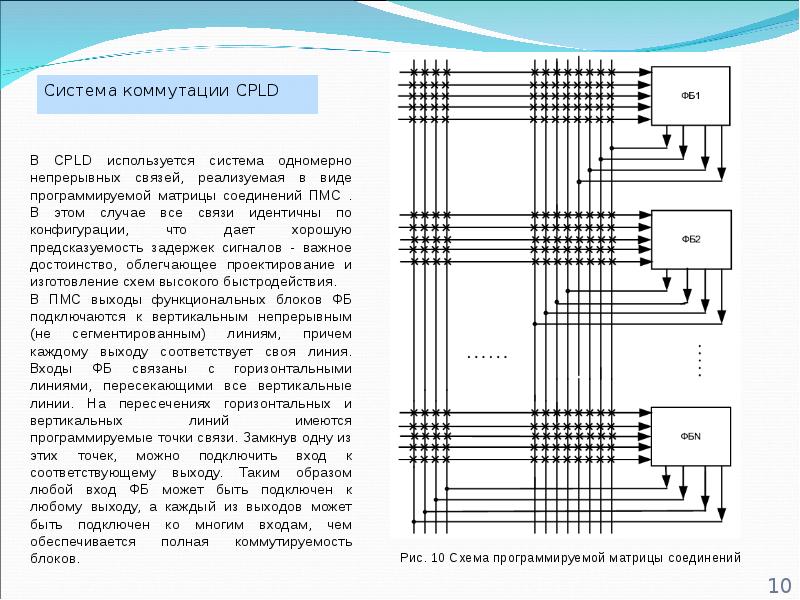

Микросхема FPGA — это та же заказная микросхема ASIC, состоящая из таких же транзисторов, из которых собираются триггеры, регистры, мультиплексоры и другие логические элементы для обычных схем. Изменить порядок соединения этих транзисторов, конечно, нельзя. Но архитектурно микросхема построена таким хитрым образом, что можно изменять коммутацию сигналов между более крупными блоками: их называют CLB — программируемые логические блоки.

Также можно изменять логическую функцию, которую выполняет CLB. Достигается это за счет того, что вся микросхема пронизана ячейками конфигурационной памяти Static RAM. Каждый бит этой памяти либо управляет каким-то ключом коммутации сигналов, либо является частью таблицы истинности логической функции, которую реализует CLB.

Так как конфигурационная память построена по технологии Static RAM, то, во-первых, при включении питания FPGA микросхему обязательно надо сконфигурировать, а во-вторых, микросхему можно реконфигурировать практически бесконечное количество раз.

Очень упрощенная 2D-структура микросхемы без конфигурационной памятиБлоки CLB находятся в коммутационной матрице, которая задает соединения входов и выходов блоков CLB.

Схема коммутационной матрицыНа каждом пересечении проводников находится шесть переключающих ключей, управляемых своими ячейками конфигурационной памяти. Открывая одни и закрывая другие, можно обеспечить разную коммутацию сигналов между CLB.

CLBCLB очень упрощенно состоит из блока, задающего булеву функцию от нескольких аргументов (она называется таблицей соответствия — Look Up Table, LUT) и триггера (flip-flop, FF). В современных FPGA LUT имеет шесть входов, но на рисунке для простоты показаны три. Выход LUT подается на выход CLB либо асинхронно (напрямую), либо синхронно (через триггер FF, работающий на системной тактовой частоте). 3 = 8 значений. Каждое из них соответствует своей комбинации входных сигналов. Эти значения вычисляются программой для разработки прошивки ПЛИС и записываются в специальные ячейки конфигурационной памяти.

3 = 8 значений. Каждое из них соответствует своей комбинации входных сигналов. Эти значения вычисляются программой для разработки прошивки ПЛИС и записываются в специальные ячейки конфигурационной памяти.

Значение каждой из ячеек подается на свой вход выходного мультиплексора LUT, а входные аргументы булевой функции используются для выбора того или иного значения функции. CLB — важнейший аппаратный ресурс FPGA. Количество CLB в современных кристаллах FPGA может быть разным и зависит от типа и емкости кристалла. У Xilinx есть кристаллы с количеством CLB в пределах примерно от четырех тысяч до трех миллионов.

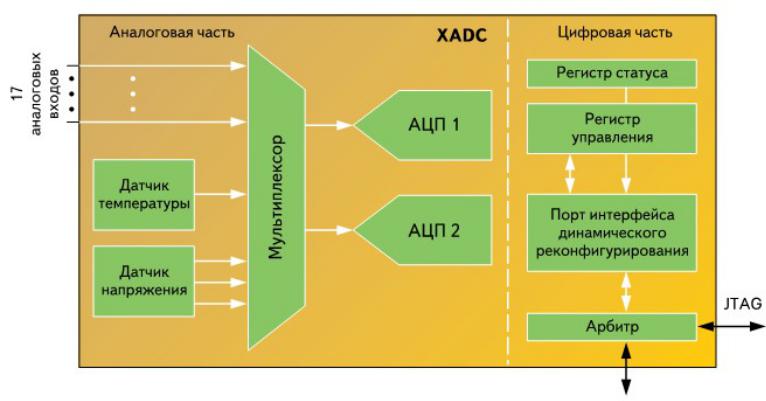

Помимо CLB, внутри FPGA есть еще ряд важных аппаратных ресурсов. Например, аппаратные блоки умножения с накоплением или блоки DSP. Каждый из них может делать операции умножения и сложения 18-битных чисел каждый такт. В топовых кристаллах количество блоков DSP может превышать 6000.

Другой ресурс — это блоки внутренней памяти (Block RAM, BRAM). Каждый блок может хранить 2 Кбайт. Полная емкость такой памяти в зависимости от кристалла может достигать от 20 Кбайт до 20 Мбайт. Как и CLB, BRAM и DSP-блоки связаны коммутационной матрицей и пронизывают весь кристалл. Связывая блоки CLB, DSP и BRAM, можно получать весьма эффективные схемы обработки данных.

Полная емкость такой памяти в зависимости от кристалла может достигать от 20 Кбайт до 20 Мбайт. Как и CLB, BRAM и DSP-блоки связаны коммутационной матрицей и пронизывают весь кристалл. Связывая блоки CLB, DSP и BRAM, можно получать весьма эффективные схемы обработки данных.

Применение и преимущества FPGA

Первый чип FPGA, созданный Xilinx в 1985 году, содержал всего 64 CLB. В то время интеграция транзисторов на микросхемах была намного ниже, чем сейчас, и в цифровых устройствах часто использовались микросхемы «рассыпной логики». Были отдельно микросхемы регистров, счетчиков, мультиплексоров, умножителей. Под конкретное устройство создавалась своя печатная плата, на которой устанавливались эти микросхемы низкой интеграции.

Использование FPGA позволило отказаться от такого подхода. Даже FPGA на 64 CLB значительно экономит место на печатной плате, а доступность реконфигурации добавила возможность обновлять функциональность устройств уже после изготовления во время эксплуатации, как говорят «in the field» (отсюда и название — field-programmable gate array).

За счет того, что внутри FPGA можно создать любую аппаратную цифровую схему (главное, чтобы хватило ресурсов), одно из важных применений ПЛИС — это прототипирование микросхем ASIC.

Разработка ASIC очень сложна и затратна, цена ошибки очень высока, и вопрос тестирования логики критичен. Поэтому одним из этапов разработки еще до начала работы над физической топологией схемы стало ее прототипирование на одном или нескольких кристаллах FPGA.

Для разработки ASIC выпускают специальные платы, содержащие много FPGA, соединенных между собой. Прототип микросхемы работает на значительно меньших частотах (может быть, десятки мегагерц), но позволяет сэкономить на выявлении проблем и багов.

Однако, на мой взгляд, существуют более интересные применения ПЛИС. Гибкая структура FPGA позволяет реализовывать аппаратные схемы для высокоскоростной и параллельной обработки данных с возможностью изменить алгоритм.

Сравнение аппаратных платформДавай подумаем, чем принципиально отличаются CPU, GPU, FPGA и ASIC. CPU универсален, на нем можно запустить любой алгоритм, он наиболее гибок, и использовать его легче всего благодаря огромному количеству языков программирования и сред разработки.

При этом из-за универсальности и последовательного выполнения инструкций CPU снижается производительность и повышается энергопотребление схемы. Происходит это потому, что на каждую полезную арифметическую операцию CPU совершает много дополнительных операций, связанных с чтением инструкций, перемещением данных между регистрами и кешем, и другие телодвижения.

На другой стороне находится ASIC. На этой платформе требуемый алгоритм реализуется аппаратно за счет прямого соединения транзисторов, все операции связаны только с выполнением алгоритма и нет никакой возможности изменить его. Отсюда максимальная производительность и наименьшее энергопотребление платформы. А вот перепрограммировать ASIC невозможно.

Справа от CPU находится GPU. Изначально эти микросхемы были разработаны для обработки графики, но сейчас используются и для майнинга вычислений общего назначения. Они состоят из тысяч небольших вычислительных ядер и выполняют параллельные операции над массивом данных.

Они состоят из тысяч небольших вычислительных ядер и выполняют параллельные операции над массивом данных.

Если алгоритм можно распараллелить, то на GPU получится добиться значительного ускорения по сравнению с CPU. С другой стороны, последовательные алгоритмы будут реализовываться хуже, поэтому платформа оказывается менее гибкой, чем CPU. Также для разработки под GPU надо иметь специальные навыки, знать OpenCL или CUDA.

Наконец, FPGA. Эта платформа сочетает эффективность ASIC с возможностью менять программу. ПЛИС не универсальны, но существует класс алгоритмов и задач, которые на них будут показывать лучшую производительность, чем на CPU и даже GPU. Сложность разработки под FPGA выше, однако новые средства разработки делают этот разрыв меньше.

Решающее же преимущество FPGA — это способность обрабатывать данные в темпе их поступления с минимальной задержкой реакции. В качестве примера можешь вообразить умный сетевой маршрутизатор с большим количеством портов: при поступлении пакета Ethernet на один из его портов необходимо проверить множество правил, прежде чем выбрать выходной порт. Возможно, потребуется изменение некоторых полей пакета или добавление новых.

Возможно, потребуется изменение некоторых полей пакета или добавление новых.

Использование FPGA позволяет решать эту задачу мгновенно: байты пакета еще только начали поступать в микросхему из сетевого интерфейса, а его заголовок уже анализируется. Использование процессоров тут может существенно замедлить скорость обработки сетевого трафика. Ясно, что для маршрутизаторов можно сделать заказную микросхему ASIC, которая будет работать наиболее эффективно, но что, если правила обработки пакетов должны меняться? Достичь требуемой гибкости в сочетании с высокой производительностью поможет только FPGA.

Таким образом, FPGA используются там, где нужна высокая производительность обработки данных, наименьшее время реакции, а также низкое энергопотребление.

FPGA in the cloud

В облачных вычислениях FPGA применяются для быстрого счета, ускорения сетевого трафика и осуществления доступа к массивам данных. Сюда же можно отнести использование FPGA для высокочастотной торговли на биржах. В серверы вставляются платы FPGA с PCI Express и оптическим сетевым интерфейсом производства Intel (Altera) или Xilinx.

В серверы вставляются платы FPGA с PCI Express и оптическим сетевым интерфейсом производства Intel (Altera) или Xilinx.

На FPGA отлично ложатся криптографические алгоритмы, сравнение последовательностей ДНК и научные задачи вроде молекулярной динамики. В Microsoft давно используют FPGA для ускорения поискового сервиса Bing, а также для организации Software Defined Networking внутри облака Azure.

Бум машинного обучения тоже не обошел стороной FPGA. Компании Xilinx и Intel предлагают средства на основе FPGA для работы с глубокими нейросетями. Они позволяют получать прошивки FPGA, которые реализуют ту или иную сеть напрямую из фреймворков вроде Caffe и TensorFlow.

Причем это все можно попробовать, не выходя из дома и используя облачные сервисы. Например, в Amazon можно арендовать виртуальную машину с доступом к плате FPGA и любым средствам разработки, в том числе и machine learning.

FPGA on the edge

Что еще интересное делают на FPGA? Да чего только не делают! Робототехника, беспилотные автомобили, дроны, научные приборы, медицинская техника, пользовательские мобильные устройства, умные камеры видеонаблюдения и так далее.

Традиционно FPGA применялись для цифровой обработки одномерных сигналов (и конкурировали с процессорами DSP) в устройствах радиолокации, приемопередатчиках радиосигналов. С ростом интеграции микросхем и увеличением производительности платформы FPGA стали все больше применяться для высокопроизводительных вычислений, например для обработки двумерных сигналов «на краю облака» (edge computing).

Эту концепцию легче всего понять на примере видеокамеры для анализа автомобильного трафика с функцией распознавания номеров машин. Можно взять камеру с возможностью передачи видео через Ethernet и обрабатывать поток на удаленном сервере. С ростом числа камер будет расти и нагрузка на сеть, что может привести к сбоям системы.

Вместо этого лучше реализовать распознавание номеров на вычислителе, установленном прямо в корпус видеокамеры, и передавать в облако номера машин в формате текста. Для этого даже можно взять сравнительно недорогие FPGA с низким энергопотреблением, чтобы обойтись аккумулятором. При этом остается возможность изменять логику работы FPGA, например, при изменении стандарта автомобильных номеров.

При этом остается возможность изменять логику работы FPGA, например, при изменении стандарта автомобильных номеров.

Что до робототехники и дронов, то в этой сфере как раз особенно важно выполнять два условия — высокая производительность и низкое энергопотребление. Платформа FPGA подходит как нельзя лучше и может использоваться, в частности, для создания полетных контроллеров для беспилотников. Уже сейчас делают БПЛА, которые могут принимать решения на лету.

Как разрабатывать проект на FPGA?

Существуют разные уровни проектирования: низкий, блочный и высокий. Низкий уровень предполагает использование языков типа Verilog или VHDL, на которых ты управляешь разработкой на уровне регистровых передач (RTL — register transfer level). В этом случае ты формируешь регистры, как в процессоре, и определяешь логические функции, изменяющие данные между ними.

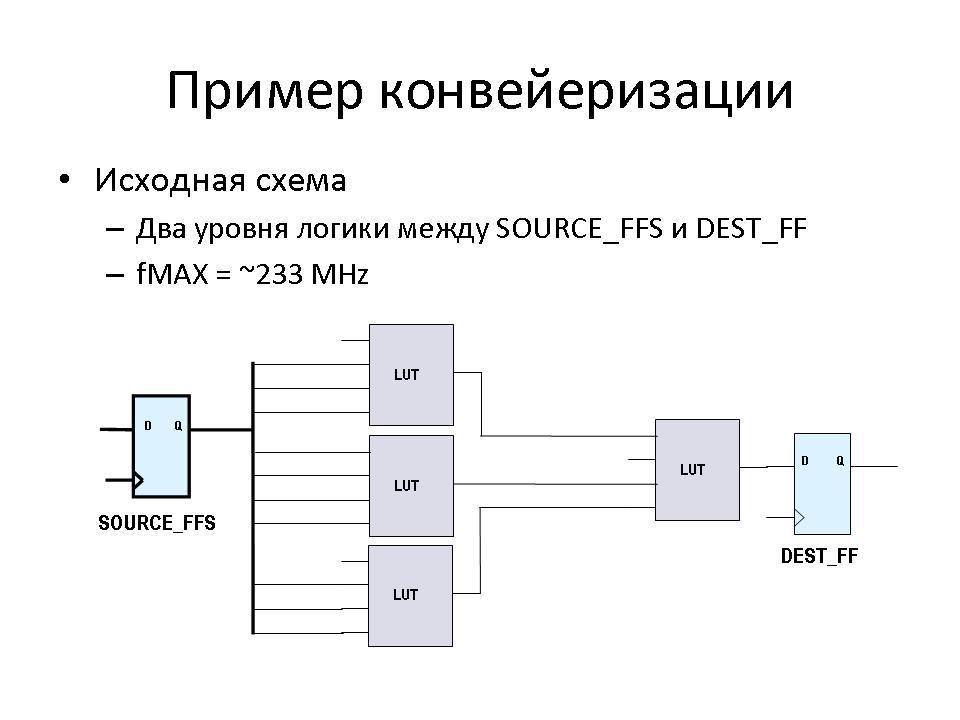

Схемы FPGA всегда работают на определенных тактовых частотах (обычно 100–300 МГц), и на уровне RTL ты определяешь поведение схемы с точностью до такта системной частоты. Эта кропотливая работа приводит к созданию максимально эффективных схем с точки зрения производительности, потребления ресурсов кристалла FPGA и энергопотребления. Но тут требуются серьезные скиллы в схемотехнике, да и с ними процесс небыстрый.

Эта кропотливая работа приводит к созданию максимально эффективных схем с точки зрения производительности, потребления ресурсов кристалла FPGA и энергопотребления. Но тут требуются серьезные скиллы в схемотехнике, да и с ними процесс небыстрый.

На блочном уровне ты занимаешься в основном соединением уже готовых крупных блоков, которые выполняют определенные функции, для получения нужной тебе функциональности системы на кристалле (system-on-chip).

На высоком уровне проектирования ты уже не будешь контролировать данные на каждом такте, вместо этого сконцентрируешься на алгоритме. Существуют компиляторы или трансляторы с языков C и C++ на уровень RTL, например Vivado HLS. Он довольно умный и позволяет транслировать на аппаратный уровень широкий класс алгоритмов.

Главное преимущество такого подхода перед языками RTL — ускорение разработки и особенно тестирования алгоритма: код на C++ можно запустить и верифицировать на компьютере, и это будет намного быстрее, чем тестировать изменения алгоритма на уровне RTL. За удобство, конечно, придется заплатить — схема может получиться не такой быстрой и займет больше аппаратных ресурсов.

За удобство, конечно, придется заплатить — схема может получиться не такой быстрой и займет больше аппаратных ресурсов.

Часто мы готовы платить эту цену: если грамотно использовать транслятор, то эффективность не сильно пострадает, а ресурсов в современных FPGA достаточно. В нашем мире с критичным показателем time to market это оказывается оправданным.

Часто в одном дизайне нужно совместить все три стиля разработки. Допустим, нам нужно сделать устройство, которое мы могли бы встроить в робота и наделить его способностью распознавать объекты в видеопотоке — например, дорожные знаки. Возьмем микросхему видеосенсора и подключим ее напрямую к FPGA. Для отладки можем использовать монитор HDMI, тоже подключенный к FPGA.

Кадры с камеры будут передаваться в FPGA по интерфейсу, который заведомо определен производителем сенсора (USB тут не катит), обрабатываться и выводиться на монитор. Для обработки кадров понадобится фреймбуфер, который обычно находится во внешней памяти DDR, установленной на печатной плате рядом с микросхемой FPGA.

Если производитель видеосенсора не предоставляет Interface IP для нашей микросхемы FPGA, то нам придется писать его самостоятельно на языке RTL, считая такты, биты и байты в соответствии со спецификацией протокола передачи данных. Блоки Preprocess, DDR Controller и HDMI IP мы, скорее всего, возьмем готовые и просто соединим их интерфейсы. А блок HLS, который выполняет поиск и обработку поступающих данных, мы можем написать на C++ и транслировать при помощи Vivado HLS.

Скорее всего, нам еще потребуется какая-то готовая библиотека детектора и классификатора дорожных знаков, адаптированная для использования в FPGA. В этом примере я, конечно, привожу сильно упрощенную блок-схему дизайна, но логику работы она отражает корректно.

Рассмотрим путь проектирования от написания кода RTL до получения конфигурационного файла для загрузки в FPGA.

Путь проектированияИтак, ты пишешь код RTL, который реализует нужную тебе схему. Прежде чем его проверять на реальном железе, надо убедиться, что он верный и корректно решает требуемую задачу. Для этого используется RTL-моделирование в симуляторе на компьютере.

Для этого используется RTL-моделирование в симуляторе на компьютере.

Ты берешь свою схему, представленную пока только в коде RTL, и помещаешь ее на виртуальный стенд, где подаешь последовательности цифровых сигналов на входы схемы, регистрируешь выходные диаграммы, зависимости от времени выходных сигналов и сравниваешь с ожидаемыми результатами. Обычно ты находишь ошибки и возвращаешься к написанию RTL.

Далее логически верифицированный код подается на вход программе-синтезатору. Она преобразует текстовое описание схемы в связанный список цифровых элементов из библиотеки, доступной для данного кристалла FPGA. В этом списке будут отображены такие элементы, как LUT, триггеры, и связи между ними. На этой стадии элементы пока никак не привязаны к конкретным аппаратным ресурсам. Чтобы это сделать, требуется наложить на схему ограничения (Constraints) — в частности, указать, с какими физическими контактами ввода-вывода микросхемы FPGA связаны логические входы и выходы твоей схемы.

В этих ограничениях также требуется указать, на каких тактовых частотах должна работать схема. Выход синтезатора и файл ограничений отдаются процессору Implementation, который, помимо прочего, занимается размещением и трассировкой (Place and Route).

Процесс Place каждый пока еще обезличенный элемент из netlist привязывает к конкретному элементу внутри микросхемы FPGA. Далее начинает работу процесс Route, который пытается найти оптимальное соединение этих элементов для соответствующей конфигурации коммутационной матрицы ПЛИС.

Place и Route действуют, исходя из ограничений, наложенных нами на схему: контактами ввода-вывода и тактовой частотой. Период тактовой частоты очень сильно влияет на Implementation: он не должен быть меньше, чем временная задержка на логических элементах в критической цепи между двумя последовательными триггерами.

Часто сразу удовлетворить это требование не удается, и тогда надо вернуться на начальный этап и изменить код RTL: например, попытаться сократить логику в критической цепи. После успешного завершения Implementation нам известно, какие элементы где находятся и как они связаны.

После успешного завершения Implementation нам известно, какие элементы где находятся и как они связаны.

Только после этого запускается процесс создания бинарного файла прошивки FPGA. Остается его загрузить в реальное железо и проверить, работает ли оно так, как ожидалось. Если на этом этапе возникают проблемы, значит, моделирование было неполным и на этом этапе не были устранены все ошибки и недочеты.

Можно вернуться на стадию симуляции и смоделировать нештатную ситуацию, а если и это не сработает, на крайний случай предусмотрен механизм отладки непосредственно в работающем железе. Ты можешь указать, какие сигналы хочешь отслеживать во времени, и среда разработки сгенерирует дополнительную схему логического анализатора, которая размещается на кристалле рядом с твоей разрабатываемой схемой, подключается к интересующим тебя сигналам и сохраняет их значения во времени. Сохраненные временные диаграммы нужных сигналов можно выгрузить на компьютер и проанализировать.

Существуют и высокоуровневые средства разработки (HLS, High-level synthesis), и даже готовые фреймворки для создания нейросетей в ПЛИС. Эти средства на выходе генерят код RTL на языках VHDL или Verilog, который дальше спускается по цепочке Synthesis → Implementation → Bitstream generation. Ими вполне можно пользоваться, но, чтобы использовать их эффективно, надо иметь хотя бы минимальное представление о языках уровня RTL.

Эти средства на выходе генерят код RTL на языках VHDL или Verilog, который дальше спускается по цепочке Synthesis → Implementation → Bitstream generation. Ими вполне можно пользоваться, но, чтобы использовать их эффективно, надо иметь хотя бы минимальное представление о языках уровня RTL.

Продолжение следует

Надеюсь, теория тебя не слишком загрузила! В следующей статье я расскажу о практике: мы посмотрим, что конкретно нужно делать, чтобы запрограммировать FPGA.

Как начать работать с HDL и ПЛИС (FPGA)

ПредисловиеПланирую написать ряд статей, про внутреннее устройство ПЛИС и их программирование. В данном сообщении я планирую дать направление читателю, что нужно прочитать для того, чтобы начать разрабатывать для ПЛИС.

Современные тенденции

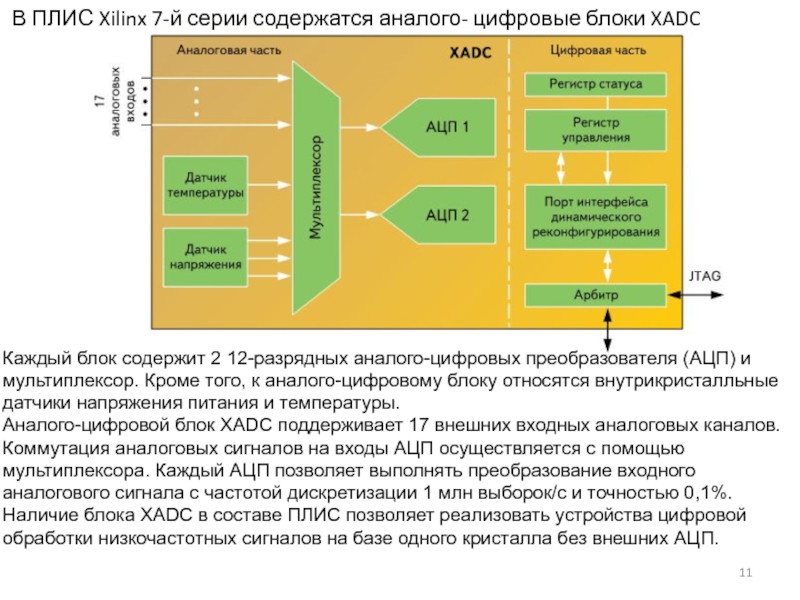

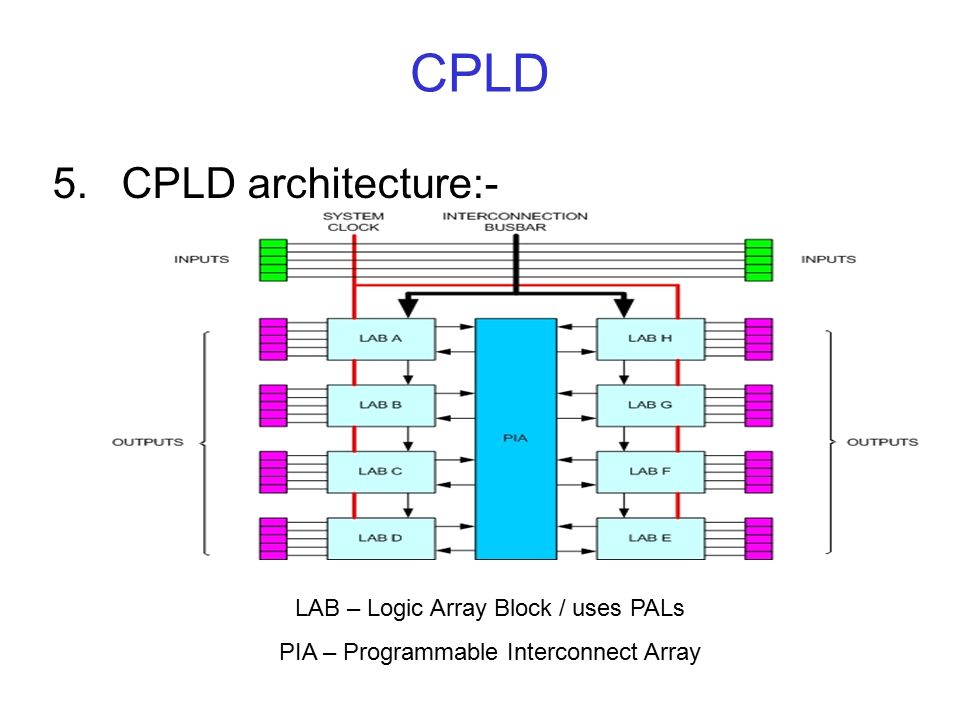

К сожалению, а может быть и к счастью (в зависимости как на это посмотреть) разработка современной электроники, особенно цифровой, но не только сводится к описанию цифровых функций и автоматов сводится к описанию их на основе одного из HDL (Hardware Description Language) -языков описания аппаратуры. На данный момент, существуют следующие языки описания аппаратуры: AHDL, VHDL, Verilog и System Verilog. Сами ПЛИС (CPLD, FPGA) представляют собой квадратные матрицы ячеек (состоящих из сотен – тысяч, в зависимости от ресурсов ПЛИС, логических элементов), к этим ячейкам подходят магистрали источников синхросигналов (клоков) и линий питания (+5 или +3,3 В) и земли. К слову говоря, современные ПЛИС (7 серия от Xilinx, 5 поколение Cyclone и т.п.) – это SoC в которых кроме, самой ПЛИС присутствует процессорное ядро и аппаратная поддержка различных интерфейсов таких, как : USB, Ethernet, CAN, SPI, I2C, RS232 и др.

На данный момент, существуют следующие языки описания аппаратуры: AHDL, VHDL, Verilog и System Verilog. Сами ПЛИС (CPLD, FPGA) представляют собой квадратные матрицы ячеек (состоящих из сотен – тысяч, в зависимости от ресурсов ПЛИС, логических элементов), к этим ячейкам подходят магистрали источников синхросигналов (клоков) и линий питания (+5 или +3,3 В) и земли. К слову говоря, современные ПЛИС (7 серия от Xilinx, 5 поколение Cyclone и т.п.) – это SoC в которых кроме, самой ПЛИС присутствует процессорное ядро и аппаратная поддержка различных интерфейсов таких, как : USB, Ethernet, CAN, SPI, I2C, RS232 и др.

Три кита разработки цифровых устройств с использованием ПЛИС (FPGA)

1. Основа всего это алгебра логики (булева алгебра) и способы построения простых цифровых схем и автоматов с использованием алгебры логики.

2. Схемотехника входных и выходных каскадов логических элементов (для понимания, что такое высокоимпедансное Z-состояние, нагрузочные характеристики элементов, схемы с открытым коллектором).

3. И, конечно, 3 этап это способы построения простых цифровых схем с использованием языков описания аппаратуры.

Алгебра логики

Основными в алгебре логики являются следующие вещи:

1) Принцип двойственности

2) Теорема Де-Моргана

Эти два принципа можно посмотреть, например, здесь: https://studme.org/2002061028280/tovarovedenie/algebra_logiki . Позже сам напишу про алгебру логики.

Так же следует упомянуть про способы представления (алгебраическое, табличное и в виде карт/диаграм Карно и Вена) и минимизации логических функций через карты Карно или другие методы, например, метод Мак-Класки (https://ru.wikipedia.org/wiki/%D0%9C%D0%B5%D1%82%D0%BE%D0%B4_%D0%9A%D1%83%D0%B0%D0%B9%D0%BD%D0%B0_%E2%80%94_%D0%9C%D0%B0%D0%BA-%D0%9A%D0%BB%D0%B0%D1%81%D0%BA%D0%B8).

Одна неплохая презентация про алгебру логики: https://drive.google.com/file/d/0B9GLCHSwsJn8cURyT3BOUEVxdVE/view?usp=sharing

После понимания математических основ цифровой электроники нужно двигаться к способам реализации простых цифровых схем клмбинационной логики (логики не зависящей от состояния схемы):

– мультиплексоры

– дешифраторы

– преобразователи кода

– и другие схемы.

Вот, например, https://drive.google.com/open?id=0B9GLCHSwsJn8NmxtTVNUOVZZbWs

Следующий шаг – изучение последовательностных схем (схемы зависящие от состояния и сигналов на входе схемы). Такими схемами являются:

-триггеры

-счетчики

-регистры

-генераторы

и др.

Например, https://distant.msu.ru/pluginfile.php/38192/mod_resource/content/1/%D0%9B%D0%B5%D0%BA%D1%86%D0%B8%D1%8F%204.pdf

или

https://drive.google.com/open?id=0B9GLCHSwsJn8YkJZeGtVZzZ4LTQ

а также ознакомиться с описанием цифровых автоматов (которых, 2 основных вида: Мили и Мура (https://neerc.ifmo.ru/wiki/index.php?title=%D0%90%D0%B2%D1%82%D0%BE%D0%BC%D0%B0%D1%82%D1%8B_%D0%9C%D1%83%D1%80%D0%B0_%D0%B8_%D0%9C%D0%B8%D0%BB%D0%B8)

Схемотехника логических элементов

Данный раздел в большей степени относится к разаботке цифровых устройств с использованием дискретных микросхем, однако, в ряде моментов при проектировании с использованием ПЛИС эти знания также оказываются необходимыми

Прежде всего схемотехника зависит от типа логики: ТТЛ (ТТЛШ), КМОП и ЭСЛ: http://www. inp.nsk.su/students/radio/lectures/Pulse/07.pdf

inp.nsk.su/students/radio/lectures/Pulse/07.pdf

Параметры логических элементов:

http://myrepititor.ru/electronics/82-Osnovnye_xarakteristiki_i_parametry_logicheskix_eleme.html

http://audioakustika.ru/node/1555

Языки HDL, способы проектирования

У меня довольно большаыя подборка книг по ПЛИС: https://drive.google.com/open?id=0B9GLCHSwsJn8Z0Y3U24ybmxjVjA

Если использовать Verilog, то стоить начать с Verilog и VerilogTutorial, если VHDL – то “Языки Verilog и VHDL”, кроме того среди этого архива есть документ с “Золотыми ссылками по HDL”.

Что будет в продолжении?

В будущем планирую пройтись по каждому из этих пунктов и написать цикл статей с примерами дизайна цифровых схем (на github).

IcaliaLabs / plis: Автоматические задачи разработки заданы красиво

GitHub – IcaliaLabs / plis: Автоматические задачи разработки заданы красивоКрасиво поставленные задачи автоматизированной разработки

Файлы

Постоянная ссылка Не удалось загрузить последнюю информацию о фиксации.

Тип

Имя

Последнее сообщение фиксации

Время фиксации

Помогает процессу разработки с помощью Docker Compose, задавая вежливые запросы 🙂

Установить

В macOS установите через Homebrew:

кран для заваривания icalialabs / формулы

заварить установить плис

В других системах вы можете:

- Загрузите исполняемый файл для своей системы с Релизы Страница

- Поместите его на любой из путей, доступных в $ PATH

Особое поведение:

-

plis start [services-optional]: запускает проект docker-compose со следующими дополнительными функциями:- Если некоторые или все контейнеры запрошенного проекта отсутствуют, выдает команду

docker-compose up -d.

- Если присутствуют все запрошенные контейнеры проекта, выдает команду

docker-compose start.

- Если некоторые или все контейнеры запрошенного проекта отсутствуют, выдает команду

-

plis attach [имя_службы]: определяет контейнер данной службы и присоединяет к нему консоль. -

plis run [service_name] [command]: запускает указанную команду:- Если для данной службы запущен контейнер, он выполняет его, выдав команду

docker exec -ti. - Если для данной службы нет запущенных контейнеров, она выполняет команду

docker-compose run --rm.

- Если для данной службы запущен контейнер, он выполняет его, выдав команду

# Запустить проект docker-compose: плис начать # Перезапустить службу: Пожалуйста, перезапустите Интернет # Присоединяем консоль к сервису: плис прикрепить веб # Выполнить команду для существующего или нового контейнера: плис запустить веб-рельсы c # Остановить службу: пожалуйста, останови Интернет

ЗАДАЧИ:

Около

Красиво поставленные задачи автоматизированной разработки

Темы

ресурсов

Лицензия

Вы не можете выполнить это действие в настоящее время. Вы вошли в систему с другой вкладкой или окном. Перезагрузите, чтобы обновить сеанс.

Вы вышли из системы на другой вкладке или в другом окне. Перезагрузите, чтобы обновить сеанс.

Вы вошли в систему с другой вкладкой или окном. Перезагрузите, чтобы обновить сеанс.

Вы вышли из системы на другой вкладке или в другом окне. Перезагрузите, чтобы обновить сеанс.«Большие размеры» – бессмысленный термин, и бренды должны начать с ним покончить – Quartz

На протяжении десятилетий розничные торговцы относились к женщинам, которые носят большие размеры, как к совершенно другому типу покупателей. Для них существовал даже специальный свод правил: избегать ярких цветов. Никогда не делайте горизонтальных полос.

В наши дни такие стереотипы просто смехотворны, считает Мэри Алдерете, директор по маркетингу интернет-магазина женской модной одежды ModCloth. «Хотите знать, какое платье номер один по продажам на этой неделе? Радужное платье, и оно уже распродано во всех расширенных размерах! ” – говорит она, имея в виду размеры от больших до 4X. Платье ярко окрашено и покрыто шевронными полосами.

В последние несколько лет все больше женщин призывают положить конец разграничению «больших размеров», которое варьируется в зависимости от продавца, но часто относится к размерам от 16 и выше.Многие считают, что эта категория маргинализирует их, предполагая, что они представляют собой небольшую группу вне мейнстрима, чьи потребности в моде второстепенны. На самом деле, среднестатистическая американка, скорее всего, будет иметь размер 16, а не 2.

Если розничные торговцы будут умны, они решат отказаться от «плюсов» и, наконец, предложат вместо этого больший диапазон размеров в своих основных линиях. . Этикетка и стереотипы, которые сопровождают «большие размеры», устарели и часто оскорбительны. Все, что поддерживает это различие, – это история – и уродливое наследие модной индустрии – исключительное поведение.

Вышло из моды

Несмотря на недавние усилия, по словам Маршала Коэна, главного аналитика розничной торговли исследовательской компании NPD Group, сохраняется множество давних заблуждений относительно того, как покупают большие покупатели. В дополнение к представлению о том, что эта категория покупателей не будет покупать яркие цвета или полосы, традиционно считалось, что они не носят больших принтов или обтягивающую одежду и не любят делать покупки или примерять вещи. Коэн считает, что все эти представления ужасно устарели.

«Это имело смысл в прошлом, когда, когда эти правила могли быть применимы, [иметь] отдельную линию, отдельный отдел или отдельный магазин для потребителей больших размеров», – говорит он. «Сегодня это уже не так».

Независимо от того, действительно ли женщины хотели делать такие покупки или просто делали это по указанию СМИ и дизайнеров, правила изменились – во многом благодаря Интернету. Сара Конли, стильный блогер и эксперт по моде больших размеров, говорит, что Instagram оказал «огромное влияние».

В прошлом году, например, после того, как журнал O Magazine объявил, что женщины должны носить топы только при плоском животе, Конли помог организовать ответ в Интернете, побудив женщин всех размеров делиться своими фотографиями, используя хэштег #RockTheCrop.

«Это вызвало много негативной реакции в Интернете, потому что это неправда, и эти правила стиля очень устарели», – говорит она. Вне таких кампаний бодипозитивные женщины обычно используют хэштеги, такие как #effyourbeautystandards или иногда #DropThePlus.

Сегодня покупатели предпочитают цвета, модную одежду и одежду, подчеркивающую их фигуру. Коэн добавляет, что они хотят «делать покупки в одном месте и покупать тот же товар», что и женщины прямого роста, если использовать выражение индустрии. Хотя данные показывают, что они делают меньше покупок, это незначительно. И даже этот разрыв сокращается.

Сегодня покупатели предпочитают цвета, модную одежду и одежду, подчеркивающую их фигуру.

Коэн говорит, что после рецессии все больше брендов запустили линейки Plus, поскольку они ищут новый источник продаж.Джей Си Пенни, например, дебютировал в мае. Также появились новые бренды, ориентированные на модную одежду больших размеров, такие как Eloquii и Torrid.

Похоже, что попытки выйти на недостаточно обслуживаемый рынок окупаются. NPD недавно обнаружил, что количество подростков, купивших одежду больших размеров, за последние пять лет увеличилось вдвое, во многом потому, что теперь у них есть больше возможностей. А за 12 месяцев до февраля 2016 года продажи одежды больших размеров в США выросли на 3% до 20,4 млрд долларов, сообщает группа.

Есть еще много возможностей для роста. Эта цифра составляет около 17% от общего объема продаж женской одежды в размере 120,3 миллиарда долларов за тот же период. Хотя нет конкретной оценки количества потребителей больших размеров в США, Коэн отмечает, что около 36% американских женщин страдают ожирением. Ожирение и размер несовместимы. Но Коэн считает, что продажи одежды больших размеров примерно вдвое меньше, чем они могли бы быть, если бы индустрия моды сделала больше возможностей.

В то время как индустрия больших размеров находится на подъеме, исследования показывают, что многие женщины не любят делать покупки в отдельной категории.В опросе покупателей из Великобритании, проведенном в 2015 году, около 61% потребителей больших размеров заявили, что они предпочли бы делать покупки в основном ассортименте розничных магазинов, а не в ответвлениях больших размеров. ModCloth обнаружила аналогичные результаты, когда в прошлом году опросила 1500 женщин, носящих размер 16 и выше. Примерно две трети заявили, что хотели бы видеть большие размеры в том же разделе, что и другие размеры, а 60% сообщили, что стесняются покупать одежду в отдельном магазине или отделе.

Где «плюс размер» происходит от

Во многом благодаря Лейну Брайанту, терминология больших размеров прочно укоренилась в индустрии моды на протяжении десятилетий.В настоящее время компания является синонимом розничной торговли плюс-сайз, хотя начинала она с продажи одежды для беременных.

Лена Химмельштейн Брайант была портнихой, которая открыла магазин в Нью-Йорке в 1904 году. В то время все больше женщин из среднего класса работали во время беременности. Покупательница попросила Брайанта кое-что, что она могла бы износить, ожидая. Брайант согласился, создав платье с эластичным поясом и юбкой со складками гармошкой.

Слухи распространились, и Lane Bryant вскоре стала первой компанией, которая начала массово производить одежду этого стиля, как объясняет Американский музей истории текстиля.В период с 1909 по 1923 год продажи выросли с 50 000 долларов в год до 5 миллионов долларов.