Справочник “Цифровые Интегральные Микросхемы”

Справочник “Цифровые Интегральные Микросхемы” [ Содержание ] Увлекаетесь электроникой?

Приглашаем Вас принять участие

в бета-тестировании онлайн-редактора

электрических схем.

sapr.asvcorp.ru

Работайте со схемами прямо из браузера.

2.5.3. JK-триггеры

JK-триггеры подразделяются на универсальные и комбинированные. Универсальный JK-триггер имеет два информационных входа J и K. По входу J триггер устанавливается в состояние Q=1, /Q=0, а по входу K-в состояние Q=0, /Q=1.

JK-триггер отличается от RS-триггера прежде всего тем что в нем устранена неопределенность, которая возникает в RS-триггере при определенной комбинации входных сигналов.

Универсальность JK-триггера состоит в том, что он может выполнять функции RS-, Т- и D-триггеров.

Комбинированный JK-триггер отличается от универсального наличием

дополнительных асинхронных входов S и R для предварительной

установки триггера в определенное состояние (логической 1 или 0).

Простейший JK-триггер можно получить из синхронного RS-триггера с динамическим управлением, если ввести дополнительные обратные связи с выходов триггера на входы, которые позволяют устранить неопределенность в таблице состояний (рис. 2.50.а).

Рис. 2.50.a. Преобразование синхронного RS-триггера в JK-триггер;

Если на входы J и К подать уровень логической единицы, то получим T-триггер, который переключается каждым входным импульсом (рис. 2.50, б).

Рис. 2.50.б. Преобразование JK-триггера в T-триггер;

На рис. 2.50.в приведено условное обозначение JK-триггера и таблица состояний. При входных сигналах J=К=0 состояние триггера не изменяется, так как напряжение низкого уровня на одном входе элемента И-НЕ отменяет пpохождение сигналов от других его входов и удерживает выходной сигнал в текущем логическом состоянии.

Рис. 2.50.в. условное обозначение JK-триггера

| Установлено | Записано | ||

|---|---|---|---|

| J | K | Qn+1 | /Qn+1 |

| H | H | Без изменений Qn /Qn | |

| Н | В | Н=0 | В=1 |

| В | Н | В=1 | Н=0 |

| В | В | Переброс /Qn Qn | |

Если на входы J и К подать взаимно противоположные уровни,

то при подаче перепада напряжения на вход С выходы JK-триггера

устанавливаются в такие же состояния. При подаче на входы J и К

одновременно напряжений высокого уровня триггер переключается в состояние,

противоположное предыдущему, если на вход синхронизации С подать

перепад напряжения.

При подаче на входы J и К

одновременно напряжений высокого уровня триггер переключается в состояние,

противоположное предыдущему, если на вход синхронизации С подать

перепад напряжения.

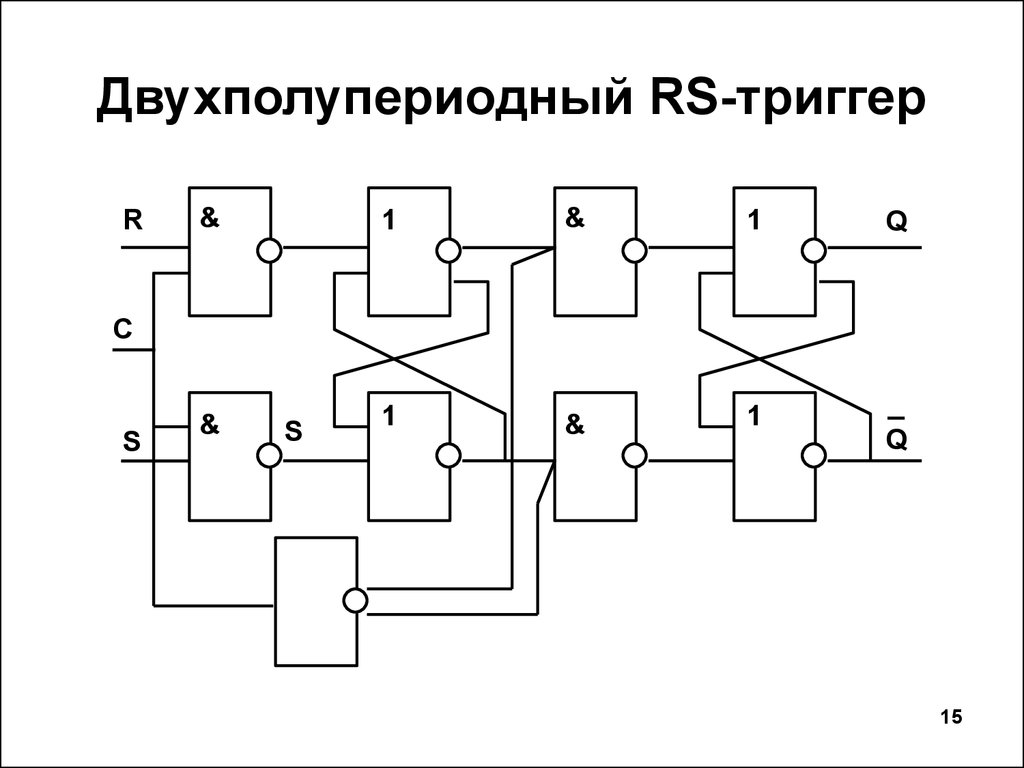

Управление полным тактовым импульсом, подаваемым на вход С, применяется для двухступенчатых триггеров (рис. 2.50.г).

Рис. 2.50.г. двухступенчатый JK-триггер;

Такой триггер тоже имеет обратные связи с выходов на входы, исключающие неопределенное состояние триггера.

Рис. 2.50.д. двухступенчатый JK-триггер на логических элементах И-НЕ

с симметричной схемой управления триггера второй ступени;

Из JK-триггера можно получить D-триггер, если вход К соединить со входом J через дополнительный инвертор (рис. 2.50,д).

Рис. 2.50.е. Схема преобразования JK-триггера в D-триггер

Микросхема TB1 (рис. 2.51) представляет собой универсальный двухступенчатый JK-триггер.

Рис. 2.51. Комбинированный JK-триггер – структура микросхемы, условное обозначение и цоколевка микросхемы ТВ1.

Триггер имеет инверсные асинхронные входы установки /S и сброса /R, т. е. с активным низким уровнем. Если на эти входы подать противоположные уровни (низкий – 0 и высокий – 1), то входы J, K и С не действуют и состояния выходов Q и /Q триггера определяются сигналами на входах /S и /R, таблица состояний (табл. 2.27).

| Режим работы | Входы | Выходы | |||||

|---|---|---|---|---|---|---|---|

| /S | /R | J | K | C | Qn+1 | /Qn+1 | |

| Асинхронная установка | 0 | 1 | Х | Х | Х | 1 | 0 |

| Асинхронный сброс | 1 | 0 | Х | Х | Х | 0 | 1 |

| Неопределенность | 0 | 0 | Х | Х | Х | X | X |

| Загрузка “1” (установка) | 1 | 1 | 1 | 0 | _/\_ | 1 | 0 |

| Загрузка “0” (сброс) | 1 | 1 | 0 | 1 | _/\_ | 0 | 1 |

| Переключение | 1 | 1 | 1 | 1 | _/\_ | /Qn | Qn |

| Хранение (нет изменений) | 1 | 1 | 0 | 0 | _/\_ | Qn | /Qn |

Когда на входы /S и /R поданы напряжения высокого уровня,

в триггер можно загружать информацию от входов J и K или

хранить ее (см. таблицу состояний). Каждый из входов J и K

снабжен логическим элементом 3И, т.е. микросхема ТВ1 имеет

три входа J и три входа K. Вход синхронизации C инверсный

динамический. Состояния двухступенчатого триггера переключаются

фронтом и спадом положительного импульса, подаваемого на вход

синхронизации C. Информация со входов J и K загружается в

триггер первой ступени (элементы DD1.3 и DD1.4), когда напряжение

входа C изменяется от низкого уровня к высокому (по фронту) и

переносится в триггер второй ступени по отрицательному перепаду

импульса синхронизации (по спаду). Сигналы на входах J и K не должны

изменяться, если на входе /C присутствует напряжение высокого уровня.

Состояния выходов Q и /Q будут неопределенные, если на входы /S и /R

одновременно подать напряжение низкого уровня, т. е. комбинация

сигналов /S=/R=0 является запрещенной.

таблицу состояний). Каждый из входов J и K

снабжен логическим элементом 3И, т.е. микросхема ТВ1 имеет

три входа J и три входа K. Вход синхронизации C инверсный

динамический. Состояния двухступенчатого триггера переключаются

фронтом и спадом положительного импульса, подаваемого на вход

синхронизации C. Информация со входов J и K загружается в

триггер первой ступени (элементы DD1.3 и DD1.4), когда напряжение

входа C изменяется от низкого уровня к высокому (по фронту) и

переносится в триггер второй ступени по отрицательному перепаду

импульса синхронизации (по спаду). Сигналы на входах J и K не должны

изменяться, если на входе /C присутствует напряжение высокого уровня.

Состояния выходов Q и /Q будут неопределенные, если на входы /S и /R

одновременно подать напряжение низкого уровня, т. е. комбинация

сигналов /S=/R=0 является запрещенной.

Микросхемы ТВ6 и ТВ9, ТВ10 и TB11 содержат по два JK-триггера с общим выводом питания (рис. 2.52).

Рис. 2.52. Структура, условное обозначение и цоколевка микросхем ТВ6, ТВ9;

Рис.

Вход синхронизации С у всех триггеров инверсный динамический, поэтому данные от входов J и К переносятся на выходы Q и /Q по отрицательному перепаду импульса С. Когда импульс на входе С переходит от высокого уровня к низкому, сигналы на входах J и К не должны изменяться. Информацию от входов J и К следует загружать в триггер, когда на входе С присутствует напряжение высокого уровня.

У триггеров микросхемы ТВ6 нет входа предварительной установки /S, поэтому в таблице состояний (комбинированного JK-триггера) необходимо исключить первую строку (асинхронную установку 1). Если на вход /R будет подано напряжение низкого уровня, то входы J, К и С не действуют.

У триггеров микросхемы ТВ10 нет входа предварительного сброса /R, поэтому в таблице состояний комбинированного JK-триггера необходимо исключить вторую строку (асинхронный сброс 0).

Для микросхем ТВ6 и ТВ10 в таблице состояний не имеет смысла и

третья строка, т. к, они имеют только по одному асинхронному

входу (либо /S, либо /R). Триггеры микросхемы ТВ11 в отличие

от триггеров микросхемы ТВ9 имеют две общие цепи управления:

вход синхронизации /С и асинхронный вход сброса /R (рис. 2.53).

к, они имеют только по одному асинхронному

входу (либо /S, либо /R). Триггеры микросхемы ТВ11 в отличие

от триггеров микросхемы ТВ9 имеют две общие цепи управления:

вход синхронизации /С и асинхронный вход сброса /R (рис. 2.53).

Рис. 2.53. Условное обозначение и цоколевка микросхемы ТВ11

Микросхемы ТВ14 и ТВ15 содержат по два комбинированных JK-триггера, которые запускаются положительным перепадом импульса синхронизации, т. е. вход С прямой динамический. Отличительной особенностью триггеров данных микросхем является то, что второй информационный вход /К – инверсный, поэтому очень легко такие JK-триггеры превращать в D-триггеры (рис. 2.54).

Рис. 2.54. Структура ТВ15, условные обозначения и цоколевки ТВ14 и ТВ15

Состояние таких триггеров приведено в табл. 2.28.

| Режим работы | Входы | Выходы | |||||

|---|---|---|---|---|---|---|---|

| /S | /R | J | /K | C | Qn+1 | /Qn+1 | |

| Асинхронная установка | 0 | 1 | X | X | X | 1 | 0 |

| Асинхронный сброс | 1 | 0 | X | X | X | 0 | 1 |

| Неопределенность | 0 | 0 | X | X | X | 1 | 1 |

| Загрузка “1” (установка) | 1 | 1 | 1 | 0 | _/\_ | 1 | 0 |

| Загрузка “0” (сброс) | 1 | 1 | 0 | 1 | _/\_ | 0 | 1 |

| Переключение | 1 | 1 | 1 | 0 | _/\_ | /Qn=1 | Qn=0 |

| Хранение (нет изменений) | 1 | 1 | 0 | 1 | _/\_ | 1 | 0 |

Основные параметры триггеров ТТЛ приведены в табл. 2.20.

2.20.

Триггеры. Принцип работы | HomeElectronics

Всем доброго времени суток! Сегодняшний мой пост посвящён цифровым микросхемам, которые имеют память. Подобно тому, как человек помнит события из своей жизни, так и эти микросхемы могут долго хранить заложенную в них информацию, а когда необходимо выдавать её.

Такими цифровыми микросхемами являются триггеры (англ. – Trigger или Flip-Flop). В отличие от простых логических микросхем, которые называют комбинационными (НЕ, И-НЕ, ИЛИ и другие) и их сигналы на выходе чётко соответствуют сигналам на входе, то триггеры относятся к последовательным или последовательностным микросхемам, уровень выходного напряжения которых, зависит от того в какой последовательности поступали сигналы на вход триггера. С помощью триггеров строят более сложные цифровые микросхемы.

Для сборки радиоэлектронного устройства можно преобрески DIY KIT набор по ссылке.

Сигналы, поступившие на вход триггера, могут храниться только до тех пор, пока на него подается напряжение питания. После каждого включения триггера на его выходах появляются случайные логические уровни напряжения. Триггеры обладают очень высоким быстродействием, сравнимым с задержками при переключении простейших логических элементов, однако объём хранимой информации мал. Один триггер может хранить только один сигнал или бит.

После каждого включения триггера на его выходах появляются случайные логические уровни напряжения. Триггеры обладают очень высоким быстродействием, сравнимым с задержками при переключении простейших логических элементов, однако объём хранимой информации мал. Один триггер может хранить только один сигнал или бит.

Внутреннее устройство триггера

Не вдаваясь в глубину схемотехники триггера, скажу сразу, что простейший триггер представляет собой схему из двух логических элементов, взаимодействуя между собой с помощью положительной обратной связи, которая обеспечивает нахождения выходов триггера в одном их двух логических состояний неограниченное время.

Схема триггерной ячейки на логических элементах (RS триггер).

Схема на рисунке выше представляет простейший триггер (или триггерная ячейка), который имеет два входа и два выхода. Входы триггера реагируют на низкий логический уровень: вход R – сброс (англ. Reset – сброс) и вход S – установка (англ. Set – установка), выходы: прямой Q (англ. Quit – выход) и инверсный –Q.

Set – установка), выходы: прямой Q (англ. Quit – выход) и инверсный –Q.

Как говорилось выше, входы триггера R и S реагируют на низкий логический уровень и сигналы на них должны поступать с некоторой разницей во времени. Опишем работу данной схемы. Когда на обоих входах триггера присутствует низкий логический уровень, то это никак не отразится на уровне напряжения на выходах. Когда на вход S поступит сигнал лог. 1, то на выходах Q будет лог. 0, а на –Q – лог. 1. Если теперь на вход R триггера поступит лог. 1, то выходные сигналы не изменятся. И наконец если изменить уровень сигнала на входе S с высокого на низкий уровень, то на выходе триггера Q будет лог. 1, а на –Q – лог. 0. Таким образом, для данной триггерной ячейки можно составить таблицу истинности.

| Входы | Выходы | ||

| R | S | Q | -Q |

| 0 | 0 | Не определено | |

| 0 | 1 | 0 | 1 |

| 1 | 1 | Без изменений | |

| 1 | 0 | 1 | 0 |

Схемы с такой таблицей истинности называются RS триггерами. RS триггеры служат основой для многих динамических устройств: делители частоты, счётчики, регистры. Кроме вышеописанного RS триггера существует ещё несколько типов триггеров, которые отличаются методом управления, входными и выходными сигналами. Все современные триггеры объединены в серии цифровых микросхем:

RS триггеры служат основой для многих динамических устройств: делители частоты, счётчики, регистры. Кроме вышеописанного RS триггера существует ещё несколько типов триггеров, которые отличаются методом управления, входными и выходными сигналами. Все современные триггеры объединены в серии цифровых микросхем:

- RS триггеры – самый простой и редко используемый триггер, имеет обозначение ТР;

- JK триггер – имеет сложное управление, обозначение ТВ;

- D триггер – самый распространённый и имеет сложность среднюю, обозначение ТМ;

RS триггеры

Рассмотрим принцип работы RS триггера возьмём микросхему К555ТР2.

Обозначение RS триггера К555ТР2

Данная микросхема имеет 4 RS триггера, два из которых имеют по одному R входу и одному S входу, а два других – по одному R входу и по два S входа, объединенных по функции И. Все 4 RS триггера данной микросхемы имеют по одному прямому выходу. Принцип работы данных триггеров не отличатся от триггерной ячейки описанной выше. Импульс с низким уровнем на входе триггера R приводит состояние выхода к низкому уровню, а импульс с низким логическим уровнем на входе триггера S – состояние выхода в высоком логическом уровне. В случае появления одновременных сигналов на входах триггера переводит его выход в состояние лог. 1, а после окончания импульсов в одно из устойчивых состояний.

Принцип работы данных триггеров не отличатся от триггерной ячейки описанной выше. Импульс с низким уровнем на входе триггера R приводит состояние выхода к низкому уровню, а импульс с низким логическим уровнем на входе триггера S – состояние выхода в высоком логическом уровне. В случае появления одновременных сигналов на входах триггера переводит его выход в состояние лог. 1, а после окончания импульсов в одно из устойчивых состояний.

JK триггер

Микросхема типа К555ТВ9, является представителем семейства JK триггеров, который имеет следующий принцип работы.

Обозначение JK триггера К555ТВ9.

Микросхема К555ТВ9 содержит два JK триггера. Триггеры данного типа сложнее по устройству и по управлению по сравнению с RS триггером. В дополнение к стандартным входам R и S, которые работают аналогично с RS триггером, в JK триггере имеются информационные входа J и K, а также вход синхронизации С.

| Входы | Выходы | |||||

| -S | -R | C | J | K | Q | -Q |

| 0 | 1 | Х | Х | Х | 1 | 0 |

| 1 | 0 | Х | Х | Х | 0 | 1 |

| 0 | 0 | Х | Х | Х | Не определено | |

| 1 | 1 | 1→0 | 1 | 0 | 1 | 0 |

| 1 | 1 | 1→0 | 0 | 1 | 0 | 1 |

| 1 | 1 | 1→0 | 0 | 0 | Не изменяется | |

| 1 | 1 | 1→0 | 1 | 1 | Меняется на противоположное | |

| 1 | 1 | 1 | Х | Х | Не изменяется | |

| 1 | 1 | 0 | Х | Х | Не изменяется | |

| 1 | 1 | 0→1 | Х | Х | Не изменяется | |

Принцип работы JK триггера следующий. Вход R триггера служит для перевода прямого выхода в лог.1, а вход S триггера – в состояние лог.0. Вход С (англ. Clock – часы)служит для тактирования JK триггера, то есть все изменения выходов происходят только когда на входе С сигнал изменяется с высокого уровня на низкий. Информационные входа J (англ. Jump – прыжок) и К (англ. Kill – убить) работают следующим образом: если на J лог.1 и на К лог.0, то по импульсу со входа С на Q будет лог.1 и на –Q будет лог.0. Для изменения уровня сигнала на выходах на противоположные необходимо на J подать лог.0, а на К лог.1, тогда по импульсу на входе С состояние выходов измениться.

Вход R триггера служит для перевода прямого выхода в лог.1, а вход S триггера – в состояние лог.0. Вход С (англ. Clock – часы)служит для тактирования JK триггера, то есть все изменения выходов происходят только когда на входе С сигнал изменяется с высокого уровня на низкий. Информационные входа J (англ. Jump – прыжок) и К (англ. Kill – убить) работают следующим образом: если на J лог.1 и на К лог.0, то по импульсу со входа С на Q будет лог.1 и на –Q будет лог.0. Для изменения уровня сигнала на выходах на противоположные необходимо на J подать лог.0, а на К лог.1, тогда по импульсу на входе С состояние выходов измениться.

D триггер

D триггер является самым используемым, а по управлению он занимает промежуточное положение между RS триггером и JK триггером. Представителем D триггеров является микросхема К555ТМ2.

Обозначение D триггера микросхемы К555ТМ2

В составе данной микросхемы содержится два D триггера, которые имеют два входа сброса и установки R и C, информационный вход D (англ. Dalay – задержка) триггера и один тактируемый вход С триггера, а также два выхода: прямой Q и инверсный –Q. Как и все триггеры, у которых имеется тактируемый вход С, принцип работы D триггера основан на переключении уровней напряжений на выходе триггера только стробированием по входу С. Таким образом можно составить таблицу истинности D триггера.

Dalay – задержка) триггера и один тактируемый вход С триггера, а также два выхода: прямой Q и инверсный –Q. Как и все триггеры, у которых имеется тактируемый вход С, принцип работы D триггера основан на переключении уровней напряжений на выходе триггера только стробированием по входу С. Таким образом можно составить таблицу истинности D триггера.

Таблица истинности D триггера

| Входы | Выходы | ||||

| -S | -R | C | D | Q | -Q |

| 0 | 1 | X | X | 1 | 0 |

| 1 | 0 | X | X | 0 | 1 |

| 0 | 0 | X | X | Не определено | |

| 1 | 1 | 0→1 | 0 | 0 | 1 |

| 1 | 1 | 0→1 | 1 | 1 | 0 |

| 1 | 1 | 0 | Х | Не меняется | |

| 1 | 1 | 1 | Х | Не меняется | |

| 1 | 1 | 1→0 | Х | Не меняется | |

D триггер является наиболее универсальным потому, что данным триггером можно заменить все остальные RS триггеры и JK триггеры. Для замены RS триггера необходимо просто не использовать входы D и C входы D триггера, а относительно JK триггера, то для большинства схем одной пары входов вполне достаточно. Ниже приведены схемы замены триггеров

Для замены RS триггера необходимо просто не использовать входы D и C входы D триггера, а относительно JK триггера, то для большинства схем одной пары входов вполне достаточно. Ниже приведены схемы замены триггеров

Схема замены D триггером: RS триггера (слева) и JK триггера в счётном режиме (справа).

Теория это хорошо, но необходимо отрабатывать это всё практически ПОПРОБЫВАТЬ МОЖНО ЗДЕСЬ

J-K триггер

J-K триггер

Если J и K оба низкие

тогда никаких изменений не происходит.

| Index Electronics concepts Digital circuits Sequential Operations J-K Flip-Flop Applications | |||||

| Назад |

Хотя эта реализация JK-триггера с четырьмя вентилями NAND в принципе работает, возникают проблемы с синхронизацией. Синхронизирующий импульс должен быть очень коротким, потому что изменение Q до того, как тактовый импульс погаснет, может вызвать в схеме колебание, называемое «гонками». Современные ИС настолько быстры, что эта простая версия триггера JK непрактична (мы собрали один в лаборатории с доступным чипом 4-NAND, и он был очень неустойчив к гонкам). Следующим шагом в использовании универсального JK-триггера является использование четырех дополнительных вентилей NAND для создания JK-триггера Master-Slave, который имеет два вентильных триггера SR, используемых в качестве защелок таким образом, чтобы подавлять «гонки». .

| Индекс Концепции электроники Цифровые схемы Учебники по электронике allaboutcircuits | |||||||||||||||||||||

| Назад |

Для этой версии JK-триггера при входных условиях J=K=1 переключение будет разрешено в любое время, когда часы имеют значение 1, а скорость переключения будет определяться задержкой распространения по цепи. Значение вывода в любое время нельзя было бы предсказать по состоянию часов. Это называется «гонками» или «состоянием гонки». Это неконтролируемое переключение можно подавить, используя схему ведущий-ведомый, в которой передача значения J на выход задерживается на половину тактового цикла и не возвращается немедленно на входную сторону.

| Index Electronics concepts Digital circuits Data Transfer J-K Flip-Flop Applications References ECE Turorials/ | ||||||

| Вернуться назад |

JK Flip Flop Схема, таблица истинности и пояснения к работе

Термин «цифровой» в электронике означает генерацию, обработку или хранение данных в виде двух состояний. Два состояния могут быть представлены как ВЫСОКОЕ или НИЗКОЕ, положительное или неположительное, установленное или сброшенное, что в конечном итоге является двоичным. Высокий уровень равен 1, а низкий уровень равен 0, и, следовательно, цифровая технология выражается последовательностью нулей и единиц. Примером является 011010, в котором каждый термин представляет отдельное состояние. Таким образом, этот процесс фиксации в аппаратном обеспечении выполняется с использованием определенных компонентов, таких как защелка или триггер, мультиплексор, демультиплексор, кодировщики, декодеры и т. д., которые вместе называются 9.0351 Последовательные логические схемы .

Два состояния могут быть представлены как ВЫСОКОЕ или НИЗКОЕ, положительное или неположительное, установленное или сброшенное, что в конечном итоге является двоичным. Высокий уровень равен 1, а низкий уровень равен 0, и, следовательно, цифровая технология выражается последовательностью нулей и единиц. Примером является 011010, в котором каждый термин представляет отдельное состояние. Таким образом, этот процесс фиксации в аппаратном обеспечении выполняется с использованием определенных компонентов, таких как защелка или триггер, мультиплексор, демультиплексор, кодировщики, декодеры и т. д., которые вместе называются 9.0351 Последовательные логические схемы .

Итак, мы собираемся обсудить триггеры , также называемые защелками . Защелки также можно понимать как бистабильный мультивибратор как два стабильных состояния. Как правило, эти схемы защелки могут быть либо активными-высокими, либо активными-низкими, и они могут запускаться сигналами ВЫСОКОГО или НИЗКОГО соответственно.

Общие типы триггеров:

- RS-триггер (RESET-SET)

- D Триггер (данные)

- JK Триггер (Джек-Килби)

- T Триггер (тумблер)

Из вышеперечисленных типов только триггеры JK и D доступны в форме интегрированной ИС и также широко используются в большинстве приложений. Здесь, в этой статье, мы обсудим JK Flip Flop .

Триггер JK:

Триггер JK назван в честь изобретателя Джека Килби из Texas Instruments. Благодаря своей универсальности они доступны в виде пакетов IC. Основными приложениями триггера JK являются регистры сдвига, регистры хранения, счетчики и схемы управления. Несмотря на простое подключение триггера типа D, триггер JK имеет переключающий характер. Это было дополнительным преимуществом. Следовательно, они в основном используются в счетчиках и генерации ШИМ и т. Д. Здесь мы используем Элементы И-НЕ для демонстрации триггера JK

Всякий раз, когда тактовый сигнал НИЗКИЙ, вход никогда не повлияет на состояние вывода . Часы должны быть высокими, чтобы входы стали активными. Таким образом, JK-триггер представляет собой управляемую бистабильную защелку , где тактовый сигнал является сигналом управления. Таким образом, выход имеет два устойчивых состояния на основе входных данных, которые обсуждались ниже.

Часы должны быть высокими, чтобы входы стали активными. Таким образом, JK-триггер представляет собой управляемую бистабильную защелку , где тактовый сигнал является сигналом управления. Таким образом, выход имеет два устойчивых состояния на основе входных данных, которые обсуждались ниже.

Таблица истинности JK Flip Flop:

Часы | ВХОД | ВЫХОД | |||

СБРОС | Дж | К | Q | Вопрос | |

х | НИЗКИЙ | х | х | 0 | 1 |

ВЫСОКИЙ | ВЫСОКИЙ | 0 | 0 | Без изменений | |

ВЫСОКИЙ | ВЫСОКИЙ | 0 | 1 | 0 | 1 |

ВЫСОКИЙ | ВЫСОКИЙ | 1 | 0 | 1 | 0 |

ВЫСОКИЙ | ВЫСОКИЙ | 1 | 1 | Переключить | |

НИЗКИЙ | ВЫСОКИЙ | х | х | Без изменений | |

ВЫСОКИЙ | ВЫСОКИЙ | х | х | Без изменений | |

ВЫСОКИЙ | ВЫСОКИЙ | х | х | Без изменений | |

J (Джек) и K (Килби) являются входными состояниями для триггера JK. Q и Q’ представляют собой выходные состояния триггера. Согласно таблице, на основе входов выход меняет свое состояние. Но важно учитывать, что все это может происходить только при наличии тактового сигнала. Это работает как триггер SR для дополнительных входов, и преимущество состоит в том, что он имеет функцию переключения.

Q и Q’ представляют собой выходные состояния триггера. Согласно таблице, на основе входов выход меняет свое состояние. Но важно учитывать, что все это может происходить только при наличии тактового сигнала. Это работает как триггер SR для дополнительных входов, и преимущество состоит в том, что он имеет функцию переключения.

Представление JK Flip-Flop с использованием логических вентилей:

Таким образом, сравнивая таблицу истинности вентилей И-НЕ с тремя и двумя входами и применяя входные данные, указанные в таблице истинности триггера JK, можно проанализировать выходные данные. Анализ вышеприведенной сборки как двухэтапной структуры, учитывая, что предыдущее состояние (Q’) равно 0

. ‘= 0. Работает правильно.

СБРОС:

На контакте RESET должен быть активный ВЫСОКИЙ уровень. Все контакты станут неактивными при низком уровне сигнала на контакте RESET. Следовательно, этот штифт всегда поднят вверх и может быть опущен только при необходимости.

Следовательно, этот штифт всегда поднят вверх и может быть опущен только при необходимости.

IC Пакет:

В | Истинный выход |

Q’ | Вывод комплимента |

ЧАСЫ | Ввод часов |

Дж | Ввод данных 1 |

К | Ввод данных 2 |

СБРОС | Прямой СБРОС (низкий уровень активации) |

ЗЕМЛЯ | Земля |

В СС | Напряжение питания |

Используется микросхема MC74HC73A (двойной триггер типа JK со СБРОСОМ). Это 14-контактный корпус, внутри которого находятся 2 отдельных JK-триггера. Выше приведена схема выводов и соответствующее описание выводов.

Выше приведена схема выводов и соответствующее описание выводов.

Требуемые компоненты:

- IC MC74HC73A (двойной триггер JK) – 1 шт.

- LM7805 – 1 шт.

- Тактильный переключатель — 4 шт.

- Батарея 9В – 1 шт.

- Светодиод (зеленый — 1; красный — 1)

- Резисторы (1кОм – 4; 220кОм -2)

- Макет

- Соединительные провода

Триггер JK Принципиальная схема и объяснение:

Источник питания IC V DD работает в диапазоне от 0 до +7 В, данные доступны в техническом описании. На снимке ниже это показано. Также мы использовали светодиод на выходе, источник был ограничен 5В для управления напряжением питания и выходным напряжением постоянного тока.

Мы использовали стабилизатор LM7805 для ограничения напряжения светодиода.

Практическая демонстрация и работа JK-триггера:

Кнопки J (Данные1), K (Данные2), R (Сброс), CLK (Часы) являются входами для JK-триггера. Два светодиода Q и Q’ отображают выходные состояния триггера. Батарея 9 В действует как вход для регулятора напряжения LM7805. Следовательно, регулируемый выход 5 В используется в качестве источника питания Vcc и вывода для микросхемы. Таким образом, для разных входов на D соответствующий выход можно увидеть через светодиоды Q и Q’.

Два светодиода Q и Q’ отображают выходные состояния триггера. Батарея 9 В действует как вход для регулятора напряжения LM7805. Следовательно, регулируемый выход 5 В используется в качестве источника питания Vcc и вывода для микросхемы. Таким образом, для разных входов на D соответствующий выход можно увидеть через светодиоды Q и Q’.

Штыри J, K, CLK обычно опущены, а штифт R поднят . Следовательно, состояние входа по умолчанию будет НИЗКИМ для всех контактов, кроме R, который является состоянием нормальной работы. Таким образом, начальное состояние по таблице истинности такое, как показано выше. Q=1, Q’=0 . Используемые светодиоды имеют ограничение по току с помощью резистора 220 Ом.

Примечание: Поскольку CLOCK срабатывает от HIGH к LOW фронту, обе кнопки ввода должны быть нажаты и удерживаться до тех пор, пока не будет отпущена кнопка CLOCK.

Ниже мы описали различные состояния JK Flip-Flop с использованием макетной платы с IC MC74HC73A . Демонстрационное видео также приведено ниже:

Демонстрационное видео также приведено ниже:

Состояние 1:

Часы – ВЫСОКИЙ ; Дж – 0 ; К – 1; Р – 1; Q – 0; Q’ – 1

Для входа состояния 1 горит КРАСНЫЙ светодиод, указывая на ВЫСОКИЙ уровень Q’, а ЗЕЛЕНЫЙ светодиод указывает на НИЗКИЙ уровень Q’. Работу можно проверить с помощью таблицы истинности.

Примечание: R уже поднят, поэтому не нужно нажимать кнопку, чтобы сделать это 1.

Состояние 2: Часы – ВЫСОКИЙ ; Дж – 1; К – 0; Р – 1; В – 1; Q’ – 0

Для входов состояния 2 горит ЗЕЛЕНЫЙ светодиод, указывая на ВЫСОКИЙ уровень Q’, а КРАСНЫЙ индикатор указывает на НИЗКИЙ уровень Q’. То же самое можно проверить с помощью таблицы истинности.

Состояние 3: Часы – ВЫСОКИЙ ; Дж – 1; К – 1; Р – 1; Q/Q’ — Переключение между двумя состояниями

Для входов состояния 3 КРАСНЫЙ и ЗЕЛЕНЫЙ светодиоды загораются попеременно для каждого тактового импульса (с ВЫСОКОГО на НИЗКИЙ фронт), указывая на действие переключения.

Если J и K оба высокие

на краю тактового сигнала выход будет переключаться из одного состояния в другое. Он может выполнять функции триггера установки/сброса и имеет то преимущество, что нет неоднозначных состояний. Он также может действовать как T-триггер для выполнения действия переключения, если J и K связаны вместе. Это приложение-переключатель находит широкое применение в двоичных счетчиках.

Если J и K оба высокие

на краю тактового сигнала выход будет переключаться из одного состояния в другое. Он может выполнять функции триггера установки/сброса и имеет то преимущество, что нет неоднозначных состояний. Он также может действовать как T-триггер для выполнения действия переключения, если J и K связаны вместе. Это приложение-переключатель находит широкое применение в двоичных счетчиках. Это то, что дает действие переключения, когда J=K=1.

Это то, что дает действие переключения, когда J=K=1. Состояние «разрешение» не сохраняется на протяжении всей положительной фазы часов. Входы J и K сами по себе не могут вызвать переход, но их значения во время PGT определяют выход в соответствии с таблицей истинности. Это применение универсального триггера JK. Поскольку эта версия JK-триггера 4-NAND подвержена проблеме «гонок», был разработан Master-Slave JK Flip Flop, чтобы обеспечить более стабильную схему с той же функцией.

Состояние «разрешение» не сохраняется на протяжении всей положительной фазы часов. Входы J и K сами по себе не могут вызвать переход, но их значения во время PGT определяют выход в соответствии с таблицей истинности. Это применение универсального триггера JK. Поскольку эта версия JK-триггера 4-NAND подвержена проблеме «гонок», был разработан Master-Slave JK Flip Flop, чтобы обеспечить более стабильную схему с той же функцией. Окончательный вывод Q затем отслеживает вывод ведущей секции M после половины такта.

Окончательный вывод Q затем отслеживает вывод ведущей секции M после половины такта.

Обратите внимание, что выходные сигналы возвращаются к разрешающим вентилям И-НЕ. Это то, что дает действие переключения, когда J=K=1. Переключение может быть желательным поведением, но обычно вы хотели бы, чтобы время переключения контролировалось тактовыми импульсами в качестве активаторов, чтобы вы могли контролировать и прогнозировать вывод.

Обратите внимание, что выходные сигналы возвращаются к разрешающим вентилям И-НЕ. Это то, что дает действие переключения, когда J=K=1. Переключение может быть желательным поведением, но обычно вы хотели бы, чтобы время переключения контролировалось тактовыми импульсами в качестве активаторов, чтобы вы могли контролировать и прогнозировать вывод.