Что такое 10 нм, 7 нм или 5 нм в смартфоне? Техпроцесс для «чайников»

Последнее обновление:

Оценка этой статьи по мнению читателей:Появление этой статьи на Deep-Review было лишь вопросом времени. Многие читатели задавали одни и те же вопросы, суть которых сводилась к следующему: что реально отражает эта цифра (12, 10, 7 или 5 нм) в технических характеристиках смартфонов, где в процессоре те самые 5 нанометров? Что вообще такое техпроцесс и какой процессор лучше выбрать?

Даже в современных печатных книгах сплошь и рядом встречается распространенное заблуждение, будто эти цифры означают размеры транзисторов, из которых состоит процессор.

В общем, пришло время разобраться с этим вопросом!

Сразу предупреждаю, что статья рассчитана на самый широкий круг читателей, то есть, при желании все сказанное смогут понять даже дети.

Но прежде, чем говорить о нанометрах и техпроцессе, нужно разобраться с транзистором. Без понимания этого устройства весь наш дальнейший разговор будет лишен смысла.

Без понимания этого устройства весь наш дальнейший разговор будет лишен смысла.

Что такое транзистор в процессоре смартфона? Как он работает и зачем вообще нужен?

Транзистор — это основа любого процессора, памяти и других микросхем. Он представляет собой крошечное устройство, способное работать в двух режимах: усиления или переключения электрического сигнала. Нас интересует именно режим переключателя.

Основа любой вычислительной техники — это единички и нолики. Просмотр видео на смартфоне, прослушивание музыки, дополненная реальность и нейронные сети — все это работает на «единичках и ноликах»:

- Единица — есть ток

- Ноль — нет тока

Именно для получения единиц и нулей мы используем транзисторы. Когда из этого миниатюрного устройства выходит ток, мы говорим, что это единица, когда нет никакого электрического сигнала — получаем ноль.

Соответственно, один транзистор — это совершенно бесполезная ерунда, которая не сможет сделать ничего. Даже, чтобы посчитать 2+2 нам нужны десятки транзисторов.

Даже, чтобы посчитать 2+2 нам нужны десятки транзисторов.

Итак, для создания транзистора мы берем немножко песка (условно какую-то часть одной песчинки) и делаем из него микроскопическую основу:

Это будет наша кремниевая подложка (кремний получают именно из песка). Теперь нужно на эту основу нанести две области. Я думал, стоит ли погружаться в физику этого процесса и объяснять, как эти области делаются и что там происходит на уровне электронов, но решил не перегружать статью излишней информацией. Поэтому будем немножко абстрагироваться.

Итак, делаем две области: в одну ток подаем (вход в транзистор), а из другой — считываем (выход):

Мы сделали эти области внутри кремниевой подложки таким образом, чтобы ток не смог пройти от входа к выходу. Он будет останавливаться самим кремнием (показан зеленым цветом). Чтобы ток смог пройти от входа к выходу по поверхности кремниевой подложки, нужно сверху разместить проводящий материал (скажем, металл) и хорошенько его изолировать:

А теперь самое важное! Когда мы подадим напряжение на этот изолированный кусочек металла, размещенный над кремниевой подложкой, он создаст вокруг себя электрическое поле. Изоляция никак не будет влиять на действие этого электрического поля. И здесь происходит вся «магия»: слой кремния под действием этого электрического поля начинает проводить ток от входа к выходу! То есть, когда мы подаем напряжение, ток может легко протекать между двумя областями:

Изоляция никак не будет влиять на действие этого электрического поля. И здесь происходит вся «магия»: слой кремния под действием этого электрического поля начинает проводить ток от входа к выходу! То есть, когда мы подаем напряжение, ток может легко протекать между двумя областями:

Вот и все! Осталось дело за малым — подключить «провода» (электроды) ко входу, выходу и кусочку изолированного металла, с помощью которого мы и будем включать/выключать транзистор. Назовем их так:

- Вход — Исток

- Выход — Сток

- Металл с изоляцией — Затвор

Для закрепления материала немножко поиграемся с этим транзистором.

Итак, транзистор находится под напряжением, то есть, электричество подается на исток. Но на затворе тока нет, так как на наш транзистор не «пришла единица». Соответственно затвор «закрыл» транзистор и ток по нему пройти дальше не сможет, так что и на выходе из транзистора мы получаем ноль:

Теперь ситуация изменилась и на затворе транзистора появилось напряжение, которое создало электрическое поле, позволившее току пройти через транзистор от истока к стоку. Как результат — транзистор выдал единицу (есть электрический сигнал):

Как результат — транзистор выдал единицу (есть электрический сигнал):

Вот так все просто! То есть, основное напряжение поступает на вход ко всем транзисторам, но будет ли каждый конкретный транзистор пропускать этот ток дальше — зависит от незначительного напряжения на затворе. Это напряжение может появляться, например, когда другой транзистор, подключенный к этому, отправил электрический импульс («единичку»).

Этого знания более, чем достаточно для того, чтобы ответить на все остальные вопросы, касательно нанометров и логики работы процессора.

О том, какие физические процессы стоят за таким нехитрым переключателем, то есть, что именно заставляет электроны проходить по кремнию, когда над ним появляется электрическое поле, я рассказывать не буду. Возможно, о легировании кремния фосфором и бором, p-n переходах и электрических полях мы поговорим как-нибудь в другой раз. А сейчас перейдем к основному вопросу.

Что такое техпроцесс или где же спрятаны эти «7 нанометров»?

Предположим, у нас есть современный смартфон, процессор которого выполнен по 7-нм техпроцессу. Что внутри такого процессора имеет размер 7 нанометров? Предлагаю вам выбрать правильный вариант ответа:

Что внутри такого процессора имеет размер 7 нанометров? Предлагаю вам выбрать правильный вариант ответа:

- Длина транзистора

- Ширина транзистора

- Расстояние между двумя транзисторами

- Длина затвора

- Ширина затвора

- Расстояние между затворами соседних транзисторов

Какой бы вариант вы ни выбрали, ваш ответ — неверный, так как ничего из перечисленного не имеет такого размера. Если бы этот же вопрос я задал лет 20 назад, правильным ответом была бы длина затвора (или длина канала, по которому протекает ток от стока к истоку):

Стоп! Длина канала, ширина, площадь — да какая разница, что в чем измеряется!? Зачем вообще придумали эти названия техпроцессов, для чего они нужны простым людям? Что вообще должен показывать техпроцесс обычному покупателю? Зачем ему знать ту же длину затвора транзистора?

Давным давно один человек по имени Гордон Мур (основатель корпорации Intel) задумался о том, как быстро развиваются технологии. Под словом «развитие» он подразумевал рост количества транзисторов, помещающихся на одной и той же площади. Дело в том, что этот показатель напрямую влияет на скорость вычислений. Процессор, вмещающий всего 1 млн транзисторов будет работать гораздо медленней, чем тот, внутри которого находятся 10 млн транзисторов.

Под словом «развитие» он подразумевал рост количества транзисторов, помещающихся на одной и той же площади. Дело в том, что этот показатель напрямую влияет на скорость вычислений. Процессор, вмещающий всего 1 млн транзисторов будет работать гораздо медленней, чем тот, внутри которого находятся 10 млн транзисторов.

Более того, уменьшая размер транзистора, автоматически снижается его энергопотребление (ток, проходящий через транзистор пропорционален отношению его ширины к длине). Также уменьшается размер затвора и его емкость, позволяя ему переключаться еще быстрее. В общем, одни плюсы!

Так вот, этот человек наблюдал за историей развития вычислительной техники и заметил, что количество транзисторов на кристалле удваивается примерно каждые 2 года. Соответственно, размеры транзисторов уменьшаются на корень из двух раз.

Другими словами, нужно умножать каждую сторону квадратного транзистора на 0.7, чтобы его площадь уменьшилась вдвое:

Это наблюдение получило название «закон Мура» и так родилась маркировка техпроцесса: каждые два года эту цифру умножали на 0. 7. Например, при переходе от 1000-нм техпроцесса к 700-нм, количество транзисторов на чипе возросло в 2 раза. Примерно то же можно сказать и обо всех современных процессорах: 14 нм -> 10 нм -> 7 нм -> 5 нм. Каждое последующее поколение просто умножаем на 0.7, предполагая, что количество транзисторов там увеличивалось вдвое.

7. Например, при переходе от 1000-нм техпроцесса к 700-нм, количество транзисторов на чипе возросло в 2 раза. Примерно то же можно сказать и обо всех современных процессорах: 14 нм -> 10 нм -> 7 нм -> 5 нм. Каждое последующее поколение просто умножаем на 0.7, предполагая, что количество транзисторов там увеличивалось вдвое.

Повторюсь, до определенного момента эта цифра означала длину канала (или длину затвора), так как эти элементы уменьшались пропорционально размеру транзистора.

Но затем удалось сокращать длину затвора быстрее, чем другие части транзистора. С тех пор связывать размер затвора с техпроцессом стало не совсем корректно, так как это уже не отражало реального увеличения плотности размещения транзисторов на кристалле.

Например, в 250-нм техпроцессе длина затвора составляла 190 нанометров, но транзисторы не были упакованы настолько плотно по сравнению с предыдущим техпроцессом, чтобы называть его 190-нанометровым (по размеру затвора). Это не отражало бы реальную плотность.

Это не отражало бы реальную плотность.

Затем длина канала и вовсе перестала уменьшаться каждые два года, так как появилась новая проблема. При дальнейшем уменьшении длины канала, электроны могли обходить узкий затвор, так как блокирующий эффект был недостаточно сильным. Более того, такие утечки возникали постоянно, вызывая повышенное энергопотребление и нагрев транзистора (и, как следствие, всего процессора).

В общем, техпроцесс отвязали от длины затвора и взяли просто группу из нескольких транзисторов (так называемую ячейку) и площадь этой ячейки использовали для названия техпроцесса.

К примеру, в 100-нм техпроцессе ячейка из 6 транзисторов занимала, скажем, 100 000 нанометров (это условная цифра из головы). Компания упорно работала над уменьшением размеров транзисторов или увеличением плотности их размещения и через пару лет добилась того, что в новом процессоре эта же ячейка занимает уже 50 000 нм.

Не важно, уменьшился ли размер транзисторов или просто удалось упаковать их более плотно (за счет сокращения слоя металла и других ухищрений), можно смело говорить, что количество транзисторов на кристалле выросло в два раза. А значит мы умножаем предыдущий техпроцесс (100 нм) на 0.7 и получаем новенький процессор, выполненный по 70-нм техпроцессу.

А значит мы умножаем предыдущий техпроцесс (100 нм) на 0.7 и получаем новенький процессор, выполненный по 70-нм техпроцессу.

Однако, когда мы дошли до 22-нанометрового техпроцесса, уменьшать длину затвора уже было нереально, так как электроны проходили бы сквозь этот затвор и транзисторы постоянно бы пропускали ток.

Решение оказалось простым и гениальным — нужно взять канал, по которому проходит ток и поднять его вверх, над кремниевой основной, чтобы он полностью проходил через затвор:

Теперь всё пространство, по которому идет ток, управляется затвором, так как полностью им окружено. А раньше, как мы видим, этот затвор находился сверху над каналом и создавал сравнительно слабый блокирующий эффект.

С новой технологией, получившей название FinFET, можно было продолжать уменьшать длину затвора и размещать еще больше транзисторов, так как они стали более узкими (сравните на картинке ширину канала). Но говорить о размерах транзистора стало вообще бессмысленно. Не совсем понятно даже, как эти размеры теперь высчитывать, когда транзистор из плоского превратился в трехмерный.

Таким образом, техпроцесс полностью «оторвался» от каких-либо реальных величин и просто условно обозначает увеличение плотности транзисторов относительно предыдущего техпроцесса.

К примеру, длина канала в 14-нм процессоре от Intel составляет 24 нанометра, а у Samsung — 30 нанометров. Отличаются и другие метрики этих процессоров, сделанных, казалось бы, по одинаковому техпроцессу. Более того, длина затвора — не самая миниатюрная часть транзистора. В том же 14-нм процессоре ширина канала вообще состоит из нескольких атомов и составляет 8 нанометров! То есть, техпроцесс — это даже не описание самой маленькой части транзистора.

Другими словами, нанометровый техпроцесс не описывает размеры транзисторов. Сегодня это условная цифра, означающая плотность размещения транзисторов или увеличение количества транзисторов относительно предыдущего техпроцесса (что напрямую влияет на быстродействие процессора).

В любом случае, важно запомнить простое правило и пользоваться им при анализе характеристик смартфона:

Разница техпроцесса в 0.

7 раз означает двукратное увеличение количества транзисторов

Для примера можем посмотреть на последние чипы от Apple. В 10-нм процессоре Apple A11 Bionic содержится 4.3 млрд транзисторов, а в 7-нм Apple A13 Bionic — 8.5 млрд транзисторов. То есть, видим, что техпроцесс отличается в 0.7 раз, а количество транзисторов — в 2 раза. Соответственно, 7-нм процессор гораздо производительней 10-нанометрового.

Продолжая аналогию, в 5-нм процессоре должно вмещаться в 2 раза больше транзисторов, чем в 7-нанометровом! Если вас не очень удивляет этот факт, обязательно почитайте на досуге мою заметку об экспоненциальном развитии технологий.

Итак, когда вы будете смотреть на два смартфона с 14-нм и 10-нм процессорами, то знайте что в последнем гораздо больше транзисторов, соответственно, его вычислительная мощность заметно выше. Так и следует пользоваться «техпроцессом» при выборе смартфона.

А если вам интересно, как эти бездушные транзисторы умеют «думать», делать сложные вычисления, показывать фильмы или проигрывать музыку, тогда ответы на эти вопросы читайте в нашем новом материале!

Алексей, глав. редактор Deep-Review

редактор Deep-Review

P.S. Не забудьте подписаться в Telegram на первый научно-популярный сайт о мобильных технологиях — Deep-Review, чтобы не пропустить очень интересные материалы, которые мы сейчас готовим!

где на самом деле 7 нанометров в технологии 7 нм? / Хабр

Современные микроэлектронные технологии — как «Десять негритят». Стоимость разработки и оборудования так велика, что с каждым новым шагом вперёд кто-то отваливается. После новости об отказе GlobalFoundries от разработки 7 нм их осталось трое: TSMC, Intel и Samsung. А что такое, собственно “проектные нормы” и где там тот самый заветный размер 7 нм? И есть ли он там вообще?

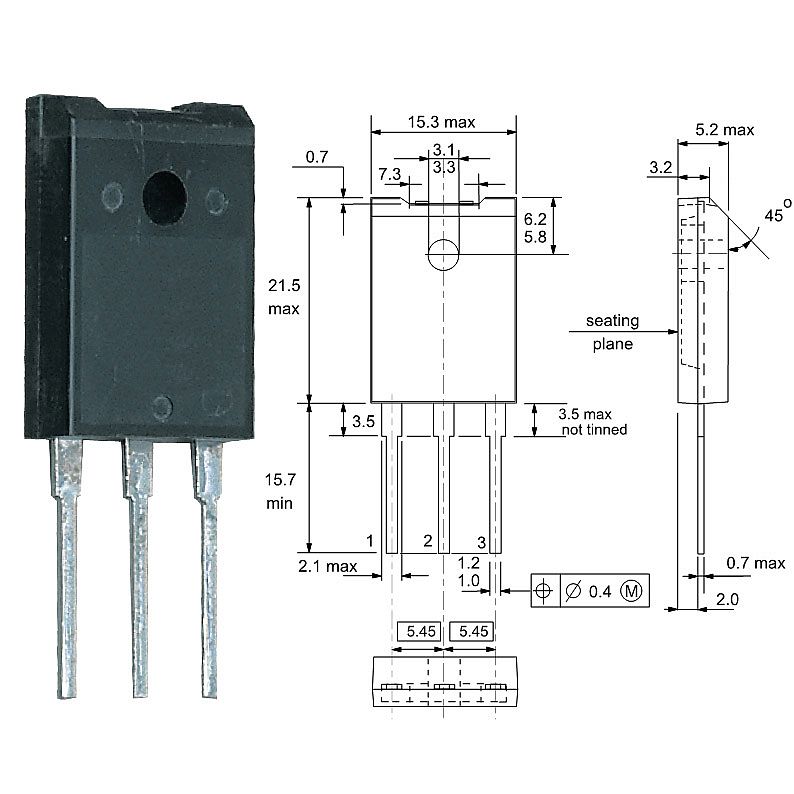

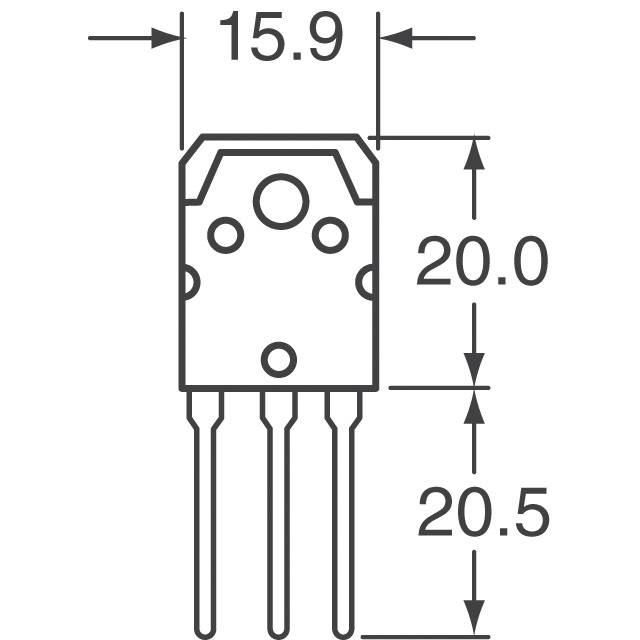

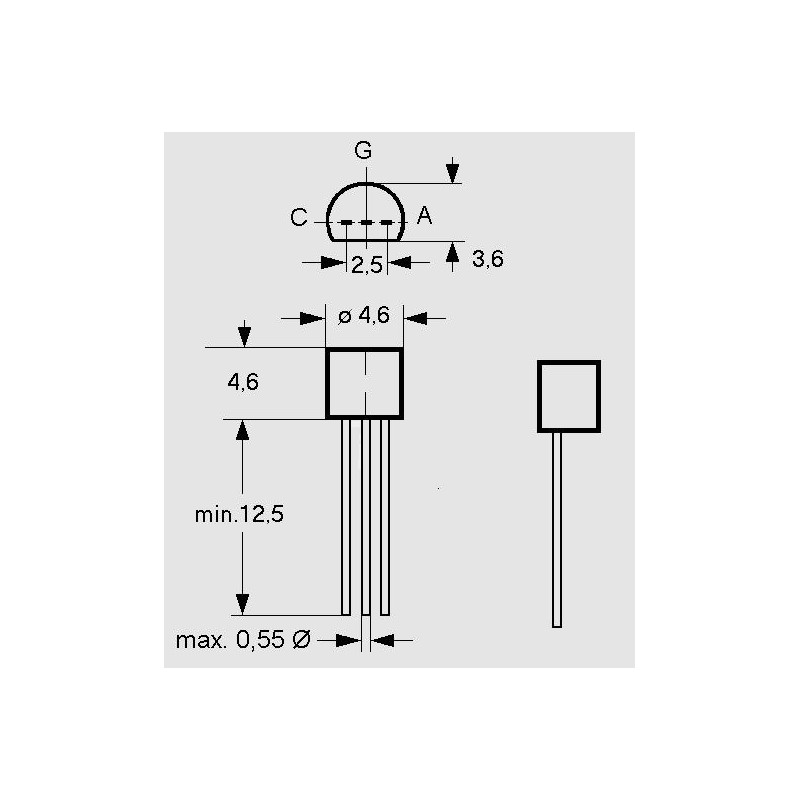

Рисунок 1. Транзистор Fairchild FI-100, 1964 год.

Самые первые серийные МОП-транзисторы вышли на рынок в 1964 году и, как могут увидеть из рисунка искушенные читатели, они почти ничем не отличались от более-менее современных — кроме размера (посмотрите на проволоку для масштаба).

Зачем уменьшать размер транзисторов? Самый очевидный ответ на этот вопрос носит название закона Мура и гласит, что каждые два года количество транзисторов на кристалле должно увеличиваться вдвое, а значит линейные размеры транзисторов должны уменьшаться в корень из двух раз.

Ток через МОП-транзистор пропорционален отношению его ширины к длине, а значит мы можем сохранять один и тот же ток, пропорционально уменьшая оба этих параметра. Более того, уменьшая размеры транзистора, мы уменьшаем еще и емкость затвора (пропорциональную произведению длины и ширины канала), делая схему еще быстрее. В общем, в цифровой схеме нет практически никаких причин делать транзисторы больше, чем минимально допустимый размер. Дальше начинаются нюансы насчет того, что в логике p-канальные транзисторы обычно несколько шире n-канальных, чтобы скомпенсировать разницу в подвижности носителей заряда, а в памяти наоборот, n-канальные транзисторы шире, чтобы память нормально записывалась через некомплементарный ключ, но это действительно нюансы, а глобально — чем меньше размеры транзистора — тем лучше для цифровых схем.

Именно поэтому длина канала всегда была самым маленьким размером в топологии микросхемы, и самым логичным обозначением проектных норм.

Здесь надо заметить, что вышеописанные рассуждения про размер не справедливы для аналоговых схем. Например, прямо сейчас на втором мониторе моего компьютера — согласованная пара транзисторов по 150 нм технологии, по 32 куска размером 8/1 мкм каждый. Так делается для того, чтобы обеспечить идентичность этих двух транзисторов, несмотря на технологический разброс параметров. Площадь при этом имеет второстепенное значение.

У технологов и топологов существует так называемая лямбда-система типовых размеров топологии. Она очень удобна для изучения проектирования (и была придумана в университете Беркли, если я не ошибаюсь) и переноса дизайнов с фабрики на фабрику. Фактически, это обобщение типичных размеров и технологических ограничений, но немного загрубленное, чтобы на любой фабрике точно получилось. На ее примере удобно посмотреть на типовые размеры элементов в микросхеме. Принципы в основе лямбда-системы очень просты:

Принципы в основе лямбда-системы очень просты:

- если сдвиг элементов на двух разных фотолитографических масках имеет катастрофические последствия (например, короткое замыкание), то запас размеров для предотвращения несостыковок должен быть не менее двух лямбд;

- если сдвиг элементов имеет нежелательные, но не катастрофические последствия, запас размеров должен быть не менее одной лямбды;

- минимально допустимый размер окон фотошаблона — две лямбды.

Из третьего пункта следует, в частности, то, что лямбда в старых технологиях — половина проектной нормы (точнее, что длина канала транзистора и проектные нормы — две лямбды).

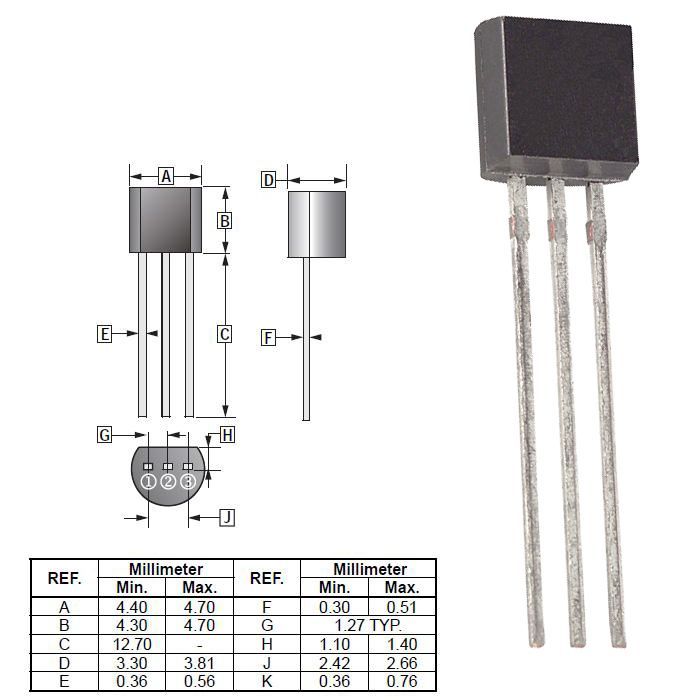

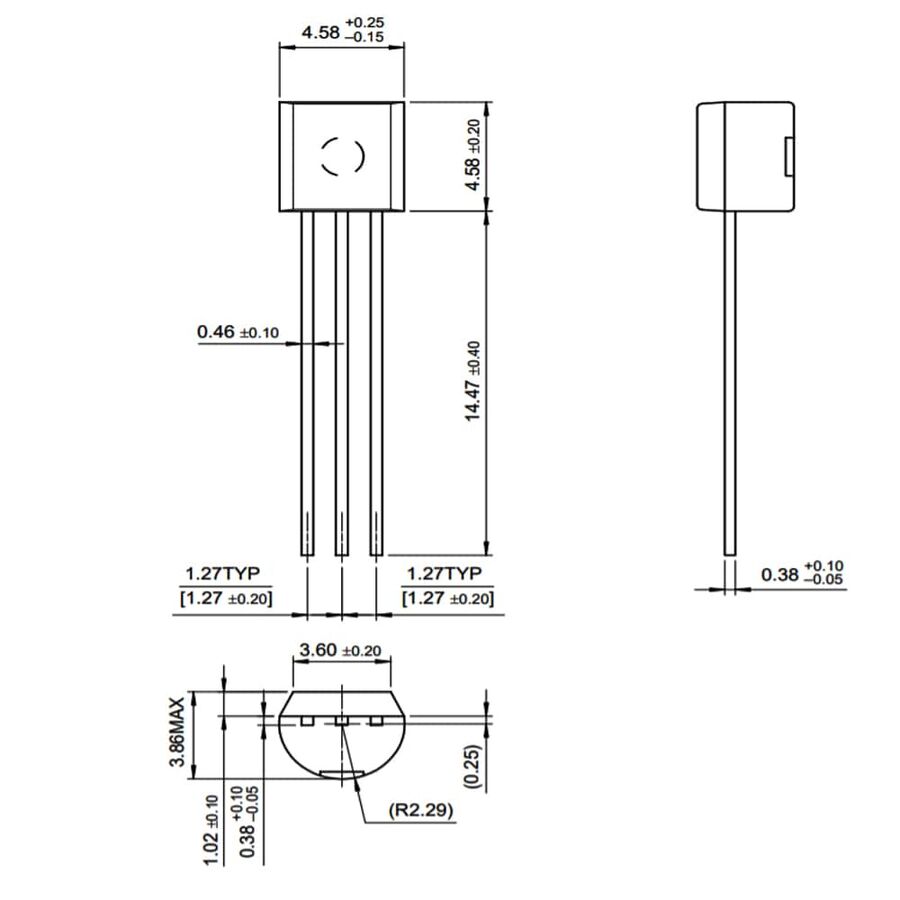

Рисунок 2. Пример топологии, выполненной по лямбда-системе.

Лямбда-система отлично работала на старых проектных нормах, позволяя удобно переносить производство с фабрики на фабрику, организовывать вторых поставщиков микросхем и делать много еще чего полезного. Но с ростом конкуренции и количества транзисторов на чипе фабрики стали стремиться сделать топологию немного компактнее, поэтому сейчас правила проектирования, соответствующие «чистой» лямбда-системе, уже не встретить, разве что в ситуациях, когда разработчики самостоятельно их загрубляют, имея в виду вероятность производства чипа на разных фабриках.

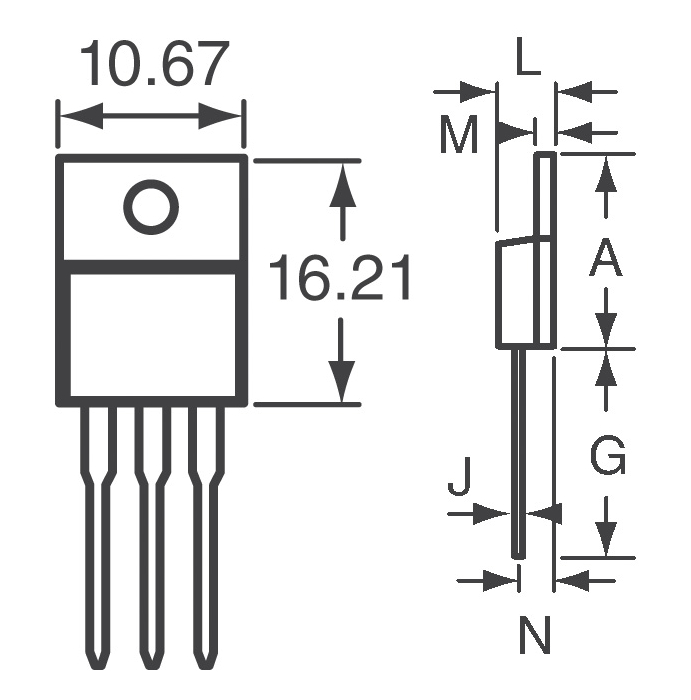

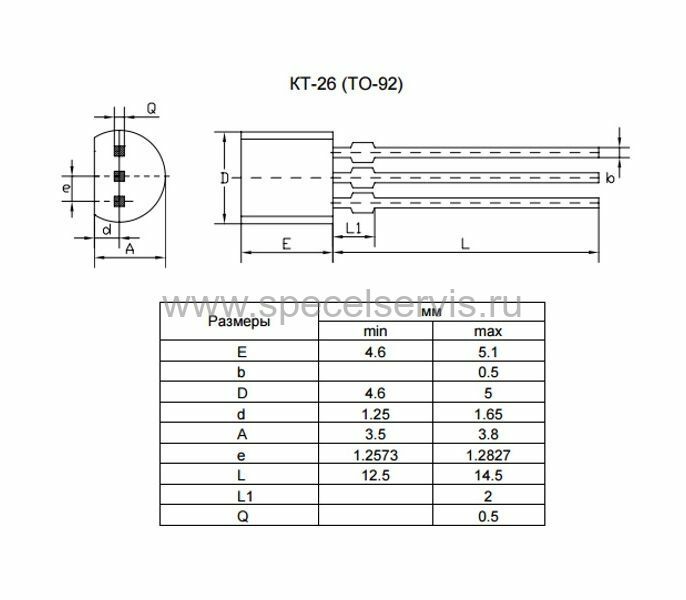

Рисунок 3. Схематичный разрез транзистора.

На этом рисунке приведен ОЧЕНЬ сильно упрощенный разрез обычного планарного (плоского) транзистора, демонстрирующий разницу между топологической длиной канала (Ldrawn) и эффективной длиной канала (Leff). Откуда берется разница?

Говоря о микроэлектронной технологии, почти всегда упоминают фотолитографию, но гораздо реже — другие, ничуть не менее важные технологические операции: травление, ионную имплантацию, диффузию и т.д. и т.п. Для нашего с вами разговора будет не лишним напоминание о том, как работают диффузия и ионная имплантация.

Рисунок 4. Сравнение диффузии и ионной имплантации.

С диффузией все просто. Вы берете кремниевую пластину, на которой заранее (с помощью фотолитографии) нанесен рисунок, закрывающий оксидом кремния те места, где примесь не нужна, и открывающий те, где она нужна.

Очевидный минус диффузии — то, что примесь проникает в кремний во всех направлениях одинаково, что вниз, что вбок, таким образом сокращая эффективную длину канала. И мы говорим сейчас о сотнях нанометров! Пока проектные нормы измерялись в десятках микрон, все было нормально, но разумеется, такое положение дел не могло продолжаться долго, и на смену диффузии пришла ионная имплантация.

При ионной имплантации пучок ионов примеси разгоняется и направляется на пластину кремния. При этом все ионы движутся в одном направлении, что практически исключает их расползание в стороны. В теории, конечно же. На практике ионы все-таки немного расползаются в стороны, хоть и на гораздо меньшие расстояния, чем при диффузии.

Тем не менее, если мы возвратимся к рисунку транзистора, то увидим, что разница между топологической и эффективной длиной канала начинается именно из-за этого небольшого расползания. Ей, в принципе, можно было бы пренебречь, но она — не единственная причина различия. Есть еще короткоканальные эффекты. Их пять, и они разными способами изменяют параметры транзистора в случае, если длина канала приближается к различным физическим ограничениям. Описывать все их я не буду, остановлюсь на самом релевантном для нас — DIBL (Drain-Induced Barrier Lowering, индуцированное стоком снижение потенциального барьера).

Ей, в принципе, можно было бы пренебречь, но она — не единственная причина различия. Есть еще короткоканальные эффекты. Их пять, и они разными способами изменяют параметры транзистора в случае, если длина канала приближается к различным физическим ограничениям. Описывать все их я не буду, остановлюсь на самом релевантном для нас — DIBL (Drain-Induced Barrier Lowering, индуцированное стоком снижение потенциального барьера).

Для того, чтобы попасть в сток, электрон (или дырка) должен преодолеть потенциальный барьер стокового pn-перехода. Напряжение на затворе уменьшает этот барьер, таким образом управляя током через транзистор, и мы хотим, чтобы напряжение на затворе было единственным управляющим напряжением. К сожалению, если канал транзистора слишком короткий, на поведение транзистора начинает влиять стоковый pn-переход, который во-первых, снижает поровогое напряжение (см. рисунок ниже), а во-вторых, на ток через транзистор начинает влиять напряжение не только на затворе, но и на стоке, потому что толщина стокового pn-перехода увеличивается пропорционально напряжению на стоке и соответственно укорачивает канал.

Рисунок 5. Эффект Drain-Induced Barrier Lowering (DIBL).

Источник — википедия.

Кроме того, уменьшение длины канала приводит к тому, что носители заряда начинают свободно попадать из истока в сток, минуя канал и формируя ток утечки (bad current на рисунке ниже), он же статическое энергопотребление, отсутствие которого было одной из важных причин раннего успеха КМОП-технологии, довольно тормозной по сравнению с биполярными конкурентами того времени. Фактически, каждый транзистор в современной технологии имеет стоящий параллельно ему резистор, номинал которого тем меньше, чем меньше длина канала.

Рисунок 6. Рост статического потребления из-за утечек в технологиях с коротким каналом.

Источник — Synopsys.

Рисунок 7. Доля статического энергопотребления микропроцессоров на разных проектных нормах.

Источник — B. Dieny et. al., «Spin-Transfer Effect and its Use in Spintronic Components», International Journal of Nanotechnology, 2010

Сейчас же, как вы можете видеть на рисунке выше, статическое потребление существенно превышает динамическое и является важным препятстствием для создания малопотребляющих микросхем, например, для носимой электроники и интернета вещей.

Для борьбы с нежелательными эффектами короткого канала на проектных нормах 800-32 нанометров было придумано очень много разных технологических решений, и я не буду описывать их все, иначе статья разрастется до совсем уж неприличных размеров, но с каждым новым шагом приходилось внедрять новые решения — дополнительные легирования областей, прилегающих к pn-переходам, легирования в глубине для предотвращения утечек, локальное превращение кремния в транзисторах в кремний-германий… Ни один шаг в уменьшении размеров транзисторов не дался просто так.

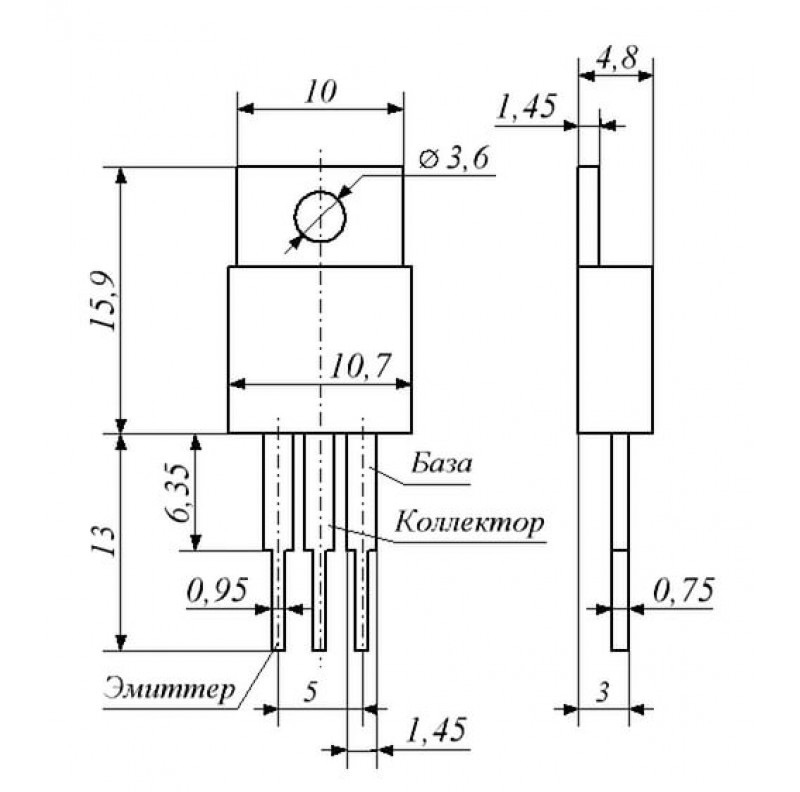

Рисунок 8. Эффективная длина канала в технологиях 90 нм и 32 нм. Транзисторы сняты в одном и том же масштабе. Полукруги на рисунках — это форма дополнительного слабого подлегирования стоков (LDD, lightly doped drain), делаемого для уменьшения ширины pn-переходов.

Источник — Synopsys.

Типичные размеры металлизации и расстояния между элементами при переходе от 90 нм до примерно 28 нм уменьшались пропорционально уменьшению цифры проектных норм, то есть типовой размер следующего поколения составлял 0.7 от предыдущего (чтобы, согласно закону Мура, получить двукратное уменьшение площади). Одновременно с этим длина канала уменьшалась в лучшем случае как 0.9 от предыдущего поколения, а эффективная длина канала практически не менялась вовсе. Из рисунка выше хорошо видно, что линейные размеры транзисторов при переходе от 90 нм к 32 нм изменились вообще не в три раза, и все игры технологов были вокруг уменьшения перекрытий затвора и легированных областей, а также вокруг контроля за статическими утечками, который не позволяли делать канал короче.

В итоге стали понятны две вещи:

- спуститься ниже 25-20 нм без технологического прорыва не получится;

- маркетологам стало все сложнее рисовать картину соответствия прогресса технологии закону Мура.

Закон Мура — это вообще противоречивая тема, потому что он является не законом природы, а эмпирическим наблюдением некоторых фактов из истории одной конкретной компании, экстраполированном на будущий прогресс всей отрасли. Собственно, популярность закона Мура неразрывно связана с маркетологами Intel, которые сделали его своим знаменем и, на самом деле, много лет толкали индустрию вперед, заставляя ее соответствовать закону Мура там, где, возможно, стоило бы немного подождать.

Какой выход нашли из ситуации маркетологи? Весьма изящный.

Длина канала транзистора — это хорошо, но как по ней оценить выигрыш площади, который дает переход на новые проектные нормы? Довольно давно в индустрии для этого использовалась площадь шеститранзисторной ячейки памяти — самого популярного строительного блока микропроцессоров. Именно из таких ячеек обычно состоит кэш-память и регистровый файл, которые могут занимать полкристалла, и именно поэтому схему и топологию шеститранзисторной ячейки всегда тщательно вылизывают до предела (часто — специальные люди, которые только этим и занимаются), так что это действительно хорошая мера плотности упаковки.

Рисунок 9. Схема шеститранзисторной ячейки статической памяти.

Рисунок 10. Разные варианты топологии шеститранзисторной ячейки статической памяти. Источник — G. Apostolidis et. al., «Design and Simulation of 6T SRAM Cell Architectures in 32nm Technology», Journal of Engineering Science and Technology Review, 2016

Так что довольно давно в описаниях технологий цифру проектных норм сопровождала вторая цифра — площадь ячейки памяти, которая, по идее, должна быть производной от длины канала. А дальше случилась интересная подмена понятий. В момент, когда прямое масштабирование перестало работать, и длина канала перестала уменьшаться каждые два года по закону Мура, маркетологи догадались, что можно не выводить площадь ячейки памяти из проектных норм, а выводить цифру проектных норм из площади ячейки памяти!

То есть натурально “раньше у нас была длина канала 65 нм и площадь ячейки памяти Х, а теперь длина канала 54 нм, но мы ужали металлизацию, и теперь площадь ячейки стала Х/5, что примерно соответствует переходу от 65 до 28 нм. Так давайте всем скажем, что у нас проектные нормы 28 нм, а про длину канала 54 нм никому говорить не будем?” Справедливости ради, “ужали металлизацию” — это тоже важное достижение, и какое-то время после начала проблем с миниатюризацией собственно транзисторов озвученным проектным нормам соответствовала минимальная ширина металлизации, размер контакта к транзистору или еще какая-нибудь цифра на топологии. Но дальше начались пляски с FinFET транзисторами, у которых ключевые размеры никак не связаны с разрешением литографии, скорости миниатюризации транзисторов и всего остального окончательно разошлись, и единственной нормальной цифрой осталась площадь ячейки памяти, на основе которой нам сейчас и сообщают про “10”, “7” и “5” нанометров.

Так давайте всем скажем, что у нас проектные нормы 28 нм, а про длину канала 54 нм никому говорить не будем?” Справедливости ради, “ужали металлизацию” — это тоже важное достижение, и какое-то время после начала проблем с миниатюризацией собственно транзисторов озвученным проектным нормам соответствовала минимальная ширина металлизации, размер контакта к транзистору или еще какая-нибудь цифра на топологии. Но дальше начались пляски с FinFET транзисторами, у которых ключевые размеры никак не связаны с разрешением литографии, скорости миниатюризации транзисторов и всего остального окончательно разошлись, и единственной нормальной цифрой осталась площадь ячейки памяти, на основе которой нам сейчас и сообщают про “10”, “7” и “5” нанометров.

Рисунок 11. Сравнение технологий 14 нм и 10 нм Intel.

Источник — Intel.

Вот отличный пример этого “нового скейлинга”. Нам показывают, как поменялись характерные размеры в ячейке памяти. Многие параметры, но о длине и ширине канала транзистора тут ни слова!

Как решали проблему невозможности уменьшения длины канала и контроля за утечками технологи?

Они нашли два пути. Первый — в лоб: если причина утечек — большая глубина имплантации, давайте ее уменьшим, желательно радикально. Технология «кремний на изоляторе» (КНИ) известна уже очень давно (и активно применялась все эти годы, например в 130-32 нм процессорах AMD, 90 нм процессоре приставки Sony Playstation 3, а также в радиочастотной, силовой или космической электронике), но с уменьшением проектных норм она получила второе дыхание.

Рисунок 12. Сравнение транзисторов, выполненных по обычной объемной и FDSOI (полностью обедненный КНИ) технологиях.

Источник — ST Microelectronics.

Как видите, идея более чем элегантная — под очень тонким активным слоем располагается оксид, убирающий вредный ток утечки на корню! Заодно, за счет уменьшения емкости pn-переходов (убрали четыре из пяти сторон куба стока) увеличивается быстродействие и еще уменьшается энергопотребление. Именно поэтому сейчас технологии FDSOI 28-22-20 нм активно рекламируются как платформы для микросхем интернета вещей — потребление действительно сокращается в разы, если не на порядок. И еще такой подход позволяет в перспективе поскейлить обычный плоский транзистор до уровня 14-16 нм, чего объемная технология уже не позволит.

Тем не менее, ниже 14 нм на FDSOI особенно не опуститься, да и другие проблемы у технологии тоже есть (например, страшная дороговизна подложек КНИ), в связи с чем индустрия пришла к другому решению — FinFET транзисторам. Идея FinFET транзистора тоже весьма элегантна. Мы хотим, чтобы бОльшая часть пространства между стоком и истоком управлялась затвором? Так давайте окружим это пространство затвором со всех сторон! Хорошо, не со всех, трех будет вполне достаточно.

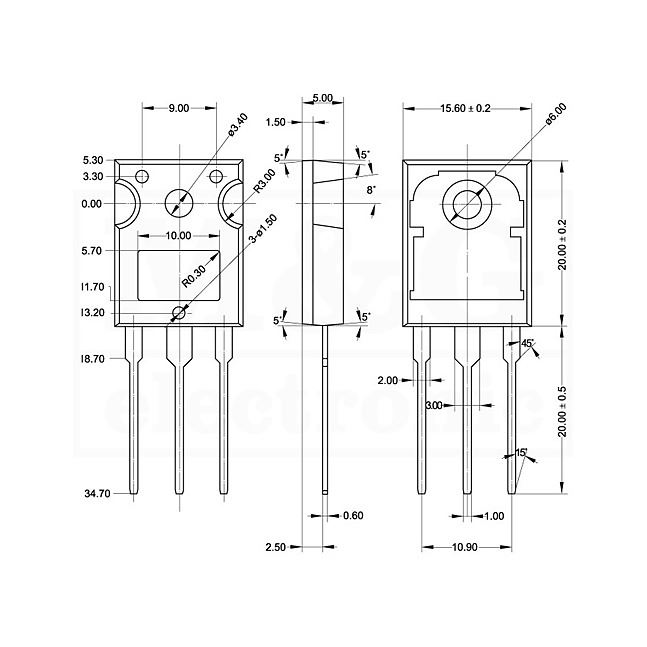

Рисунок 13. Структура FinFET.

Источник — A. Tahrim et.al., «Design and Performance Analysis of 1-Bit FinFET Full Adder Cells for Subthreshold Region at 16 nm Process Technology», Journal of Nanomaterials, 2015

Рисунок 14. Сравнение энергопотребления разных вариантов сумматора, выполненных на планарных транзисторах и на FinFET.

Источник — A. Tahrim et.al., «Design and Performance Analysis of 1-Bit FinFET Full Adder Cells for Subthreshold Region at 16 nm Process Technology», Journal of Nanomaterials, 2015

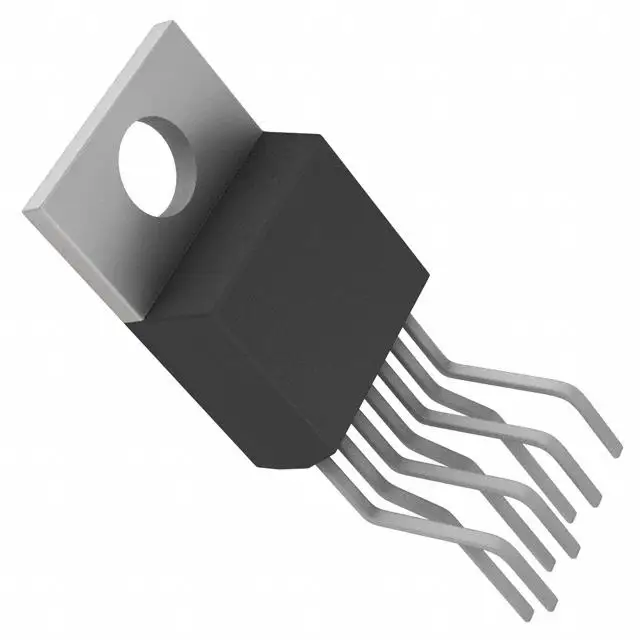

В FinFET канал не плоский и находящийся прямо под поверхностью подложки, а образует вертикальный плавник (Fin — это и есть плавник), выступающий над поверхностью и с трех сторон окруженный затвором. Таким образом, все пространство между стоком и истоком контролируется затвором, и статические утечки очень сильно уменьшаются. Первыми FinFET серийно выпустили Intel на проектных нормах 22 нм, дальше подтянулись остальные топовые производители, включая такого апологета КНИ, как Global Foundries (бывшие AMD).

Вертикальность канала в FinFET, кроме всего прочего, позволяет экономить на площади ячейки, потому что FinFET c широким каналом довольно узкий в проекции, и это, в свою очередь, опять помогло маркетологам с их рассказами про площадь ячейки памяти и ее двухкратное уменьшение с каждым новым шагом «проектных норм», уже никак не привязанных к физическим размерам транзистора.

Рисунок 15. Топологии разных вариантов ячеек памяти (5T-9T) в технологии с FinFET. Источник — M. Ansari et. al., «A near-threshold 7T SRAM cell with high write and read margins and low write time for sub-20 nm FinFET technologies», the VLSI Journal on Integration, Volume 50, June 2015.

Вот примеры разных вариантов ячеек памяти в технологии с FinFET. Видите, как геометрическая ширина канала намного меньше длины? Также можно видеть, что, несмотря на все пертурбации, лямбда-система у топологов все еще в ходу для количественных оценок. А что с абсолютными цифрами?

Рисунок 16. Некоторые размеры транзисторов в 14-16 нм технологиях.

Источник — the ConFab 2016 conference proceedings.

Как видно из рисунка, топологическая длина канала в 16 нм FinFET технологиях все еще больше, чем 20-25 нм, о которых говорилось выше. И это логично, ведь физику не обманешь. Но из этого же рисунка можно сделать и другой, более интересный вывод: если присмотреться, то становится понятно, что минимальный имеющийся в транзисторах размер — это не длина канала, а ширина плавника. И тут нас ожидает забавное открытие: ширина плавника в техпроцессе Intel 14 nm составляет (барабанная дробь!) ВОСЕМЬ нанометров.

Рисунок 17. Размеры плавника в 14 нм техпроцессе Intel.

Источник — wikichip.org

Как видите, тут маркетологи, привязавшись к размерам ячейки памяти, обманули сами себя, и теперь вынуждены озвучивать цифру больше, чем могли бы. На самом деле, конечно, в условиях принципиального изменения структуры транзистора и ожидания пользователей услышать какую-то метрику, использование метрики, отражающей плотность упаковки, было, наверное, единственно верным решением, и маркетологи в конечном счете оказались правы, хоть это и приводит иногда к забавным ситуациям, когда одни и те же проектные нормы в разных компаниях называют по-разному. Например, читая новости о том, что TSMC уже запустила 7 нм, а Intel опять задерживает начало производства 10 нм, стоит помнить о том, что 7 нм TSMC и 10 нм Intel — это на самом деле одни и те же проектные нормы с точки зрения и плотности упаковки, и размеров отдельных транзисторов.

Что дальше? На самом деле, никто не знает. Закон Мура исчерпал себя уже довольно давно, и если десять лет назад ответ на вопрос «что дальше?» можно было найти в отчетах исследовательских центров, то сейчас все чаще слышно о том, что от перспективных разработок приходится отказываться, так как они оказываются чрезмерно сложными во внедрении. Так уже произошло с пластинами диаметром 450 миллиметров, так частично происходит с EUV-литографией (с которой ученые носились лет двадцать), так, видимо, произойдет с транзисторами на графене и углеродных нанотрубках. Еще один технологический прорыв нужен, но пути к нему, как это ни прискорбно, пока не видно. Дошло до того, что новый директор TSMC Марк Лиу назвал наиболее перспективным направлением развития микроэлектронной технологии не уменьшение размеров транзисторов, а 3D-интеграцию. «Настоящая» 3D-интеграция, а не объединение нескольких чипов в одном корпусе действительно будет огромной вехой в развитии микроэлектроники, но вот закон Мура как закон уменьшения размеров транзисторов, кажется, умер окончательно.

Intel решила догнать и перегнать конкурентов, отказавшись от слова нанометр

| Поделиться Intel решила переименовать техпроцессы проивзодства чипов – старая схема, опирающаяся на физический размер транзистора, устарела и малоинформативна. Новая тоже не дает четкого представления об изделиях на ее основе, но демонстрирует, что технологическая отсталость чипмейкера от своих конкурентов не так уж велика – это важно в связи с грядущим выходом Intel на рынок контрактного производства. Intel не теряет надежд догнать и перегнать TSMC в течение четерых следующих лет. Для этого компания внедрит EUV, перейдет к полупроводниковым технологиям уровня ангстремов и начнет использовать инновационный GAA-транзистор, с разработкой которого ей, возможно, помогла IBM.Intel расписала план развития технологий до 2025 года

Intel представила дорожную карту развития технологий производства микропроцессоров до 2025 г.

Согласно анонсированному плану, корпорация изменит подход к именованию собственных технологических процессов, чтобы привести их в соответствие с принятыми в отрасли, в частности, компаниями TSMC и Samsung. Теперь в названии техпроцесса не будут фигурировать какие-либо единицы измерения длины. Вместо этого Intel будет обозначать техпроцесс, опираясь на соотношение между производительностью и энергопотреблением чипов на его базе.

Intel также представила новую архитектуру транзисторов RibbonFET – впервые за последние 10 лет, а также рассказала о технологии PowerVia, которая предлагает новый подход к подаче питания на транзисторы очень малого размера.

История и будущее инноваций в техпроцессах Intel

Кроме того, компания заявила о планах по внедрению фотолитографии в глубоком ультрафиолете (EUV) нового поколения (High-NA EUV). Intel рассчитывает завершить этот процесс первой в отрасли при помощи оборудования нидерландской ASML.

Чипмейкер рассчитывает догнать лидера отрасли TSMC к 2024 г. по показателю совершенства внедренного техпроцесса, а в 2025 г. и вовсе вернуть себе пальму первенства. Однако стоит иметь в виду, что Intel под этим понимает отношение производительности выпускаемых процессоров к потребляемой мощности, а не, например, применение самых компактных транзисторов в мире.

Новые названия техпроцессов

Итак, Intel отказывается от номенклатуры техпроцессов, которая включает слово «нанометры». 10-нанометровый процесс Enhanced SuperFin теперь называется Intel 7. По данным корпорации, у Intel 7 показатель производительности на единицу потребляемой мощности на 10–15% выше в сравнении с предшественником – 10-нм SuperFin. Intel 7 применяется при производстве новых процессоров семейств Alder Lake и Sapphire Rapids, которые предназначены для потребительского и серверного сегментов соответственно. Поставки чипов Alder Lake должны стартовать в 2021 г., Sapphire Rapids – в I квартале 2022 г.

Новая система именования техпроцессов Intel

Intel 4 (ранее Intel 7 нм) компания рассчитывает освоить ко второй половине 2022 г. Intel обещает прирост производительности на ватт на уровне по сравнению с предыдущим поколением на уровне 20%. Переход на данный техпроцесс также ознаменует полную адаптацию Intel к применению технологии EUV. Именно отставание в ее освоении называют в качестве причин задержки компании с выпуском 10-нм чипов. Технология Intel 4 будет применяться в настольных и мобильных процессорах Meteor Lake, а также серверных процессорах Granite Rapids, которые, как ожидается, появятся на рынке в 2023 г.

Техпроцесс Intel 3 (ранее Intel 7+ нм) должен обеспечить увеличить производительность на ватт примерно на 18% относительно предшественника. Процессоры на базе Intel 3 будут готовы к массовому производству во второй половине 2023 г.

Исторически в названии производственного процесса полупроводников фигурировало число, которое соответствовало длине затвора транзистора. Однако в 1994 г. производители перестали следовать этому правилу. До 2009 г. длина затвора была меньше заявленного в названии значения, а затем «нанометры» взяли на вооружение маркетологи, из-за чего цифры в названии техпроцесса стали иметь мало общего с фактическими размерами транзисторов или плотностью их расположения в интегральной схеме. Например, актуальный 10-нм процесс Intel (FinFET) по размеру и плотности размещения транзисторов примерно соответствует 7-нм процессу TSMC.

Решение отказаться от традиционного числового определения производственных норм в нанометрах, по всей видимости, связано с недавним решением Intel выйти на рынок контрактного производства. Здесь американская корпорация будет напрямую конкурировать с гигантами вроде тайваньской TSMC и южнокорейской Samsung, поэтому пересмотр принципа именования производственных норм выглядит логичным – так заказчикам будет проще ориентироваться на рынке.

Ангстремная эра, транзисторы RibbonFET и технология PowerVia

Первая половина 2024 г., согласно планам Intel, ознаменуется наступлением эры ангстрема, в которой некоторые физические характеристики чипов можно будет выразить только в десятых долях нанометра – ангстремах (десятимиллиардных долях метра).

Первый техпроцесс Intel новой эры будет иметь обозначение 20A (A – angstrom, ангстрем), однако это не значит, что транзистор обязательно будет соответствующего размера. Тем не менее, технология производства Intel 20A предусматривает использование новых транзисторов под названием RibbonFET. Это первый транзистор Intel с кольцевым затвором (GAA, Gate-all-around) и первый транзистор новой архитектуры, выпущенный Intel с 2011 г.

RibbonFET отличается от используемых сейчас FinFET тем, что в первом каждый из четырех его каналов окружен затвором не с трех, а с четырех сторон. Такая конструкция, по оценке Intel, позволяет увеличить скорость переключения устройства при использовании такого же управляющего тока.

Схематичное изображение транзистора RibbonFET с кольцевым затвором

Кроме того, в техпроцессе Intel 20A чипмейкер планирует использовать технологию PowerVia – подачу питания с обратной стороны кристалла через межкремниевые соединения. Запуск Intel 20A ожидается в 2024 г. В частности, продукция Qualcomm будет выпускаться по техпроцессу Intel 20A, однако пока не известно, что это будут за чипы.

Private LTE: что важно знать о выделенных сетях

Беспроводная связьНа начало 2025 г. намечено освоение техпроцесса Intel 18A. Именно тогда Intel рассчитывает внедрить EUV-литографию с высокой числовой апертурой (High-NA EUV).

Проблемы Intel и пути их решения

Intel испытала серьезные проблемы с внедрением 10-нанометрового техпроцесса, неоднократно откладывая его.

Сперва корпорация обещала начать выпуск 10-нанометровых чипов в 2015 г., после чего последовало несколько сообщений о задержке. В результате официальная дата выхода нового поколения микросхем была перенесена на 2017 г., но затем вновь сдвинута на второе полугодие 2018 г. В конце апреля 2018 г. тогдашний глава компании Брайан Кржанич (Brian Krzanich), объявил о том, что Intel сможет запустить 10-нанометровые процессоры в массовое производство не ранее 2019 г.

В конце мая 2019 г. Intel официально представила свои первые массовые 10-нанометровые процессоры – чипы Ice Lake на базе новой архитектуры Sunny Cove, предназначенные для мобильных устройств.

Пока Intel «покоряла» 10 нанометров и осуществляла реорганизацию производственного подразделения, его главный конкурент – компания AMD – успешно освоила нормы техпроцесса 7 нм.

В марте 2021 г. Intel анонсировала новую стратегию своего развития на ближайшие годы, получившую название IDM 2.0. Для ее реализации Intel вернула в штат нескольких ценных экс-сотрудников.

В рамках реализации стратегии чипмейкер планировал построить два новых завода за три года и $20 млрд, перейти на 7 нм в 2023 г. и стать партнером многих крупных производителей чипов, которые помогут ему в выпуске собственных процессоров.

В частности, Intel упоминала о партнерстве с IBM, которая в начале мая 2021 г. представила первый GAA-транзистор размером 2 нм и тестовый чип на его основе. Tom’s Hardware предполагает, что IBM могла оказать Intel помощь в разработке фирменных транзисторов RibboFET.

В начале июля 2021 г. CNews писал о том, что, по некоторым данным, Intel выпустит свой первый 3-нанометровый процессор в начале 2023 г., причем сделает это в сотрудничестве с TSMC. Также в июле 2021 г. сообщалось о возможном приобретении Intel компании GlobalFoundries, входящую в тройку крупнейших мировых производителей полупроводников, за $30 млрд. Однако позже представители последней опровергли информацию о будущей сделке.

Дмитрий Степанов

8. Транзисторы – Условные графические обозначения на электрических схемах – Компоненты – Инструкции

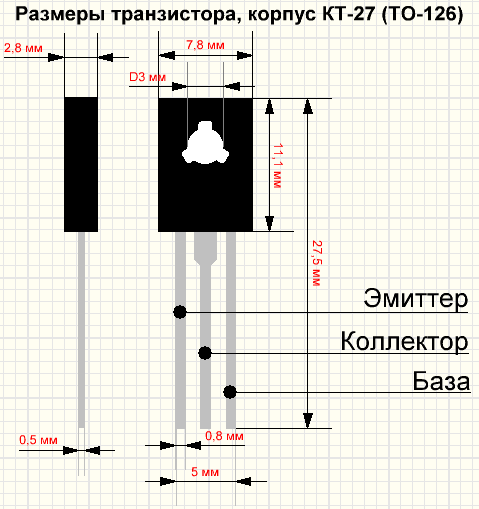

Транзистор (от английских слов tran(sfer) — переносить и (re)sistor — сопротивление) — полупроводниковый прибор, предназначенный для усиления, генерирования и преобразования электрических колебаний. Наиболее распространены так называемые биполярные транзисторы. Электропроводность эмиттера и коллектора всегда одинаковая (р или n), базы — противоположная (n или р). Иными словами, биполярный транзистор содержит два р-n-перехода: один из них соединяет базу с эмиттером (эмиттерный переход), другой — с коллектором (коллекторный переход).

Буквенный код транзисторов — латинские буквы VT. На схемах эти полупроводниковые приборы обозначают, как показано на рис. 8.1 [5]. Здесь короткая черточка с линией от середины символизирует базу, две наклонные линии, проведенные к ее краям под углом 60°, — эмиттер и коллектор. Об электропроводности базы судят по символу эмиттера: если его стрелка направлена к базе (см. рис. 8.1, VT1), то это означает, что эмиттер имеет электропроводность типа р, а база— типа n; если же стрелка направлена в противоположную сторону (VT2), электропроводность эмиттера и базы обратная.

Знать электропроводность эмиттера базы и коллектора необходимо для того, чтобы правильно подключить транзистор к источнику питания. В справочниках эту информацию приводят в виде структурной формулы. Транзистор, база которого имеет электропроводимость типа n, обозначают формулой р-п-р, а транзистор с базой, имеющей электропроводность типа р, обозначают формулой n-р-n. В первом случае на базу и коллектор следует подавать отрицательное по отношению к эмиттеру напряжение, во втором — положительное.

Для наглядности условное графическое обозначение дискретного транзистора обычно помещают в кружок, символизирующий его корпус. Иногда металлический корпус соединяют с одним из выводов транзистора. На схемах это показывается точкой в месте пересечения соответствующего вывода с символом корпуса. Если же корпус снабжен отдельным выводом, линию-вывод допускается присоединять к кружку без точки (VT3 на рис. 8.1). В целях повышения информативности схем рядом с позиционным обозначением транзистора допускается указывать его тип.

Линии электрической связи, идущие от эмиттера и коллектора проводят в одном из двух направлений: перпендикулярно или параллельно выводу базы (VT3—VT5). Излом вывода базы допускается лишь на некотором расстоянии от символа корпуса (VT4).

Транзистор может иметь несколько эмиттерных областей (эмиттеров). В этом случае символы эмиттеров обычно изображают с одной стороны символа базы, а окружность обозначения корпуса заменяют овалом (рис. 8.1, VT6).

Стандарт допускает изображать транзисторы и без символа корпуса, например, при изображении бескорпусных транзисторов или когда на схеме необходимо показать транзисторы, входящие в состав сборки транзисторов или интегральной схемы.

Поскольку буквенный код VT предусмотрен для обозначения транзисторов, выполненных в виде самостоятельного прибора, транзисторы сборок обозначают одним из следующих способов: либо используют код VT и присваивают им порядковые номера наряду с другими транзисторами (В этом случае на поле схемы помещают такую, например, запись: VT1-VT4 К159НТ1), либо используют код аналоговых микросхем (DA) и указывают принадлежность транзисторов в сборке в позиционном обозначении (рис. 8.2, DA1.1, DA1.2). У выводов таких транзисторов, как правило, приводят условную нумерацию, присвоенную выводам корпуса, в котором выполнена матрица.

Без символа корпуса изображают на схемах и транзисторы аналоговых и цифровых микросхем (для примера на рис. 8.2 показаны транзисторы структуры п-р-п с тремя и четырьмя эмиттерами).

Условные графические обозначения некоторых разновидностей биполярных транзисторов получают введением в основной символ специальных знаков. Так, чтобы изобразить лавинный транзистор, между символами эмиттера и коллектора помещают знак эффекта лавинного пробоя (см. рис. 8.3, VT1, VT2). При повороте УГО положение этого знака должно оставаться неизменным.

Иначе построено УГО однопереходного транзистора: у него один р-п-переход, но два вывода базы. Символ эмиттера в УГО этого транзистора проводят к середине символа базы (рис. 8.3, VT3, VT4). Об электропроводности последней судят по символу эмиттера (направлению стрелки).

На символ однопереходного транзистора похоже УГО большой группы транзисторов с p-n-переходом, получивших название полевых. Основа такого транзистора — созданный в полупроводнике и снабженный двумя выводами (исток и сток) канал с электропроводностью п или р-типа. Сопротивлением канала управляет третий электрод — затвор. Канал изображают так же, как и базу биполярного транзистора, но помещает в середине кружка-корпуса (рис. 8.4, VT1), символы истока и стока присоединяют к нему с одной стороны, затвора — с другой стороны на продолжении линии истока. Электропроводность канала указывают стрелкой на символе затвора (на рис. 8.4 условное графическое обозначение VT1 символизирует транзистор с каналом п-типа, VT1 — с каналом p-типа).

В условном графическом обозначении полевых транзисторов с изолированным затвором (его изображают черточкой, параллельной символу канала с выводом на продолжении линии истока) электропроводность канала показывают стрелкой, помещенной между символами истока и стока. Если стрелка направлена к каналу, то это значит, что изображен транзистор с каналом n-типа, а если в противоположную сторону (см. рис. 8.4, VT3) — с каналом p-типа. Аналогично поступают при наличии вывода от подложки (VT4), а также при изображении полевого транзистора с так называемым индуцированным каналом, символ которого — три коротких штриха (см. рис. 8.4, VT5, VT6). Если подложка соединена с одним из электродов (обычно с истоком), это показывают внутри УГО без точки (VT1, VT8).

В полевом транзисторе может быть несколько затворов. Изображают их более короткими черточками, причем линию-вывод первого затвора обязательно помещают на продолжении линии истока (VT9).

Линии-выводы полевого транзистора допускается изг[цензура] лишь на некотором расстоянии от символа корпуса (см. рис. 8.4, VT2). В некоторых типах полевых транзисторов корпус может быть соединен с одним из электродов или иметь самостоятельный вывод (например, транзисторы типа КПЗ03).

Из транзисторов, управляемых внешними факторами, широкое применение находят фототранзисторы. В качестве примера на рис. 8.5 показаны условные графические обозначения фототранзисторов с выводом базы (FT1, VT2) и без него (К73). Наряду с другими полупроводниковыми приборами, действие которых основано на фотоэлектрическом эффекте, фототранзисторы могут входить в состав оптронов. УГО фототранзистора в этом случае вместе с УГО излучателя (обычно светодиода) заключают в объединяющий их символ корпуса, а знак фотоэффекта — две наклонные стрелки заменяют стрелками, перпендикулярными символу базы.

Для примера на рис. 8.5 изображена одна из оптопар сдвоенного оптрона (об этом говорит позиционное обозначение U1.1), Аналогично строится У ГО оптрона с составным транзистором (U2).

7 против 14 нм: сравнение размера транзисторов Intel и TSMC

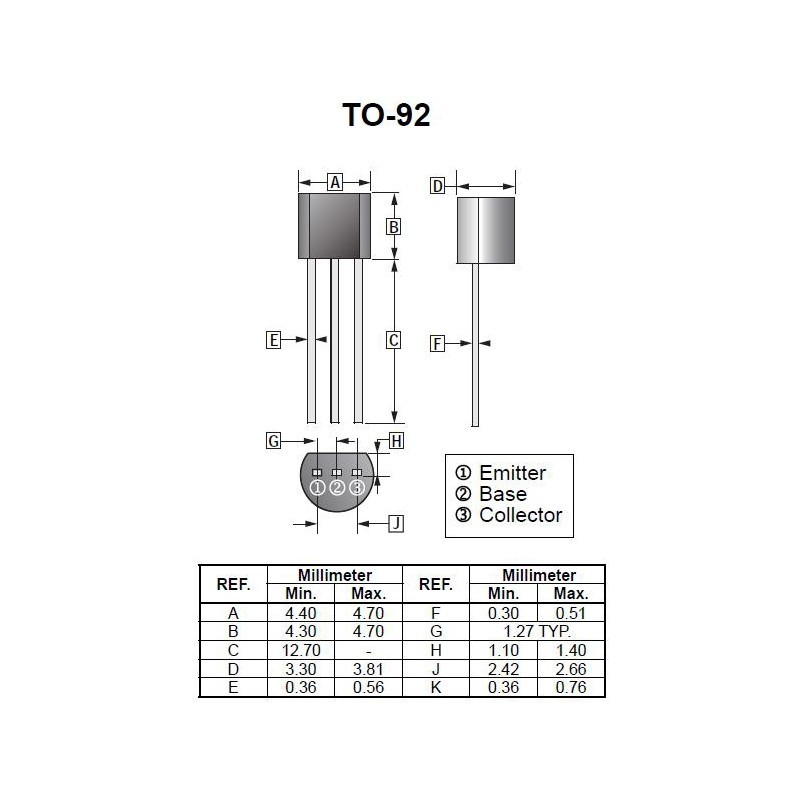

Чуть больше двух лет назад Роман Хартунг с ником der8auer поместил Intel Core i7-8700K под растровый электронный микроскоп в Хайльброннской высшей школе. Теперь настала очередь AMD Ryzen 9 3950X и Intel Core i9-10900K, вернее, соответствующих кристаллов. Цель заключалась в том, чтобы сравнить 7- и 14-нм техпроцесс.

С помощью нагрева, шкурки и других материалов 10-ядерный кристалл Intel и кристаллы CCD и IOD процессора Ryzen 9 3950X были извлечены из корпусировки. Но перед тем, как поместить их под растровый электронный микроскоп, необходимы и другие шаги. Среди прочего, семпл нужно приклеить на пробу. Причем для работы микроскопа должен использоваться проводящий материал.

Сначала на семпл напыляется платина, затем с помощью ионного луча семпл вырезается из кристалла для дальнейшего изучения. Процесс напыления длится несколько часов, после чего к семплу крепится игла-держатель. Длина семпла составляет всего 100 мкм. С помощью платинового напыления игла скрепляется с семплом. В итоге слой семпла толщиной всего 200-300 нм можно изучать под электронным микроскопом.

На первых двух видеороликах показана подготовка семпла и работа растрового электронного микроскопа. Третий видеоролик, наконец, посвящен изучению транзисторов.

На видео показаны транзисторы процессора Ryzen, который изготавливается по 7-нм техпроцессу (TSMC, N7), и процессора Intel с 14-нм техпроцессом (14 nm+++). Хорошо видно, что ширина затвора процессоров Intel Core i9-10900K составляет 24 нм, а у 7-нм процессора Ryzen она ненамного меньше – 22 нм. Высота затвора тоже очень близка, но TSMC располагает транзисторы более плотно.

Вывод следующий: сравнение техпроцессов только на “числах” не так важно. Следует оценивать плотность упаковки транзисторов и 3D-структуру, которая именно трехмерная. А число техпроцесса – одномерная характеристика. Кроме того, существуют разные типы транзисторов, в зависимости от сферы использования: кэш или логика процессора, например. Intel и TSMC с техпроцессами 7 и 10 нм, соответственно, располагают на квадратном миллиметре порядка 90 млн. транзисторов. Для 5 нм (TSMC) и 7 нм (Intel) плотность транзисторов будет уже больше 150 MT/мм².

Но, опять же, данные значения нельзя напрямую сравнивать друг с другом, поскольку high-end процессор использует транзисторы разных типов. То же самое касается GPU. Недавно мы как раз рассматривали новый Ampere GPU от NVIDIA. GA102 GPU производится по 8-нм техпроцессу на заводах Samsung, плотность составляет 44,56 MT/мм², в случае же 7-нм GA100 на заводах TSMC плотность выше – 65,37 MT/мм².

Подписывайтесь на группы Hardwareluxx ВКонтакте и Facebook, а также на наш канал в Telegram (@hardwareluxxrussia).

Создан молекулярный транзистор, способный контролировать движение отдельных электронов

Источники:

http://www.gizmag.com/single-molecule-transistor/38476/

http://www.dailytechinfo.org/nanotech/7214-sozdan-molekulyarnyy-tranzist…

Группе исследователей из Германии, Японии и США удалось создать крошечный транзистор, собранный из единственной молекулы и десятка дополнительных атомов различных химических элементов. Чувствительность этого транзистора столь высока, что он может управлять потоком, состоящим из единичных электронов, и такая способность молекулярного транзистора открывает путь к разработке нового поколения различных наноматериалов и сверхминиатюризированной электроники.

Практически вся используемая людьми электроника состоит из крошечных “выключателей”, транзисторов, и для того, чтобы современные цифровые электронные устройства продолжали становиться все быстрее и экономичней, требуется уменьшение габаритных размеров транзисторов. Однако, размер кремниевых транзисторов невозможно сокращать до бесконечности. Диаметр одного атома кремния равен приблизительно половине нанометра, а в современных кремниевых транзисторах их электроды разделяет расстояние, равное диаметру 30 атомов. Но как только эти расстояния начнут исчисляться единицами атомов, транзисторы потеряют свою работоспособность поскольку электроны начнут самопроизвольно перемещаться между электродами за счет эффекта квантового туннелирования.

Крошечные молекулярные транзисторы, созданные учеными, имеют намного меньшие размеры, нежели размеры транзисторов в процессорах наших компьютеров. Однако, при создании первых образцов молекулярных транзисторов ученые столкнулись с весьма тяжелой задачей. Поскольку такие транзисторы имеют очень малые размеры их включенное или выключенное состояние определяется местоположением одного единственного электрона. И лишь недавно вышеупомянутой группе ученых удалось добиться реализации высокоточного управления состоянием молекулярного транзистора, который стал способен контролировать движение через него единственных электронов.

В отличие от кремниевых транзисторов, молекулярные транзисторы строятся постепенно, собирая атомы будущей молекулы один за другим при помощи химических методов. С первого взгляда такой процесс кажется невероятно сложным и трудоемким, однако все используемые технологии обеспечивают достаточно высокую точность сборки и повторяемость результатов. И на основе этих технологий достаточно несложно будет разработать полностью автоматизированный технологический процесс, при помощи которого можно будет производить крошечные молекулярные транзисторы в сколь угодно больших количествах.

Для создания молекулярного транзистора ученые использовали туннельный сканирующий микроскоп (scanning tunneling microscope, STM). Заготовкой для будущего транзистора стал крошечный кристалл арсенида индия, на который в соответствующих местах были помещены 12 атомов индия, образовавших шестиугольную структуру. А “ядром” транзистора стала молекула фталоцианина, помещенная в центр шестиугольной структуры из атомов индия.

Центральная молекула очень слабо связана с поверхностью кристалла арсенида индия. Когда ученые подвели наконечник микроскопа к молекуле на определенное расстояние и подали на него электрический потенциал, то отдельные электроны начали “туннелироваться” с наконечника через молекулу на поверхность кристалла. Положительно заряженные ионы, окружающие молекулу, действуют как управляющий электрод, затвор транзистора, регулируя поток электронов, перемещающихся с наконечника микроскопа на кристалл.

Контролируя работу молекулярного транзистора, ученые заметили весьма необычный эффект. Оказывается, что центральная молекула не находится в статичном состоянии, она ориентируется в различных направлениях в зависимости от ее электрического заряда и положение молекулы имеет сильное влияние на поток электронов, протекающий через структуру молекулярного транзистора.

В настоящее время ученые исследуют работу созданного ими транзистора с целью лучшего понимания всех явлений, происходящих в процессе его работы. Если ученым удастся точно определить и описать математически зависимости проводимости транзистора от ориентации молекулы, то люди получат достаточно надежный метод регулирования электрического тока с невероятной точностью, с точностью до отдельных электронов. И это будет использовано для создания новых типов высокоэффективных полупроводников и наноматериалов, при помощи которых будут реализовываться технологии следующих поколений.

Переход на 2 нм и тонкости техпроцесса — android.mobile-review.com

9 мая 2021

Владимир Нимин

Вконтакте

Иан Катрис с AnandTech написал интересную заметку о новом первом в мире 2 нм процессоре от IBM. Вещь интересная, так что считаю полезным поделиться.

По материалам AnandTech

Каждое новое десятилетие проверяет на прочность пределы закона Мура, и это десятилетие ничем не отличается. Благодаря Extreme Ultra Violet (EUV) и другим технологическим улучшениям появилась возможность ещё больше уменьшить размер транзисторов.

Тут следует пояснить, что несмотря на то, что новость озаглавлена как «переход на технологический процесс производства 2 нм», это переход не в классическом понимании. Дело в том, что раньше уменьшение техпроцесса было эквивалентной метрикой для размера элемента на кристалле в 2D (в смысле, в двух измерениях, то есть на плоскости), например, так было с 90 нм, 65 нм и 40 нм. Однако с распространением технологии производства FinFETs и 3D-дизайна транзисторов произошло изменение, и теперь для простоты по-прежнему говорят «5-нанометровые транзисторы», но понимают как «пятинанометровые транзисторы в эквиваленте 2D-дизайна». По факту некоторые вспомогательные части транзисторов (например, ребра с изоляцией) могут быть «толще», чем 5 нм. Однако тут нанометровая метрика используется в контексте повышения плотности расположения транзисторов на плате. То есть транзисторы могут быть толще, но на плоскости их разместили так, что это количество соответствует заявленному техпроцессу.

В пресс-релизе говорится, что разработка IBM 2-нм техпроцессов улучшит производительность на 45% при той же мощности или приведет к 75% энергоэффективности при той же производительности по сравнению с современными 7-нм процессорами. IBM также подчеркивает, что компания была первой как при разработке 7 нм техпроцесса в 2015 году, так и 5 нм в 2017 году. При этом с 5 нм произошел переход с FinFET на технологии нанолистов, которые позволяют более точно настраивать характеристики напряжения отдельных транзисторов.

Таким образом, IBM заявляет, что, во-первых, она по-прежнему великая и инновационная компания, а, во-вторых, с помощью этой технологии можно разместить «50 миллиардов транзисторов на микросхеме размером с ноготь». Журналисты Anandtech первым делом обратились к IBM с просьбой разъяснить, что в компании понимают под размером ногтя, и получили ответ, что речь о площади 150 квадратных миллиметров. Таким образом, плотность транзисторов IBM составляет 333 миллиона транзисторов на квадратный миллиметр.

| Пиковая плотность транзисторов в миллионах транзисторов на квадратный миллиметр | ||||

| Размеры | IBM | TSMC | Intel | Samsung |

| 22нм | 16.5 | |||

| 16нм/14нм | 28.88 | 44.67 | 33.32 | |

| 10нм | 52.51 | 100.76 | 51.82 | |

| 7нм | 91.2 | 237.18 | 95.08 | |

| 5нм | 171.3 | |||

| 3нм | 292.21 | |||

| 2нм | 333.33 | |||

| Данные собраны из доступных открытых источников. У разных производителей понимание техпроцесса и плотности может отличаться. | ||||

Как видите, у разных производителей официальные названия техпроцессов обладают разной плотностью. Стоит отметить, что значения плотности часто указываются как пиковая плотность для компоновки транзисторов. Однако, например, самые быстрые части процессора могут обладать даже в 2 раза меньшей плотностью расположения транзисторов. Обычно это связано с вопросами температуры (то есть, по сути, им дают больше пространства, чтобы они в кучке не перегревались и не выходили из строя).

Судя по картинкам, IBM использует трехступенчатую технологию посадки транзисторов (Gate-All-Around — GAA). Samsung планирует использовать GAA при переходе на 3 нм, а TSMC хочет подождать до перехода на 2 нм. В свою очередь, Intel по ожиданиям аналитиков перейдет на GAA при производстве процессоров по техпроцессу 5 нм.

GAA в разрезе. То есть башенки транзисторов всё выше, но в 2D это рост количества транзисторов на одной площади.Трехступенчатая GAA башенка от IBM обладает высотой 75 нм и шириной 40 нм. Расстояние между блоками — 5 нм.

Если вас интересует, почему вообще IBM является первой компанией, разработавшей 2-нм техпроцесс, то ответ прост. Сегодня IBM обладает одним из ведущих мировых R&D (исследовательским центром) по полупроводниковым технологиям. Несмотря на отсутствие портфеля привычных коммерческих решений на продажу (как у Samsung или Qualcomm), IBM вместе с другими компаниями занята разработкой.

Также тут можно отметить, что IBM продала свое производство GlobalFoundries (это американская компания, занимающаяся производством полупроводниковых интегральных схем) с 10-летним партнерским соглашением еще в 2014 году. Ещё IBM в настоящее время работает с Samsung и недавно объявила о партнерстве с Intel. Несомненно, Intel и Samsung будут сотрудничать с IBM, так как обе компании разрабатывают собственные коммерческие чипсеты.

Кроме пресс-релиза, фотографию «вафли» (wafer – полупроводниковая пластина, на поверхности которой производится массив полупроводников и интегральных схем) и заявления, что продукт создали в исследовательской лаборатории в Олбани, пока что никакой подробной информации IBM не представила, так что можно предположить, что на текущий момент собрали лишь демо-образец с базовой логикой, демонстрирующий, что в целом всё работает.

Заключение

2 нм чипсеты или процессоры – это вещь, безусловно, интересная. Например, учитывая, что и текущую мощность чипсетов в смартфонах некуда девать, возможно, будут представлены новые энергоэффективные решения, которые при сохранении текущих показателей производительности будут на 75% экономичнее. А вот процессорам в ноутбуках больше пригодится прирост производительности.

Интересно, что получается, что IBM значительно обходит по времени остальных игроков рынка. Впрочем, TSMC говорит, что уже в следующем году перейдет на производство чипсетов и процессоров по технологии 4 нм и 3 нм.

Так как IBM в основном разрабатывает решения для собственных нужд, непонятно, когда будут представлены конкретные продукты. Хотя, учитывая сотрудничество с Intel и Samsung, наработки IBM могут опосредованно попасть на рынок. Ну и для полноты картины стоит отметить, что в этом году IBM планирует представить свой собственный 7-нм процессор, который будет использоваться в Power Systems (Power Systems – это линейка серверов от IBM, работающая на архитектуре POWER (RISC)).

Очевидно, что порядок вещей релиз IBM не изменит и на рынок 2 нм чипсеты раньше времени не попадут. Однако хорошо знать, что технологии развиваются, а нам как пользователям электроники есть чему радоваться и удивляться.

ученых сделали транзисторы меньше, чем мы думали

Ученым из Национальной лаборатории Лоуренса Беркли, Стэнфордского университета и Техасского университета в Далласе удалось построить затвор транзистора, длина которого составляет всего 1 нанометр. Их новый транзисторный затвор предлагает значительное улучшение по сравнению с существующими моделями и может значительно повысить скорость работы компьютеров. Их результаты опубликованы в статье в журнале Science .

Транзисторы – это строительные блоки каждого компьютера.Ученые и инженеры продолжают находить способы сделать их меньше, чтобы можно было разместить больше на одном кристалле. Чем больше транзисторов можно разместить на микросхеме, тем быстрее может работать компьютер.

Есть только одна проблема: мы почти достигли предела возможностей малых транзисторов. В настоящее время размер транзисторов составляет около 10-20 нанометров, и ожидается, что в ближайшие несколько лет они сократятся до 5-7 нанометров, но, похоже, это далеко не все. В этот момент транзисторы настолько малы, что квантовые эффекты мешают им работать должным образом.

Чтобы обойти эту проблему, группа исследователей разработала новый тип транзистора, используя другие материалы: дисульфид молибдена и углеродные нанотрубки вместо кремния. Эти новые материалы не имеют такого же минимального размера 5 нанометров, как у традиционных кремниевых транзисторов.

Хотя эта новая технология все еще находится на начальной стадии, она может предоставить компаниям способ обойти застойку миниатюризации, которая, согласно прогнозам, произойдет в 2021 году. Тем временем исследователи планируют провести дополнительную работу, чтобы сделать новые транзисторы более совершенными. эффективный и простой в производстве.

Источник: IEEE Spectrum

Этот контент создается и поддерживается третьей стороной и импортируется на эту страницу, чтобы помочь пользователям указать свои адреса электронной почты. Вы можете найти больше информации об этом и подобном контенте на сайте piano.io.

Существует предел тому, насколько маленькими мы можем сделать транзисторы, но решение – фотонные чипы – Quartz

В течение последних четырех десятилетий электронная промышленность руководствовалась так называемым «законом Мура», который является не законом, а чем-то большим. аксиома или наблюдение.Фактически, это предполагает, что электронные устройства удваиваются по скорости и возможностям примерно каждые два года. И действительно, каждый год технологические компании создают новые, более быстрые, умные и лучшие устройства.

В частности, закон Мура, сформулированный соучредителем Intel Гордоном Муром, гласит, что «количество транзисторов, встроенных в микросхему, будет примерно удваиваться каждые 24 месяца». Транзисторы – крошечные электрические переключатели – являются основным элементом, который управляет всеми электронными устройствами, о которых мы можем думать.По мере того, как они становятся меньше, они также становятся быстрее и потребляют меньше электроэнергии для работы.

В мире технологий один из самых больших вопросов 21 века: насколько маленькими мы можем сделать транзисторы? Если есть предел тому, насколько крошечными они могут быть, мы можем достичь точки, когда больше не сможем производить меньшие, более мощные и более эффективные устройства. Только в США это отрасль с годовым доходом более 200 миллиардов долларов. Может он перестанет расти?

Приближаясь к пределуВ настоящее время такие компании, как Intel, массово производят транзисторы диаметром 14 нанометров – всего в 14 раз шире, чем молекулы ДНК.Они сделаны из кремния, второго по распространенности материала на нашей планете. Размер атома кремния составляет около 0,2 нанометра.

Сегодняшние транзисторы имеют ширину около 70 атомов кремния, поэтому возможность сделать их еще меньше сокращается. Мы приближаемся к пределу того, насколько маленьким можно сделать транзистор.

В настоящее время транзисторы используют электрические сигналы – электроны, перемещающиеся из одного места в другое – для связи. Но если бы мы могли использовать свет, состоящий из фотонов, вместо электричества, мы могли бы сделать транзисторы еще быстрее.Моя работа по поиску способов интеграции обработки света с существующими чипами является частью этих зарождающихся усилий.

Помещение света внутрь микросхемыТранзистор состоит из трех частей; думайте о них как о частях цифрового фотоаппарата. Сначала информация поступает в линзу, аналогично транзисторному источнику. Затем он проходит по каналу от датчика изображения к проводам внутри камеры. И, наконец, информация хранится на карте памяти камеры, которая называется «стоком» транзистора – где информация в конечном итоге и попадает.

Прямо сейчас все это происходит за счет перемещения электронов. Чтобы заменить свет в качестве среды, нам на самом деле нужно вместо этого перемещать фотоны. Субатомные частицы, такие как электроны и фотоны, перемещаются в волновом движении, колеблясь вверх и вниз, даже когда они движутся в одном направлении. Длина каждой волны зависит от того, через что она проходит.

В кремнии наиболее эффективная длина волны фотонов составляет 1,3 микрометра. Это очень мало – человеческий волос составляет около 100 микрометров в поперечнике. Но электроны в кремнии еще меньше – с длинами волн от 50 до 1000 раз короче фотонов.

Это означает, что оборудование для обработки фотонов должно быть больше, чем устройства для обработки электронов, которые мы имеем сегодня. Может показаться, что это заставит нас строить транзисторы большего размера, а не меньшего размера.

Однако по двум причинам мы могли бы сохранить чипы того же размера и обеспечить большую вычислительную мощность, уменьшить чипы, обеспечивая при этом ту же мощность, или, возможно, и то, и другое. Во-первых, фотонному чипу требуется всего несколько источников света, генерирующих фотоны, которые затем можно направлять вокруг чипа с помощью очень маленьких линз и зеркал.

Во-вторых, свет намного быстрее электронов. В среднем фотоны могут перемещаться примерно в 20 раз быстрее, чем электроны в чипе. Это означает, что компьютеры будут в 20 раз быстрее, а при нынешних технологиях на это потребуется около 15 лет.

Ученые продемонстрировали прогресс в области фотонных чипов в последние годы. Ключевой задачей является обеспечение того, чтобы новые световые чипы могли работать со всеми существующими электронными чипами. Если мы сможем понять, как это сделать – или даже использовать световые транзисторы для улучшения электронных, – мы сможем увидеть значительное улучшение производительности.

Когда я смогу получить световой ноутбук или смартфон?Нам еще предстоит пройти долгий путь, прежде чем первое потребительское устройство выйдет на рынок, и прогресс требует времени. Первый транзистор был изготовлен в 1907 году с использованием электронных ламп, которые обычно имели высоту от одного до шести дюймов (в среднем 100 мм). К 1947 году был изобретен современный тип транзистора – тот, который сейчас имеет диаметр всего 14 нанометров, и он имел длину 40 микрометров (примерно в 3000 раз длиннее нынешнего).А в 1971 году первый коммерческий микропроцессор (двигатель любого электронного устройства) был в 1000 раз больше, чем сегодня, когда он был выпущен.

Огромные исследовательские усилия и последующая эволюция, наблюдаемая в электронной промышленности, только начинаются в фотонной промышленности. В результате современная электроника может выполнять гораздо более сложные задачи, чем лучшие современные фотонные устройства. Но по мере продвижения исследований возможности света будут догонять и в конечном итоге превосходить скорости электроники.Как бы долго мы ни добирались до этого, будущее фотоники безоблачно.

Изначально этот пост был опубликован на сайте The Conversation.

Новые 2-нм чипы IBM имеют транзисторы меньше, чем нить ДНК.

Яркий пример неумолимого развития технологий – компания IBM представила новые полупроводниковые чипы с самыми маленькими транзисторами из когда-либо созданных. Новая 2-нанометровая (нм) технология позволяет компании втиснуть 50 миллиардов транзисторов в микросхему размером с ноготь.

Текущим отраслевым стандартом являются микросхемы с 7-нм транзисторами, и некоторые высокопроизводительные потребительские устройства, такие как процессоры Apple M1, начинают переходить на 5-нм. А экспериментальные чипы уменьшились до 2,5 нм.

Новые микросхемы IBM объединяют их все, а ширина транзисторов теперь составляет всего 2 нм – для справки, это уже, чем нить человеческой ДНК. Это, конечно, означает, что крошечные транзисторы можно втиснуть в микросхему гораздо плотнее, чем когда-либо прежде, увеличивая вычислительную мощность устройства и повышая энергоэффективность процесса.Компания утверждает, что по сравнению с текущими 7-нм чипами новые 2-нм чипы могут обеспечить на 45 процентов более высокую производительность или на 75 процентов более низкое энергопотребление.

На практике IBM заявляет, что эта технология может повысить производительность всего: от бытовой электроники до распознавания объектов ИИ и времени реакции автономных транспортных средств. Или его экономия энергии может уменьшить значительный углеродный след центров обработки данных или сделать батареи для смартфонов, которые работают четыре дня без подзарядки.

Крупный план 2-нм кремниевой пластины, содержащей сотни отдельных микросхемIBM

Транзисторы часто используются для определения технического прогресса – закон Мура гласит, что количество транзисторов на кристалле будет удваиваться каждые два года или около того. Хотя это более или менее верно с тех пор, как оно было предложено в 1960-х годах, в последние годы эта скорость несколько замедлилась.

Прошло почти четыре года с тех пор, как IBM представила свои 5-нм микросхемы с 30 миллиардами транзисторов – если следовать закону Мура до Т, мы опоздаем на два года и 10 миллиардов транзисторов не хватит.Фактически, IBM только сейчас удваивает количество транзисторов в своих первых 7-нм чипах, представленных в 2015 году.

Изображение с помощью сканирующего электронного микроскопа отдельных транзисторов на новом чипе IBM, каждый из которых имеет ширину 2 нанометра – уже, чем нить человеческой ДНКIBM

Тем не менее, мы не должны преуменьшать значение новой разработки – 2 нм – это настоящий инженерный подвиг. Еще в 2019 году инженеры выразили опасения, что технологии не позволят добиться значительного прогресса при размере меньше 3 нм.Исследования, проведенные многими компаниями за последние несколько лет, развеяли эти опасения.

Вполне вероятно, что мы не увидим эти 2-нм чипы в потребительской электронике не раньше 2023 года, так что пока пользуйтесь преимуществами все еще впечатляющих 5-нм чипов.

IBM обсуждает новый технологический прорыв в видео ниже.

IBM представляет первую в мире технологию чипов с 2 нанометрами

Источник: IBM

Самый маленький в мире транзистор имеет длину 1 нм, будь к черту физика

Размер транзистора – важная часть совершенствования компьютерных технологий.Чем меньше у вас транзисторы, тем больше вы можете уместить на микросхеме и тем быстрее и эффективнее может быть ваш процессор. Вот почему это такая большая новость, что команда из Национальной лаборатории Лоуренса Беркли успешно построила функциональный транзисторный затвор длиной 1 нанометр, который, по утверждению лаборатории, является самым маленьким работающим транзистором из когда-либо созданных.

В течение многих лет компьютерная индустрия регулируется законом Мура, который гласит, что количество транзисторов в полупроводниковой схеме удваивается каждые два года.В технологиях нынешнего поколения используется технология шкалы 14 нм, а выпуск полупроводников 10 нм ожидается в 2017 или 2018 годах с такими продуктами, как линейка Intel Cannonlake.

Заглядывая в будущее, закон Мура начинает вызывать проблемы

Но если смотреть в будущее, закон Мура начинает сталкиваться с проблемами. И под проблемой я имею в виду законы физики. Видите ли, хотя 7-нанометровый узел технически возможно изготавливать из кремния, после этого вы сталкиваетесь с проблемами, когда кремниевые транзисторы размером менее 7 нм становятся настолько физически близкими друг к другу, что электроны испытывают квантовое туннелирование.Таким образом, вместо того, чтобы оставаться в намеченном логическом элементе, электроны могут непрерывно перетекать от одного затвора к другому, что по существу делает невозможным для транзисторов состояние выключения.

Суджай Десаи / Калифорнийский университет в Беркли

И хотя такие компании, как Intel, первоначально заявили, что будут изучать другие материалы для производства 7-нм полупроводников и не только, исследовательская группа Berkeley Lab опередила их, используя углеродные нанотрубки и дисульфид молибдена (MoS 2 ) для создания полупроводниковых материалов. суб-7нм транзистор.MoS 2 функционирует как полупроводник, а полая углеродная нанотрубка действует как затвор для управления потоком электронов.

Исследования здесь все еще находятся на очень ранней стадии

Тем не менее, исследования здесь все еще находятся на очень ранней стадии. На 14-нм кристалле находится более миллиарда транзисторов, и команде Berkley Lab еще предстоит разработать жизнеспособный метод массового производства новых 1-нм транзисторов или даже разработать микросхему, использующую их. Но только как доказательство концепции, результаты здесь по-прежнему важны – новые материалы могут по-прежнему позволять использовать транзисторы меньшего размера, а вместе с тем увеличивать мощность и эффективность компьютеров будущего.

Достигнуторазмеров затвора в один нанометр для транзисторов

Этот танец называется динамическое масштабирование напряжения и частоты (DVFS) постоянно происходит в процессоре, называемом системой на кристалле (SoC), который управляет вашим телефоном и вашим ноутбуком, а также на серверах, которые их поддерживают. Все это делается для того, чтобы сбалансировать вычислительную производительность и энергопотребление, что особенно сложно для смартфонов. Цепи, которые управляют DVFS, стремятся обеспечить стабильные часы и стабильный уровень напряжения, несмотря на скачки тока, но они также являются одними из самых непростых в проектировании.