Триггеры. Симметричный триггер на биполярных транзисторах. RS-триггеры на логических элементах, страница 2

Электротехника \ Электроника

Состояние триггера называют единичным, если на прямом выходе имеется уровень напряжения, соответствующий логической единице, а на инверсном — логическому нулю, т.е. при , .

Вход, на который подается сигнал, устанавливающий триггер в состояние 1, обозначают буквой S. Вход, на который поступает сигнал, устанавливающий триггер в состояние 0 (, ), обозначают R (от англ. set — установка и reset — сброс). Такой триггер с раздельным запуском получил название RS-триггера.

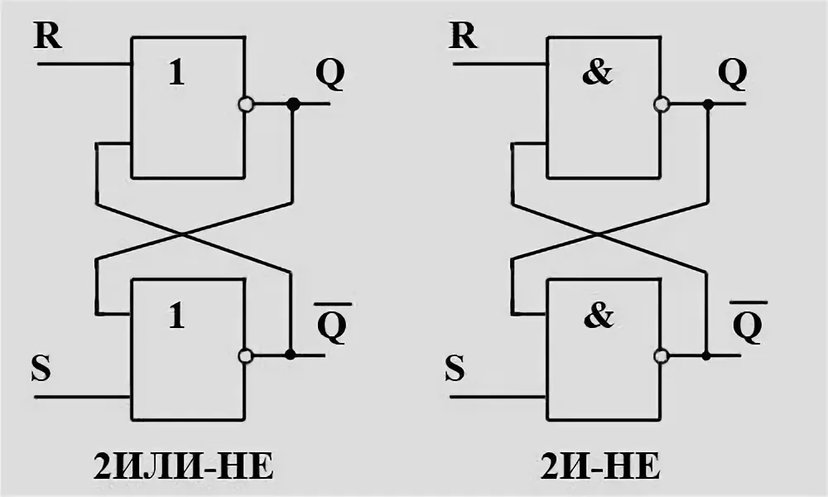

6.3. RS-триггеры на логических элементах. Асинхронные RS-триггеры являются простейшими и выполняются на двух двухвходовых логических элементах типа И — НЕ либо ИЛИ — НЕ.

Асинхронные RS-триггеры

на ЛЭ ИЛИ — НЕ. Асинхронный RS-триггер

на двух логических элементах ИЛИ — НЕ (рис. 6.3, а) содержит два информационных

входа и ,

на которых возможны четыре комбинации логических сигналов: ; ;

и .

Рис.6.3. Схема (а) и условное обозначение (б) асинхронного RS-триггера

на ЛЭ ИЛИ – НЕ с прямым управлением

Этим комбинациям соответствуют определенные сигналы на выходах триггера и , что отображается таблицей состояний триггера (табл. 6.2). В ней приняты следующие обозначения: и – моменты времени до и после срабатывания триггера; и – сигналы на информационных входах в момент ; и – сигналы на прямом выходе в моменты времени и .

На основании таблицы состояний и карты Карно можно получить выражение для логической (переключательной) функции для RS-триггера с прямым входом, которая имеет вид:

(6.1)

Таблица 6.2. Состояния -триггера с прямым управлением

0 | 0 | |

1 | 0 | 1 |

0 | 1 | 0 |

1 | 1 | x |

Из таблицы состояний и выражения (6.

Комбинация входных сигналов переводит RS-триггер в единичное состояние: , , если он перед этим находился в нулевом состоянии (, ). Если же RS-триггер в момент времени находился в единичном состоянии (,), то данная комбинация подтверждает это состояние (, ). Поэтому вход называют единичным входом.

Комбинация входных сигналов обеспечивает

нулевое состояние триггера. Действительно, если , , то при поступлении сигналов и на

одном входе верхнего ЛЭ появится логическая 1. Это вызовет появление на его

выходе логического 0 (), и на обоих входах

нижнего ЛЭ будут логические нули, а на его выходе —

логическая единица. Если же триггер находился в нулевом состоянии (, ), то комбинация входных сигналов состояние триггера не изменит, так

как на обоих входах верхнего ЛЭ будут логические единицы, а нижнего ЛЭ —

логические нули, подтверждающие выходные сигналы , . По этой причине вход называют нулевым входом.

Действительно, если , , то при поступлении сигналов и на

одном входе верхнего ЛЭ появится логическая 1. Это вызовет появление на его

выходе логического 0 (), и на обоих входах

нижнего ЛЭ будут логические нули, а на его выходе —

логическая единица. Если же триггер находился в нулевом состоянии (, ), то комбинация входных сигналов состояние триггера не изменит, так

как на обоих входах верхнего ЛЭ будут логические единицы, а нижнего ЛЭ —

логические нули, подтверждающие выходные сигналы , . По этой причине вход называют нулевым входом.

При комбинации входных сигналов на обоих выходах триггера появятся логические нули (, ). Если вслед за этим последует нейтральная комбинация входных сигналов (), то триггер с равной вероятностью примет единичное или нулевое состояние. Поэтому комбинацию входных сигналов для рассматриваемого RS-триггера называют

В рассмотренном триггере переключение состояний

осуществляется единичными сигналами. Такой триггер называют триггером с прямым

управлением и обозначают так, как показано на рис. 6.3, б.

Такой триггер называют триггером с прямым

управлением и обозначают так, как показано на рис. 6.3, б.

Асинхронные RS-триггеры на ЛЭ И — НЕ. Асинхронный RS-триггер можно выполнить и на двух двухвходовых ЛЭ И —НЕ (рис. 6.4, а).

Рис. 6.4. Схема (а) и условное обозначение (б) асинхронного RS-триггера на логических элементах И — НЕ с инверсным управлением

В отличие от RS-триггера на ЛЭ ИЛИ — НЕ переключения данного триггера осуществляются сигналами логического 0. Такой триггер называют триггером с инверсным управлением (-триггер). На функциональных схемах переключающие входы -триггера снабжаются индикаторами инверсии, а к буквенным обозначениям входов добавляются знаки отрицания (рис. 6.4, б). Состояния триггера в зависимости от комбинаций входных сигналов приведены в табл.6.3, а его логическая (переключательная) функция имеет вид:

(6. 2)

2)

Таблица 6.3. Состояния -триггера с инверсным управлением

0 | x | |

0 | 1 | 1 |

1 | 0 | 0 |

1 | 1 | |

Из таблицы состояний (6. 3) и выражения (6.2) следует,

что комбинация входных сигналов является нейтральной,

а — запрещенной.

3) и выражения (6.2) следует,

что комбинация входных сигналов является нейтральной,

а — запрещенной.

Если ко входам -триггера добавить два инвертора (рис. 6.4, в), то получится -триггер, подобный триггеру на элементах ИЛИ — НЕ. Асинхронные -триггеры используются в качестве ячеек памяти в оперативных запоминающих устройствах (ОЗУ) статического типа (например, ИМС К155РУ1).

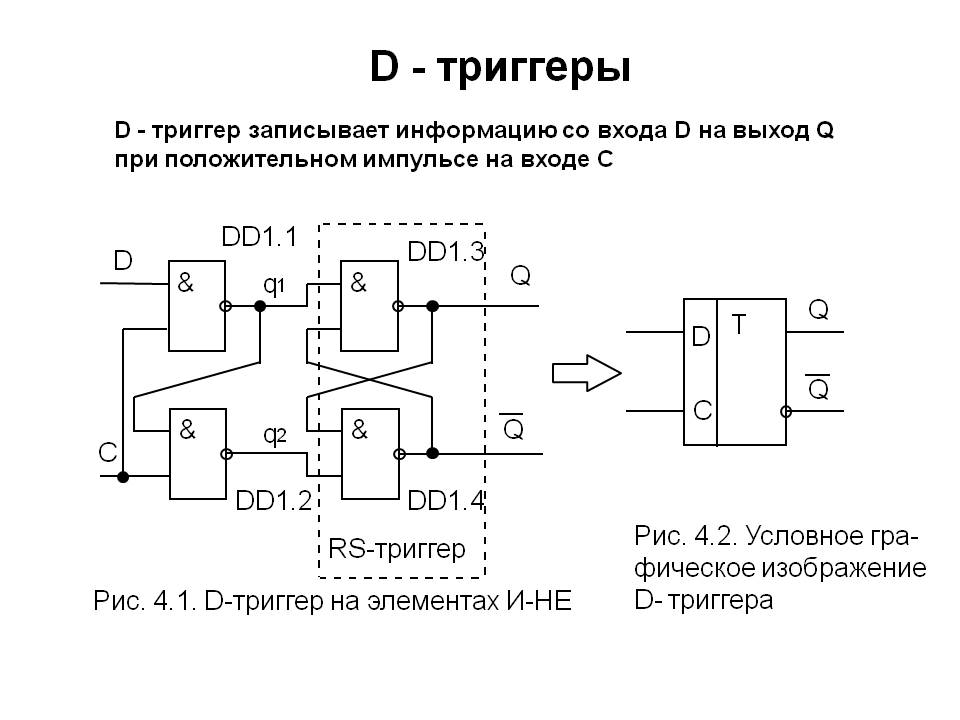

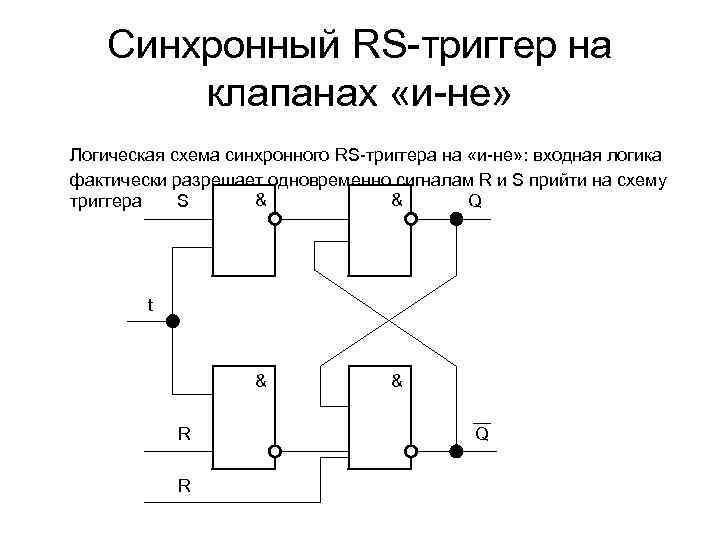

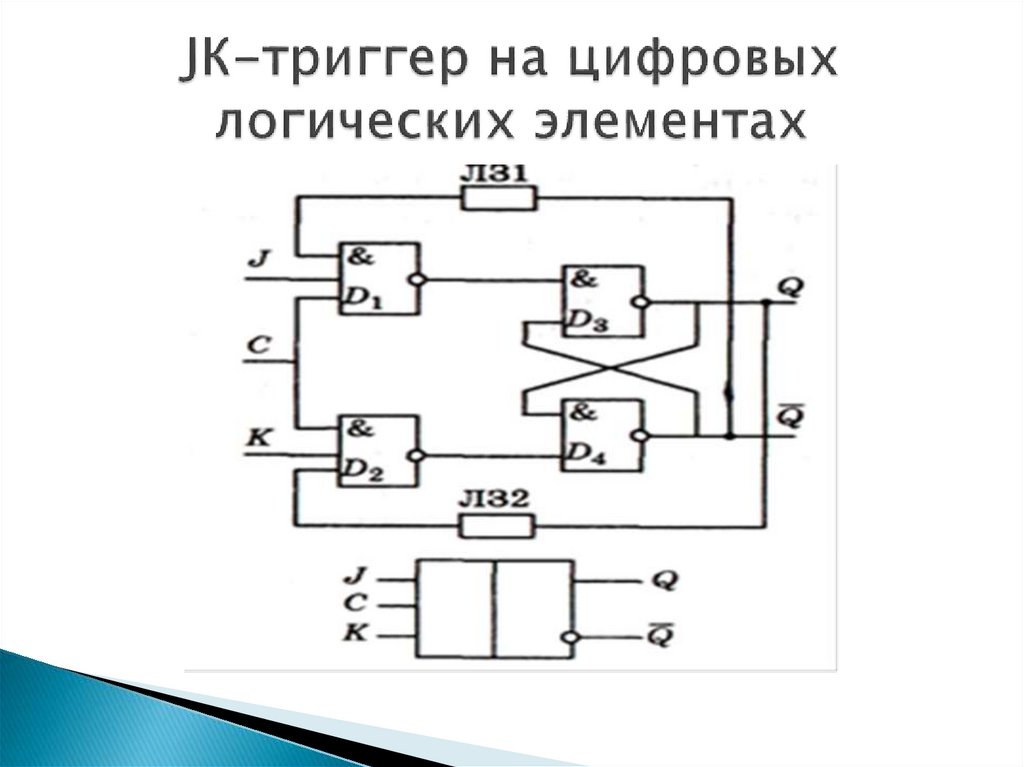

Синхронные -триггеры на ЛЭ И — НЕ. На рис. 6.5, а приведена структурная схема синхронного -триггера со статическим управлением на ЛЭ И — НЕ. Собственно триггер выполнен на элементах и , а элементы и образуют устройство управления. Кроме информационных входов и , устройство управления имеет синхронизирующий, или тактовый, вход , связанный с входами и операциями И — НЕ. Поэтому информация с входов и передается на собственно триггер только при .

Рис. 6.5. Схема (а) и условные обозначения (б, в) синхронного -триггера на логических элементах И -НЕ

Собственно триггер управляется внутренними сигналами и . Переключения осуществляются нулевыми уровнями этих сигналов так же, как в

триггере на рис. 6.4, а. Так как ЛЭ и осуществляют инверсию входных сигналов

и ,

то нулевым уровням сигналов и должны соответствовать единичные

уровни внешних информационных сигналов и

. Работа триггера определяется

таблицей состояний (6.4) и его логической (переключательной) функцией:

Переключения осуществляются нулевыми уровнями этих сигналов так же, как в

триггере на рис. 6.4, а. Так как ЛЭ и осуществляют инверсию входных сигналов

и ,

то нулевым уровням сигналов и должны соответствовать единичные

уровни внешних информационных сигналов и

. Работа триггера определяется

таблицей состояний (6.4) и его логической (переключательной) функцией:

(6.3)

Рассмотрим работу синхронного -триггера,

приняв . Если ,

то ЛЭ и закрыты

и . Такая комбинация внутренних

сигналов и является

нейтральной для собственно триггера, и он сохраняет свое состояние . Это состояние не изменяется при

любых значениях информационных сигналов и

. С приходом синхронизирующего

импульса () на входах ЛЭ будет действовать логическая 1,

вследствие чего и .

Так как (поскольку и

), то на входы ЛЭ поступят сигналы и и

на его выходе будет сигнал . Такое состояние

будет сохраняться и после прекращения действия синхронизирующего импульса, так

как при для собственно триггера опять

возникнет нейтральная комбинация .

Скачать файл

Выбери свой ВУЗ

- АлтГТУ 419

- АлтГУ 113

- АмПГУ 296

- АГТУ 267

- БИТТУ 794

- БГТУ «Военмех» 1191

- БГМУ 172

- БГТУ 603

- БГУ 155

- БГУИР 391

- БелГУТ 4908

- БГЭУ 963

- БНТУ 1070

- БТЭУ ПК 689

- БрГУ 179

- ВНТУ 120

- ВГУЭС 426

- ВлГУ 645

- ВолгГТУ 235

- ВНУ им. Даля 166

- ВЗФЭИ 245

- ВятГСХА 101

- ВятГГУ 139

- ВятГУ 559

- ГГДСК 171

- ГомГМК 501

- ГГМУ 1966

- ГГТУ им.

Сухого 4467

Сухого 4467 - ГГУ им. Скорины 1590

- ГМА им. Макарова 299

- ДГПУ 159

- ДальГАУ 279

- ДВГГУ 134

- ДВГМУ 408

- ДВГТУ 936

- ДВГУПС 305

- ДВФУ 949

- ДонГТУ 498

- ДИТМ МНТУ 109

- ИвГМА 488

- ИГХТУ 131

- ИжГТУ 145

- КемГППК 171

- КемГУ 508

- КГМТУ 270

- КировАТ 147

- КГКСЭП 407

- КГТА им.

Дегтярева 174

Дегтярева 174 - КнАГТУ 2910

- КрасГАУ 345

- КрасГМУ 629

- КГПУ им. Астафьева 133

- КГТУ (СФУ) 567

- КГТЭИ (СФУ) 112

- КПК №2 177

- КубГТУ 138

- КубГУ 109

- КузГПА 182

- КузГТУ 789

- МГТУ им. Носова 369

- МГЭУ им. Сахарова 232

- МГЭК 249

- МГПУ 165

- МАИ 144

- МАДИ 151

- МГИУ 1179

- МГОУ 121

- МГСУ 331

- МГУ 273

- МГУКИ 101

- МГУПИ 225

- МГУПС (МИИТ) 637

- МГУТУ 122

- МТУСИ 179

- ХАИ 656

- ТПУ 455

- НИУ МЭИ 640

- НМСУ «Горный» 1701

- ХПИ 1534

- НТУУ «КПИ» 213

- НУК им.

Макарова 543

Макарова 543 - НВ 1001

- НГАВТ 362

- НГАУ 411

- НГАСУ 817

- НГМУ 665

- НГПУ 214

- НГТУ 4610

- НГУ 1993

- НГУЭУ 499

- НИИ 201

- ОмГТУ 302

- ОмГУПС 230

- СПбПК №4 115

- ПГУПС 2489

- ПГПУ им. Короленко 296

- ПНТУ им. Кондратюка 120

- РАНХиГС 190

- РОАТ МИИТ 608

- РТА 245

- РГГМУ 117

- РГПУ им.

Герцена 123

Герцена 123 - РГППУ 142

- РГСУ 162

- «МАТИ» — РГТУ 121

- РГУНиГ 260

- РЭУ им. Плеханова 123

- РГАТУ им. Соловьёва 219

- РязГМУ 125

- РГРТУ 666

- СамГТУ 131

- СПбГАСУ 315

- ИНЖЭКОН 328

- СПбГИПСР 136

- СПбГЛТУ им. Кирова 227

- СПбГМТУ 143

- СПбГПМУ 146

- СПбГПУ 1599

- СПбГТИ (ТУ) 293

- СПбГТУРП 236

- СПбГУ 578

- ГУАП 524

- СПбГУНиПТ 291

- СПбГУПТД 438

- СПбГУСЭ 226

- СПбГУТ 194

- СПГУТД 151

- СПбГУЭФ 145

- СПбГЭТУ «ЛЭТИ» 379

- ПИМаш 247

- НИУ ИТМО 531

- СГТУ им.

Гагарина 114

Гагарина 114 - СахГУ 278

- СЗТУ 484

- СибАГС 249

- СибГАУ 462

- СибГИУ 1654

- СибГТУ 946

- СГУПС 1473

- СибГУТИ 2083

- СибУПК 377

- СФУ 2424

- СНАУ 567

- СумГУ 768

- ТРТУ 149

- ТОГУ 551

- ТГЭУ 325

- ТГУ (Томск) 276

- ТГПУ 181

- ТулГУ 553

- УкрГАЖТ 234

- УлГТУ 536

- УИПКПРО 123

- УрГПУ 195

- УГТУ-УПИ 758

- УГНТУ 570

- УГТУ 134

- ХГАЭП 138

- ХГАФК 110

- ХНАГХ 407

- ХНУВД 512

- ХНУ им.

Каразина 305

Каразина 305 - ХНУРЭ 325

- ХНЭУ 495

- ЦПУ 157

- ЧитГУ 220

- ЮУрГУ 309

ОглавлениеПРЕДИСЛОВИЕВВЕДЕНИЕ ГЛАВА 1. ПАССИВНЫЕ КОМПОНЕНТЫ ЭЛЕКТРОННЫХ УСТРОЙСТВ § 1.1. РЕЗИСТОРЫ Основные параметры резисторов § 1.2. КОНДЕНСАТОРЫ Основные параметры постоянных конденсаторов 1.3. КАТУШКИ ИНДУКТИВНОСТИ Основные параметры катушки индуктивности (ГОСТ 20718—75) § 1.4. ТРАНСФОРМАТОРЫ ЭЛЕКТРОННОЙ АППАРАТУРЫ Основные параметры трансформаторов питания ГЛАВА 2. ПОЛУПРОВОДНИКОВЫЕ КОМПОНЕНТЫ ЭЛЕКТРОННЫХ ЦЕПЕЙ § 2.1. ЭЛЕКТРОПРОВОДНОСТЬ ПОЛУПРОВОДНИКОВ Основные положения теории электропроводности. Примесная электропроводность.  § 2.2. ОСНОВНЫЕ СВОЙСТВА И ХАРАКТЕРИСТИКИ ПОЛУПРОВОДНИКОВ Концентрация носителей зарядов. Уравнения непрерывности. § 2.3. ЭЛЕКТРИЧЕСКИЕ ПЕРЕХОДЫ Контакт металл — полупроводник. Контакт двух полупроводников p- и n-типов. Свойства несимметричного p-n-перехода. p-n-переход смещен в прямом направлении Переход, смещенный в обратном направлении. Переходы p-i, n-i-, p+-p-, n+-n-типов. 2.4. ОСОБЕННОСТИ РЕАЛЬНЫХ p-n-ПЕРЕХОДОВ Пробой p-n-перехода. § 2.5. ОСНОВНЫЕ ТЕХНОЛОГИЧЕСКИЕ ПРОЦЕССЫ, ИСПОЛЬЗУЕМЫЕ ПРИ ИЗГОТОВЛЕНИИ ПОЛУПРОВОДНИКОВЫХ ПРИБОРОВ И ИНТЕГРАЛЬНЫХ МИКРОСХЕМ § 2.6. ПОЛУПРОВОДНИКОВЫЕ ДИОДЫ Выпрямительные диоды. Основные параметры выпрямительных диодов и их значения у маломощных диодов Импульсные диоды. Полупроводниковые стабилитроны. Варикапы. Диоды других типов. § 2.7. БИПОЛЯРНЫЕ ТРАНЗИСТОРЫ Математическая модель транзистора. Три схемы включения транзистора. Инерционные свойства транзистора.  Шумы транзистора. Н-параметры транзисторов. § 2.8. БИПОЛЯРНЫЕ ТРАНЗИСТОРЫ С ИНЖЕКЦИОННЫМ ПИТАНИЕМ § 2.9. ТИРИСТОРЫ Симметричные тиристоры. Основные параметры тиристоров и их ориентировочные значения § 2.10. ПОЛЕВЫЕ ТРАНЗИСТОРЫ Основные параметры полевых транзисторов и их ориентировочные значения § 2.11. ОСОБЕННОСТИ КОМПОНЕНТОВ ЭЛЕКТРОННЫХ ЦЕПЕЙ В МИКРОМИНИАТЮРНОМ ИСПОЛНЕНИИ Пассивные компоненты ИС. Конденсаторы. Индуктивности. Транзисторы ИС. Изоляция компонентов в монолитных интегральных узлах. ГЛАВА 3. КОМПОНЕНТЫ ОПТОЭЛЕКТРОНИКИ И ТЕХНИЧЕСКИЕ СРЕДСТВА ОТОБРАЖЕНИЯ ИНФОРМАЦИИ § 3.1. ОБЩИЕ СВЕДЕНИЯ О КОМПОНЕНТАХ ОПТОЭЛЕКТРОНИКИ § 3.2. УПРАВЛЯЕМЫЕ ИСТОЧНИКИ СВЕТА Основные параметры и характеристики светодиодов § 3.3. ФОТОПРИЕМНИКИ Основные характеристики и параметры фоторезистора Фотодиоды. Основные характеристики и параметры фотодиода Фототранзисторы. Основные характеристики и параметры фототранзистора Фототиристоры.  Многоэлементные фотоприемники. Фотоприемники с внешним фотоэффектом. § 3.4. СВЕТОВОДЫ И ПРОСТЕЙШИЕ ОПТРОНЫ § 3 5. ОБЩИЕ СВЕДЕНИЯ О КОМПОНЕНТАХ УСТРОЙСТВ ОТОБРАЖЕНИЯ ИНФОРМАЦИИ § 3.6. ЖИДКОКРИСТАЛЛИЧЕСКИЕ ПРИБОРЫ ДЛЯ ОТОБРАЖЕНИЯ ИНФОРМАЦИИ § 3.7. ГАЗОНАПОЛНЕННЫЕ ПРИБОРЫ ДЛЯ ОТОБРАЖЕНИЯ ИНФОРМАЦИИ Основные параметры газонаполненных матричных панелей неременного тока § 3.8. ВАКУУМНЫЕ ПРИБОРЫ ДЛЯ ОТОБРАЖЕНИЯ ИНФОРМАЦИИ § 3.9. ПОЛУПРОВОДНИКОВЫЕ И ЭЛЕКТРОЛЮМИНЕСЦЕНТНЫЕ ПРИБОРЫ ДЛЯ ОТОБРАЖЕНИЯ ИНФОРМАЦИИ ГЛАВА 4. УСИЛИТЕЛИ ЭЛЕКТРИЧЕСКИХ СИГНАЛОВ § 4.1. ОБЩИЕ СВЕДЕНИЯ ОБ УСИЛИТЕЛЯХ ЭЛЕКТРИЧЕСКИХ СИГНАЛОВ, ИХ ОСНОВНЫХ ПАРАМЕТРАХ И ХАРАКТЕРИСТИКАХ § 4.2. ОСНОВНЫЕ ПОЛОЖЕНИЯ ТЕОРИИ ОБРАТНОЙ СВЯЗИ ПРИМЕНИТЕЛЬНО К УСИЛИТЕЛЯМ § 4.3. СТАТИЧЕСКИЙ РЕЖИМ РАБОТЫ УСИЛИТЕЛЬНЫХ КАСКАДОВ § 4.4. УСИЛИТЕЛЬНЫЕ КАСКАДЫ НА ПОЛЕВЫХ ТРАНЗИСТОРАХ Каскад с общим стоком. § 4.5. УСИЛИТЕЛЬНЫЙ КАСКАД НА БИПОЛЯРНОМ ТРАНЗИСТОРЕ С ОБЩИМ ЭМИТТЕРОМ Входное сопротивление.  § 4.6. УСИЛИТЕЛЬНЫЙ КАСКАД НА БИПОЛЯРНОМ ТРАНЗИСТОРЕ С ОБЩЕЙ БАЗОЙ § 4.7. УСИЛИТЕЛЬНЫЙ КАСКАД НА БИПОЛЯРНОМ ТРАНЗИСТОРЕ С ОБЩИМ КОЛЛЕКТОРОМ Сложные эмиттерные повторители. § 4.8. ДИФФЕРЕНЦИАЛЬНЫЕ УСИЛИТЕЛЬНЫЕ КАСКАДЫ § 4.9. УСИЛИТЕЛЬНЫЕ КАСКАДЫ С ДИНАМИЧЕСКОЙ НАГРУЗКОЙ И С КАСКОДНЫМ ВКЛЮЧЕНИЕМ ТРАНЗИСТОРОВ § 4.10. УПРАВЛЯЕМЫЕ ИСТОЧНИКИ ТОКА И УСИЛИТЕЛЬНЫЕ КАСКАДЫ НА ИХ ОСНОВЕ 4.11. УСИЛИТЕЛЬНЫЕ КАСКАДЫ С ТРАНСФОРМАТОРНОЙ СВЯЗЬЮ 4.12. МОЩНЫЕ УСИЛИТЕЛЬНЫЕ КАСКАДЫ Каскад с ОБ трансформаторным входом и трансформаторным выходом. Двухтактные выходные каскады. § 4.13. БЕСТРАНСФОРМАТОРНЫЕ МОЩНЫЕ ВЫХОДНЫЕ КАСКАДЫ ГЛАВА 5. МНОГОКАСКАДНЫЕ УСИЛИТЕЛИ § 5.1. МНОГОКАСКАДНЫЕ УСИЛИТЕЛИ Параметры RC-цепи связи. § 5.2. УСИЛИТЕЛИ В ИНТЕГРАЛЬНОМ ИСПОЛНЕНИИ 5.3. ОПЕРАЦИОННЫЕ УСИЛИТЕЛИ § 5.4. ПАРАМЕТРЫ И ХАРАКТЕРИСТИКИ ОПЕРАЦИОННЫХ УСИЛИТЕЛЕЙ § 5.5. ОПЕРАЦИОННЫЕ УСИЛИТЕЛИ С УЛУЧШЕННЫМИ ХАРАКТЕРИСТИКАМИ § 5.6. ОСОБЕННОСТИ ВКЛЮЧЕНИЯ И СВОЙСТВА ОПЕРАЦИОННЫХ УСИЛИТЕЛЕЙ, ОХВАЧЕННЫХ ОБРАТНОЙ СВЯЗЬЮ § 5.  7. УСТОЙЧИВОСТЬ УСИЛИТЕЛЕЙ И КОРРЕКЦИЯ ИХ ХАРАКТЕРИСТИК 7. УСТОЙЧИВОСТЬ УСИЛИТЕЛЕЙ И КОРРЕКЦИЯ ИХ ХАРАКТЕРИСТИКГЛАВА 6. АНАЛОГОВЫЕ ПРЕОБРАЗОВАТЕЛИ ЭЛЕКТРИЧЕСКИХ СИГНАЛОВ § 6.1. МАСШТАБНЫЕ УСИЛИТЕЛИ 6.2. ЛИНЕЙНЫЕ ПРЕОБРАЗОВАТЕЛИ ЭЛЕКТРИЧЕСКИХ СИГНАЛОВ 6.3. ИНТЕГРИРУЮЩИЕ УСТРОЙСТВА Интеграторы на основе операционных усилителей. § 6.4. ДИФФЕРЕНЦИРУЮЩИЕ УСТРОЙСТВА Активные дифференцирующие устройства. § 6.5. АКТИВНЫЕ ФИЛЬТРЫ § 6.6. МАГНИТОЭЛЕКТРОННЫЕ ПРЕОБРАЗОВАТЕЛИ ЭЛЕКТРИЧЕСКИХ СИГНАЛОВ § 6.7. НЕЛИНЕЙНЫЕ ПРЕОБРАЗОВАТЕЛИ ЭЛЕКТРИЧЕСКИХ СИГНАЛОВ § 6.8. ПЕРЕМНОЖИТЕЛИ СИГНАЛОВ И УСТРОЙСТВА, ВЫПОЛНЯЮЩИЕ МАТЕМАТИЧЕСКИЕ ОПЕРАЦИИ § 6.9. ДЕТЕКТОРЫ ЭЛЕКТРИЧЕСКИХ СИГНАЛОВ ГЛАВА 7. ЭЛЕКТРОННЫЕ КЛЮЧИ § 7.1. ОБЩИЕ СВЕДЕНИЯ ОБ ИМПУЛЬСНЫХ ПРОЦЕССАХ И УСТРОЙСТВАХ § 7.2. ДИОДНЫЕ КЛЮЧИ § 7.3. КЛЮЧИ НА БИПОЛЯРНЫХ ТРАНЗИСТОРАХ § 7.4. ПЕРЕХОДНЫЕ ПРОЦЕССЫ В КЛЮЧЕВЫХ ЦЕПЯХ С БИПОЛЯРНЫМИ ТРАНЗИСТОРАМИ 7.5. КЛЮЧИ НА ПОЛЕВЫХ ТРАНЗИСТОРАХ § 7.6. ПЕРЕХОДНЫЕ ПРОЦЕССЫ В КЛЮЧАХ НА ПОЛЕВЫХ ТРАНЗИСТОРАХ ГЛАВА 8.  ЛОГИЧЕСКИЕ ЭЛЕМЕНТЫ, ТРИГГЕРЫ, АВТОГЕНЕРАТОРЫ ЛОГИЧЕСКИЕ ЭЛЕМЕНТЫ, ТРИГГЕРЫ, АВТОГЕНЕРАТОРЫ§ 8.1. ОБЩИЕ СВЕДЕНИЯ О ЛОГИЧЕСКИХ ЭЛЕМЕНТАХ § 8.2. ЛОГИЧЕСКИЕ ЭЛЕМЕНТЫ 8.3. ЛОГИЧЕСКИЕ ЭЛЕМЕНТЫ НА МОП-ТРАНЗИСТОРАХ § 8.4. ТРИГГЕРЫ § 8.5. НЕСИММЕТРИЧНЫЕ ТРИГГЕРЫ § 8.6. ГЕНЕРАТОРЫ КОЛЕБАНИЙ Генераторы напряжения прямоугольной формы. Генераторы линейно изменяющегося напряжения (ГЛИН). Генераторы напряжения треугольной формы. Генераторы синусоидальных колебаний. Генераторы LC-типа. Генераторы с кварцевыми резонаторами и электромеханическими резонансными системами. ЗАКЛЮЧЕНИЕ Приложение Схемы включения операционных усилителей ЛИТЕРАТУРА |

JK | Схема, таблица истинности, ограничения и использование

— Реклама —

JK Flip-flop — это улучшенная версия SR-триггера, в которой неопределенное состояние SR-триггера устраняется за счет обеспечения обратной связи. Давайте посмотрим на логическую схему триггера JK. Мы можем сделать триггеры JK, используя только вентили NAND. Но здесь мы взяли схему, в которой используются вентили И и ИЛИ, точно так же, как мы обсуждали в SR-триггере.

Давайте посмотрим на логическую схему триггера JK. Мы можем сделать триггеры JK, используя только вентили NAND. Но здесь мы взяли схему, в которой используются вентили И и ИЛИ, точно так же, как мы обсуждали в SR-триггере.

Читайте также: Все, что вам нужно знать о триггере

JK Flip-Flop РаботаДавайте рассмотрим возможные случаи и запишем их в нашу таблицу истинности. На часах всегда 1.

– Реклама –

Случай 1: J=0, K=0

Gate1 = 0, Gate2 = 0, Gate3/Q(n+1) = Q, Gate4/Q(n+1)’ = Q’

Примечание.

- Поскольку один вход вентилей1 и вентиль2 равен 0, а оба вентиля являются вентилями И, выход обоих вентилей будет равен 0 независимо от других входов.

- Gate3 = (0+Q’)’ = (Q’)’ = Q

- Gate4 = (0+Q)’ = (Q)’ = Q’

Случай 2: J=0, K=1

Gate1 = Q, Gate2 = 0, Gate3/Q(n+1) = 0, Gate4/Q(n+1)’ = 1

Примечание :

- Поскольку оба входа Gate1 равны 1, а Gate1 является логическим элементом И, выход Gate1 будет равен третьему входу.

- Поскольку один вход вентиля 2 равен 0, а вентиль 2 является логическим элементом И, выходной вентиль 2 будет равен 0 независимо от других входов.

- Gate3 = (Q+Q’)’ = 1’ = 0

Случай 3: J=1, K=0

Gate1 = 0, Gate2 = Q’, Gate4/Q(n+1)’ = 0, Gate3/Q(n+1) = 1

Примечание.

- Поскольку оба входа Gate2 равны 1, а Gate2 является логическим элементом И, выход Gate2 будет равен третьему входу.

- Поскольку один вход вентиля 1 равен 0, а вентиль 1 является логическим элементом И, выходной вентиль 1 будет равен 0 независимо от других входов.

- Gate4 = (Q’+Q)’ = 1’ = 0

Случай 4: J=1, K=1

Gate1 = Q, Gate2 = Q’, Gate4/Q(n+1)’ = 0, Gate3/Q(n+1) = Q’

Примечание.

- Поскольку один вход вентилей1 и вентиль2 равен 0, а оба вентиля являются вентилями И, выход обоих вентилей будет равен третьему входу.

- Gate4 = (Q’+Q)’ = 1’ = 0

- Gate3 = (Q+0)’ = Q’

Теперь напишем таблицу истинности-

Таблица истинности JK Flip Flop| Дж | К | Q(n+1) | Состояние |

| 0 | 0 | Qn | Без изменений |

| 0 | 1 | 0 | СБРОС |

| 1 | 0 | 1 | НАБОР |

| 1 | 1 | № | ПЕРЕКЛЮЧАТЕЛЬ |

Мы будем использовать эту таблицу истинности, чтобы написать таблицу характеристик JK-триггера. В таблице истинности вы видите два входа J и K и один выход Q(n+1). Но в таблице характеристик вы увидите три входа J, K и Qn и один выход Q(n+1).

Из приведенной выше логической схемы видно, что Qn и Qn’ являются двумя взаимодополняющими выходами, которые также действуют как входы для Gate3 и Gate4, поэтому мы будем рассматривать Qn, т. е. текущее состояние триггера, в качестве входных данных, а Q(n+ 1), то есть следующее состояние в качестве вывода.

е. текущее состояние триггера, в качестве входных данных, а Q(n+ 1), то есть следующее состояние в качестве вывода.

После написания таблицы характеристик мы нарисуем K-карту с 3 переменными, чтобы вывести характеристическое уравнение.

| Дж | К | Qn | Q(n+1) |

| 0 | 0 | 0 | 0 |

| 0 | 0 | 1 | 1 |

| 0 | 1 | 0 | 0 |

| 0 | 1 | 1 | 0 |

| 1 | 0 | 0 | 1 |

| 1 | 0 | 1 | 1 |

| 1 | 1 | 0 | 1 |

| 1 | 1 | 1 | 0 |

Из K-карты вы получаете 2 пары. При решении обоих мы получаем следующее характеристическое уравнение:

Q(n+1) = JQn’ + K’QnПреимущества

Использование триггера JK дает несколько преимуществ. Некоторые из них перечислены ниже:

Некоторые из них перечислены ниже:

- Возможность переключения: Имеет возможность переключения, что означает, что его можно использовать для создания схемы, которая переключается между двумя состояниями.

- Нет недопустимых состояний: В отличие от триггера SR, триггер JK не имеет недопустимых состояний.

- Уменьшенные условия гонки: Он менее чувствителен к условиям гонки, чем триггер SR, что может привести к более стабильной работе схемы.

- Бистабильная работа: Как и SR-триггер, JK-триггер имеет бистабильную работу, что означает, что он может удерживать состояние неопределенно долгое время, пока оно не будет изменено входным сигналом.

Помимо нескольких преимуществ, JK-триггеры имеют некоторые ограничения. Некоторые из них перечислены ниже:

- Сложность: JK-триггер сложнее, чем некоторые другие типы триггеров, что может затруднить его проектирование и реализацию в цифровых системах.

- Потребляемая мощность: Триггер JK может потреблять больше энергии, чем другие типы триггеров, особенно при использовании в режиме переключения.

- Задержка распространения: JK-триггер имеет задержку распространения, что может привести к проблемам синхронизации в цифровых системах с жесткими временными ограничениями.

- Ограниченная масштабируемость: Триггер JK может быть трудно масштабировать до более сложных цифровых систем, поскольку это может привести к увеличению сложности и возможности ошибок.

Вот некоторые примеры применения триггера JK в реальном мире:

- Счетчики: JK-триггер можно использовать вместе с другими цифровыми логическими элементами для создания двоичного счетчика. Это делает его полезным в приложениях реального времени, таких как таймеры и часы.

- Хранение данных: Триггер JK можно использовать для хранения временных данных в цифровых системах.

- Синхронизация: Триггер JK можно использовать для синхронизации сигналов данных между двумя цифровыми схемами, гарантируя, что они работают в одном и том же тактовом цикле. Это делает его полезным в приложениях, где время имеет решающее значение.

- Деление частоты: Триггер JK можно использовать для создания делителя частоты, представляющего собой схему, которая делит частоту входного сигнала на фиксированную величину. Это делает его полезным в приложениях реального времени, таких как обработка аудио и видео.

SR Основные сведения о шлепанцах | Схема, таблица истинности, ограничения и использование

— Реклама —

Это самый распространенный триггер среди всех. Эта простая триггерная схема имеет вход установки (S) и вход сброса (R). Кроме того, вы можете увидеть часы на входе. На выходе вы найдете два дополнительных выхода. Выход также является обратной связью со входом, видимым в его схеме. Следовательно, Q и Q’ не являются фактическими выходами. Вы можете сделать этот простой триггер либо с помощью логических элементов AND и NOR, либо только с логическими элементами NAND. Для лучшего понимания мы взяли базовую схему SR-триггера с использованием вентилей AND и NOR. Вы можете проверить основы логических вентилей.

Эта простая триггерная схема имеет вход установки (S) и вход сброса (R). Кроме того, вы можете увидеть часы на входе. На выходе вы найдете два дополнительных выхода. Выход также является обратной связью со входом, видимым в его схеме. Следовательно, Q и Q’ не являются фактическими выходами. Вы можете сделать этот простой триггер либо с помощью логических элементов AND и NOR, либо только с логическими элементами NAND. Для лучшего понимания мы взяли базовую схему SR-триггера с использованием вентилей AND и NOR. Вы можете проверить основы логических вентилей.

Давайте рассмотрим возможные случаи и запишем их в нашу таблицу истинности. Часы всегда равны 1.

SR Flip Flop WorkingСлучай 1: S=0, R=0

– Реклама –

Gate1 = 0, Gate2 = 0, Gate3/Q(n+1) = Q, Gate4/Q(n+1)’ = Q’

Примечание: оба вентиля являются вентилями ИЛИ-НЕ, выход обоих вентилей будет дополнять второй вход в соответствии со свойством вентилей ИЛИ-НЕ.

Случай 2: S=0, R=1

Gate1 = 1, Gate2 = 0, Gate3/Q(n+1) = 0, Gate4/Q(n+1)’ = 1

Примечание : Поскольку один вход вентиля 3 равен 1, а вентиль 3 является вентилем ИЛИ-НЕ, выходной вентиль 3 будет равен 0 независимо от другого входа в соответствии со свойством вентиля ИЛИ-НЕ.

Случай 3: S=1, R=0

Gate1 = 0, Gate2 = 1, Gate4/Q(n+1)’ = 0, Gate3/Q(n+1) = 1

Примечание : Поскольку один вход вентиля 4 равен 1, а вентиль 4 является вентилем ИЛИ-НЕ, выходной вентиль 4 будет равен 0 независимо от другого входа в соответствии со свойством вентиля ИЛИ-НЕ.

Случай 4: S=1, R=1

Gate1 = 1, Gate2 = 1, Gate4/Q(n+1)’ = 0, Gate3/Q(n+1) = 0

Примечание :

- Поскольку один вход вентиля 3 и вентиля 4 равен 1, а оба вентиля являются вентилями ИЛИ-НЕ, выходной вентиль3 и вентиль4 будет равен 0 независимо от другого входа в соответствии со свойством вентиля ИЛИ-ИЛИ.

- Q(n+1) и Q(n+1)’ являются дополнительными выходами, поэтому не могут быть одинаковыми

- Недопустимое состояние

Теперь составим таблицу истинности-

Таблица истинности триггера SR| S | Р | Q(n+1) | Состояние |

| 0 | 0 | Qn | Без изменений |

| 0 | 1 | 0 | СБРОС |

| 1 | 0 | 1 | НАБОР |

| 1 | 1 | х | НЕДЕЙСТВИТЕЛЬНЫЙ |

Мы будем использовать эту таблицу истинности для написания таблицы характеристик SR-триггера. В таблице истинности вы видите два входа S и R и один выход Q(n+1). Но в таблице характеристик вы увидите три входа S, R и Qn и один выход Q(n+1). Из приведенной выше логической схемы ясно, что Qn и Qn’ являются двумя дополнительными выходами, которые также действуют как входы для Gate3 и Gate4, поэтому мы будем рассматривать Qn, т. е. текущее состояние триггера, в качестве входных данных, а Q(n+1) то есть следующее состояние в качестве вывода.

е. текущее состояние триггера, в качестве входных данных, а Q(n+1) то есть следующее состояние в качестве вывода.

После написания таблицы характеристик мы нарисуем K-карту с 3 переменными, чтобы вывести характеристическое уравнение.

Таблица характеристик| S | Р | Qn | Q(n+1) |

| 0 | 0 | 0 | 0 |

| 0 | 0 | 1 | 1 |

| 0 | 1 | 0 | 0 |

| 0 | 1 | 1 | 0 |

| 1 | 0 | 0 | 1 |

| 1 | 0 | 1 | 1 |

| 1 | 1 | 0 | Х |

| 1 | 1 | 1 | Х |

SR Flip Flop K-Map

Из K-карты вы получаете 2 пары. Решив оба, мы получим следующее характеристическое уравнение:

Решив оба, мы получим следующее характеристическое уравнение:

Q(n+1) = S + R’QnПреимущества

Использование SR-триггера дает несколько преимуществ. Некоторые из них перечислены ниже:

- Простота: Триггер SR представляет собой простую и понятную схему.

- Скорость: Триггер SR относительно быстр, что делает его пригодным для использования в высокоскоростных цифровых системах.

- Низкое энергопотребление: Триггер SR потребляет очень мало энергии, что делает его пригодным для использования в устройствах с батарейным питанием.

- Бистабильная работа: SR-триггер можно устанавливать и сбрасывать, что делает его бистабильной схемой, которая может удерживать состояние неопределенно долгое время, пока оно не будет изменено входным сигналом.

Помимо нескольких преимуществ, у SR-триггеров есть некоторые ограничения. Некоторые из них перечислены ниже:

Некоторые из них перечислены ниже:

- R ace condition: SR-триггер чувствителен к состояниям гонки, которые возникают, когда состояние вывода изменяется непредсказуемо из-за различий во времени входных сигналов.

- Недопустимые состояния: Если оба входа установки и сброса активированы одновременно, SR-триггер может войти в недопустимое состояние, когда оба выхода имеют высокий уровень или оба являются низкими. Это может привести к непредсказуемому поведению цифровых систем.

- Ограниченная масштабируемость: SR-триггер может быть трудно масштабировать до более сложных цифровых систем, поскольку это может привести к увеличению сложности и возможности ошибок.

Вот некоторые примеры применения SR-триггера в реальном мире:

- Системы управления: SR-триггер используется в системах управления для синхронизации сигналов и координации работы других компонентов системы.

К книге добавлены главы из первого издания, усеченные во 2-м.

К книге добавлены главы из первого издания, усеченные во 2-м.