Схемы делителей частоты на микросхеме счетчике CD4040 (К561ИЕ20)

В некоторых схемах бывает нужно получить какую-то определенную частоту от источника более высокой частоты. Это можно сделать делением исходной частоты на некий делитель.

Если этот делитель целое число и не превышает числа 4096, частоту можно разделить при помощи счетчика CD4040 (аналог К561ИЕ20) и диодно-резисторной схемы «Монтажное И».

Микросхема CD4040

На рисунке 1 показана схема счетчика CD4040. Это двоичный счетчик с полным числом 12-ти разрядов. При работе счетчика логические единицы на его выходах появляются по системе двоичного кода, при достижении определенного числа входных импульсов. Максимальным является коэффициент деления, если снимать выходные импульсы с вывода 1, это будет 4096.

Коэффициенты деления присвоенные другим выходам будут равны двухкратному числу, из тех, что возле них подписаны. То есть, если, например, снимать импульсы с вывода 3 (число 16), то коэффициент деления буде 16×2=32.

Рис. 1. Схема счетчика CD4040 (К561ИЕ20).

Таким образом, если ничего не добавлять, и просто снимать импульсы с выходов счетчика, мы можем получить коэффициенты деления 2, 4, 8, 16, 32, 64, 128, 256, 512, 1024, 2048, 4096.

Но, на практике чаще требуется какой-то определенный коэффициент деления. Например, чтобы от источника частоты 50 Гц получить частоту 1 Гц, нужно сделать деление на 50.

В этом случае можно собрать схему, которая будет обнулять счетчик, каждый раз, как только он насчитает 50 входных импульсов. Пример такой схемы показан на рисунке 2.

Рассмотрим как она работает. Начальной исходной точкой является нулевое состояние счетчика. При этом, на всех его выходах установлены логические нули, и все диоды VD1-VD3 открыты, притягивая обнуляющий вход счетчика «R» к логическому нулю.

Затем пошел счет входных импульсов, и вот что происходит, через каждые два входных импульса появляется единица на выходе «2», через каждые 16 входных импульсов появляется единица на выходе «16», а через каждые 32 импульса появляется единица на выходе «32».

Рис. 2. Схема делителя частоты на 50, собрано на CD4040 (К561ИЕ20).

Чтобы счетчик обнулился нам нужно чтобы все диоды оказались открытыми, тогда напряжение логической единицы поступит на вход «R» счетчика через резистор R1. Но, такое может возникнуть только тогда, когда будут логические единицы на выходах «2», «16» и «32».

А первый раз с момента обнуления счетчика это произойдет при поступлении на вход счетчика числа импульсов, равного 2+16+32=50. Таким образом, счетчик обнулится через 50 импульсов.

И если снимать выходные импульсы с самого старшего из этих выходов, то есть с выхода «32», то частота импульсов на этом выходе будет в 50 раз меньше входной, то есть, если на входе 50 Гц, – на выходе «32» теперь будет 1 Гц.

Схема делителя на 2000

На рисунке 3 показана схема делителя на 2000, для получения частоты 500 Гц от входной частоты 1 МГц.

Рис. 3. Схема делителя частоты на 2000, микросхема CD4040 (К561ИЕ20).

Чтобы правильно и быстро рассчитать точки подключения диодов, можно пользоваться весьма простым способом. Вот, например, здесь нужен коэффициент деления 2000.

Вот, например, здесь нужен коэффициент деления 2000.

Берем число 2000 и ищем на выход счетчика с наиболее близким к нему, но меньшим числом, – это 1024. Делаем вычитание 2000-1024=976. Теперь ищем ближайшее меньшее к 976, это 512. Получается, 976-512=464.

Далее ищем ближайшее меньшее к 464, это 256, получается 464-256=208. Потом ищем ближайшее меньшее к 208, -128. Получается 208-128=80. Теперь ближайшее меньшее к 80, – это 64, получается 80-64=16.

Ну и остается выход 16, теперь 16-16=0. Таким образом, 2000-1024-512-256-128-64-16=0. Значит, для получения коэффициента деления 2000 диоды нужно катодами цеплять к выходам «1024», «512», «256», «128», «64» и «16». Что, собственно, и показано на схеме на рисунке 3.

Схема для получения 160 Гц из 500 кГц

На рисунке 4 показана схема делителя частоты, чтобы из входной частоты 500 кГц получить выходную 160 Гц. Коэффициент деления в данном случае требуется 500000/160 = 3125.

Рис. 4. Схема делителя частоты, чтобы из входной частоты 500 кГц получить выходную 160 Гц.

Соответственно, делаем расчет: 3125-2048-1024-32-16-4-1 =0 Таким образом, катоды диодов цепляем на выходы «2048», «1024», «32», «16», «4» и «1». В результате, на самом старшем из используемых выходов частота будет в 3125 раз меньше входной.

Особенность такого делителя частоты, что форма импульсов на его выходе не симметричная, – отрицательный перепад всегда больше положительного.

Например, на рис. 1 они соотносятся как 32/18. Поэтому, такой способ можно применять только там, где важна именно частота, а не скважность.

Андреев С. РК-03-2020.

| Наиболее часто для этого используют

счетчики, хотя можно разделить частоту с

помощью ждущего мультивибратора, ограничив

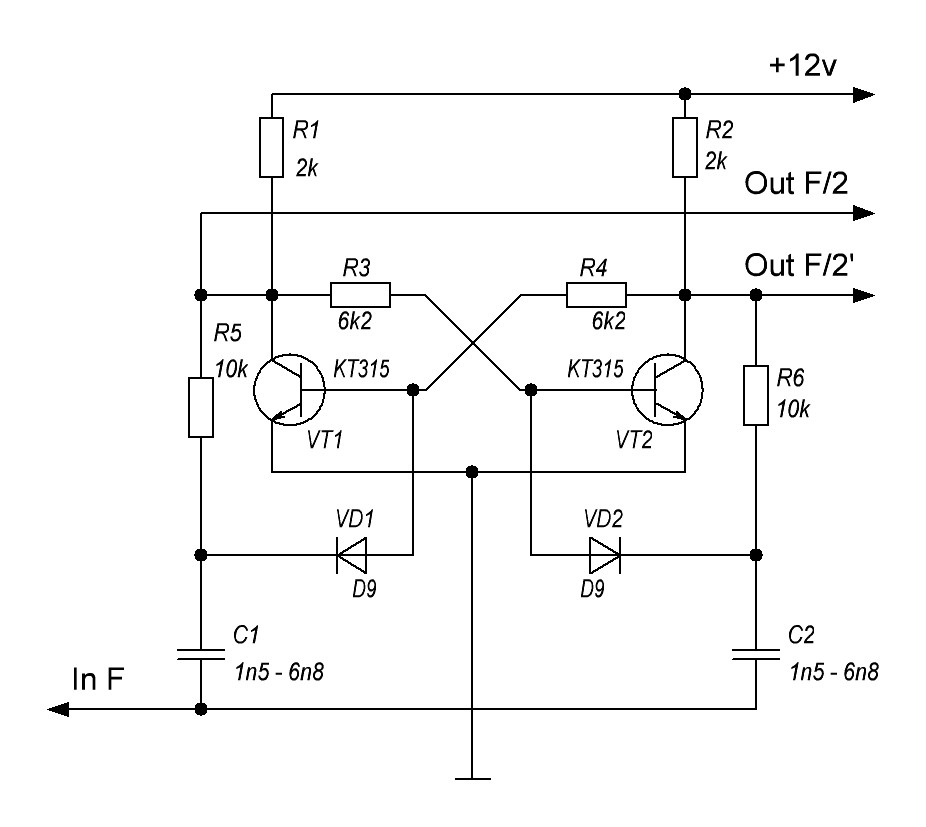

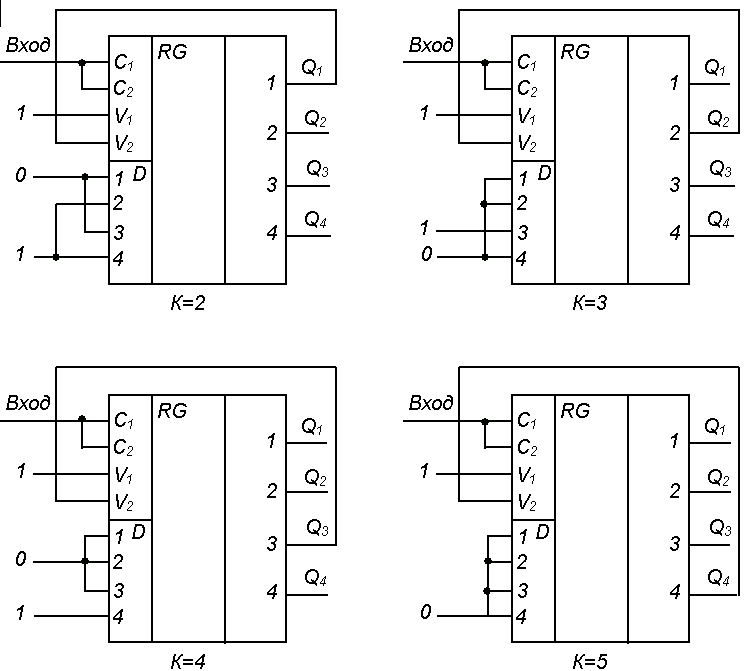

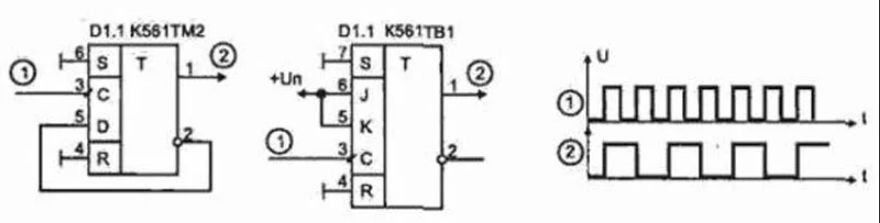

число проходящих на выход импульсов. Рис. 1.60 Делитель частоты с использованием ждущего мультивибратора Как только импульс входной частоты поступает на выход 5, ждущий мультивибратор D1.1, D1.3 запирает элемент D1.2 на время, определяемое резистором R1. Когда ждущий мультивибратор возвращается в исходное состояние, на выход поступает следующий импульс и цикл возобновляется. Схему можно усовершенствовать, заменив потенциометр полевым транзистором, что позволит управлять коэффициентом деления с помощью напряжения. Рис. 1.61. Счетный триггер на логических элементах Рис. 1.62. Делитель частоты на 2 Рис. 1.63. Делитель на 3 Делитель на 2 можно собрать из простейших ЛЭ, рис. 1.61. Схемы делителей без использования RC-цепей имеют лучшую помехоустойчивость и болееширокий диапазон входной частоты сигнала. Основным элементом всех счетчиков является триггер с так называемым счетным входом, рис. 1.62. Таблица поясняет логику работы триггера 561ТМ2

в зависимости от управляющих сигналов (х —

безразлично состояние на данном входе;

состояние, когда на входах S и R микросхемы

одновременно действует лог.

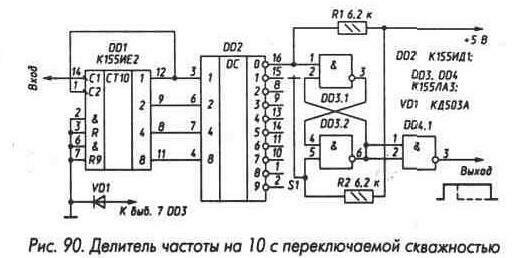

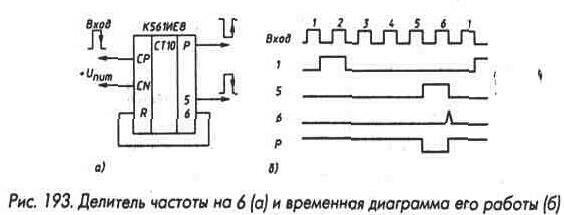

Рис. Рис. 1 65. Схема делителя на 60 Рис. 1. 66. а)

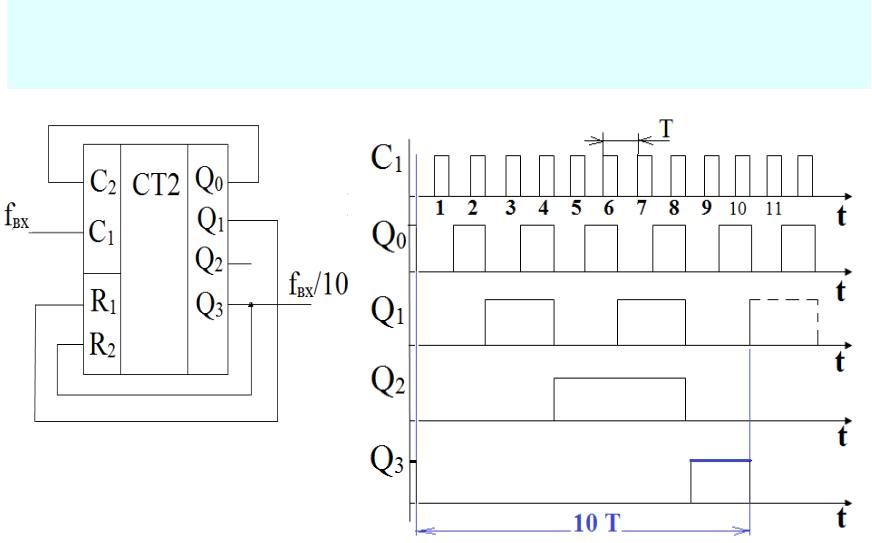

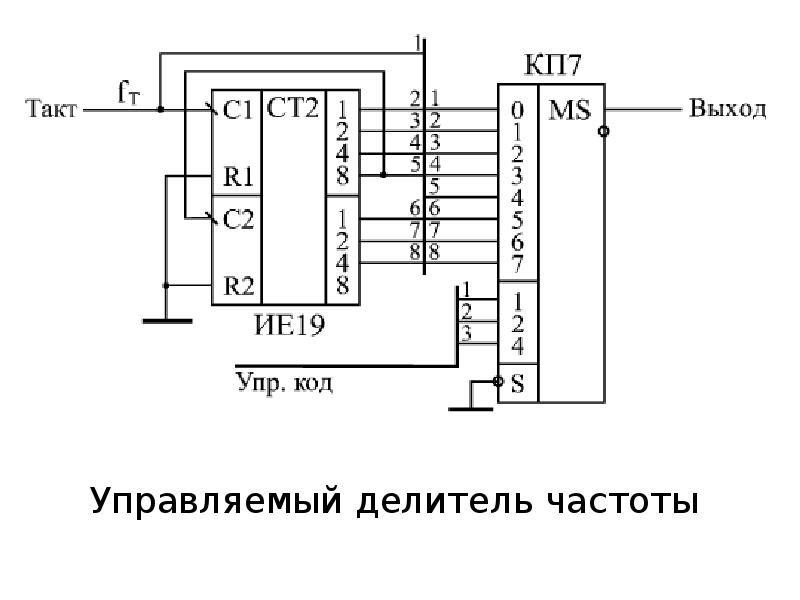

Универсальный реверсивный счетчик, Комбинационное включение триггеров позволяет получать счетчик с нужным коэффициентом деления входной частоты. На рис. 1.63…1.65 приведены примеры включения элементов микросхем для получения деления на 2, 3, 6, 10 и 60. Промышленность выпускает универсальные счетчики, которые в зависимости от управляющих сигналов могут переключаться по переднему или заднему фронту входного сигнала, а также менять направление счета (сложение или вычитание). В качестве примера приведена диаграмма работы двоичного четырехразрядного реверсивного счетчика на микросхеме 561ИЕ11, рис. 1.66. Таблица истинности поясняет назначение

управляющих сигналов и логику управления

микросхемой (1 — лог. “1”; 0 — лог.

“0”; х — состояние безразлично, т. е. 0

или 1). Счетчик предусматривает возможность

загрузить по входам D1, D2, D4, D8 параллельный

код.

Pис 1.67. Делитель на 1000 Для получения нужного коэффициента деления

можно использовать микросхемы двоичных

счетчиков, соединяя соответствующие выходы

с помощью ЛЭ, рис. 1.67, или же применить

счетчик с программируемым коэффициентом

деления 564ИЕ15, см. рис. 1.26. | |||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

Схема делителя частоты с CD4017

от Ayesha Khan

7 334 просмотраВведение:

Делитель частоты, как видно из названия, представляет собой схему, которая генерирует выходную частоту, кратную подаваемой входной частоте. Он также известен как предварительный скаляр или делитель часов. Для разделения частоты используются различные электронные устройства, такие как регенеративные устройства, релаксационные генераторы и т.д. Существует три основных типа делителей частоты: аналоговые, цифровые и дробные делители.

Делители частоты могут представлять собой простые или сложные схемы в зависимости от применения. Простая схема может быть построена с использованием микросхемы таймера 555, которая используется в качестве генератора или таймера в различных схемах, и микросхемы CD4017, представляющей собой микросхему декодера с десятью выходами, которую можно использовать в качестве счетчика или делителя. Цель состоит в том, чтобы предоставить простую и удобную схему для понимания концепции делителя частоты.

Купить на Amazon

Аппаратные компоненты

Следующие компоненты необходимы для изготовления схемы делителя частоты

| S. № | Компоненты | Стоимость | Количество |

|---|---|---|---|

| 1. | Таймер 555 IC | 1 | |

| 2. | Счетчик декад IC | CD4017 | 1 |

| 3. | IC регулятор напряжения | 7805 | 1 |

| 4. | Переменный резистор 90 036 | 50 кОм | 1 |

5. | Светодиод | 2 | |

| 6. | Переключатель | 1 | |

| Аккумулятор | 9 В | 2 | |

| 8. | Резистор | 33 кОм , 10 кОм, 330 Ом | 1, 1, 2 |

| 9. | Конденсатор | 10 мкФ, 0,1 мкФ | 1 | 9 0031

CD4017 Распиновка

Подробное описание распиновки, размеров и технических характеристик скачать техпаспорт CD4017

Распиновка микросхемы NE555

Для получения подробного описания цоколевки, размеров и технических характеристик загрузите техническое описание таймера 555

Цепь делителя частоты

Принципиальная схема делителя частоты приведена ниже:

Двумя основными компонентами схемы являются ИС таймера 555 и ИС CD4027, а также другие пассивные компоненты, завершающие схему и работающие надлежащим образом.

Здесь микросхема таймера 555 используется в качестве генератора импульсов для деления частоты. Было обнаружено, что ИС применима для различных целей, таких как синхронизация или генератор колебаний, генератор импульсов и т. Д. ИС CD4017 используется в качестве делителя для деления частоты на несколько частей. Он производит десять декодированных выходов, обычно используемых в качестве делителя или счетчика.

Схема работает в два этапа: первый — в генераторе входной частоты, а второй — в цепи декодера или делителя. Микросхема таймера 555 настроена на нестабильный режим. Разрядный вывод микросхемы включен между двумя резисторами R1 и R2 (временно-временными резисторами), которые последовательно соединены с переменным резистором VR1 и времязадающим конденсатором C1. Пороговый и триггерный контакты соединены вместе и подключены между VR1 и C1, в то время как вход 5V подключен к контактам сброса и VCC, соединенным вместе. Выход микросхемы таймера подключен к микросхеме 4017, а два светодиода отображают входную частоту.

Контакт 14 микросхемы 4017 принимает входные данные и выдает декодированный выходной сигнал с Q0 по Q9, выходной сигнал берется с контакта 2 после преобразования его в делитель частоты, в то время как светодиод указывает на выходной сигнал. Выходной сигнал с частотным делением можно увидеть с помощью осциллографа с контакта 2. Контакт сброса соединен с переключателем в направлении Q2, Q4 и Q6 для выбора выходов F/2, F/4 и F/6 соответственно.

Применение:

Делитель частоты может быть реализован в различных аналоговых и цифровых схемах, имеет следующие применения:

- Схема используется в синтезаторах частот для генерации диапазона частот с одного входа.

- Он также используется в атомных часах или телевизорах.

- Схема также применима в радиолокационных системах в качестве устройства синхронизации.

- Схема используется для создания «n» кратных частот, которые можно использовать в схемах тактового буфера.

- Он также находит применение в радиочастотных устройствах, звуковом и военном оборудовании и т.

д.

д.

Похожие сообщения:

Схема делителя частоты D-типа» Electronics Notes

– информация и схема электронной схемы логического триггера D-типа для обеспечения деления частоты на два.

Логический / цифровой дизайн Включает:

Типы логических вентилей

Логическая таблица истинности

Как преобразовать вентили И-НЕ/ИЛИ-НЕ с помощью инверторов

RS-триггер

RS Flip-Flop с срабатыванием по фронту

Программируемый инвертор

Делитель частоты D-типа

Логический триггер D-типа — очень универсальная схема. Его можно использовать во многих областях, где требуется схема с запуском по фронту. В одном приложении эта логическая или цифровая схема обеспечивает очень простой метод деления входящей последовательности импульсов на коэффициент два.

В схеме деления на два используется один логический элемент d-типа. Просто введя последовательность импульсов в схему синхронизации и подключив выход Qbar к входу D, можно получить выходной сигнал с соединения Q на D-типе.

Схема работает просто. Входящая последовательность импульсов действует как часы для устройства, а данные, которые находятся на входе D, затем синхронизируются на выходе. Чтобы точно увидеть, как работает схема, стоит изучить, что происходит на каждом этапе сигналов, показанных ниже. Возьмем ситуацию, когда выход Q имеет уровень «1». Это означает, что выход Qbar будет равен «0». Эти данные синхронизируются на выходе Q по следующему положительному фронту от входящей последовательности импульсов на входе синхронизации. В этот момент выход изменяется с «1» на «0». При следующем положительном тактовом импульсе данные на выходе Qbar снова тактируются. Поскольку теперь это «1» (напротив выхода Q), это передается на выход, и выход снова меняет состояние.

Видно, что выход схемы изменяет состояние только на положительных фронтах входящего импульсного тактового потока.

Пример

такой схемы показан на рис. 1.60.

Пример

такой схемы показан на рис. 1.60. “1”,

является запрещенным).

“1”,

является запрещенным). 1.64. а) Делитель на

10 на RS-триггерах; б) делитель на 10 на JK-триггерах

1.64. а) Делитель на

10 на RS-триггерах; б) делитель на 10 на JK-триггерах