Эксперименты с RS-триггером.

Схемы RS-триггеров на микросхемах

После знакомства с принципом работы различных триггеров у начинающего радиолюбителя возникает естественное желание опробовать работу этих самых триггеров в “железе”.

На практике изучение работы триггеров гораздо интересней и увлекательней, кроме того происходит знакомство с реальной элементной базой.

Далее будут рассмотрены несколько схем триггеров, выполненных на цифровых микросхемах так называемой жёсткой логики. Сами по себе схемы не являются завершёнными готовыми устройствами и служат лишь для наглядной демонстрации принципов работы RS-триггера.

Итак, начнём.

Для ускорения процесса сборки и тестирования схем применялась беспаечная макетная плата. С её помощью удаётся быстро сконфигурировать и изменить схему в соответствии с потребностями. Пайка, естественно, не применяется.

Схема RS-триггера на микросхеме К155ЛА3.

Данная схема уже приводилась на страницах сайта в статье про RS-триггер.

Для дела сгодится даже 5-ти вольтовый зарядник от сотового телефона. Но стоит понимать, что не каждый зарядник держит стабильное напряжение. Оно может гулять в пределах 4,5 – 6 вольт. Поэтому всё-таки лучше использовать стабилизированный блок питания. При желании можно собрать блок питания своими руками. К выводу 14 микросхемы К155ЛА3 подключается “+” питания, а к 7 выводу “-” питания.

Как видим, схема очень простая и выполнена на логических элементах 2И-НЕ. Собранная схема имеет всего лишь два устойчивых состояния 0 или 1.

После того, как на схему будет подано напряжение питания, загорится один из светодиодов. В данном случае загорался синий светодиод, который подключен к инверсному выходу триггера (Q).

При однократном нажатии на кнопку Set (установка), RS-триггер устанавливается в единичное состояние. При этом должен засветиться тот светодиод, который подключен к так называемому прямому выходу Q. В данном случае это красный светодиод.

Это свидетельствует о том, что триггер «запомнил» 1 и выдал сигнал об этом на прямой выход Q.

Светодиод (синий), который же подключен к инверсному выходу Q, должен погаснуть. Инверсный – это значит обратный прямому. Если на прямом выходе 1, то на инверсном 0. При повторном нажатии на кнопку Set, состояние триггера не изменится – реагировать на нажатия кнопки он не будет. В этом и заключается основное свойство любого триггера – способность длительное время сохранять одно из двух состояний. По сути, это простейший

Чтобы сбросить RS-триггер в нуль (т.е. записать в триггер логический 0) нужно один раз нажать на кнопку Reset (сброс). При этом красный светодиод погаснет, а синий загорится. Повторные нажатия на кнопку Reset состояние триггера не изменят.

При этом красный светодиод погаснет, а синий загорится. Повторные нажатия на кнопку Reset состояние триггера не изменят.

Показанную схему можно считать примитивной, так как собранный RS-триггер не имеет никакой защиты от помех, а сам триггер является одноступенчатым. Но зато в схеме применяется микросхема К155ЛА3, которая очень часто встречается в электронной аппаратуре и поэтому она легкодоступна.

Также стоит отметить, что на этой схеме выводы установки S, сброса R, прямого Q и инверсного выхода Q показаны условно – их можно поменять местами и суть работы схемы не изменится. Это всё потому, что схема выполнена на неспециализированной микросхеме.

Видео работы RS-триггера на микросхеме К155ЛА3.

Далее же мы разберём пример реализации RS-триггера на специализированной микросхеме-триггере.

Схема RS-триггера на микросхеме КМ555ТМ2.

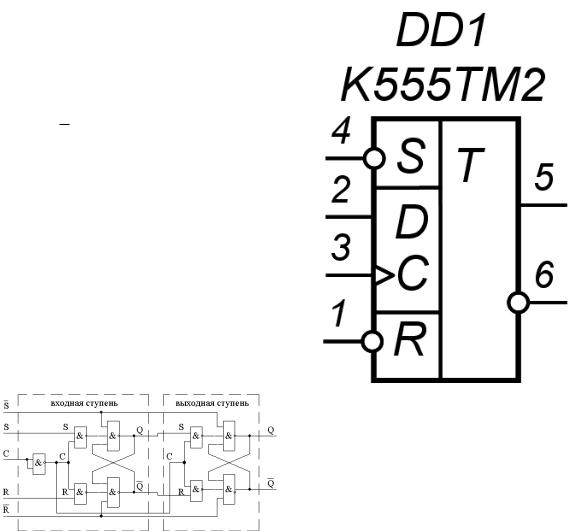

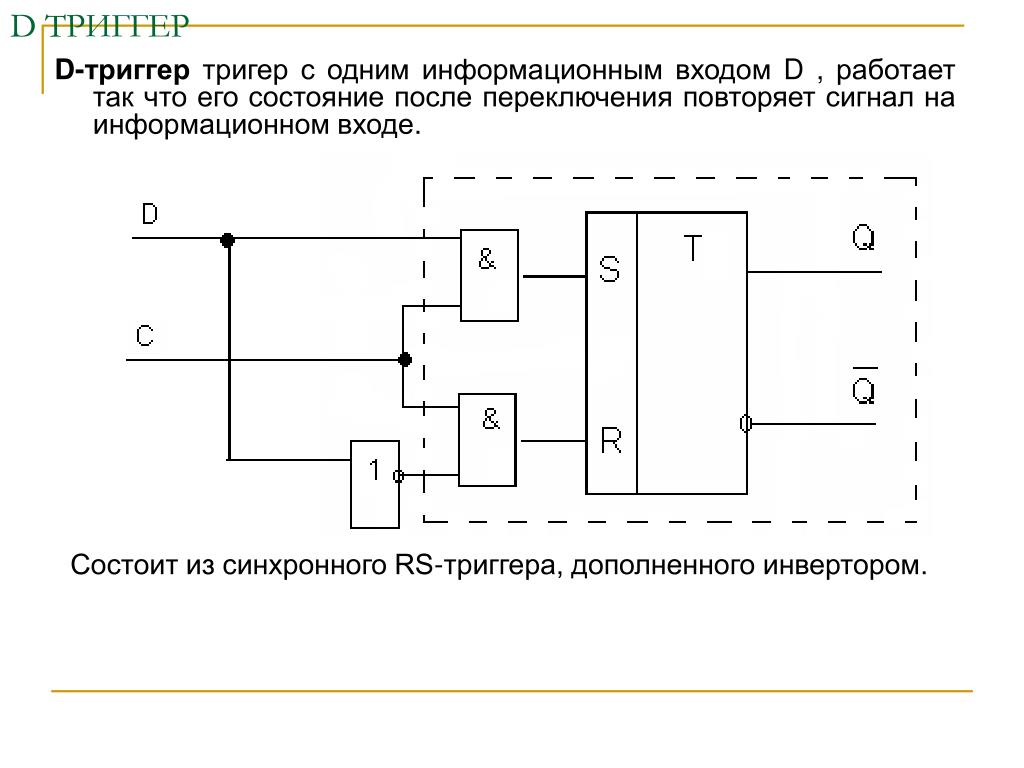

В данной схеме используется специализированная микросхема КМ555ТМ2, в составе которой 2 D-триггера. Эта микросхема выполнена в керамическом корпусе, поэтому в названии присутствует сокращение КМ. Также можно применить микросхемы К555ТМ2 и К155ТМ2. Они имеют пластмассовый корпус.

Эта микросхема выполнена в керамическом корпусе, поэтому в названии присутствует сокращение КМ. Также можно применить микросхемы К555ТМ2 и К155ТМ2. Они имеют пластмассовый корпус.

Как мы знаем, D-триггер несколько отличается от RS-триггера, но у него также присутствуют входы для установки (S) и сброса (R). Если не использовать вход данных (D) и тактирования (C), то на базе микросхемы КМ555ТМ2 легко собрать RS-триггер. Вот схема.

В схеме применён только один из двух D-триггеров микросхемы КМ555ТМ2. Второй D-триггер не используется. Его выводы никуда не подключаются.

Так как входы S и R микросхемы КМ555ТМ2 являются инверсными (отмечены кружком), то переключение триггера из одного устойчивого состояния в другое происходит при подаче на входы S и R логического 0.

Чтобы подать на входы 0, нужно просто соединить эти входы с минусовым проводом питания (с минусом «-»). Сделать это можно как с помощью специальных кнопок, например, тактовых, как на схеме, так и с помощью обычного проводника. Кнопками, конечно, это делать гораздо удобнее.

Сделать это можно как с помощью специальных кнопок, например, тактовых, как на схеме, так и с помощью обычного проводника. Кнопками, конечно, это делать гораздо удобнее.

Жмём кнопку SB1 (Set) и устанавливаем RS-триггер в единицу. Засветится красный светодиод.

А теперь жмём кнопку SB2 (Reset) и сбрасываем триггер в нуль. Засветится синий светодиод, который подключен к инверсному выходу триггера (Q).

Стоит отметить, что входы S и R у микросхемы КМ555ТМ2 являются приоритетными. Это значит, что сигналы на этих входах для триггера являются главными. Поэтому если на входе R нулевое состояние, то при любых сигналах на входах C и D состояние триггера не изменится. Это утверждение относится к работе D-триггера.

Видео работы RS-триггера на микросхеме КМ555ТМ2.

Если найти микросхемы К155ЛА3, КМ155ЛА3, КМ155ТМ2, К155ТМ2, К555ТМ2 и КМ555ТМ2 не удастся, то можно использовать зарубежные аналоги этих микросхем стандартной транзисторно-транзисторной логики (ТТЛ): 74LS74 (аналог К555ТМ2), SN7474N и SN7474J (аналоги К155ТМ2), SN7400N и SN7400J (аналоги К155ЛА3).

Главная » Цифровая электроника » Текущая страница

Также Вам будет интересно узнать:

Цифровые микросхемы транзисторы.

Микросхемы ТТЛ (74…).

На рисунке показана схема самого распространенного логического элемента — основы микросхем серии К155 и ее зарубежного аналога — серии 74. Эти серии принято называть стандартными (СТТЛ). Логический элемент микросхем серии К155 имеет среднее быстродействие tзд,р,ср.= 13 нс. и среднее значение тока потребления Iпот = 1,5…2 мА. Таким образом, энергия, затрачиваемая этим элементом на перенос одного бита информации, примерно 100 пДж.

Для обеспечения выходного напряжения высокого уровня U1вых. 2,5 В в схему на рисунке потребовалось добавить диод сдвига уровня VD4, падение напряжения на котором равно 0,7 В. Таким способом была реализована совместимость различных серий ТТЛ по логическим уровням.

| ТТЛ серия | Параметр | Нагрузка | ||||

|---|---|---|---|---|---|---|

| Российские | Зарубежные | Pпот. мВт. | tзд.р. нс | Эпот. пДж. | Cн. пФ. | Rн. кОм. |

| К155 КМ155 | 74 | 10 | 9 | 90 | 15 | 0,4 |

| К134 | 74L | 1 | 33 | 33 | 50 | 4 |

| К131 | 74H | 22 | 6 | 132 | 25 | 0,28 |

| К555 | 74LS | 2 | 9,5 | 19 | 15 | 2 |

| К531 | 74S | 19 | 3 | 57 | 15 | 0,28 |

| К1533 | 74ALS | 1,2 | 4 | 4,8 | 15 | 2 |

| К1531 | 74F | 4 | 3 | 12 | 15 | 0,28 |

При совместном использовании микросхем ТТЛ высокоскоростных, стандартных и микромощных следует учитывать, что микросхемы серии К531 дают увеличенный уровень помех по шинам питания из-за больших по силе и коротких по времени импульсов сквозного тока короткого замыкания выходных транзисторов логических элементов.

| Нагружаемый выход |

Число входов-нагрузок из серий | ||

|---|---|---|---|

| К555 (74LS) | К155 (74) | К531 (74S) | |

| К155, КM155, (74) | 40 | 10 | 8 |

| К155, КM155, (74), буферная | 60 | 30 | 24 |

| К555 (74LS) | 20 | 5 | 4 |

| К555 (74LS), буферная | 60 | 15 | 12 |

| 50 | 12 | 10 | |

| К531 (74S), буферная | 150 | 37 | 30 |

Выходы однокристальных, т. е. расположенных в одном корпусе, логических элементов ТТЛ, можно соединять вместе. При этом надо учитывать, что импульсная помеха от сквозного тока по проводу питания пропорционально возрастет. Реально на печатной плате остаются неиспользованные входы и даже микросхемы (часто их специально «закладывают про запас») Такие входы логического элемента можно соединять вместе, при этом ток Ioвх. не увеличивается. Как правило, микросхемы ТТЛ с логическими функциями И, ИЛИ потребляют от источников питании меньшие токи, если на всех входах присутствуют напряжения низкого уровня. Из-за этого входы таких неиспользуемых элементов ТТЛ следует заземлять.

е. расположенных в одном корпусе, логических элементов ТТЛ, можно соединять вместе. При этом надо учитывать, что импульсная помеха от сквозного тока по проводу питания пропорционально возрастет. Реально на печатной плате остаются неиспользованные входы и даже микросхемы (часто их специально «закладывают про запас») Такие входы логического элемента можно соединять вместе, при этом ток Ioвх. не увеличивается. Как правило, микросхемы ТТЛ с логическими функциями И, ИЛИ потребляют от источников питании меньшие токи, если на всех входах присутствуют напряжения низкого уровня. Из-за этого входы таких неиспользуемых элементов ТТЛ следует заземлять.

| Параметр | Условия измерения | К155 | К555 | К531 | К1531 | |||||||

|---|---|---|---|---|---|---|---|---|---|---|---|---|

Мин. |

Тип. | Макс. | Мин. | Тип. | Макс. | Мин. | Тип. | Макс. | Мин. | Макс. | ||

| U1вх, В схема |

U1вх или U0вх Присутствуют на всех входах | 2 | 2 | 2 | 2 | |||||||

| U0вх, В схема |

0,8 | 0,8 | 0,8 | |||||||||

| U0вых, В схема | Uи.п.= 4,5 В | 0,4 | 0,35 | 0,5 | 0,5 | 0,5 | ||||||

| I0вых= 16 мА | I0вых= 8 мА | I0вых= 20 мА | ||||||||||

| U1вых, В схема |

Uи. п.= 4,5 В п.= 4,5 В |

2,4 | 3,5 | 2,7 | 3,4 | 2,7 | 3,4 | 2,7 | ||||

| I1вых= -0,8 мА | I1вых= -0,4 мА | I1вых= -1 мА | ||||||||||

| I1вых, мкА с ОК схема | U1и.п.= 4,5 В, U1вых=5,5 В | 250 | 100 | 250 | ||||||||

| I1вых, мкА Состояние Z схема |

U1и.п.= 5,5 В, U1вых= 2,4 В на входе разрешения Е1 Uвх= 2 В | 40 | 20 | 50 | ||||||||

| I0вых, мкА Состояние Z схема |

U1и. п.= 5,5 В, Uвых= 0,4 В, Uвх= 2 В п.= 5,5 В, Uвых= 0,4 В, Uвх= 2 В |

-40 | -20 | -50 | ||||||||

| I1вх, мкА схема | U1и.п.= 5,5 В, U1вх= 2,7 В | 40 | 20 | 50 | 20 | |||||||

| I1вх, max, мА | U1и.п.= 5,5 В, U1вх= 10 В | 1 | 0,1 | 1 | 0,1 | |||||||

| I0вх, мА схема |

U1и.п.= 5,5 В, U0вх= 0,4 В | -1,6 | -0,4 | -2,0 | -0,6 | |||||||

Iк. з., мА з., мА | U1и.п.= 5,5 В, U0вых= 0 В | -18 | -55 | -100 | -100 | -60 | -150 | |||||

Микросхемы К561ТР2, К561ТМ2 » Вот схема!

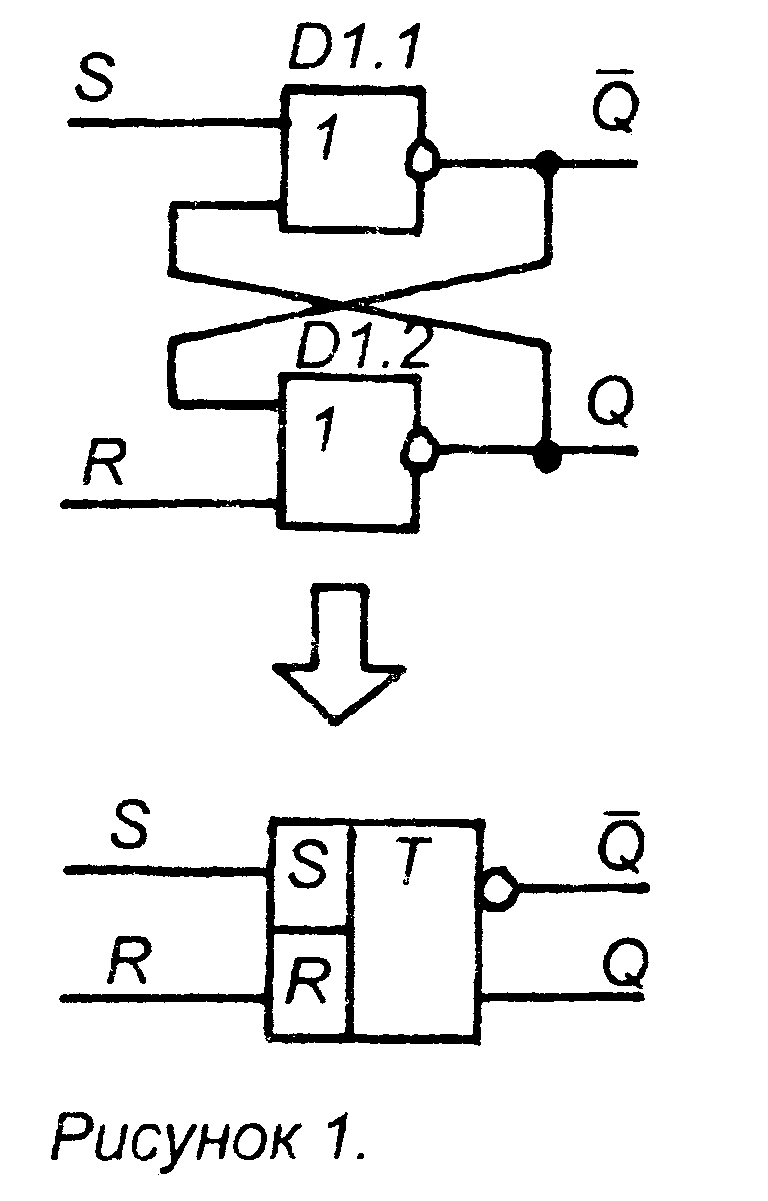

Как работает RS-триггер? У него имеются два входа и два выхода, входы обозначим R и S, а выходы Q (прямой) и Q (инверсный). Когда единичный импульс поступает на вход S триггер устанавливается в единичное состояние и на его выходе Q будет единица (на выходе Q будет ноль, поскольку выход инверсный).

Такое состояние сохранится и если убрать единицу с входа S. И оно будет сохраняться до тех пор, пока на вход R не будет подан единичный импульс, тогда триггер “перекинется” в противоположное состояние, и на Q будет ноль, а на Q — единица. Таким образом RS-триггер может быть в двух устойчивых состояниях — единичном, когда на выходе Q единица, и нулевом, когда на Q ноль.

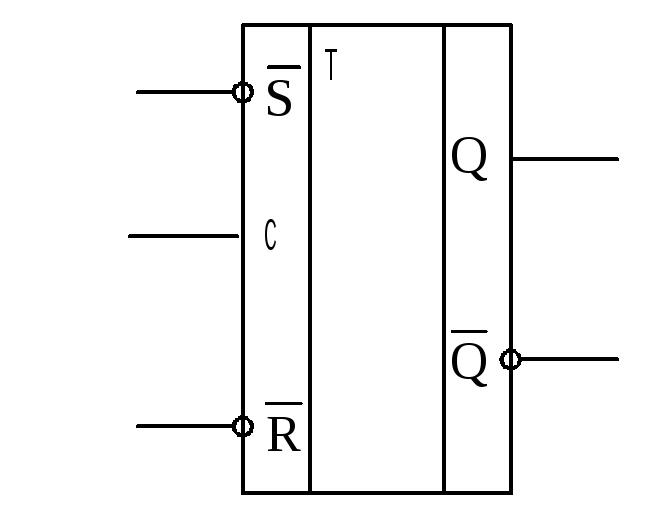

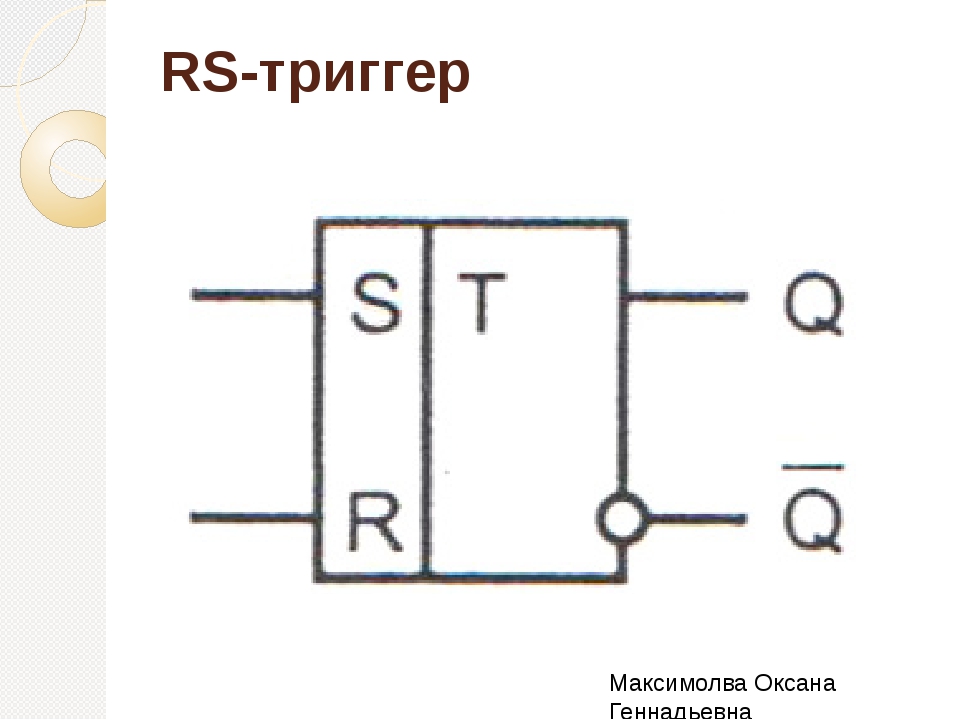

На схемах RS-триггер обозначается так, как показано внизу рисунка 1. Таким образом RS-триггер становится еще одной “элементарной частицей” цифровой схемы, “черным ящичком”, имеющим строго определенные функции: подал единичный импульс на S и на Q будет единица, подал единичный_импульс на R и на Q теперь будет ноль (а на Q — все наоборот).

В сериях К176 и К561 есть только одна микросхема, содержащая RS-триггеры в “чистом виде” — это К561ТР2, причем только в серии К561 (К176ТР2 не бывает). Схема микросхемы К561ТР2 показана на рисунке 2, она содержит четыре RS-триггера, имеющих только по одному прямому выходу (Q), которые к тому же можно отключать от выходных выводов микросхемы при помощи внутреннего ключевого устройства.

При подаче единицы на вывод 5 эти ключи замыкаются и уровни с выходов триггеров поступают на выходные выводы микросхемы, а если на вывод 5 подать нуль, то ключи разомкнутся и выходы триггеров отключатся от выходных выводов микросхемы (на этих выводах, в таком случае, будет “серый уровень”или “высокоимпендансное состояние”, то есть они, практически, никуда не будут подключены).

Корпус у этой микросхемы почти такой же как у К561ЛЕ5 или К561ЛА7, но у него на два вывода больше, то есть с каждого бока микросхемы не по семь выводов, а по восемь. Кроме RS-триггеров существуют еще и D-триггеры, с которыми нам предстоит познакомиться на этом занятии.

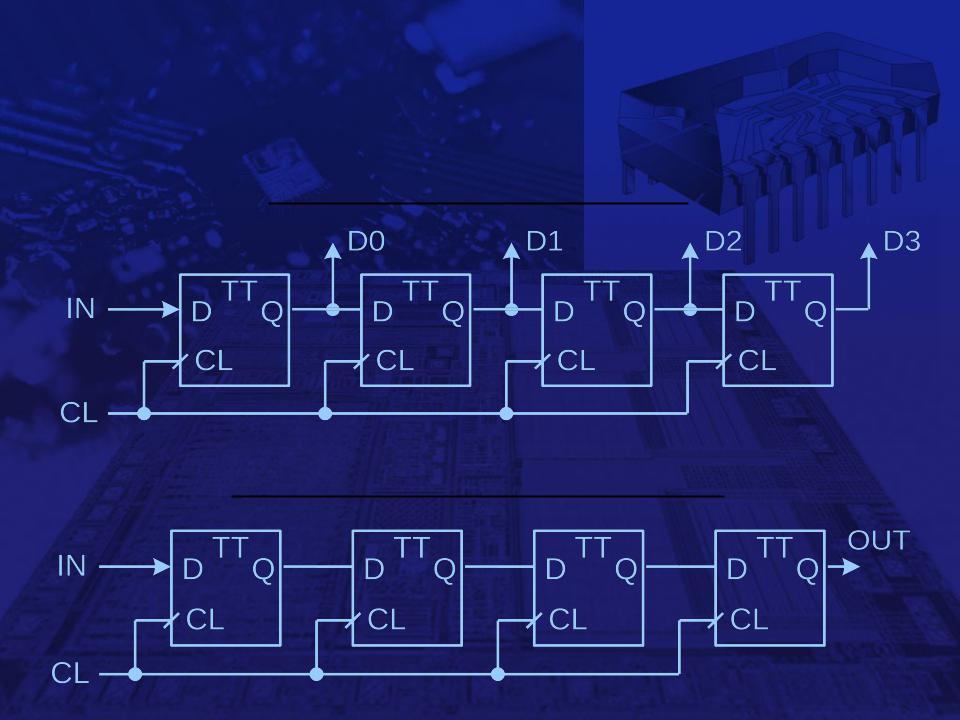

Распространенная микросхема К561ТМ2 (или К176ТМ2) содержит два D-триггера (рисунок 3). Микросхема имеет точно такой же корпус как у К561ЛЕ5, К561ЛА7 (К176ЛЕ5, К176ЛА7). Как видно из рисунка отличие D-триггера от RS-триггера в том, что у него есть два новых входа — вход D и вход С.

Чтобы изучить работу D-триггера соберем схему, показанную на рисунке 4. S1 — кнопка, S2 — микротумблер, но как и прежде, если нет кнопок, можно просто соединять два оголенных монтажных провода. Прибор Р1 — любой тестер или мультиметр, переключенный на измерение напряжения до 10-15В, когда он будет показывать напряжение, почти равное напряжению питания, — это единица, когда почти ноль — это ноль. Батарея питания составлена из двух батареек по 4,5В каждая, так что в сумме они дают 9В (включены последовательно).

Входы S и R триггера соединим с общим минусом питания, как работает RS-триггер мы знаем, так что, пусть они нам не мешают.

В момент включения питания триггер окажется в одном из двух положений, либо ноль на выводе 1, либо на нем же единица. Если нужно установить его принудительно в какое-то положение это можно сделать выводами R и S как в RS-триггере, на нам это не нужно. Предположим на выходе нуль (низкие показания Р1). Если мы будем нажимать на S1 ничего не изменится. Но если сначала замкнуть S2 (на вход D подать единицу), а потом, удерживая S2 в замкнутом состоянии, нажать на S1 то триггер перекинется в единичное состояние, и на его выводе 1 будет единица (напряжение около напряжения питания).

Теперь, удерживая S2 по-прежнему в нажатом состоянии, попробуем снова нажать на S1 — ничего не меняется. Триггер жестко держится в единичном состоянии. Попробуем разомкнуть S2 (теперь на вход D поступает ноль через R2). Снова нажмем на S1 — триггер вернется в нулевое состояние (нуль на выводе 1).

Таким образом, при нажатии на S1 триггер устанавливается в такое положение, при котором логический уровень на его прямом выходе будет таким же как на входе D. После отпускания S1, триггер останется в установившемся положении, ему будет все равно, что на входе D, если на входе С (кнопка S1) нуль. То есть, если на входе D будет единица, то в момент нажатия на S1 (подача единицы на вход С) состояние триггера станет единичным (единица на выводе 1), и останется таким и после отпускания S1 и изменения уровня на D. Но если на D подать нуль, и удерживая этот нуль, нажать на S1 (подать единицу на С), то триггер перейдет в нулевое положение.

ТРИГГЕРЫ НА МИКРОСХЕМАХ

Если мультивибратор это прибор с двумя неустойчивыми состояниями, который самопроизвольно переходит из одного состояния в другое, то триггер ему полностью противоположен. Это прибор с двумя устойчивыми состояниями и эти состояния он меняет только под внешнем воздействии. Благодаря этому свойству триггеры используются в запоминающих устройствах [1]. В данной работе предлагаются к повторению широко распространенные схемы триггеров, которые можно реализовать на одной логической микросхеме К155ЛА3. Питание подается на 14 выход микросхемы, общий провод 7. Питание осуществляется от стабилизированного источника питания напряжением 5 В.

В данной работе предлагаются к повторению широко распространенные схемы триггеров, которые можно реализовать на одной логической микросхеме К155ЛА3. Питание подается на 14 выход микросхемы, общий провод 7. Питание осуществляется от стабилизированного источника питания напряжением 5 В.

Асинхронный RS-триггер

Самый простой тип триггера, который является основой для сборки остальных триггеров в данной лабораторной работе. Он собирается на паре логических элементов И-НЕ, хотя аналогично можно использовать ИЛИ-НЕ [2]

Как видно на электрической принципиальной схеме данное электронное устройство обладает симметрией. Если поменять местами входы S и R, одновременно с выходами Q и Q1, то по сути мы получим туже самую схему. Таким образом то где у триггера прямой выход, а где инверсный это по сути вопрос договора.

Для практической реализации схемы используются самодельные модули для изучения микросхем. При подаче питания триггер устанавливается в случайное состояние.

Используя данное устройство можно проследить за выполнением таблицы истинности асинхронного RS-триггер.

Таблица истинности асинхронного RS-триггера

В частности, можно увидеть, что данный триггер переключается просто от прикосновения к проводам и пронаблюдать запрещенное состояние.

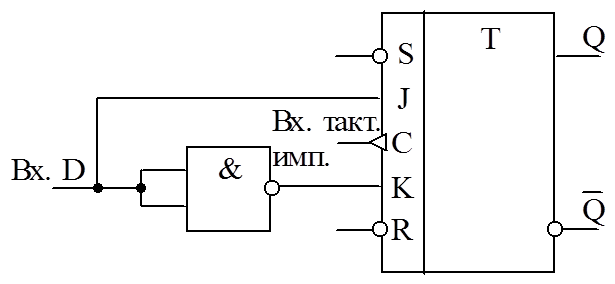

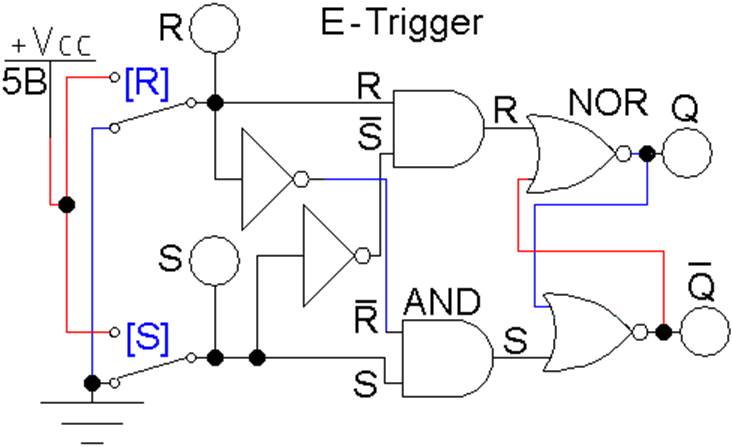

Синхронный RS-триггер

Схема асинхронного RS-триггера проста, но за это приходится заплатить целым рядом недостатков: наличие запрещенного состояния, установка 0 и 1 по отдельным линиям отсутствие синхронизации, низкая помехоустойчивость. Эти недостатки частично устраняются в синхронном RS-триггере, который представляет собой асинхронный RS-триггер к которому добавлена схема синхронизации.

В целом работа данного триггера аналогична, с той поправкой, что при наличии на входе синхронизации низкого логического уровня триггер хранит предыдущее состояние, не реагируя на сигналы по входным линиям, т.е. в этот момент он как минимум гораздо более помехоустойчив.

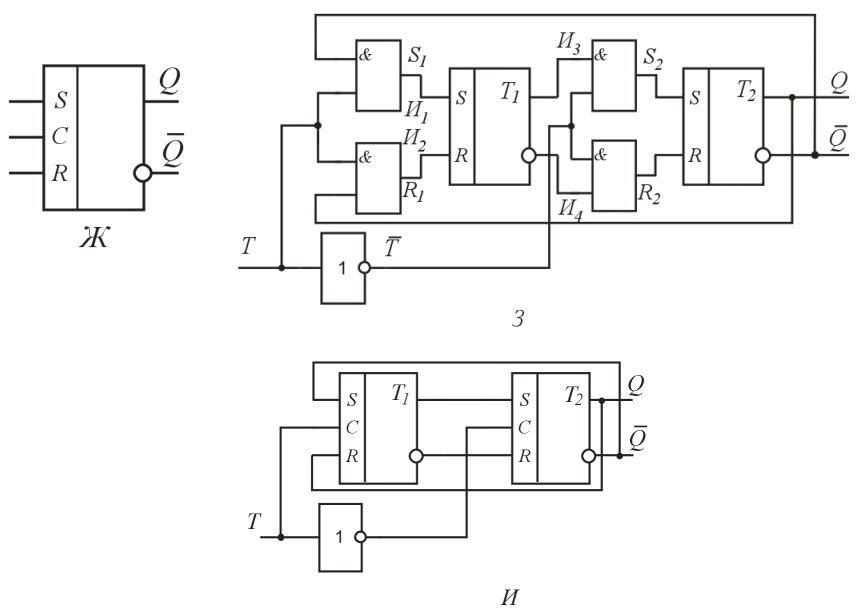

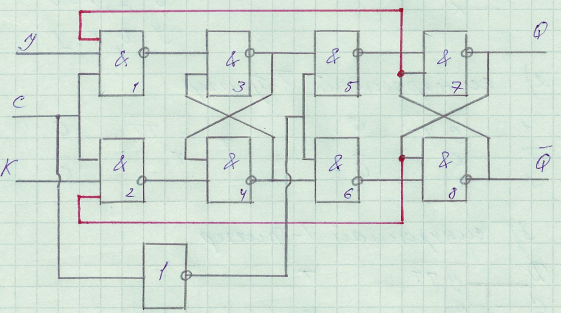

Синхронный статический D-триггер

В основе данного устройства также лежит асинхронный RS-триггер, к которому присоединена схема синхронизации.

Статический D-триггер имеет один информационный вход и один вход синхронизации. Таким образом, устраняется недостаток RS-триггер – установка 0 и 1 по отдельным линиям. При наличии низкого логического уровня на входе синхронизации данное устройство хранит информацию. При подаче на вход синхронизации высокого логического уровня возможна запись информации в устройство.

Таблица истинности синхронного статического D-триггера [2]

Литература

- Отряшенков Ю.М. Юный кибернетик – М.: Детская литература, 1978

- Ямпольский В.С. Основы автоматики и электронно-вычислительной техники – М. Просвещение, 1991

Специально для сайта Радиосхемы – Denev

Форум

Форум по обсуждению материала ТРИГГЕРЫ НА МИКРОСХЕМАХ

Справочник “Цифровые Интегральные Микросхемы”

Справочник “Цифровые Интегральные Микросхемы” [ Содержание ]2.

5.1. RS-триггеры

5.1. RS-триггерыRS-триггер – это триггер с раздельной установкой состояний логического нуля и единицы (с раздельным запуском). Он имеет два информационных входа S и R. По входу S триггер устанавливается в состояние Q=l (/Q=0), а по входу R – в состояние Q = О (/Q = 1).

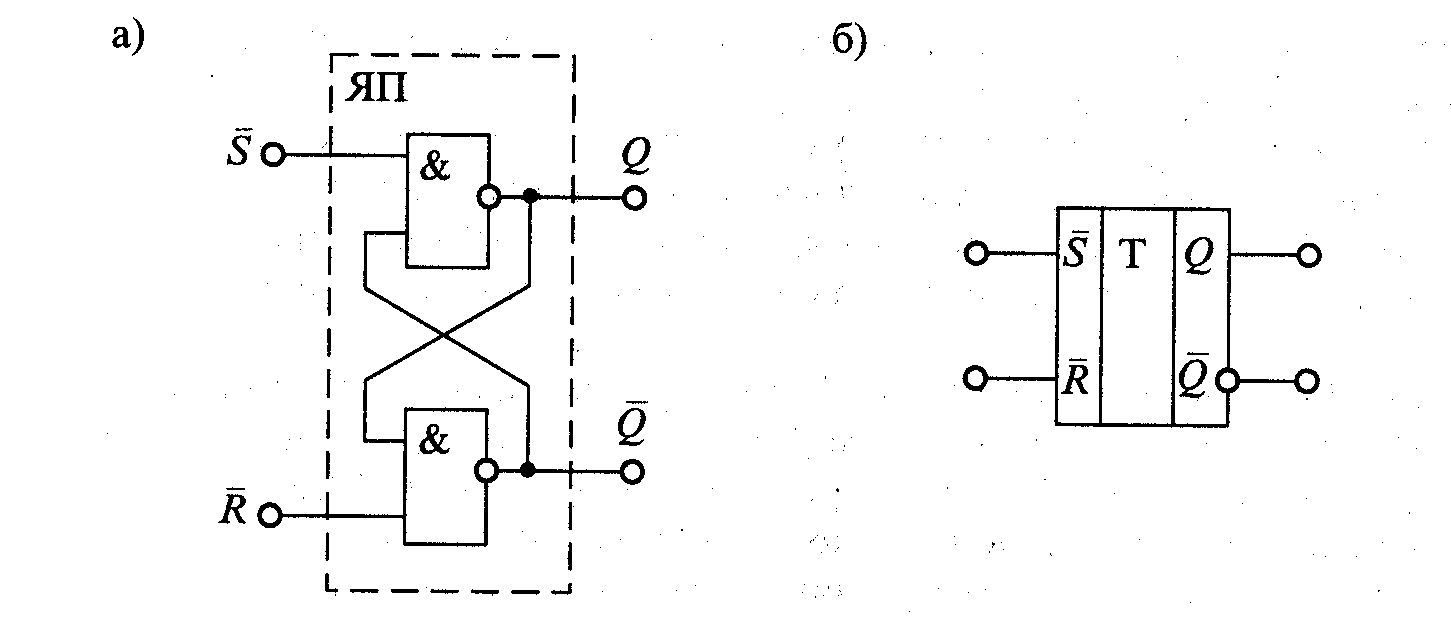

Асинхронные RS-триггеры. Они являются наиболее простыми триггерами. В качестве самостоятельного устройства применяются редко, но являются основой для построения более сложных триггеров. В зависимости от логической структуры различают RS-триггеры с прямыми и инверсными входами. Их схемы и условные обозначения приведены на рис. 2.37. Триггеры такого типа построены на двух логических элементах: 2 ИЛИ-НЕ – триггер с прямыми входами (рис. 2.37, а), 2 И-НЕ – триггер с инверсными входами (рис. 2.37, б). Выход каждого из логических элементов подключен к одному из входов другого элемента, что обеспечивает триггеру два устойчивых состояния.

Рис. 2.37. Асинхронные RS-триггеры: а – RS-триггер на логических элементах ИЛИ-НЕ и условное обозначение; б – RS-триггер на логических элементах И-НЕ и условное обозначение.

Состояния триггеров под воздействием определенной комбинации входных сигналов приведены в таблицах функционирования (состояний) (табл. 2.18).

| Входы | Выходы | ||||

|---|---|---|---|---|---|

| S | R | Логика И-НЕ | Логика ИЛИ-НЕ | ||

| Qn+1 | /Qn+1 | Qn+1 | /Qn+1 | ||

| 0 | 0 | X | Qn | /Qn | |

| 1 | 0 | 0 | 1 | 1 | 0 |

| 0 | 1 | 1 | 0 | 0 | 1 |

| 1 | 1 | Qn | /Qn | X | |

В таблицах Qn (/Qn) обозначены уровни, которые были на

выходах триггера до подачи на его входы так называемых

активных уровней. Активным называют логический уровень,

действующий на входе логического элемента и однозначно

определяющий логический уровень выходного сигнала

(независимо от логических уровней, действующих на остальных

входах). Для элементов ИЛИ-НЕ за активный уровень принимают

высокий уровень – 1, а для элементов И-НЕ – низкий

уровень – О. Уровни, подача которых на один из входов не

приводит к изменению логического уровня на выходе элемента,

называют пассивными. Уровни Qn+1(/Qn+1) обозначают логические

уровни на выходах триггера после подачи информации на его входы.

Для триггера с прямыми входами при подаче на вход комбинации

сигналов S=1, R=0 на выходе получим Qn+1=1 (/Qn+1=0). Такой

режим называют режимом записи логической единицы.

Активным называют логический уровень,

действующий на входе логического элемента и однозначно

определяющий логический уровень выходного сигнала

(независимо от логических уровней, действующих на остальных

входах). Для элементов ИЛИ-НЕ за активный уровень принимают

высокий уровень – 1, а для элементов И-НЕ – низкий

уровень – О. Уровни, подача которых на один из входов не

приводит к изменению логического уровня на выходе элемента,

называют пассивными. Уровни Qn+1(/Qn+1) обозначают логические

уровни на выходах триггера после подачи информации на его входы.

Для триггера с прямыми входами при подаче на вход комбинации

сигналов S=1, R=0 на выходе получим Qn+1=1 (/Qn+1=0). Такой

режим называют режимом записи логической единицы.

Если со входа S снять единичный сигнал, т. е. установить на входе S нулевой сигнал, то состояние триггера не изменится. Режим S=0, R=0 называют режимом хранения информации, так как информация на выходе остается неизменной.

При подаче входных сигналов S=0, R=1 произойдет переключение триггера,

а на выходе будет Qт+1=0 (/Qn+1=1). Такой режим называют режимом записи

логического нуля (режим сброса). При S=R=1 состояние триггера будет

неопределенным, так как во время действия информационных сигналов

логические уровни на выходах триггера одинаковы (Qn+1=/Qn+1=0),

а после окончания их действия триггер может равновероятно принять

любое из двух устойчивых состояний. Поэтому такая комбинация S=R=1

является запрещенной.

Такой режим называют режимом записи

логического нуля (режим сброса). При S=R=1 состояние триггера будет

неопределенным, так как во время действия информационных сигналов

логические уровни на выходах триггера одинаковы (Qn+1=/Qn+1=0),

а после окончания их действия триггер может равновероятно принять

любое из двух устойчивых состояний. Поэтому такая комбинация S=R=1

является запрещенной.

Для триггера с инверсными входами режим записи логической единицы реализуется при /S=0, /R=1, режим записи логического нуля – при /S=1, /R=0. При /S=/R=1 обеспечивается хранение информации. Комбинация входных сигналов /S = /R = 0 является запрещенной.

Микросхема ТР2 включает четыре асинхронных RS-триггера, причем два из

них имеют по два входа установки /S. Управляющим сигналом является уровень

логического нуля (низкий уровень), так как триггеры построены на логических

элементах И-НЕ с обратными связями (т. е. входы инверсные статические).

Установка триггера в состояние высокого или низкого уровня осуществляется

кодом 01 или 10 на входах /S и /R со сменой кода информации. Если на входах /S1 = /S2 = /R = 0, то на выходе Q появится напряжение

высокого уровня – 1. Однако это состояние не будет зафиксировано,

«защелкнуто»; если входные уровни 0 убрать, на выходе Q появится

неопределенное состояние. При подаче на входы /S1 = /S2 = R = 1 напряжение

на выходе останется без изменения. Достаточно на одном из входов /S триггера

установить низкий уровень напряжения – 0, а на входе /R высокий уровень

напряжения – 1, и триггер установится в состояние высокого уровня

Qn+1 = 1. Табл. 2.19 дает состояния одного из триггеров микросхемы TP2.

Если на входах /S1 = /S2 = /R = 0, то на выходе Q появится напряжение

высокого уровня – 1. Однако это состояние не будет зафиксировано,

«защелкнуто»; если входные уровни 0 убрать, на выходе Q появится

неопределенное состояние. При подаче на входы /S1 = /S2 = R = 1 напряжение

на выходе останется без изменения. Достаточно на одном из входов /S триггера

установить низкий уровень напряжения – 0, а на входе /R высокий уровень

напряжения – 1, и триггер установится в состояние высокого уровня

Qn+1 = 1. Табл. 2.19 дает состояния одного из триггеров микросхемы TP2.

| Входы | Выход | |||

|---|---|---|---|---|

| /S1 | /S2 | /S | /R | Qn+1 |

| 1 | 1 | 1 | 1 | Qn |

| 0 | 1 | 0 | 1 | 1 |

| 1 | 0 | |||

| 0 | 0 | |||

| 1 | 1 | 1 | 0 | 0 |

| 0 | 1 | 0 | 0 | 1* |

| 1 | 0 | |||

| 0 | 0 | |||

Временные диаграммы его работы, а также цоколевка представлены на рис. 2.38

Рис. 2.38. Условное обозначение, цоколевка и временные диаграммы работы микросхем типа ТР.

Основные параметры приведены в табл. 2.20б.

Синхронные RS-триггеры. Триггерные ячейки – это основа делителей частоты, счетчиков и регистров. В этих устройствах записанную ранее информацию по специальному сигналу, называемому тактовым, следует передать на выход и переписать в следующую ячейку. Для осуществления такого режима в RS-триггер необходимо ввести дополнительный вход С, который может быть статическим или динамическим, т. е. получим синхронный RS-триггер.

Схема синхронного RS-триггера на логических элементах И-НЕ со статическим управлением записью (вход С – статический) и его условное обозначение приведены на рис. 2.39, а.

Рис. 2.39. Синхронные RS-триггеры: а – синхронный RS-триггер на элементах И-НЕ и условное обозначение;

б – синхронный RS-триггер на элементах ИЛИ-НЕ и условное обозначение.

Элементы DD1.1 и DD1.2 образуют схему управления, а элементы DD1.3 и DD1.4 – асинхронный RS-триггер. Иногда такой триггер называют RST-триггером (если вход С считать тактовым входом Т).

Триггер имеет прямые статические входы, поэтому управляющим сигналом является уровень логической единицы.

Если на вход С подать сигнал логической единицы C=1, то работа триггера аналогична работе простейшего асинхронного RS-триггера. При C=0 входы S и R не оказывают влияние на состояние триггера. Комбинация сигналов S=R=C=1 является запрещенной. Табл. 2.21 отражает состояния такого триггера.

Синхронный RS-триггер, выполненный на элементах ИЛИ-НЕ, будет иметь инверсные статические входы (рис. 2.39,б). Его функционирование будет определяться таблицей состояний при /C=0 (табл. 2.22). Запрещенной комбинацией входных сигналов будет комбинация /S=/R=/C=0.

|

| ||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

Синхронный RS-триггер с динамическим управлением записью функционирует согласно сигналам, которые были на информационных входах S и R к моменту появления перепада на входе С. Схема такого триггера, его условное обозначение даны на рис. 2.40.

Рис. 2.40. Синхронный RS-триггер с динамическим управлением на логических элементах И-НЕ и условное обозначение.

Элементы DD1.1 … DD1.4 образуют схему управления,

а DD1.5 и DD1.6 – асинхронный RS-триггер, выполняющий роль

элемента памяти. У данного триггера входы /S и /R инверсные

статические (управляющий сигнал – уровень логического нуля),

вход С – прямой динамический. Новое состояние триггера устанавливается

положительным перепадом напряжения (от уровня логического нуля до

уровня логической единицы) на входе С в соответствии с сигналами на

информационных входах /S и /R. Функционирование триггера при некоторых

комбинациях входных сигналов можнопроследить с помощью таблицы

состояний (табл. 2.23).

| Входы | Внутренние выходы | Выходы | ||||||

| /S | /R | C | A1 | A2 | A3 | A4 | Q | /Q |

|---|---|---|---|---|---|---|---|---|

| 1 | 1 | X | 0 | 1 | 1 | 0 | 0 | 1 |

| 0 | 1 | X | 1 | 1 | 1 | 0 | 0 | 1 |

| 0 | 1 | _/ | 1 | 0 | 1 | 0 | 1 | 0 |

| 1 | 0 | _/ | 1 | 0 | 1 | 1 | 1 | 0 |

| 1 | 0 | X | 0 | 1 | 1 | 1 | 1 | 0 |

| 1 | 0 | _/ | 0 | 1 | 0 | 1 | 0 | 1 |

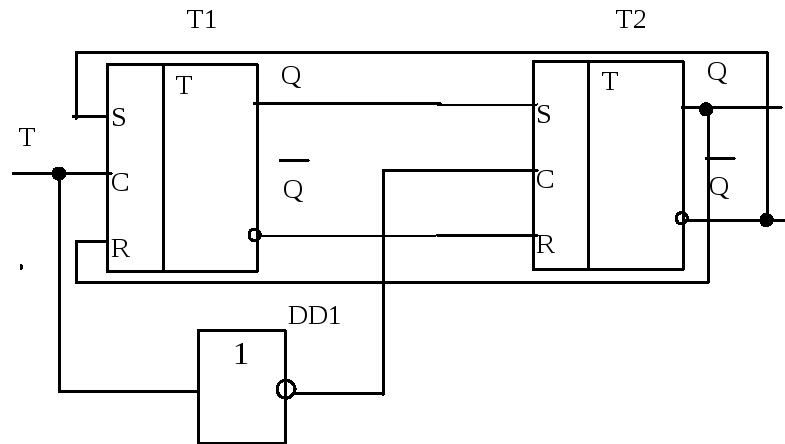

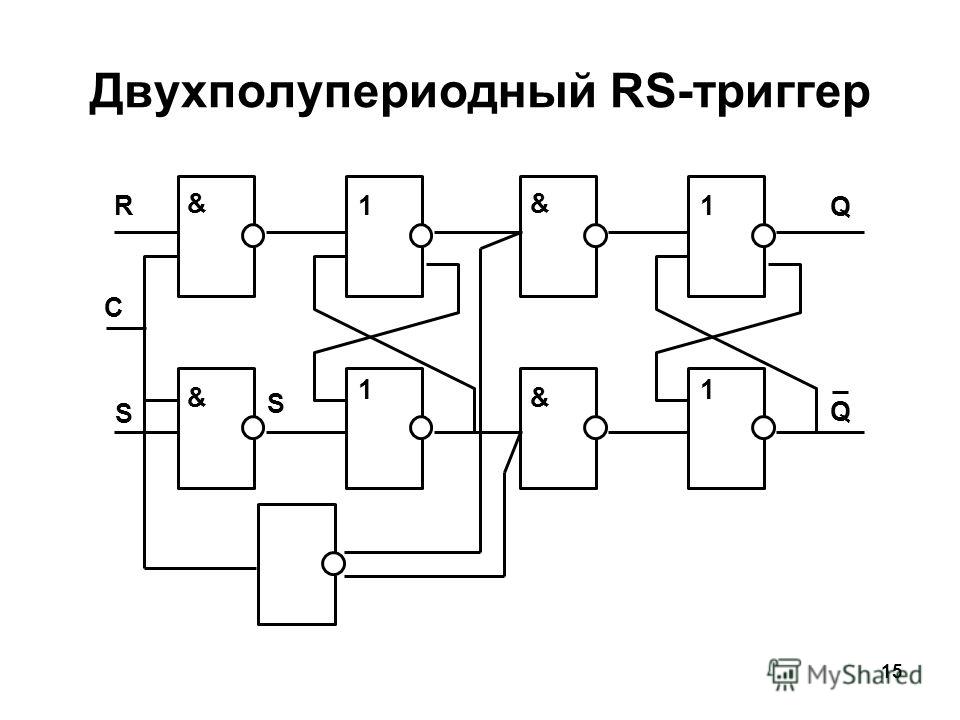

Синхронный двухступенчатый RS-триггер (master-slave,

что переводится «мастер-помощник») состоит из двух синхронных

RS-триггеров и инвертора, рис. 2.41, а. Входы С обоих триггеров

соединены между собой через инвертор DD1.1. Если C=1,

то первый триггер функционирует согласно сигналам на его входах S и R.

Второй триггер функционировать не-может, т. к, у него C=0.

Если C=0, то первый триггер не функционирует, а для второго

триггера C=1, и он изменяет свое состояние согласно сигналам

на выходах первого триггера.

2.41, а. Входы С обоих триггеров

соединены между собой через инвертор DD1.1. Если C=1,

то первый триггер функционирует согласно сигналам на его входах S и R.

Второй триггер функционировать не-может, т. к, у него C=0.

Если C=0, то первый триггер не функционирует, а для второго

триггера C=1, и он изменяет свое состояние согласно сигналам

на выходах первого триггера.

Рис. 2.41. Синхронный двухступенчатый RS-триггер: a – схема триггера на логических элементах И-НЕ;

б – условное обозначение и временные диаграммы тактового импульса.

На рис. 2.41, б показано, что двухступенчатым триггером

управляет полный (фронтом и срезом) тактовый импульс С.

Если каждый из триггеров имеет установку положительным перепадом,

то входная RS-комбинация будет записана в первую ступень в момент

прихода положительного перепада тактового импульса С. В этот момент

во вторую ступень информация попасть не может. Когда придет

отрицательный перепад тактового импульса С, на выходе инвертора

DD1.1 он появится как положительный. Следовательно, положительный

перепад импульса /С перепишет данные от выходов первого триггера

в триггер второй ступени. Сигнал на выходе появится с задержкой,

равной длительности тактового импульса.

Следовательно, положительный

перепад импульса /С перепишет данные от выходов первого триггера

в триггер второй ступени. Сигнал на выходе появится с задержкой,

равной длительности тактового импульса.

Очень часто необходимо использовать триггер для деления частоты входной последовательности импульсов на два, т. е. производить переключение триггера в новое состояние каждым входным импульсом (фронтом или спадом). Такой триггер называют счетным, или T-триггером (от англ. Toggle). Он имеет один управляющий вход Т. В сериях выпускаемых микросхем T-триггеров нет. Но триггер такого типа может быть создан на базе синхронного RS-триггера с динамическим управлением, если прямой выход Q соединить с инверсным входом /S, а инверсный выход /Q соединить с инверсным входом /R. На вход синхронизации С подать входную последовательность импульсов (т. е. это будет T-вход). На рис. 2.42 показана схема такого триггера и временные диаграммы его работы.

Рис. 2.42. T-триггер, его обозначение и временные диаграммы.

Аналогичным образом Т-триггер может быть собран на синхронном двухступенчатом RS-триггере.

RS-триггер

RS-триггер

Радиолюбительские устройства на микросхеме КМОП 4093Базовые схемы и источники питанияНа рис. 1.13 показано, как из двух логических элементов 2И-НЕ ИС 4093 можно собрать RS-триггер. Схема представляет собой бистабильную ячейку, переключаемую импульсами с потенциалом лог. 0.

Рис.1.13. RS-триггер на двух логических вентилях ИС4093

Как видно, схема имеет два выхода: нормальный Q и инверсный. Когда на одном выходе – единица, на другом обязательно будет нуль и наоборот, потому что они комплементарны. Схема имеет два входа: вход установки единицы (S – Set) и вход установки нуля (R – Reset), как показано на рисунке. На входы подаются переключающие сигналы. Удерживающий R-вход соединен с инверсным Q-выходом и удерживающий S-вход соединен с Q-выходом, образуя замкнутую петлю обратной связи для цифровых сигналов. Схема работает следующим образом. Когда “отрицательный” импульс поступает на вход S, выход Q переключается в состояние лог. 1. Так как с этим выходом соединен удерживающий вход R, лог. 1 вызывает появление на выходе Q лог. 0. Но инверсный Q -выход также соединен с удерживающим входом S, образуя цепь обратной связи, побуждающую выход Q оставаться в состоянии лог. 1 даже при исчезновении переключающего импульса.

Схема работает следующим образом. Когда “отрицательный” импульс поступает на вход S, выход Q переключается в состояние лог. 1. Так как с этим выходом соединен удерживающий вход R, лог. 1 вызывает появление на выходе Q лог. 0. Но инверсный Q -выход также соединен с удерживающим входом S, образуя цепь обратной связи, побуждающую выход Q оставаться в состоянии лог. 1 даже при исчезновении переключающего импульса.

Чтобы переключить триггер снова, нужно подать “отрицательный” импульс на вход R. Этот импульс побуждает инверсный выход Q перейти в состояние лог. 1 и, так как этот выход соединен с удерживающим входов S, переводит выход Q в состояние лог. 0. Лог. 0 с выхода Q подается на удерживающий вход R, и после окончания переключающего импульса выходы продолжают оставаться в своих состояниях. Заметим, что схема имеет два стабильных состояния, изменить которые мы можем лишь с помощью “отрицательных” импульсов на входах (R или S). Переключаемая вручную бистабильная ячейка может быть образована подсоединением кнопочных переключателей к входам S и R, как показано на рис. 1.14.

1.14.

Высокое входное сопротивление ИС 4093 позволяет использовать широкий диапазон номиналов резисторов в этой схеме. Обычно они могут меняться от 1 кОм до 10 МОм. Резисторы подают высокий логический уровень на входы, когда выключатели разомкнуты. Без резисторов мы будем иметь неопределенное состояние на входах, когда выключатели разомкнуты, и это может вызвать ошибки в работе схемы. При наличии высокоомных резисторов в этой схеме мы получим бистабильную ячейку, переключаемую прикосновением, как показано на рис. 1.15. Многие схемы в следующих статьях построены на базе этой конфигурации. Можно получить различные модификации этой базовой схемы, используя другие логические элементы в качестве инверторов, и собрать управляемые положительными импульсами RS-триггеры.

Справочник “Цифровые Интегральные Микросхемы”

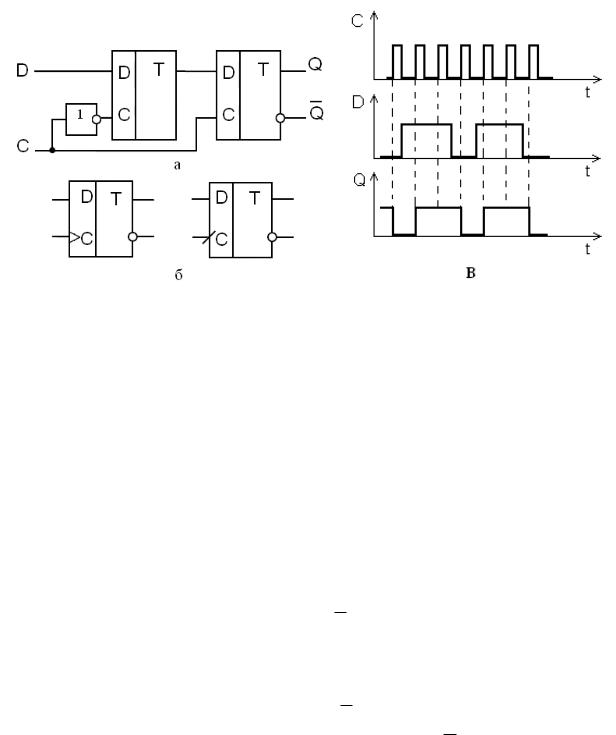

Справочник “Цифровые Интегральные Микросхемы” [ Содержание ]2.5.2. D-триггеры

D-триггером называется триггер с одним информационным

входом, работающий так, что сигнал на выходе после

переключения равен сигналу на входе D до переключения,

т. е. Qn+1=Dn Основное назначение D-триггеров – задержка

сигнала, поданного на вход D. Он имеет информационный

вход D (вход данных) и вход синхронизации С. Вход

синхронизации С может быть статическим (потенциальным)

и динамическим. У триггеров со статическим входом С информация

записывается в течение времени, при котором уровень сигнала C=1.

В триггерах с динамическим входом С информация записывается

только в течение перепада напряжения на входе С. Динамический

вход изображают на схемах треугольником. Если вершина треугольника

обращена в сторону микросхемы (прямой динамический вход), то

триггер срабатывает по фронту входного импульса, если от нее

(инверсный динамический вход) – по срезу импульса. В таком

триггере информация на выходе может быть задержана на один такт

по отношению к входной информации.

е. Qn+1=Dn Основное назначение D-триггеров – задержка

сигнала, поданного на вход D. Он имеет информационный

вход D (вход данных) и вход синхронизации С. Вход

синхронизации С может быть статическим (потенциальным)

и динамическим. У триггеров со статическим входом С информация

записывается в течение времени, при котором уровень сигнала C=1.

В триггерах с динамическим входом С информация записывается

только в течение перепада напряжения на входе С. Динамический

вход изображают на схемах треугольником. Если вершина треугольника

обращена в сторону микросхемы (прямой динамический вход), то

триггер срабатывает по фронту входного импульса, если от нее

(инверсный динамический вход) – по срезу импульса. В таком

триггере информация на выходе может быть задержана на один такт

по отношению к входной информации.

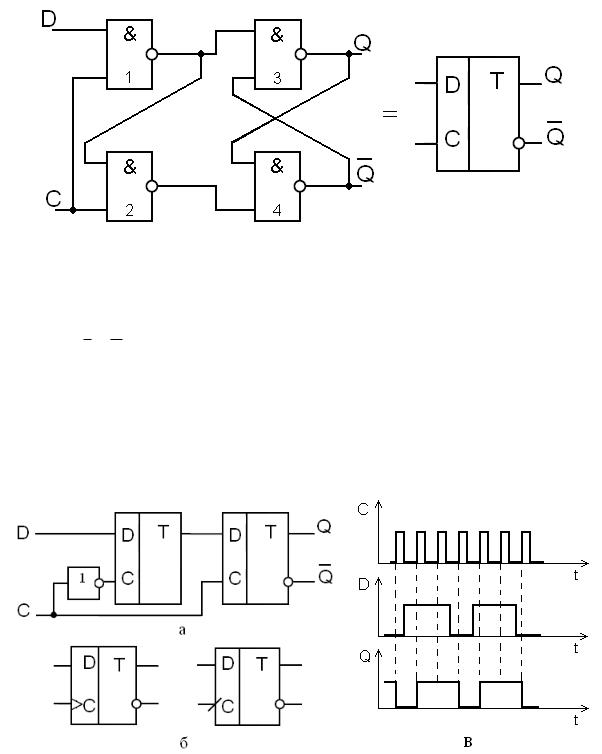

D-триггеры могут быть построены по различным схемам. На рис. 2.43,а

показана схема одноступенчатого D-триггера на элементах И-НЕ и его

условное обозначение. Триггер имеет прямые статические входы

(управляющий сигнал – уровень логической единицы). На элементах DD1.1 и DD1.2

выполнена схема управления, а на элементах DD1.3 и DD1.4 асинхронный RS-триггер.

На элементах DD1.1 и DD1.2

выполнена схема управления, а на элементах DD1.3 и DD1.4 асинхронный RS-триггер.

Рис. 2.43. Синхронный D-триггер: а – схема D-триггера на элементах И-НЕ и условное обозначение;

б – временные диаграммы; в – преобразование синхронного RS-триггера в синхронный D-триггер;

г – временные диаграммы записи и считывания.

Если уровень сигнала на входе С = 0, состояние триггера устойчиво и не зависит от уровня сигнала на информационном входе D. При этом на входы асинхронного RS-триггера с инверсными входами (DD1.3 и DD1.4) поступают пассивные уровни /S = /R = 1.

При подаче на вход синхронизации уровня С = 1 информация на прямом выходе будет повторять информацию, подаваемую на вход D.

Следовательно, при C=0 Qn+1=Qn, а при C=l Qn+1=Dn. Временные диаграммы, поясняющие работу D-триггера, приведены на рис. 2.43,б.

D-триггер возможно получить из синхронного RS-триггера,

если ввести дополнительный инвертор DD1.1 между входами

S и R (рис. 2.43,в). В таком триггере состояние неопределенности

для входов S и R исключается, так как инвертор DD1.1 формирует

на входе R сигнал /S. Временные диаграммы записи в D-триггер

напряжений высокого и низкого входных уровней и их считывание

приведены на рис. 2.43,г. Обязательным условием правильной

работы D-триггера является наличие защитного временного

интервала после прихода импульса на

вход D перед тактовым импульсом (вход С). Этот интервал

времени tn+1-tn зависит от справочных данных на D-триггер.

2.43,в). В таком триггере состояние неопределенности

для входов S и R исключается, так как инвертор DD1.1 формирует

на входе R сигнал /S. Временные диаграммы записи в D-триггер

напряжений высокого и низкого входных уровней и их считывание

приведены на рис. 2.43,г. Обязательным условием правильной

работы D-триггера является наличие защитного временного

интервала после прихода импульса на

вход D перед тактовым импульсом (вход С). Этот интервал

времени tn+1-tn зависит от справочных данных на D-триггер.

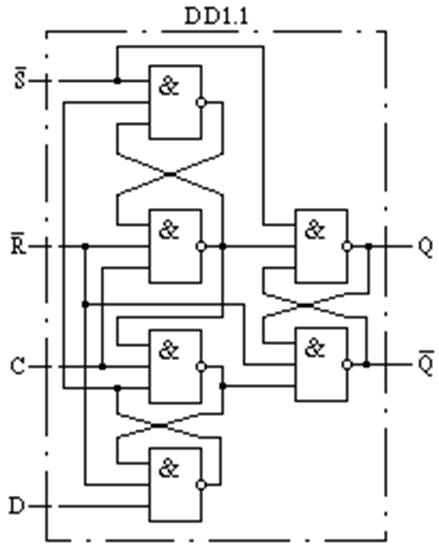

Комбинированные D-триггеры имеют дополнительные входы асинхронной установки логических 0 и 1 – входы S и R. Схема и условное обозначение одного такого триггера представлены на рис. 2.44. Триггер собран на шести элементах И-НЕ по схеме трех RS-триггеров. Входы /S и /R служат для первоначальной установки триггера в определенное состояние.

Рис. 2.44. Комбинированный D-триггер и его условное обозначение.

Если C=D=0, установить /S=0, а /R=1, то элементы

DD1.1 … DD1. 5 будут закрыты, а элемент DD1.6 будет открыт,

т. е. Q=l, /Q=0. При снятии нулевого сигнала со входа /S,

откроется элемент DD1.1, состояние остальных элементов не

изменится. При подаче единичного сигнала на вход С на всех

входах элемента DD1.3 будут действовать единичные сигналы

и он откроется, а элемент DD1.6 закроется: /Q = 1. Теперь

на всех входах элемента DD1.5 действуют единичные сигналы

и он будет открыт: Q = 0. Следовательно, после переключения

триггера сигнал на выходе Q стал равным сигналу на входе D

до переключения: Qn+1=Dn=0. После снятия единичного сигнала

со входа С состояние триггера не изменится.

5 будут закрыты, а элемент DD1.6 будет открыт,

т. е. Q=l, /Q=0. При снятии нулевого сигнала со входа /S,

откроется элемент DD1.1, состояние остальных элементов не

изменится. При подаче единичного сигнала на вход С на всех

входах элемента DD1.3 будут действовать единичные сигналы

и он откроется, а элемент DD1.6 закроется: /Q = 1. Теперь

на всех входах элемента DD1.5 действуют единичные сигналы

и он будет открыт: Q = 0. Следовательно, после переключения

триггера сигнал на выходе Q стал равным сигналу на входе D

до переключения: Qn+1=Dn=0. После снятия единичного сигнала

со входа С состояние триггера не изменится.

D-триггер с динамическим входом C может работать как T-триггер.

Для этого необходимо вход С соединить с инверсным выходом триггера /Q

(рис. 2.45,а). Если на входе D поставить дополнительный двухвходовый

элемент И и инверсный выход триггера /Q соединить с одним из входов

элемента И, а на второй вход подать сигнал EI, то получим T-триггер с

дополнительным разрешением по входу (рис. 2.45,б).

2.45,б).

Рис. 2.45. Схемы преобразования D-триггера. а – преобразование D-триггера в T-триггер и его временная диаграмма работы;

б – преобразование D-триггера в в T-триггер с дополнительным входом расширения EI и его временная диаграмма работы;

Микросхема ТМ2 содержит два независимых комбинированных D-триггера,

имеющих общую цепь питания. У каждого триггера имеется один

информационный вход D, вход синхронизации С и два дополнительных

входа /S и /R независимой асинхронной установки триггера в единичное

и нулевое состояния, а также комплементарные выходы Q и /Q (рис. 2.46).

Логическая структура одного D-триггера (рис. 2.46) содержит следующие

элементы: основной асинхронный RS-триггер (ТЗ), вспомогательный

синхронный RS-триггер (Т1) записи логической единицы (высокого уровня)

в основной триггер, вспомогательный синхронный RS-триггер (Т2) записи

логического нуля (низкого уровня) в основной триггер.

Входы /S и /R – асинхронные, потому что они работают (сбрасывают состояние

триггера) независимо от сигнала на тактовом входе, активный уровень

для них низкий (т. е. инверсные входы /S и /R).

е. инверсные входы /S и /R).

Рис. 2.46. Структура D-триггера микросхемы ТМ2

Асинхронная установка D-триггера в единичное или нулевое состояния осуществляется подачей взаимопротивоположных логических сигналов на входы /S и /R. В это время входы D и С не влияют.

Если на входы /S и /R одновременно подать сигнал низкого уровня (логический нуль), то на обоих выходах триггера Q и /Q будет высокий уровень (логическая единица). Однако после снятия этих сигналов со входов /S и /R состояние триггера будет неопределенным. Поэтому комбинация /S=/R=0 для этих входов является запрещенной.

Загрузить в триггер входные уровни В или Н (т. е. логические 1 или 0) можно,

если на входы /S и /R подать напряжение высокого уровня: /S=/R=1. Сигнал от

входа D передается на выходы триггера при поступлении положительного перепада

импульса на вход С (изменение от низкого* к высокому). Однако, чтобы D-триггер

переключался правильно (согласно таблице состояний, табл. 2.24), необходимо

уровень на входе D зафиксировать заранее, т. е. до прихода перепада на вход С.

Причем этот защитный временной интервал должен быть больше времени задержки

распространения сигнала в триггере (определяется по справочнику).

е. до прихода перепада на вход С.

Причем этот защитный временной интервал должен быть больше времени задержки

распространения сигнала в триггере (определяется по справочнику).

| Режим работы | Входы | Выходы | ||||

|---|---|---|---|---|---|---|

| /S | /R | D | C | Q | /Q | |

| Асинхронная установка | 0 | 1 | X | X | 1 | 0 |

| Асинхронный сброс | 1 | 0 | Х | Х | 0 | 1 |

| неопределенность | 0 | 0 | Х | Х | 1 | 1 |

| Загрузка “1” (установка) | 1 | 1 | 1 | _/ | 1 | 0 |

| Загрузка “0” (сброс) | 1 | 1 | 0 | _/ | 0 | 1 |

Цоколевка микросхемы ТМ2 приведена на рис. 2.47,

а основные параметры см. в табл. 2.20а.

2.47,

а основные параметры см. в табл. 2.20а.

Рис. 2.47. Условное обозначение и

цоколевка микросхемы ТМ2

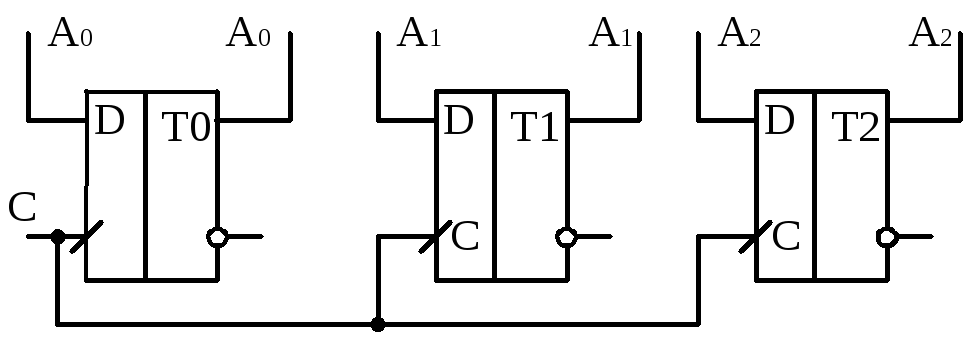

Микросхемы ТM5 и ТМ7 содержат по четыре D-триггера, входы синхронизации

которых попарно соединены и обозначены как входы разрешения загрузки EI.

Если на такой вход разрешения EI подается напряжение высокого уровня,

то информация, поступающая на входы D, передается на выходы триггеров.

При напряжении низкого уровня на входе разрешения EI на выходах триггеров

сохраняются предыдущие состояния (состояние входов D безразлично).

В триггерах будет зафиксирована информация, имевшаяся на входах D, если

состояние входа EI переключить от напряжения высокого уровня к низкому.

Такие триггеры используются в качестве четырехразрядного регистра

хранения информации с непарным тактированием разрядов, а также в

качестве буферной памяти и элемента задержки. Каждый триггер микросхемы

ТМ5 имеет только прямой выход Q, а каждый триггер микросхемы ТМ7 имеет

прямые Q и инверсные /Q выходы. Функциональные схемы, цоколевка,

схема одного D-триггера и временные диаграммы работы приведены

на рис. 2.48, а, основные параметры триггеров даны в

табл. 2.20, состояния триггеров даны в

табл. 2.25.

Функциональные схемы, цоколевка,

схема одного D-триггера и временные диаграммы работы приведены

на рис. 2.48, а, основные параметры триггеров даны в

табл. 2.20, состояния триггеров даны в

табл. 2.25.

Рис. 2.48. Функциональные схемы, цоколевки, структура D-триггера и временные диаграммы микросхем ТМ5, ТМ7.

| Режим работы | Входы | Выходы | ||

|---|---|---|---|---|

| EI | D | Qn+1 | /Qn+1 | |

| Разрешение передачи данных на выход | 1 | 0 | 0 | 1 |

| 1 | 1 | 1 | 0 | |

| Защелкивание данных | 0 | Х | Qn=1 | /Qn=0 |

Микросхемы. TM8 и ТМ9 содержат четыре и шесть D-триггеров соответственно. Они имеют общие входы синхронного сброса /R (установки в состояние низкого уровня)

и входа синхронизации C. Структура ТМ8 и ТМ и их цоколевка приведены на рис. 2.49.

Они имеют общие входы синхронного сброса /R (установки в состояние низкого уровня)

и входа синхронизации C. Структура ТМ8 и ТМ и их цоколевка приведены на рис. 2.49.

Рис. 2.48. Функциональные схемы и цоколевки микросхем ТМ8 и ТМ9.

Триггеры микросхемы ТМ9 имеют только прямые входы Q, а триггеры ТМ8 – прямые и инверсные выходы Q и /Q. На входах C и /R поставлены дополнительные инверторы. Микросхемы К1533ТМ8, К1533ТМ9 имеют повышенную нагрузочную способность, т.е. на каждом из выходов поставлены дополнительные инверторы. Функционрированне триггеров в микросхемах ТМ8 и ТМ9 соответствует таблице состояний (табл. 2.26).

| Режим работы | Входы | Выходы | |||

|---|---|---|---|---|---|

| /R | D | C | Qn+1 | /Qn+1 | |

| Сброс | 0 | X | X | 0 | 1 |

| Загрузка “1” | 1 | 1 | _/ | 1 | 0 |

| Загрузка “0” | 1 | 0 | _/ | 0 | 1 |

Установка всех триггеров в состояние Q = 0 произойдет, когда на

асинхронный вход /R подать напряжение низкого уровня – 0. Входы С и D в это время не действуют. Информацию от входов D можно

загрузить в триггеры, если на вход /R подать напряжение высокого

уровня – 1. Тогда при подаче на вход синхронизации С положительного

перепада напряжения (фронта импульса) и предварительно поданного

на вход D напряжения высокого или низкого уровня появится на

выходе Q высокий или низкий уровень.

Входы С и D в это время не действуют. Информацию от входов D можно

загрузить в триггеры, если на вход /R подать напряжение высокого

уровня – 1. Тогда при подаче на вход синхронизации С положительного

перепада напряжения (фронта импульса) и предварительно поданного

на вход D напряжения высокого или низкого уровня появится на

выходе Q высокий или низкий уровень.

Вьетнамки | Таблица истинности и различные типы

Триггер – это электронная схема с двумя стабильными состояниями, которая может использоваться для хранения двоичных данных. Сохраненные данные можно изменить, применяя различные входные данные. Триггеры и защелки являются фундаментальными строительными блоками систем цифровой электроники, используемых в компьютерах, средствах связи и многих других типах систем. Оба используются в качестве элементов хранения данных. Это основной элемент хранения в последовательной логике. Но сначала давайте проясним разницу между защелкой и шлепанцем.

Флип-флоп с защелкой

Основное различие между защелкой и триггером – это стробирующий или синхронизирующий механизм.

Простыми словами. Триггер срабатывает по фронту, а защелка срабатывает по уровню.

Полное сравнение триггеров с защелкой читайте здесь

Например, поговорим о защелках SR и триггерах SR. В этой схеме, когда вы устанавливаете S как активный, выход Q будет высоким, а Q ’будет низким. Это независимо ни от чего. (Это цепь с активным низким уровнем, поэтому активный здесь означает низкий уровень, но для цепи с активным высоким уровнем активный означает высокий уровень)

Защелка SRТриггер, с другой стороны, является синхронным и также известен как защелка SR с синхронизацией или синхронизацией.

SR Flip-FlopНа этой принципиальной схеме выход изменяется (т. Е. Изменяются сохраненные данные) только тогда, когда вы подаете активный тактовый сигнал. В противном случае, даже если S или R активны, данные не изменятся. Давайте посмотрим на типы шлепанцев, чтобы лучше понять.

SR Вьетнамки

Существует четыре основных типа триггеров, наиболее распространенным из которых является SR-триггер. Эта простая триггерная схема имеет вход установки (S) и вход сброса (R). В этой системе, когда вы устанавливаете «S» как активный, выход «Q» будет высоким, а «Q ‘ »будет низким.После того, как выходы установлены, подключение схемы сохраняется до тех пор, пока «S» или «R» не станут высокими, или пока не будет отключено питание. Как показано выше, он самый простой и легкий для понимания. Два выхода, как показано выше, противоположны друг другу. Таблица истинности SR Flip-Flop выделена ниже.

Эта простая триггерная схема имеет вход установки (S) и вход сброса (R). В этой системе, когда вы устанавливаете «S» как активный, выход «Q» будет высоким, а «Q ‘ »будет низким.После того, как выходы установлены, подключение схемы сохраняется до тех пор, пока «S» или «R» не станут высокими, или пока не будет отключено питание. Как показано выше, он самый простой и легкий для понимания. Два выхода, как показано выше, противоположны друг другу. Таблица истинности SR Flip-Flop выделена ниже.

| S | R | Q | Q ’ |

| 0 | 0 | 0 | 1 |

| 0 | 1 | 0 | 1 |

| 1 | 0 | 1 | 0 |

| 1 | 1 | ∞ | ∞ |

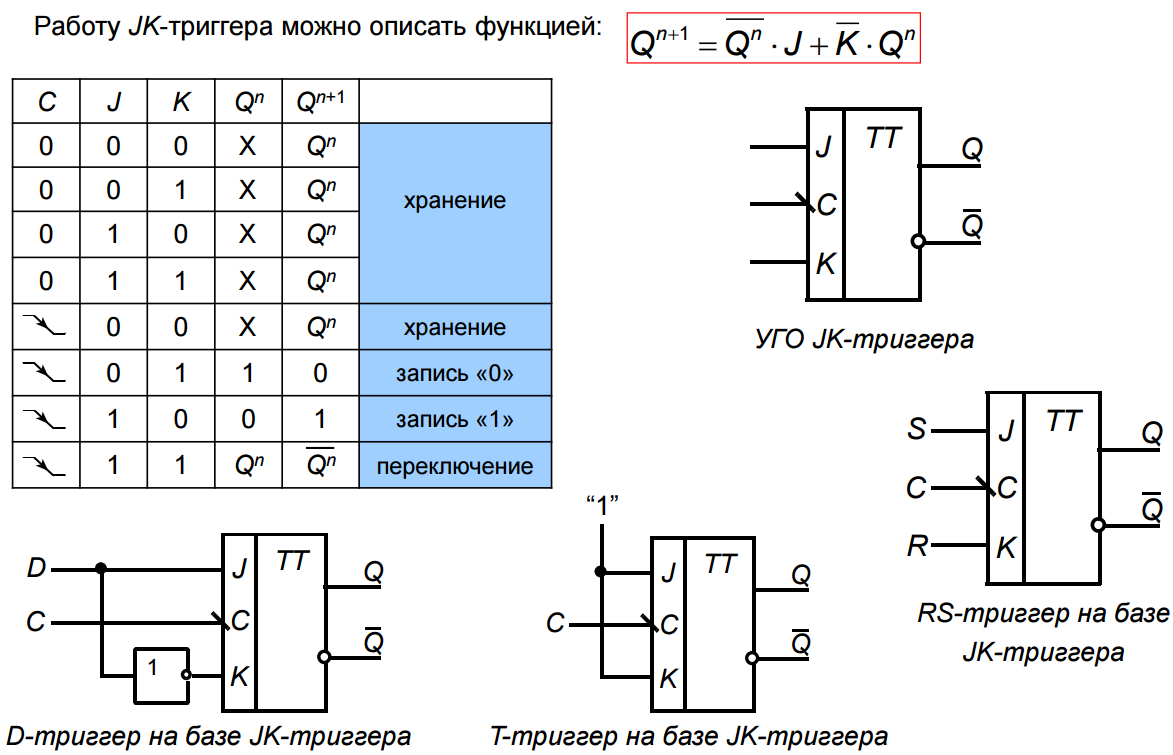

JK Триггер

Из-за неопределенного состояния в триггере SR требуется другой триггер в электронике. Триггер JK является усовершенствованием триггера SR, где S = R = 1 не является проблемой.

Триггер JK является усовершенствованием триггера SR, где S = R = 1 не является проблемой.

Условие входа J = K = 1 дает выход, инвертирующий состояние выхода. Однако при практическом тестировании схемы выходы такие же.

Проще говоря, если входные данные J и K различаются (т.е. высокий и низкий), то выход Q принимает значение J на следующем фронте тактового сигнала. Если J и K низкие, то никаких изменений не происходит. Если J и K оба имеют высокий уровень на фронте тактового сигнала, выход будет переключаться из одного состояния в другое.JK Flip-Flops могут функционировать как Set или Reset Flip-flops

| Дж | К | Q | Q ’ |

| 0 | 0 | 0 | 0 |

| 0 | 1 | 0 | 0 |

| 1 | 0 | 0 | 1 |

| 1 | 1 | 0 | 1 |

| 0 | 0 | 1 | 1 |

| 0 | 1 | 1 | 0 |

| 1 | 0 | 1 | 1 |

| 1 | 1 | 1 | 0 |

Флип-флоп D

Триггер D – лучшая альтернатива, очень популярная в цифровой электронике. Они обычно используются для счетчиков, регистров сдвига и синхронизации входов.

Они обычно используются для счетчиков, регистров сдвига и синхронизации входов.

В этом случае выход может быть изменен только на фронте тактового сигнала, и если вход изменяется в другое время, выход не будет затронут.

| Часы | Д | Q | Q ’ |

| ↓ »0 | 0 | 0 | 1 |

| ↑ »1 | 0 | 0 | 1 |

| ↓ »0 | 1 | 0 | 1 |

| ↑ »1 | 1 | 1 | 0 |

Изменение состояния выхода зависит от нарастающего фронта тактового сигнала.Выход (Q) такой же, как и вход, и может изменяться только по нарастающему фронту тактового сигнала.

T Вьетнамки

T-триггер похож на JK-триггер. По сути, это версия триггеров JK с одним входом. Эта модифицированная форма триггера JK получается путем соединения обоих входов J и K. У него есть только один вход вместе с входом часов.

Эта модифицированная форма триггера JK получается путем соединения обоих входов J и K. У него есть только один вход вместе с входом часов.

Эти триггеры называются T-триггерами из-за их способности дополнять свое состояние (т. Е.) Toggle, отсюда и название Toggle flip-flop.

| т | Q | Q (т + 1) |

| 0 | 0 | 0 |

| 1 | 0 | 1 |

| 0 | 1 | 1 |

| 1 | 1 | 0 |

Применение триггеров

Это различные типы триггеров, используемых в цифровых электронных схемах, и области применения триггеров указаны ниже.

- Счетчики

- Делители частоты

- Регистры сдвига

- Регистры памяти

Эта статья была впервые опубликована 17 августа 2017 г. и обновлена 29 июня 2021 г.

Работа и таблица истинности объяснения

Термин «цифровой» в электронике означает создание, обработку или сохранение данных в виде двух состояний. Два состояния могут быть представлены как ВЫСОКИЙ или НИЗКИЙ, положительный или неположительный, установленный или сброшенный, что в конечном итоге является двоичным.Высокое значение равно 1, а низкое – 0, поэтому цифровая технология выражается в виде серии нулей и единиц. Например, 011010, в котором каждый термин представляет отдельное состояние. Таким образом, этот процесс фиксации в аппаратном обеспечении выполняется с использованием определенных компонентов, таких как защелка или триггер, мультиплексор, демультиплексор, кодеры, декодеры и т. Д., Все вместе называемые Последовательные логические схемы .

Итак, мы собираемся обсудить триггеры , также называемые защелками . Защелки можно также понимать как бистабильный мультивибратор как два стабильных состояния.Как правило, эти схемы защелок могут быть либо активными с высоким, либо с активными с низким уровнем, и они могут запускаться сигналами HIGH или LOW соответственно.

Распространенные типы шлепанцев:

- RS Триггер (RESET-SET)

- D Триггер (данные)

- Джек-шлепок (Джек-Килби)

- T Триггер (тумблер)

Из вышеперечисленных типов только триггеры JK и D доступны в форме интегрированной ИС и также широко используются в большинстве приложений.

Здесь, в этой статье, мы обсудим SR Flip Flop и рассмотрим другие Flip Flop в следующих статьях.

SR Триггер:

SR Flip-flops использовались в обычных приложениях, таких как MP3-плееры, домашние кинотеатры, портативные аудио док-станции и т. Д. Но теперь вместо них используются современные JK и D триггеры из-за универсальности. Защелка SR может быть построена с затвором NAND или с затвором NOR. Любой из них будет дополнять друг друга входом и выходом. Здесь мы используем логические элементы NAND для демонстрации триггера SR.

Когда синхросигнал НИЗКИЙ, входы S и R никогда не будут влиять на выход .Часы должны быть высокими, чтобы входы стали активными. Таким образом, SR-триггер представляет собой управляемую бистабильную защелку, в которой тактовый сигнал является управляющим сигналом. Опять же, это делится на триггер SR, запускаемый положительным фронтом, и триггер SR, запускаемый отрицательным фронтом . Таким образом, выход имеет два стабильных состояния, основанных на входах, которые обсуждались ниже.

Таблица истинности SR Flip-Flop:

Состояние CLK | ВХОД | ВЫХОД | ||

Часы | S ’ | R ’ | Q | Q ’ |

НИЗКИЙ | х | х | 0 | 1 |

ВЫСОКИЙ | 0 | 0 | 0 | 1 |

ВЫСОКИЙ | 1 | 0 | 1 | 0 |

ВЫСОКИЙ | 0 | 1 | 0 | 1 |

ВЫСОКИЙ | 1 | 1 | 1 | 0 |

Размер памяти SR-триггера составляет один бит.S (Set) и R (Reset) являются входными состояниями для триггера SR. Q и Q ’представляют собой выходные состояния триггера. Согласно таблице, в зависимости от входов, выход меняет свое состояние. Но важно учитывать, что все это может происходить только при наличии тактового сигнала.

Мы конструируем триггер SR с использованием логического элемента И-НЕ , который выглядит следующим образом:

Используемая ИС – SN74HC00N (четырехканальный вентиль с положительной И-НЕ с 2 входами).Это 14-контактный корпус, который содержит 4 отдельных логических элемента NAND. Ниже представлена схема контактов и соответствующее описание контактов.

Необходимые компоненты:

- IC SN74HC00 (Quad NAND Gate) – 1 No.

- LM7805 – 1 No.

- Тактильный переключатель – 3

- аккумулятор 9В – 1 шт.

- светодиод (зеленый – 1; красный – 2)

- Резисторы (1 кОм – 2; 220 кОм -2)

- Макет

- Соединительные провода

и пояснение:

Здесь мы использовали IC SN74HC00N для демонстрации SR Flip Flop Circuit, , которая имеет четыре логических элемента NAND внутри.Источник питания IC был ограничен МАКСИМУМОМ 6 В, и данные доступны в таблице данных. Это показано на снимке ниже.

Следовательно, мы использовали регулятор LM7805, чтобы ограничить напряжение питания и напряжение на контактах максимумом 5 В.

Работа SR Flip Flop:

Две кнопки S (Установить) и R (Сброс) являются входными состояниями для триггера SR. Два светодиода Q и Q ’представляют собой выходные состояния триггера. Батарея 9 В действует как вход для регулятора напряжения LM7805.Следовательно, регулируемый выход 5 В используется в качестве напряжения Vcc и вывода на ИС. Таким образом, для разных входов на S ’и R’ соответствующий выход можно увидеть через светодиоды Q и Q ’.

Таблица истинности и соответствующие состояния различаются в зависимости от типа конструкции, которая может использовать вентили И-НЕ или ИЛИ-ИЛИ. Здесь это делается с помощью логических элементов NAND. Штифты S ’и R’ обычно опускаются. Следовательно, состояние входа по умолчанию будет S ’= 0, R’ = 0.

Ниже мы описали все четыре состояния SR Flip-Flop с использованием схемы SR-триггера, выполненной на макетной плате .

Состояние 1: Часы – ВЫСОКИЙ; S ’- 0; R ’- 0; Q – 0; Q ’- 0

Для входов состояния 1 светится КРАСНЫЙ светодиод, указывающий, что Q ’ВЫСОКИЙ, а ЗЕЛЕНЫЙ светодиод показывает, что Q имеет низкий уровень.

Состояние 2: Часы – ВЫСОКИЙ; S ’- 1; R ’- 0; Q – 1; Q ’- 0

Для входов Состояния 2 горит ЗЕЛЕНЫЙ светодиод, указывающий, что Q имеет ВЫСОКИЙ уровень, а КРАСНЫЙ светодиод показывает, что Q ’НИЗКОЕ.

Состояние 3: Часы – ВЫСОКИЙ; S ’- 0; R ’- 1; Q – 0; Q ’- 1

Для входов Состояния 3 светится КРАСНЫЙ светодиод, указывая на то, что Q ’ВЫСОКИЙ, а ЗЕЛЕНЫЙ светодиод показывает, что Q на НИЗКОМ.

Состояние 4: Часы – ВЫСОКИЙ; S ’- 1; R ’- 1; Q – 1; Q ’- 1

Для входов состояния 4 светятся КРАСНЫЙ и ЗЕЛЕНЫЙ светодиоды, указывая на то, что Q&Q ‘ВЫСОКОЕ. Но состояние практически не стабильно. Выходной сигнал становится Q = 1 & Q ’= 0 из-за нестабильности и отсутствия непрерывных часов.

Общие сведения об IC 4043B, IC 4044B CMOS Quad 3-State R / S Latch – Работа и распиновка

В сообщении обсуждается функция распиновки и другие важные характеристики IC 4043.Давайте узнаем о полном описании этой очень интересной микросхемы.

Таблица выводов IC 4043

Технически IC 4043 представляет собой четырехкратную защелку установки / сброса (R / S) с выходом 3 логических состояний.

Если быть более точным, эта микросхема имеет 4 набора входов (то есть 8 входных выводов) и 4 соответствующих одиночных выхода.

Четыре набора входов состоят из 4 пар входов установки / сброса.

Для каждого набора / сброса у нас есть один соответствующий выход.

Все эти входы сброса реагируют на высокие логические сигналы, создавая бистабильный эффект на соответствующих им выходных выводах.

Бистабильный триггер / флоп

Бистабильный триггер, другими словами, высокий импульс на входе “set” делает соответствующий выход высоким из его исходного низкого состояния, а высокий уровень на входе сброса возвращает указанное выше состояние из высокий обратно в низкое состояние.

Следовательно, в основном, чтобы сделать соответствующие выходы высокими, нам нужно применить высокий уровень к их “установленным” входам, а чтобы снова сделать выходы низкими, нам просто нужно подать еще один высокий уровень на их входы сброса.

Распиновка входа и выхода работает очень просто.

В дополнение к этому, IC имеет еще одну интересную распиновку входа OE, которая является общей распиновкой включения выхода.

Функция установки / сброса

Для включения описанных выше действий установки / сброса в ИС этот вход OE должен быть соединен с высоким логическим уровнем или просто с Vdd (контроль питания).

В вышеупомянутой ситуации выход разрешен с заданным функционированием триггера.

Если вход OE соединен с землей, выход замирает и дает ответ с высоким импедансом, то есть не показывает ни низкий выход, ни высокий, а блокирует вход в неотзывчивом заблокированном состоянии, отсюда и название выхода с логическим состоянием 3.

Таким образом, вход OE может использоваться для отключения работы ИС, если это необходимо для конкретного приложения.

Микросхема лучше всего работает при напряжении питания от 5 до 15 В.

Давайте суммируем функции выводов входов и выходов и спецификации IC 4043 со следующими данными:

- от 1Q до 4Q (выводы: 2, 9, 10, 1) 3-х позиционный буферизованный выход защелки

- 1R – 4R (контакты : 3, 7, 11, 15) вход сброса (активный ВЫСОКИЙ)

- 1S до 4S (контакты: 4, 6, 12, 14) установить вход (активный высокий уровень)

- OE (контакт: 5) общий вход разрешения выхода

- VSS (Pin: 8) напряжение заземления

- Н.C. (вывод: 13) не подключен

- VDD (вывод: 16) напряжение питания

Дополнительные обновления:

В этих сообщениях мы пытаемся понять работу IC 4043 и IC 4044, изучая различные спецификации , техническое описание устройств и их распиновка.

В основном оба варианта представляют собой четырехконтактную КМОП-матрицу с 3 состояниями R / S или защелки сброса / установки. Quad означает наличие 4 выходов, которые могут быть установлены или зафиксированы с высоким логическим уровнем посредством управляющего входного сигнала или сброшены до логического нуля с помощью последующего входного сигнала.

Функция 3-х состояний позволяет управлять ИС с использованием 3-х логических схем

Базовый принцип работы IC 4043 и IC 4044 такой же, как указано выше, с той лишь разницей, что IC 4043B является четырехконтактным перекрестно-связанным 3-х состояний Защелка NOR и IC 4044B представляют собой четырехконтактную защелку с тремя состояниями NAND .

Схема расположения выводов

На следующих схемах выводов микросхем показана внутренняя структура и детали расположения выводов устройств:

На схемах выше мы видим, что каждый из типов имеет 4 защелки с одним выходом и 2 отдельными входами RESET / SET.Функция контакта ENABLE для всех входов SET / RESET идентична.

ВЫСОКИЙ логический уровень на выводе ENABLE позволяет состояниям защелок соединяться с соответствующими выходами, низкий логический уровень или 0 отключает состояния защелок их выходов, вызывая полное разомкнутое состояние на выходах.

Защелка NOR, эквивалентные логические схемы защелки NAND

На следующих схемах показаны эквивалентные защелки в виде защелок NOR и NAND, которые присутствуют внутри каждой из 4 защелок отдельных ИС.

Как мы видим, каждый из блоков защелки управляется с помощью 3 логических управляющих входов, а именно SET, RESET и ENABLE, поэтому выход зависит от этих 3 входных состояний. Таблицу истинности для этих 3 логических состояний можно узнать из следующей диаграммы:

В приведенной выше таблице истинности полную форму различных сокращенных символических алфавитов можно понять, как указано ниже: S = установить штифт R = ПИН СБРОСА E = ПИН ВКЛЮЧИТЬ Q = ВЫХОДНОЙ вывод OC = разомкнутая цепь NC = Без изменений

Основные характеристики IC 4043 и IC 4044 суммированы ниже:

Практическое базовое рабочее моделирование контактов SET / RESET и ENABLE

Рабочее описание

Из приведенного выше моделирования GIF мы может понять работу модулей с четырьмя защелками по следующим пунктам:

Когда на вывод SET подается положительный источник питания, выход становится высоким и фиксируется, даже если положительный потенциал снимается с вывода SET, как показано красным Светодиод (с прямым смещением).

Когда на вывод RESET подается положительный импульс, защелка размыкается, и выход постоянно становится НИЗКИМ, даже если положительный вывод снят с вывода RESET. Об этом свидетельствует свечение синего светодиода.

Вышеуказанные операции могут быть реализованы только до тех пор, пока вывод ENABLE IC имеет положительный потенциал питания. При подключении к отрицательному потенциалу или потенциалу земли выход защелки становится открытым и не реагирует на операции SET / RESET.

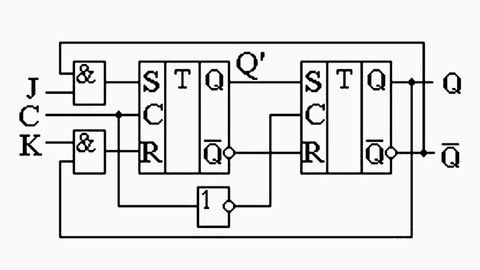

Что такое JK Flip Flop? Принципиальная схема и таблица истинности

Шлепанцы JK Flip Flop – наиболее широко используемые триггеры.Считается универсальной триггерной схемой. Последовательная работа JK-триггера такая же, как и для RS-триггера с тем же входом SET и RESET .

Разница в том, что JK-триггер не определяет недопустимые входные состояния RS-защелки (когда оба S и R равны 1). Название JK Flip Flop было сохранено на имени изобретателя схемы, известной как Jack Kilby.

Базовый символ JK Flip Flop показан ниже:

Базовый триггер RS с затвором NAND имеет две основные проблемы.

- Во-первых, следует избегать условия, когда S = 0 и R = 0.

- Во-вторых, если состояние S или R меняет свое состояние при высоком уровне входного сигнала, правильное действие фиксации не происходит.

Таким образом, для преодоления этих двух проблем RS Flip-Flop был разработан JK Flip-Flop.

JK Flip Flop – это, по сути, RS-триггер со стробированием с добавлением входной схемы синхронизации. Когда оба входа S и R равны логической «1», имеет место недопустимое условие.

Таким образом, чтобы предотвратить это недопустимое состояние, вводится схема синхронизации. JK Flip Flop имеет четыре возможных комбинации входов из-за добавления синхронизированного входа. Четыре входа – это «логическая 1», «логический 0». «Без изменений» и «Переключить».

Принципиальная схема JK Flip Flop показана на рисунке ниже:

Входы S и R бистабильного RS были заменены двумя входами, называемыми входами J и K соответственно.

Здесь J = S и K = R.Логические элементы И с двумя входами триггера RS заменены двумя логическими элементами И-НЕ с 3 входами, при этом третий вход каждого элемента подключен к выходам Q и. Это перекрестное соединение триггера RS используется для переключения. Поскольку два входа заблокированы.

Если схема находится в состоянии «SET», вход J запрещен статусом 0 Q через нижний логический элемент И-НЕ. Точно так же вход K блокируется статусом 0 Q через верхний вентиль И-НЕ в состоянии «СБРОС».

Когда оба J и K имеют логическую «1», переключается JK Flip Flop.

Таблица истинности JK Flip Flop показана ниже.

| J | K | Q | Ǭ | Описание | |

|---|---|---|---|---|---|

| То же, что и для фиксатора RS | 0 | 0 | 0 | 0 | Память Без изменений |

| 0 | 0 | 0 | 1 | ||

| 0 | 1 | 1 | 0 | Сброс Q >> 0 | |

| 0 | 1 | 0 | 1 | ||

| 1 | 0 | 0 | 1 | Установить Q >> 1 | |

| 1 | 0 | 1 | 0 | ||

| Переключатель | 1 | 1 | 0 | 1 | Переключатель |

| 1 | 1 | 1 | 0 |

JK Flip Flop похож на RS-триггер с обратной связью, которая включает только один из его входных терминалов.Он устраняет недопустимое состояние, которое возникает в триггере RS, и переводит входной терминал в режим установки или сброса по одному за раз.

Когда оба входа J и K находятся в состоянии логической «1» одновременно, а тактовый вход находится в состоянии ВЫСОКИЙ импульс, схема переключается из состояния SET в состояние RESET или наоборот. Когда оба терминала находятся в ВЫСОКОМ состоянии, триггер JK действует как триггер с переключателем типа T.

У триггераJK есть недостаток проблемы синхронизации, известный как «RACE». Состояние RACE возникает, если выход Q меняет свое состояние до того, как тактовый импульс тактового входа успевает перейти в состояние ВЫКЛ.

Период синхронизирующего импульса (T) должен быть как можно короче, чтобы избежать проблемы синхронизации.

Это условие не всегда возможно, поэтому был разработан значительно улучшенный триггер под названием Master Salve JK Flip Flop . Это устраняет все проблемы с синхронизацией за счет использования двух последовательно соединенных триггеров RS. Один для схемы «MASTER» , которая запускается по переднему фронту тактового импульса. Другой называется цепью «SLAVE» , которая запускается, когда тактовый импульс находится на заднем фронте.

глюков, триггеров

глюков, триггеровГлюки

Так далеко мы предполагали, что все логические устройства бесконечно быстрые.

Выходы сразу же отражать вводы.

В на практике это не так. Небольшая задержка между изменение логического уровня входа и соответствующее изменение выхода.

Ворота задержки для TTL обычно составляют 5 наносекунд.

20 см провода также задержит сигнал на 1 наносекунду.

А + = ИСТИНА

Однако подумайте, что происходит, когда сигнал A идет от 1 до 0

Это ложный 0 называется глюк.

Эти глюки могут иметь катастрофические последствия, а могут и не иметь.

Это можно спроектировать схемы без сбоев. Это требует дополнительное оборудование и значительные усилия.

Другой подход заключается в разработке схем, нечувствительных к сбоям. Ждать фиксированное время после смены – за которое глюки уйдут.

Это идея – это основа для тактовых схем, к которой мы вернемся позже.

Память

Обратная связь

Если мы зацикливаем выход схемы обратно на ее вход, у нас есть Условие называется обратной связью, и получены некоторые интересные результаты.

Это цепь будет быстро колебаться

Will в конце концов остановитесь на одном входе 0, а на другом 1 (в любом случае)

RS Триггер

Рассмотреть что происходит, когда S и R равны 0

Если Вопрос 0:

г. top NOR будет иметь 0 0 в качестве входных данных и будет выводить 1

г. нижний NOR будет иметь 1 0 в качестве входов и будет выводить 0

=> состояние стабильное

если Вопрос 1:

г. top NOR будет иметь 0 1 в качестве входов и выведет 0

г. нижний NOR будет иметь 0 0 в качестве входов и будет выводить 1

=> состояние стабильное

Если S переключается на 1

г. top NOR будет иметь 1 X в качестве входов и выведет 0

г. нижний NOR будет иметь 1 0 в качестве входов и будет выводить 1

=> Q принудительно принимает значение 1 (S означает Set)

Если R переключается на 1

г. нижний NOR будет иметь 1 X в качестве входов и будет выводить 0

=> Q принудительно принимает значение 0 (R означает сброс)

RS Триггеры полезны для снятия блокировки переключателя.

Переключатели совершать и ломать несколько раз, находясь в тесном контакте.

Q будет установлен в 1, если переключатель контактирует с S

Q останется на 1, несмотря на включение / отключение S, пока переключатель не коснется R

Схемы может использовать часы для выдачи тактовых импульсов. Уровни логики можно прочитать на тактовый импульс, которому разрешено повышаться только при возникновении глюков. навряд ли.

г. RS Flip-flop можно синхронизировать.

г. выход логических элементов И будет отражать только S и R, когда Часы равны 1

.Когда Часы равны 0, выходы логических элементов И всегда равны 0

X выход RS-триггера обычно

Один Проблема с RS-триггером – это то, что происходит, когда R и S равны 1.

В в этом состоянии единственным стабильным состоянием является как Q и 0!

Если оба R и S возвращаются к 0 одновременно Q произвольно переходит к 1 или 0

иначе Q будет отразите, какой из них вернулся к 0 последним.

Тактовый D-триггер

D-триггер устраняет эту двусмысленность

Часы теперь можно рассматривать как стробоскоп. Одиночный тактовый импульс.

Когда строб высокий, значение D будет передано на Q

Q будет оставаться на этом значении до тех пор, пока строб не вернется в высокое состояние.

The D Триггер действует как простая 1-битная память.

Как описанный, этот тип триггера – это уровень срабатывания . Это зависит от того, находится ли стробоскоп или часы в высоком состоянии.

В практиковать это не так уж и хочется. Лучше передать значение D на триггер при изменении строба с 0 на 1

Это называется , край сработал.

Край триггерные шлепанцы гораздо более распространены.

Они может быть либо 0 -> 1 нарастающий фронт, или 1-> 0 задний край

Тактовый шлепанец J-K

Скорее чем устранение двусмысленности триггера RS, как в D шлепанцы, шлепанцы JK используют это.

Дж эквивалентно s. Когда J = 1 => Q становится 1

К эквивалентно R. Когда К = 1 => Q становится 0

Когда J = K = 1 => Q становится

JK-триггер переключает выход , когда J = K = 1.

Дано обычные часы и J = K = 1 Q выход будет тактовым с половинной частотой.

Регистр

ср построить регистр, соединив группу D-триггеров

Все триггеры загружаются одновременно из данных в строках

Автобус

А шина – это общий набор проводов, соединяющих несколько устройств. все вместе.

Автобусы используются для соединения линий данных и адреса между компьютерами, память и устройства ввода-вывода.

Один Проблема с обычными логическими компонентами в том, что их выходы всегда активный – либо 1, либо 0 (5V или Gnd).

Если мы соединяем выход двух ворот вместе, где один выход равен 0 а другой – 1, тогда результат будет где-то между

Если мы хотим использовать автобусную архитектуру, мы должны убедиться, что только один устройство одновременно выдает логический сигнал 0 или 1

Все другие устройства должны перейти в состояние высокого импеданса

ie они выглядят так, как будто они вообще не подключены.

Трехсторонний устройства имеют такую возможность.

А Tri-State Устройство похоже на обычные ворота, но с дополнительными возможность перехода в этот автономный режим .

В устройства с тремя состояниями линия разрешения выхода OE управляет выходами в это третье состояние, а не в логическое состояние 0, как ранее.

Нет все устройства трехступенчатые. Для подключения этих устройств к шине нам понадобится чтобы установить микросхему драйвера с тремя состояниями между устройством и шиной.

А драйвер с тремя состояниями просто отправляет свой вход на свой выход, но также имеет Вход OE, чтобы выход был «не подключен».

Вьетнамки

Вьетнамки выдержки из:http://www.elec.uq.edu.au/~3e211/pracs/prac2/prac2.htm Кафедра компьютерных наук и электротехники Университет Квинсленда Сент-Люсия Qld 4072 Австралия

Элементы памяти в последовательной схеме называются триггерами . Шлепки схема имеет два выхода, один для нормального значения и один для дополнительного значения сохраненный бит.Двоичная информация может входить в триггер разными способами и вызывать к разным типам шлепанцев.

Введение – Базовая схема триггера

Схема триггера может быть построена из двух вентилей И-НЕ или двух вентилей ИЛИ-НЕ. Эти триггеры показаны на рисунках 2 и 3. Каждый триггер имеет два выхода, Q и Q ‘, и два входа, , набор и сброс . Этот тип триггера обозначается как SR триггер или Защелка SR .Триггер на рисунке 2 имеет два полезных состояния. Когда Q = 1 и Q ‘= 0, он находится в установленном состоянии (или в состоянии 1). Когда Q = 0 и Q ‘= 1, он находится в состоянии очистки (или 0-состояние). Выходы Q и Q ‘дополняют друг друга и называются нормальный и дополнительный выходы соответственно. Двоичное состояние триггера принимается равным быть значением нормального вывода.

Когда 1 применяется к обоим входам установки и сброса триггера в На рисунке 2 выходы Q и Q ‘равны 0.Это условие нарушает тот факт, что оба выхода дополняют друг друга. При нормальной работе это условия следует избегать, убедившись, что единицы не применяются к обоим входам одновременно.

(а) Логическая схема

(б) Таблица истинности

Рисунок 2. Базовая триггерная схема с вентилями ИЛИ-НЕ

(а) Логическая схема

(б) Таблица истинности

Рисунок 3. Базовая схема триггера с вентилями NAND

Базовая триггерная схема NAND на рисунке 3 (a) работает с входами обычно на 1, если не нужно менять состояние триггера. 0 применяется мгновенно на вход набора заставляет Q перейти к 1 и Q ‘перейти к 0, помещая триггер в набор штат. Когда оба входа переходят в 0, оба выхода переходят в 1. Этого условия следует избегать. в нормальном режиме работы.

Назад к содержанию

Введение – тактовый SR Flip-Flop

Триггер SR с синхронизацией, показанный на рисунке 4, состоит из базового ИЛИ триггер и два логических элемента И.Выходы двух логических элементов И остаются равными 0 до тех пор, пока тактовый импульс (или CP) равен 0, независимо от входных значений S и R. Когда идет тактовый импульс на 1, информация от входов S и R проходит к базовому триггеру. С обоими S = 1 и R = 1, появление тактового импульса приводит к тому, что оба выхода на мгновение переходят в 0. Когда импульс удален, состояние триггера является неопределенным, т. Е. Любое состояние может возникнуть, в зависимости от того, остается ли вход установки или сброса триггера на 1 больше. чем переход к 0 в конце импульса.

(а) Логическая схема

(б) Таблица истинности

Рисунок 4. Триггер SR с синхронизацией

Назад к содержанию

Введение – D-триггер