Новиков Ю.В. Основы цифровой схемотехники

Новиков Ю.В. Основы цифровой схемотехники

Предисловие

Цель этой книги – помочь в изучении основ цифровой схемотехники любому желающему – от студента до профессионала. Причем речь в данном случае идет не о физических основах электроники, не о технологии производства электронных компонентов, не об электронике или схемотехнике вообще, а именно о цифровой схемотехнике с ее специфическими особенностями.

В книге рассмотрены многие важные вопросы цифровой схемотехники, которым в литературе обычно уделяется недостаточно внимания. Видимо, авторы книг счиrают их чем-то само собой разумеющимся или полагают, что читатели сами должны сформулировать эти вопросы и сами же найти на них ответы. В результате нередки случаи, когда даже выпускники институтов по специальностям, связанным с электроникой, не могут самостоятельно разработать более или менее сложное нестандартное цифровое устройство. После изучения данной книги читатель будет обладать необходимыми навыками для проектирования как простейших узлов, так и довольно сложных устройств.

Книга написана сжато, последовательно и доступно и требует минимального обращения к другим источникам. Часть материала, представленного в ней, написана на основе лекций, читаемых автором в МИФИ.

Конечно, в такой небольшой книге невозможно рассмотреть все компоненты цифровой электроники и все приемы проектирования цифровой схемотехники. Предполагается, что она станет первой в серии книг по цифровой схемотехнике. В последующих книгах серии будут рассмотрены, в частности, следующие темы:

- схемотехника устройств на основе программируемой логики;

- схемотехника микропроцессорных устройств;

- схемотехника устройств на основе микроконтроллеров;

- схемотехника персональных компьютеров;

- схемотехника компьютерных систем измерения, контроля и управления;

- аппаратно-программные средства отладки и контроля цифровых устройств;

- программные средства проектирования цифровых устройств.

…

Основы цифровой схемотехники

ОГЛАВЛЕНИЕ

Введение

Глава 1. Философия цифровой

электроники

Философия цифровой

электроники

1.1. Аналог или цифра?

1.2. Уровни представления цифровых устройств

1.3. Входы и выходы цифровых микросхем

1.4. Основные обозначения на схемах

1.5. Серии цифровых микросхем

1.6. Корпуса цифровых микросхем

1.7. Двоичное кодирование

1.8. Функции цифровых устройств

Глава 2. Применение логических элементов

2.1. Инверторы

2.2. Повторители и буферы

2.3. Элементы И, И-НЕ, ИЛИ, ИЛИ-НЕ

2.4. Элементы Исключающее ИЛИ

2.6. Триггеры Шмитта

Глава 3. Применение комбинационных микросхем

3.1. Дешифраторы и шифраторы

3.2. Мультиплексоры

3.3. Компараторы кодов

3.4. Сумматоры

Сумматоры

3.5. Преобразователи кодов

3.6. Одновибраторы и генераторы

Глава 4. Применение триггеров и регистров

4.1. Триггеры

4.1.1. Принцип работы и разновидности триггеров

4.1.2. Основные схемы включения триггеров

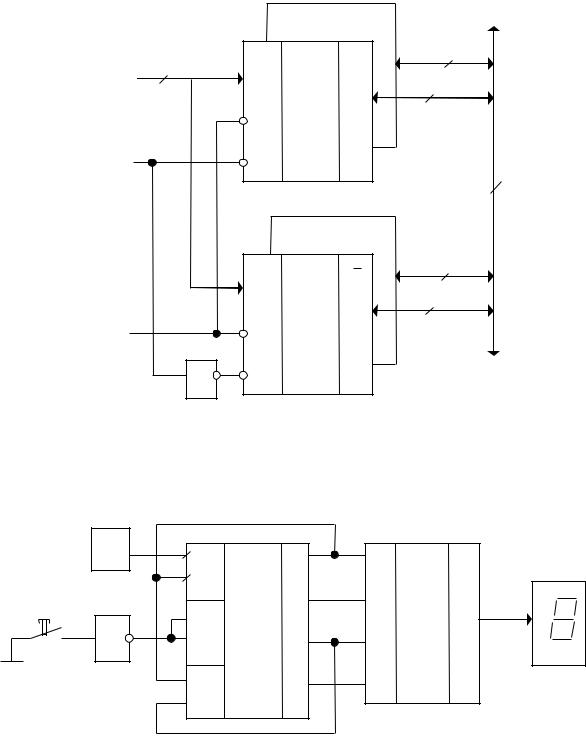

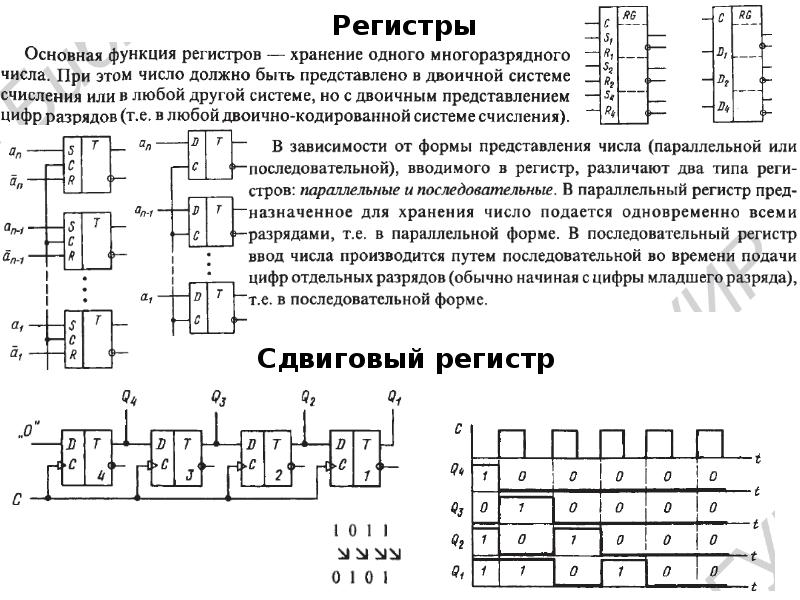

4.2. Регистры

4.2.1. Регистры, срабатывающие по фронту

4.2.2. Регистры, срабатывающие по уровню

4.2.3. Сдвиговые регистры

Глава 5. Применение счетчиков

5.1. Асинхронные счетчики

5.2. Синхронные счетчики с асинхронным переносом

5.3. Синхронные счетчики

Глава 6. Применение микросхем памяти

6.1. Постоянная память

6.1.1. ПЗУ как универсальная комбинационная микросхема

6.1.2. ПЗУ в генераторах импульсных последовательностей

6. 1.3. Микропрограммные автоматы на ПЗУ

1.3. Микропрограммные автоматы на ПЗУ

6.2. Оперативная память

6.2.1. ОЗУ для временного хранения информации

6.2.2. ОЗУ как информационный буфер

6.2.3. Улучшение параметров ОЗУ

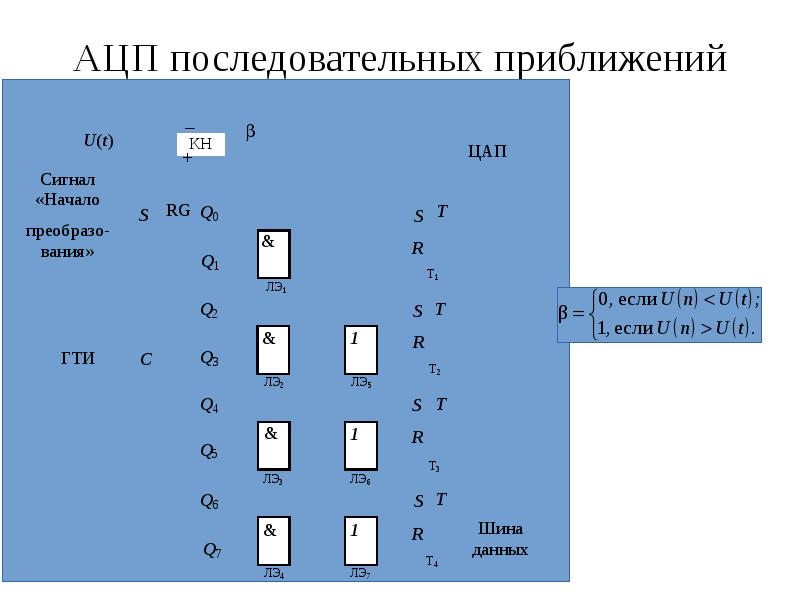

Глава 7. Применение микросхем ЦАП и АЦП

7.1. Применение ЦАП

7.2. Применение АЦП

8.1. Разработка клавиатуры

8.2. Разработка вычислителя контрольной суммы

8.3. Разработка логического анализатора

8.4. Разработка генератора аналоговых сигналов

Приложение. Микросхемы, параметры, сигналы

Список литературы

Словарь терминов и сокращений

ВВЕДЕНИЕ

Цифровая электроника в настоящее время все

более и более вытесняет традиционную аналоговую. Ведущие фирмы, производящие

самую разную электронную аппаратуру, все чаще заявляют о полном переходе на

цифровую технологию. Причем это относится как к бытовой технике (аудио-,

видеоаппаратура, средства связи), так и к профессиональной технике

(измерительная, управляющая аппаратура). Ставшие уже привычными персональные

компьютеры также полностью реализованы на цифровой электронике. Видимо, в ближайшем

будущем полностью аналоговые устройства будут применяться только в тех

случаях, когда требуются уникальные, рекордные характеристики.

Ведущие фирмы, производящие

самую разную электронную аппаратуру, все чаще заявляют о полном переходе на

цифровую технологию. Причем это относится как к бытовой технике (аудио-,

видеоаппаратура, средства связи), так и к профессиональной технике

(измерительная, управляющая аппаратура). Ставшие уже привычными персональные

компьютеры также полностью реализованы на цифровой электронике. Видимо, в ближайшем

будущем полностью аналоговые устройства будут применяться только в тех

случаях, когда требуются уникальные, рекордные характеристики.

Между тем, литературы, позволяющей самостоятельно изучить основы и главные методы цифровой схемотехники, освоить основные практические приемы проектирования цифровых устройств, явно недостаточно. Книги, которые претендуют на освещение основ цифровой схемотехники, можно разделить на три большие группы.

К первой группе относятся книги, которые

стремятся охватить всю электронику в целом (как цифровую, так и аналоговую).

Ко второй группе относятся книги,

посвященные цифровым микросхемам и их применению. Эти книги стремятся описать

как можно более подробно все имеющиеся микросхемы, поэтому обязательно

содержат большой справочный материал. Однако в любом случае приводимые в них

справочные данные далеко не полны и к тому же неизбежно содержат большое

количество ошибок.

Наконец, третья группа книг описывает

готовые цифровые устройства различного назначения. В основном такие книги

рассчитаны на «радиолюбителей», хотя, что подразумевается под этим понятием,

обычно не совсем понятно. Среди тех, кто называют себя радиолюбителями,

немало прекрасных разработчиков, а среди дипломированных профессионалов

встречаются те, кто не может разработать даже простейшей схемы.

К недостаткам многих существующих книг

можно отнести также чрезмерное увлечение описание тонкостей физических процессов,

лежащих в основе цифровой электроники, и подробное рассмотрение особенностей

технологии микросхем. Конечно, все это тоже нужно, полезно, интересно, но с

самой схемотехникой связано не жестко, не прямо и не слишком сильно.

Разработчик цифровой аппаратуры в подавляющем большинстве случаев работает с

микросхемами как с «черным ящиком», ему не слишком важно, что происходит

внутри, как реализуется та или иная функция микросхемы.

Наконец, еще одним недостатком книг о цифровой схемотехнике можно назвать стремление охватить в одной книге все области цифровой электроники: от логических элементов до компьютеров и других сложных электронных систем. В результате все вопросы рассматриваются недостаточно глубоко, и до практики разработки дело не доходит. К тому же проектирование интеллектуальных устройств довольно сильно отличается от проектирования устройств на жесткой логике, они порой требуют применения совершенно разных подходов. Поэтому их целесообразно рассматривать в различных книгах.

Данная книга посвящена самым основам

цифровой схемотехники, ее азбуке, ее основным методам, подходам и приемам.

Отличие ее состоит в том, что она может дать представление о цифровой

схемотехнике даже тем читателям, которые имеют слабое представление об

электронике вообще. Впрочем, это вовсе не означает, что книга посвящена

только самым общим, неконкретным, отвлеченным вопросам. Наоборот, она

призвана сформировать действительно хорошего проектировщика, способного

строить высокоэффективные цифровые системы самой различной сложности и четко

представляющего себе взаимосвязь всех процессов в этих системах сверху донизу.

Конечно, чтобы стать таким классным специалистом, нужны определенные

способности, даже талант, но строить простейшие цифровые устройства, пусть и

не оптимальные, не уникальные, но полезные и вполне работоспособные, способен

практически каждый человек. Хотелось бы надеяться, что данная книга окажет в

этом деле действенную помощь.

Впрочем, это вовсе не означает, что книга посвящена

только самым общим, неконкретным, отвлеченным вопросам. Наоборот, она

призвана сформировать действительно хорошего проектировщика, способного

строить высокоэффективные цифровые системы самой различной сложности и четко

представляющего себе взаимосвязь всех процессов в этих системах сверху донизу.

Конечно, чтобы стать таким классным специалистом, нужны определенные

способности, даже талант, но строить простейшие цифровые устройства, пусть и

не оптимальные, не уникальные, но полезные и вполне работоспособные, способен

практически каждый человек. Хотелось бы надеяться, что данная книга окажет в

этом деле действенную помощь.

Книга ни в коем случае не претендует на

то, чтобы заменить собой справочники по микросхемам, хотя в ней и

разъясняются функции многих микросхем. Главное, чему уделено внимание — это

применение микросхем для различных задач (причем как стандартное применение,

так и не стандартное), а также приемы объединения, комбинирования микросхем,

позволяющие создавать разнообразные узлы, устройства и системы.

Материал данной книги представляет собой тот необходимый минимум знаний который должен иметь и которым должен свободно и активно пользоваться каждый профессиональный разработчик цифровой аппаратуры. Любые другие, дополнительные знания, конечно же, не повредят, но заменить собой то, что изложено здесь, они не смогут.

Возможно, подход, предлагаемый в данной книге, несколько отличается от общепринятого. Возможно также, что используемый набор терминов не полностью совпадает со стандартным (отечественные стандарты слишком часто меняются). Но главное — это научить проектировать цифровые устройства и системы, а какие для этого используются подходы и термины, наверное, не слишком принципиально.

Книга написана на основе многолетнего

личного опыта автора по разработке цифровых устройств, а также на базе

материала учебных курсов, читаемых автором, доцентом кафедры электроники Московского

инженерно-физического института (МИФИ).

Несколько слов о структуре книги.

Первая глава рассматривает основополагающие принципы цифровой электроники, знакомит с терминологией и основными правилами оформления схем.

Главы со второй по шестую посвящены основным базовым элементам цифровых устройств, типовым и нестандартным схемам их включения. Практически все приведенные схемы проверялись автором на практике. Микросхемы описаны начиная с самых простейших логических элементов в порядке усложнения через комбинационные микросхемы, триггеры, регистры, счетчики до микросхем памяти. Каждая глава включает в себя множество примеров включений микросхем, как рассматриваемых в данной главе, так и рассмотренных в предыдущих главах.

Седьмая глава содержит краткие сведения

о цифро-аналоговых и аналого-цифровых преобразователях и основных методах их

включения в аналого-цифровых устройствах. Без этих сведений книга была бы

неполна.

В восьмой главе приводятся примеры нескольких сравнительно сложных цифровых устройств с подробным описанием всех этапов проектирования и принципов работы и взаимодействия всех узлов и микросхем. Цель этого не в том, чтобы читатель повторил данные устройства, а в том, чтобы на практике показать приемы проектирования, которые затем позволят строить любые другие цифровые устройства.

В приложении приведены таблицы параметров микросхем, таблицы основных обозначений микросхем и сигналов, таблицы соответствия отечественных и зарубежных микросхем. В конце книги имеется подробный словарь терминов и сокращений цифровой схемотехники.

В книгу не вошли материалы по основам

микропроцессорной техники, по принципам устройства и применения микроконтроллеров

и персональных компьютеров, по основам работы с программируемыми микросхемами

(ПЛИС), по методам контроля и отладки цифровых устройств, а также по

программным средствам, предназначенным для проектирования цифровых устройств

и систем. Все эти вопросы планируется рассмотреть в других книгах данной

серии.

Все эти вопросы планируется рассмотреть в других книгах данной

серии.

Новиков Ю. В. Основы цифровой схемотехники. Базовые элементы и схемы. Методы проектирования. — М.: Мир, 2001. — 379 с, ил. — (Современная схемотехника) :: Библиотека технической литературы

Книга представляет собой учебник по основам цифровой схемотехники. Рассматриваются основы схемотехники цифровых устройств, которыми должен свободно владеть и активно пользоваться каждый профессиональный разработчик цифровой аппаратуры. Обсуждается функционирование и взаимодействие всех основных типов цифровых микросхем — от самых простых до самых сложных. Описываются модели и уровни представления цифровых микросхем, используемых при проектировании цифровых электронных систем, способы оптимального построения высокоэффективных цифровых систем самой различной степени сложности. Книга позволяет освоить азбуку цифровой схемотехники даже читателям с начальным уровнем знаний по электронике. Усвоению материала помогает большое количество конкретных примеров построения самых различных цифровых устройств.

Усвоению материала помогает большое количество конкретных примеров построения самых различных цифровых устройств.

Для студентов, преподавателей и профессиональных разработчиков цифровых электронных систем.

ОГЛАВЛЕНИЕ

Предисловие …………………………………. 7

Введение ……………………………………. 8

Глава 1. Философия цифровой электроники…………… 13

1.1. Аналог или цифра?………………………… 13

1.2. Модели и уровни представления цифровых устройств 17

1.3. Входы и выходы цифровых микросхем…………. 24

1.4. Основные обозначения на схемах …………….. 32

1.5. Серии цифровых микросхем…………………. 37

1.6. Корпуса цифровых микросхем……………….. 43

1.7. Двоичное кодирование …………………….. 44

1.8. Функции цифровых устройств……………….. 50

Глава 2. Применение логических элементов…………… 53

2.1. Инверторы. ……………………………… 54

……………………………… 54

2.2. Повторители и буферы……………………… 58

2.3. Логические элементы И, И-НЕ, ИЛИ, ИЛИ-НЕ—- 65

2.4. Логические элементы Исключающее ИЛИ……… 74

2.5. Сложные логические элементы ………………. 78

2.6. Триггеры Шмитта…………………………. 80

Глава 3. Применение комбинационных микросхем………. 87

3.1. Дешифраторы и шифраторы…………………. 88

3.2. Мультиплексоры………………………….. 97

3.3. Компараторы кодов ……………………….. 101

3.4. Сумматоры …………………………….. 105

3.5. Преобразователи кодов…………………….. 109

3.6. Одновибраторы и генераторы………………… 114

Глава 4. Применение триггеров и регистров…………… 123

4.1. Триггеры………………………………… 124

4.1.1. Принцип работы и разновидности триггеров….. 124

4.1.2. Основные схемы включения триггеров. ……… 131

……… 131

4.2. Регистры………………………………… 142

4.2.1. Регистры, срабатывающие по фронту……….. 144

4.2.2. Регистры, срабатывающие по уровню……….. 153

4.2.3. Сдвиговые регистры…………………….. 157

Глава 5. Применение счетчиков …………………… 170

5.1. Асинхронные счетчики …………………….. 172

5.2. Синхронные счетчики с асинхронным переносом … 181

5.3. Синхронные счетчики……………………… 209

Глава 6. Применение микросхем памяти……………… 222

6.1. Постоянная память………………………… 225

6.1.1. ПЗУ как универсальная комбинационная микросхема …………………………………. 231

6.1.2. ПЗУ в генераторах импульсных последовательностей ………………………………….. 240

6.1.3. Микропрограммные автоматы на ПЗУ………. 245

6.2. Оперативная память………………………. 258

6.2.1. ОЗУ для временного хранения информации . …. 264

…. 264

6.2.2. ОЗУ как информационный буфер………….. 272

6.2.3. Улучшение параметров ОЗУ………………. 280

Глава 7. Применение микросхем ЦДЛ и АЦП…………. 284

7.1. Применение ЦАП…………………………. 285

7.2. Применение АЦП…………………………. 295

Глава 8. Примеры разработки цифровых устройств……… 307

8.1. Разработка клавиатуры …………………….. 308

8.2. Разработка вычислителя контрольной суммы……. 316

8.3. Разработка логического анализатора ………….. 321

8.4. Разработка генератора аналоговых сигналов…….. 336

Приложение. Микросхемы, параметры, сигналы………… 351

Список литературы……………………………… 365

Словарь терминов и сокращений……………………. 368

Основы схемотехники для начинающих

У сегодняшних программистов нет необходимости знать устройство компьютера на самом низком уровне, и все же без этого чувствуешь, что упустил что-то важное. К сожалению, в одной статье я не смогу рассказать о том, как работает даже самый примитивный процессор, поэтому мы начнем с изучения сумматора — ключевого элемента арифметико-логического устройства (АЛУ). Немного поговорим по теории, потом перейдем к практике: познакомимся с микросхемой 74HC283 и попробуем собрать на макетной плате небольшой тестовый стенд.

К сожалению, в одной статье я не смогу рассказать о том, как работает даже самый примитивный процессор, поэтому мы начнем с изучения сумматора — ключевого элемента арифметико-логического устройства (АЛУ). Немного поговорим по теории, потом перейдем к практике: познакомимся с микросхемой 74HC283 и попробуем собрать на макетной плате небольшой тестовый стенд.

Говорят, древние кодеры собирали свои компы самостоятельно, уверенно обращались с паяльником и знали ассемблер. Но потом эти умения были безвозвратно погребены под слоями абстракции, и теперь каждый — специалист в узкой области, который редко заглядывает дальше ее. Если вы не работаете с железом, то схемотехника вам вряд ли пригодится сама по себе. Так зачем ее учить? Попробую показать на примере.

Знаете, что изображено на этой картинке?

Так выглядит руль болида «Формулы-1». Нетрудно догадаться, что у пилота за таким штурвалом совершенно иной уровень подготовки. И речь не о скорости реакции или рефлексах: тут абсолютно другое, качественно более глубокое понимание принципов и особенностей работы машины.

Знания пилота «Формулы-1» — это и немного знаний конструктора, и инженера, и механика. Только так можно выжать из этого автомобиля максимум и нестись по трассе на огромной скорости под восхищенные крики болельщиц. Примерно то же и со схемотехникой: без нее ты просто скучный современный водитель, от которого скрыли устройство его машины.

РЕКОМЕНДУЕМ:

3D-сканер из смартфона или фотокамеры

Лично мне цифровая схемотехника дала многое. Я, например, узнал, что собой представляет конвейер в процессоре, почему его сброс дорого обходится для исполняемой программы и как выглядит компромисс времени и памяти на аппаратном уровне. Если мне удалось вас убедить и вы тоже хотите хоть немного овладеть этой наукой, то приступим!

Форма сигнала

Схемотехнику принято делить на две большие области: цифровую и аналоговую, по типу сигнала. Аналоговая оперирует такими параметрами, как сила тока, напряжение (иногда оно бывает отрицательным) и сопротивление. В цифровой все проще — в схеме есть только высокий и низкий логические уровни, даже без конкретных значений.

В цифровой все проще — в схеме есть только высокий и низкий логические уровни, даже без конкретных значений.

В С/С++ подобное отношение моделирует тип bool и два его состояния — true и false. Я и дальше буду использовать аналогии из языков программирования, где это уместно. Надеюсь, это поможет тебе лучше понять происходящее. Кроме того, это ярко показывает, насколько тесно все связано в цифровом мире.

Аналоговая схемотехника капризна и непредсказуема — на параметры сигнала могут влиять не только хорошо известные факторы вроде температуры и внешних наводок, но и даже такие неочевидные вещи, как вовремя не отмытый с платы флюс или окислившиеся контакты (без шуток). Цифровая схемотехника, напротив, слабо зависит от окружающих условий и вообще устойчива к шумам.

Фирма Sony удачно обыграла аналоговую и цифровую природу сигнала в названии своих ноутбуков VAIO. Если внимательно присмотреться к их логотипу, то первые его две буквы повторяют аналоговую форму синусоиды, тогда как последние две представляют пару дискретных состояний цифрового бита.

Так что нет ничего удивительного в том, что сегодня большая часть информации существует именно в цифровом виде, а компьютеры оперируют исключительно числами (если точнее, то их двоичным представлением). Для базового понимания цифровой схемотехники не требуется особых знаний — достаточно только уметь переводить числа из десятичной формы в двоичную и обратно.

Цифровая схема

Типичная цифровая схема состоит из входов, выходов и логических элементов, также называемых вентилями. Сигналы поступают на входы схемы, преобразуются по определенным правилам внутри вентилей (об этом чуть ниже) и подаются на выходы.

В комбинационных схемах состояние сигналов на выходе зависит только от состояния на входе. В последовательностных схемах выход зависит не только от входа, но еще и от внутреннего состояния схемы. В любом случае важно понимать, что сигналы на выходе зависят от входа, не наоборот.

РЕКОМЕНДУЕМ:

Как научиться электронике и схемотехнике

В этой статье мы будем рассматривать только комбинационные схемы. Они проще для понимания и наглядней. Кстати, в отечественной литературе нет устоявшегося перевода для последовательностных схем. Кто-то называет их последовательными, кто-то предпочитает кальку с английского языка и использует термин «секвенциальные схемы» (sequential). Разницы нет никакой, но все равно учти это, когда будешь читать дополнительные источники.

Базовые блоки

Все цифровые схемы сводятся к нескольким стандартным логическим элементам. Это примерно как кубики Lego в детском конструкторе. Их можно комбинировать, соединять друг с другом и получать новые схемы. Для каждого элемента я привел таблицу истинности — соответствие между входными и выходными сигналами.

Существуют еще диаграммы Венна, но, на мой взгляд, они совершенно лишние и только осложняют дело. Впрочем, если ты предпочитаешь графическое представление, то можешь ознакомиться и с ними.

NOT

Самый простой вентиль, представляет собой логическое отрицание и инвертирует сигнал на единственном входе. Так как у нас всего два возможных состояния, таблица истинности совсем крохотная. В С/C++ это оператор !, хотя там его действие распространяется на любые переменные с числовым значением, не только бинарные.

Обрати внимание, что на рисунке выше (и на всех последующих) приведены два символа для обозначения конкретного элемента на схемах. Слева — американский вариант (ANSI), справа — его европейский аналог (МЭК и ГОСТ). Второй стандарт сейчас уже редко где применяется, и даже в русскоязычной литературе почти всегда используется графически более наглядный стандарт ANSI.

AND

Сигнал на выходе этого вентиля равен логической единице только тогда, когда на всех входах присутствует высокий уровень. При этом количество входов может быть любым — таблица истинности изменится незначительно. Кроме того, ничто не мешает каскадировать такие элементы, подавая выход одного вентиля AND на вход другого.

Традиционно таблица рисуется именно таким образом: сперва все входы находятся в состоянии логического ноля, а затем последовательно инвертируется один из разрядов, начиная с младшего. Можно смотреть на это и с другой стороны — как будто все входы кодируют какое-то число (в двоичном представлении) и в каждой строке мы прибавляем к нему по единичке, проходя все возможные значения.

В С/С++ существует аж два аналога для этого вентиля: булево И (оператор &) и логическое И (оператор &&). Первый применяется для проверки флагов и других операций над отдельными битами числа, тогда как второй используется в логических выражениях.

OR

Здесь выход находится в состоянии логического ноля, только когда все входы равны нулю. Остальные комбинации приводят к высокому уровню на выходе.

Вместе AND и OR — это два основных строительных «кирпичика» цифровой логики. Сразу возникает вопрос, как их отличать друг от друга на схемах. Конечно, все решает практика, и со временем они запомнятся сами собой, но можно воспользоваться простым правилом: форма элемента со стороны входов соответствует первой букве в английском обозначении.= y;

Но вернемся к нашим вентилям. Иногда в их список добавляют также сочетания с NOT: NOT + AND = NAND, NOT + OR = NOR и NOT + XOR = XNOR. При желании можешь вывести их таблицы истинности самостоятельно, это не составляет никакого труда.

Пример

Настало время применить полученные знания и собрать что-то практически полезное. Логические операции — это, конечно, прекрасно, но хотелось бы и работать с числами, хотя бы для разнообразия!

Представим, что наши требования к безопасности таковы, что мы не можем доверять даже процессорам крупных компаний. Мы опасаемся возможных закладок, на уровне компании — разработчика схемы или на уровне компании — производителя кристалла, каких-либо гипотетических уязвимостей, которые могут эксплуатировать недоброжелатели, — словом, мы опасаемся всего и сразу. Значит, нужно собрать все самостоятельно, не доверяя никому!

РЕКОМЕНДУЕМ:

Перехват и анализ радиосигнала

Начинать стоит именно с процессора, а если еще конкретнее, то с сумматора в АЛУ. Это ключевой блок всего компьютера. Как если бы мы захотели приехать в Москву и очутились бы сразу на Красной площади.

Полусумматор

Конкретизируем задачу — пусть нам надо сложить два восьмибитных положительных значения друг с другом. Если использовать алгоритм сложения столбиком, то это будет выглядеть примерно так.

Мы последовательно складываем цифры в каждом разряде, справа налево, и получаем результат для этого разряда. При этом мы распространяем дальше перенос, если у нас возникло переполнение. Таким образом, у нас в схеме должно быть два входа (A и B) и два выхода (S и C). Составим таблицу истинности для всех возможных комбинаций А и В.

Рассматривая по отдельности получившиеся колонки S и C, легко заметить, каким логическим элементам они соответствуют. Теперь можно представить схему полностью.

Сумматор

Предыдущий блок носил несколько обидное название «полусумматора». Почему только половинка — догадаться нетрудно, ведь здесь мы никак не учитываем выход с предыдущего разряда. Логично предположить, что, комбинируя два таких блока, мы можем составить схему полного сумматора. Это как с Землей — есть Северное и Южное полушария. Хотя стоп, есть же еще Западное и Восточное…

Вопрос, куда девали вторую Землю, остается открытымТеперь, когда мы получили возможность полноценно складывать биты из одного разряда, мы можем последовательно вычислить полную сумму нашего числа, каким бы большим оно ни было. Да, вот так все просто!

Важная характеристика цифровой схемы — задержка распространения. Схема реагирует на изменение входных сигналов не мгновенно, а с некоторым запаздыванием. То есть приходится ждать какое-то время, в течение которого сигнал на выходе тоже может меняться. Чем больше элементов в схеме, тем хуже ее быстродействие. На примере с сумматором в такой наивной реализации сигнал переноса должен последовательно пройти через все биты числа, прежде чем сформируется итоговая сумма. К счастью, есть хитрые способы обойти такие ограничения, и один из них мы разберем ниже.

Практика

До этого момента в статье была сплошь теория. Сейчас я предлагаю закрепить ее практической частью и собрать восьмибитный сумматор. Нам потребуется пара беспаечных макетных плат, несколько DIP-переключателей, светодиоды для индикации, токоограничивающие резисторы на 10 кОм и пара микросхем 74HC283.

Серия 74xx включает в себя микросхемы самого разного назначения. Это могут быть как сборки логических вентилей (например, 74HC04 — шесть инверторов в одном корпусе), так и полноценные АЛУ (74HC181). Помимо комбинационных схем, там есть и последовательностные: триггеры (74НС74), регистры (74НС373) и счетчики (74НС393).

Чтобы ориентироваться во всем этом номенклатурном разнообразии, я рекомендую не скачивать документацию на каждую микросхему в отдельности, а сразу найти целый справочник по всей серии. Например, есть справочник Texas Instruments в PDF.

В СССР и России существуют аналогичные микросхемы серий К155 и КР1564, для замены 74хх и 74НСхх соответственно. Большинство из них совместимы по корпусам и контактам с зарубежными, но из-за своей редкости и высокой цены они остаются скорее занятной диковинкой. Для этой статьи я пытался достать парочку интегральных схем (ИС) белорусского «Интеграла» (ЭКР5564ИМ6), но в наличии их не оказалось, поэтому пришлось ограничиться более массовыми SN74HC283 все той же Texas Instruments.

Расположение выводов у микросхемы 74HC283 можно найти на странице 176 справочника, принципиальную схему и таблицы истинности смотри на страницах 390–391. И хотя это сумматор всего лишь на четыре бита, тут есть функция ускоренного переноса, а сами микросхемы можно объединять, собирая сумматоры на 8, 16 или даже 32 бит.

Хорошо видно, что схема здесь несколько отличается от той, что мы вывели ранее. В этом нет ничего необычного, одну и ту же функцию можно реализовать несколькими способами, и в производстве зачастую используют тот, который дешевле (по элементам) и лучше подходит для техпроцесса.

При этом все равно осталось некоторое сходство — его можно заметить при внимательном изучении. Например, элементы XOR от полусумматоров располагаются непосредственно перед выходом для значений каждого из разрядов.

Кроме того, можно понять, что значение для переноса вычисляется параллельно со значениями разрядов — для этого в микросхеме и присутствуют «лишние» элементы. Пожалуй, это самая сложная часть в статье. Поэтому, если у тебя возникли трудности, попробуй рассмотреть схему ускоренного переноса отдельно — это ИС 74HC182 на с. 338 (вот она, польза от полноценного справочника).

Сложение

Теперь, когда принцип работы микросхемы и назначение каждого ее вывода для нас не составляет секрета, можно собирать рабочий сумматор на восемь бит на макетных платах. Потребуется целый ворох проводов и перемычек, чтобы соединить все компоненты, так что главное здесь — быть внимательным и не допускать ошибок.

Как правило, значения в АЛУ попадают из регистров — самого быстрого типа памяти в компьютере. Здесь же я для удобства использую пару DIP-переключателей (левый верхний угол), чтобы можно было легко задавать нужные значения. По сути, это регистры А и В нашего протокомпьютера.

К сожалению, производитель переключателей явно не рассчитывал на такое применение, поэтому нумерация битов в каждом регистре мало того что начинается с единицы, так еще и идет в «неправильном» порядке, слева направо! Учитывай это, когда будешь работать со схемой.

Пара 74НС283 располагается по центру на нижней макетке, а результат операции отображается на линии из светодиодов (правый верхний угол). В левом нижем углу роль источника питания выполняет преобразователь USB — UART (другого способа подать стабильные 5 В я в тот момент не нашел).

Если схема была собрана без ошибок, то, задавая двоичное представление чисел на переключателях, ты сможешь наблюдать значение суммы на светодиодах. Примерно как на картинке выше.

Вычитание

Удивительно, но такую схему без каких-либо изменений и доработок можно использовать и для вычитания. Да, раньше я не говорил об этом ни слова, но такое действительно возможно. Если использовать представление отрицательных чисел в дополнительном коде, нам никак не нужно переопределять операцию сложения — все будет работать на имеющемся железе.

Наверняка ты уже представляешь, как на уровне цифровой схемы из положительного числа можно сделать отрицательное (в дополнительном коде). Действительно, достаточно только к каждому биту применить операцию NOT, а затем подать на вход сумматора вместе с единицей. Как видишь, подобное представление неочевидно с точки зрения человека, но очень удобно для реализации из набора логических вентилей.

Заключение

Статья подошла к концу, но цифровая схемотехника на этом отнюдь не заканчивается. Скорее наоборот, только начинается! Мы рассмотрели лишь самые простые комбинационные схемы (за исключением, может быть, ускоренного переноса). За бортом оказались дешифраторы, мультиплексоры, буферы и все последовательностные схемы (они несколько сложнее для понимания).

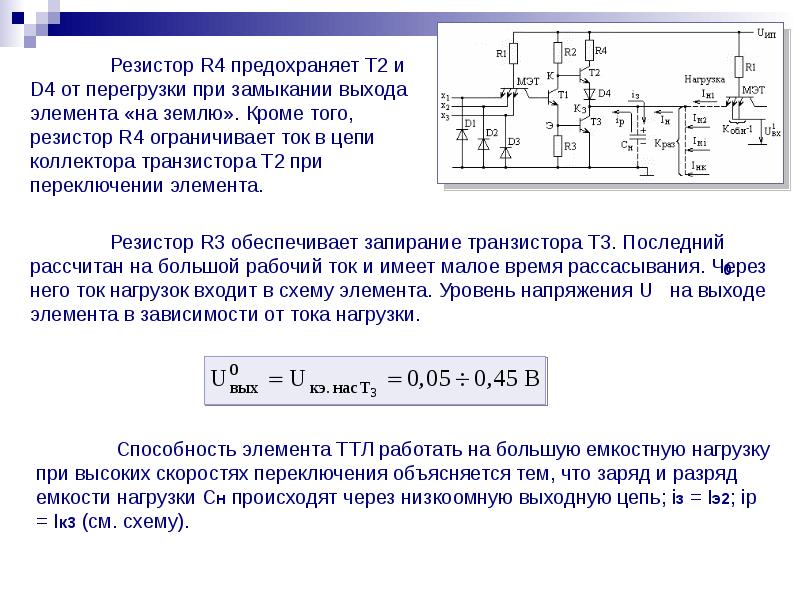

Кроме того, можно было бы спуститься на уровень ниже и рассказать о том, как собирать логические вентили из дискретных элементов — транзисторов, диодов и резисторов. В разные времена для этого использовали разные технологии, в зависимости от развития промышленности — ТТЛ (транзисторно-транзисторная логика), КМОП (комплиментарный металл-оксид-полупроводник) и другие.

РЕКОМЕНДУЕМ:

Как сделать робота для сборки кубика Рубика

Конечно, собранная самостоятельно на макетке схема с точки зрения производительности навсегда останется на уровне решений семидесятых годов прошлого века. И она никогда не сможет соперничать с современными многоядерными процессорами, с их многоуровневым кешем, блоками спекулятивных вычислений и параллелизмом.

С другой стороны, важно понимать, что основные принципы работы компьютеров не сильно изменились с тех пор. За исключением разве что квантовых машин, но это совсем другая история. Интересно, сможем ли мы когда-нибудь собирать квантовые компьютеры так же просто, как сейчас на основе полупроводниковых микросхем?

Продолжение в статье «Логические элементы и биты памяти в компьютере».

Загрузка…Основы цифровой схемотехники. 09. Умножители

${form_setting.title_name}

${form_setting.first_name_required}

* ${form_setting.first_name_required}${form_setting.title_fam}

${form_setting.last_name_required}

* ${form_setting.last_name_required}${form_setting.title_otchestvo}

Для преподавателей отчество обязательно

* Для преподавателей отчество обязательно${form_setting.title_phone}

*${country_title}

${phone.title} ${form_setting.phone_required} ${form_setting.country_required}${form_setting.type_action}

*${action.title}

${form_setting.type_action_required}${form_setting.type_action_required}

${form_setting.title_find_company}

* Выберите организацию Такой организации нет${org.title}

Выберите организацию

Некорректный url сайтаНекорректный url сайта

${form_setting.title_no_company}

${form_setting.title_fac}

${form_setting.facultet_required}

${Data.select_facultet.title}

${faculty.title}

${form_setting.facultet_required}Не нашел в списке Факультет

${form_setting.title_caf}

${form_setting.cafedra_required}

${Data.select_cafedra}

${cafedra.title}

${form_setting.cafedra_required}Не нашел в списке Кафедру

${form_setting.title_position}

${form_setting.position_required}

* ${ error }${form_setting.title_departament}

Открытое образование – Цифровая схемотехника

- 10 weeks

- от 3 до 4 часов в неделю

- 2 credit points

About

Цифровая схемотехника – это курс, посвященный изучению методов и средств построения устройств для автоматической обработки информации представленной в цифровой форме.

В курсе рассматриваются основные принципы и приемы проектирования инвариантные к технологической реализации.

Course program

Темы 1. Введение. Краткая история развития цифровой схемотехнической базы различных поколений. Классификация элементной базы. Электрические характеристики элементов.

Тема 2. Представление информации в цифровой форме. Представление логических переменных электрическими сигналами в потенциальной и импульсной системе. Параметры элементов и их связь с характеристиками.

Тема 3. Элементная база. ГОСТы и ЕСКД в цифровой схемотехнике. Условные графические и условные буквенные обозначения. Типы логик и их связь с условными графическими изображениями. Прямые и инверсные входы и выходы.

Тема 4. Логические основы цифровой схемотехники. Функции Алгебры Логики (ФАЛ). Способы задания функций. Понятие Базиса. СДНФ, СКНФ. Переход из одного базиса в другой. Комбинационная Схема. Минимизация ФАЛ методом Квайна Мак-Класски. Графические методы минимизации ФАЛ. Не полностью определенные функции. Минимизация не полностью определенных функций.

Тема 5. Комбинационные схемы. Постановка задачи, этапы анализа и синтеза комбинационных схем на базе аппарата ФАЛ. Реализация булевых функций на элементах. Синтез и функциональные узлы комбинационных схем: исключающие ИЛИ, мультиплексор, дешифратор, Использование мультиплексоров и дешифраторов для реализации логических функций. Увеличение разрядности комбинационных схем. Классификация сумматоров. Построение комбинационных сумматоров, быстродействие сумматора. Увеличение разрядности сумматора, организация цепей ускоренного переноса.

Тема 6. Временные параметры. Модель логического элемента. Временные параметры. Построение временных диаграмм комбинационных схем методом ранжирования. Построение временных диаграмм схем с памятью событийным методом. Анализ критического пути.

Тема 7. Состязания сигналов. Состязания сигналов в цифровых схемах: причины появления состязаний, переходные процессы в цифровых схемах. Классификация состязаний сигналов: примеры статических и динамических состязаний. Анализ цифровых схем на состязания. Устранение состязаний сигналов в комбинационных схемах. Способы синтеза цифровых схем, свободных от состязаний.

Тема 8. Схемы с памятью. Элементарные триггерные схемы на элементах И-НЕ, ИЛИ-НЕ. Классификация триггерных схем. Таблицы внешних переходов. Асинхронные и синхронные триггерные схемы. Триггерные схемы со статическим и динамическим управлением записью, двухступенчатые триггерные схемы. Примеры двухступенчатых триггеров типа RS, JK, DV, D, T. Примеры триггеров с прямым и инверсным динамическим управлением записью типов RS, JK, DV, D, T.

Тема 9. Проектирование триггера. Проектирование триггера с заданной таблицей перехода. Построение временных диаграмм работы триггера, определение динамических параметров: время переключения, время предварительной установки, время удержания, длительность импульса.

Тема 10. Разработка произвольного счетчика. Классификация счетчиков. Синхронные и асинхронные счетчики. Двоично-десятичные счетчики. Реверсивные счетчики. Увеличение разрядности счетчиков и организация цепей переноса, динамические параметры. Счетчики по модулю М. Проектирование счетчиков с заданным модулем пересчета.

Тема 11. Проектирование многофункционального регистра. Классификация регистров. Регистры хранения и сдвига. Многофункциональные регистры. Организация цепей ввода и вывода информации. Основные принципы проектирования регистров. Примеры регистров. Динамические параметры регистров. Распределители сигналов, формирователи импульсов.

Тема 12. Запоминающие устройства. Схемотехника запоминающих устройств: параметры и классификация ЗУ, временные диаграммы работы и динамические параметры; статические, динамические и постоянные ЗУ. Двух портовая память. Организация буферной (FIFO) и стековой (LIFO) памяти.

Тема 13. Особенности передачи сигналов в цифровых схемах. Типы выходных каскадов: логический выход, элементы с тремя состояниями, выход с открытым коллектором. Элементы индикации, оптоэлектронные развязки, генераторы импульсов, элементы задержки. Организация цепей питания: фильтрация питающих напряжений. Линии передачи сигналов, длинные линии, отражения, согласованная нагрузка.

Тема 14. Программируемая логика. ПЛМ и ПЛИС FPGA. Программируемые логические матрицы (ПЛМ), программируемая матричная логика (ПМК), базовые матричные кристаллы (БМК): базовые структуры, схемные и конструктивные особенности, примеры реализации функций. Программируемые логические интегральные схемы (ПЛИС). Классификация ПЛИС (FPGA, CPLD, FLEX, SOC и др.). Архитектура и топология ПЛИС. Основные элементы: конфигурируемые логические элементы (логическая таблица, триггер, мультиплексор, схемы ускоренного переноса), блоки ввода-вывода, блоки линий межсоединений, «теневое ЗУ». ОЗУ в ПЛИС, шины с тремя состояниями, система синхронизации. Конфигурация ПЛИС. Примеры реализации функций и типовых цифровых узлов.

Тема 15. Средства автоматизации проектирования и отладки цифровых устройств. Этапы проектирования цифровых устройств. Методика и средства автоматизированного проектирования. Использование языков высокого уровня для описания цифровых устройств: проблемно-ориентированный язык VHDL. Примеры проектирования цифровых элементов с применением языка VHDL: описание проекта, компиляция, тестирование и реализация на кристалле FPGA. Тема 16. Заключение. Перспективы развития цифровой схемотехники

Райхлин, Вадим Абрамович – Основы цифровой схемотехники : учебное пособие для студентов вузов, обучающихся по направлению “Информатика и вычислительная техника”

Поиск по определенным полям

Чтобы сузить результаты поисковой выдачи, можно уточнить запрос, указав поля, по которым производить поиск. Список полей представлен выше. Например:

author:иванов

Можно искать по нескольким полям одновременно:author:иванов title:исследование

Логически операторы

По умолчанию используется оператор AND.

Оператор AND означает, что документ должен соответствовать всем элементам в группе:

исследование разработка

author:иванов title:разработка

оператор OR означает, что документ должен соответствовать одному из значений в группе:исследование OR разработка

author:иванов OR title:разработка

оператор NOT исключает документы, содержащие данный элемент:исследование NOT разработка

author:иванов NOT title:разработка

Тип поиска

При написании запроса можно указывать способ, по которому фраза будет искаться. Поддерживается четыре метода: поиск с учетом морфологии, без морфологии, поиск префикса, поиск фразы.

По-умолчанию, поиск производится с учетом морфологии.

Для поиска без морфологии, перед словами в фразе достаточно поставить знак “доллар”:

$исследование $развития

Для поиска префикса нужно поставить звездочку после запроса:исследование*

Для поиска фразы нужно заключить запрос в двойные кавычки:“исследование и разработка“

Поиск по синонимам

Для включения в результаты поиска синонимов слова нужно поставить решётку “#” перед словом или перед выражением в скобках.

В применении к одному слову для него будет найдено до трёх синонимов.

В применении к выражению в скобках к каждому слову будет добавлен синоним, если он был найден.

Не сочетается с поиском без морфологии, поиском по префиксу или поиском по фразе.

#исследование

Группировка

Для того, чтобы сгруппировать поисковые фразы нужно использовать скобки. Это позволяет управлять булевой логикой запроса.

Например, нужно составить запрос: найти документы у которых автор Иванов или Петров, и заглавие содержит слова исследование или разработка:

author:(иванов OR петров) title:(исследование OR разработка)

Приблизительный поиск слова

Для приблизительного поиска нужно поставить тильду “~” в конце слова из фразы. Например:

бром~

При поиске будут найдены такие слова, как “бром”, “ром”, “пром” и т.д.Можно дополнительно указать максимальное количество возможных правок: 0, 1 или 2.4 разработка По умолчанию, уровень равен 1. Допустимые значения – положительное вещественное число.

Поиск в интервале

Для указания интервала, в котором должно находиться значение какого-то поля, следует указать в скобках граничные значения, разделенные оператором TO.

Будет произведена лексикографическая сортировка.

author:[Иванов TO Петров]

Будут возвращены результаты с автором, начиная от Иванова и заканчивая Петровым, Иванов и Петров будут включены в результат.author:{Иванов TO Петров}

Такой запрос вернёт результаты с автором, начиная от Иванова и заканчивая Петровым, но Иванов и Петров не будут включены в результат.Для того, чтобы включить значение в интервал, используйте квадратные скобки. Для исключения значения используйте фигурные скобки. Основы

, схемотехника, проблемы проектирования и их применения.

Цифровые схемы или цифровая электроника – это отрасль электроники, которая имеет дело с цифровыми сигналами для выполнения различных задач в соответствии с различными требованиями. Входной сигнал, подаваемый на эти схемы, имеет цифровую форму, которая представлена в двоичном языковом формате 0 и 1. Эти схемы разработаны с использованием логических элементов, таких как И, ИЛИ, НЕ, NANAD, NOR, XOR, которые выполняют логические операции. Это представление помогает схеме переключаться из одного состояния в другое для обеспечения точного вывода.Системы цифровых схем в основном предназначены для преодоления недостатка аналоговых систем, которые работают медленнее, и получаемые выходные данные могут содержать ошибку.

Что такое цифровая схема?

Определение : Цифровая схема разработана с использованием ряда логических вентилей на одной интегральной схеме – IC. Вход в любую цифровую схему имеет двоичную форму «0» и «1». Выходные данные, полученные при обработке необработанных цифровых данных, имеют точную ценность. Эти схемы могут быть представлены двумя способами: комбинационным или последовательным.

Основы цифровых схем

Проектирование цифровых схем сначала было начато с разработки реле, позднее – электронных ламп, транзисторно-транзисторной логики TTL, эмиттерно-связанной логики и логики CMOS. Эти конструкции используют большое количество логических вентилей, таких как И, ИЛИ, НЕ и т. Д., Интегрированных в одну ИС. Ввод и вывод цифровых данных представлены в логической таблице истинности и временной диаграмме.

Логический уровень

Цифровые данные представлены в логическом формате, то есть в формате «0» и «1».Где логический 0 означает низкий уровень сигнала или «GND», а логический 1 означает высокий уровень сигнала или подключение к источнику «VCC», как показано ниже.

Логический уровеньТаблица логической истины

Таблица логической истинности представляет собой математическое представление рабочих характеристик. цифрового сигнала при прохождении через цифровую схему. Таблица состоит из 3 столбцов: столбца часов, столбца ввода и столбца вывода. Например, логическая таблица логического элемента НЕ представлена следующим образом:

| Тактовый сигнал | Входная логика | Выходная логика |

High | 0 | 1 |

| High | 1 | 0 |

Временная диаграмма

Поведение цифрового сигнала представлено во временной области, например, если мы рассматриваем НЕ таблицу истинности логического элемента, временная диаграмма представлена следующим образом, когда часы высокий, вход низкий, затем выход высокий.Точно так же, когда вход высокий, выход становится низким.

Временная диаграммаШлюз

Логический вентиль – это электронный компонент, который реализован с использованием логической функции. Затворы обычно реализуются с использованием диодов, транзисторов и реле. Существуют разные типы логических вентилей: AND, OR, NOT, NANAD, NOR, XOR. Среди которых AND, OR, NOT являются основными воротами, а NAND и NOR – универсальными воротами. Давайте рассмотрим представление логического элемента И, как показано ниже, которое имеет 2 входа и один выход.

AND Gate| Тактовый сигнал | Входная логика 1 | Входная логика 2 | Выходная логика |

| High | 0 | 029 | |

| Высокий | 0 | 1 | 0 |

| Высокий | 1 | 0 | 0 |

| Высокий | 1 | 1 | 1 |

Таблица истинности Логический элемент И

Временная диаграмма логического элемента ИСуществует множество способов построения цифровой схемы, использующей логические элементы, путем создания комбинационной логики, последовательной логической схемы или с помощью программируемого логического устройства, которое использует таблицы поиска, или с помощью комбинации многих IC и т. д.Обычно они разрабатываются с использованием формата комбинационной и последовательной схемы, как показано ниже.

Комбинированная логическая схема

Это комбинация различных логических элементов, таких как И, ИЛИ, НЕ. Дизайн комбинационной логики сделан таким образом, что выход зависит от текущего входа, а логика не зависит от времени. Комбинационные логические схемы подразделяются на 3 типа, это

Комбинационная логическая схемаПоследовательная схема

Конструкция последовательной схемы отличается от комбинационной схемы.В последовательной схеме логика вывода зависит как от текущих, так и от прошлых входных значений. Он также состоит из элемента памяти, в котором хранятся обработанные и обработанные данные. Последовательные схемы подразделяются на 2 типа:

- Синхронная схема

- Асинхронная схема

Некоторыми примерами последовательных схем являются триггеры, тактовые генераторы, счетчики и т. Д.

Схема последовательной схемыКонструкция цифровой схемы

Цифровая схемы могут быть спроектированы следующими способами:

- Использование последовательного представления системы и представления комбинационной системы

- Использование математических методов путем сокращения алгоритмов логической избыточности, таких как K-Map, булева алгебра, алгоритм QM, диаграммы двоичных решений и т. д.

- Использование машин потока данных, которые состоят из регистров и шин или проводов. Данные передаются между различными компонентами с помощью шин и регистров. Эти машины разработаны с использованием языков описания оборудования, таких как VHDL или Verilog.

- Компьютер – это логическая машина общего назначения с переносом регистров, разработанная с использованием микропрограммы и процессора микропоследовательностей.

Проблемы проектирования цифровых схем

Поскольку цифровые схемы состоят из аналоговых компонентов, таких как резисторы, реле, транзисторы, диоды, триггеры и т. Д.Необходимо отметить, что эти компоненты не влияют на поведение сигнала или данных во время работы цифровой схемы. Ниже приведены проблемы проектирования, которые обычно наблюдаются:

- Проблемы, такие как сбои, могут возникнуть из-за неправильной конструкции системы

- Неправильная синхронизация другого тактового сигнала приводит к метастабильности в схеме

- Расчет цифровых схем более многократно из-за высокой помехоустойчивости.

Примеры цифровых схем

Ниже приведены примеры цифровых схем

- Мобильные телефоны

- Радио

- Калькуляторы и т. Д.

Преимущества

Ниже приведены преимущества

- Высокая точность и программируемость

- Простота сохранения цифровых данных

- Устойчивость к шумам

- Многие цифровые схемы могут быть интегрированы в одну микросхему

- Высокая гибкость

- Высокая надежность

- Высокая скорость передачи

- Высокая безопасность.

Недостатки

Ниже приведены недостатки

- Они работают только с цифровыми сигналами

- Потребляет больше энергии, чем аналоговые схемы

- Рассеивание тепла больше

- Высокая стоимость.

Приложения

Ниже приведены приложения

Часто задаваемые вопросы

1). Для чего используются цифровые схемы?

Цифровые схемы используются для выполнения логических операций.

2). Как работает цифровая схема?

Цифровая схема работает с дискретными сигналами, которые представлены в двоичной форме нулей и единиц.

3). Каковы основные компоненты цифровой схемы?

Основными компонентами цифровых схем являются триггеры, диоды, транзисторы, вентили и т. Д.

4). Из чего сделана схема?

Электронная схема состоит из ряда пассивных и активных компонентов, соединенных между собой проводящими проводами.

5). Назовите несколько примеров активных и пассивных компонентов?

- Примерами активных компонентов являются диоды, ИС, триодные вакуумные лампы и т. Д.

- Примерами пассивных компонентов являются резистор, конденсатор, катушка индуктивности, трансформатор и т. Д.

6). Почему мы используем резистор в схемах?

Мы используем резистор в цепи, чтобы контролировать ток.

Электронная схема состоит из ряда пассивных и активных компонентов, соединенных между собой проводящими проводами. Это два типа схем: аналоговая схема и цифровая схема. Входом в аналоговую схему является непрерывный переменный сигнал, который предоставляет информацию о сигнале, такую как ток, напряжение и т. Д. Входной сигнал цифровой схемы находится в дискретном формате временной области, который представлен в виде «0» и «1». Он обеспечивает уровень сигнала, коэффициент шума, затухание и т. Д. Характеристики цифрового сигнала.Основное преимущество использования цифровых схем в том, что их легко реализовать и понять.

4. Базовые цифровые схемы – Введение в цифровые схемы

Все логические схемы, которые мы обсуждали до сих пор, являются ациклическими , то есть они не образуют циклов или циклов, кроме как неявно через источник питания. Ациклические схемы имеют входы \ (A \) и выходы \ (Y, \) и реализовать логические функции входов, \ (Y = f (A). \) Когда входы изменяются, выходы принимают значения, определенные на \ (f \) после задержки распространения, характерной для схемы.Циклический схемы демонстрируют более сложное, зависящее от времени поведение, чем их ациклические кузены, потому что их выходы зависят от входной последовательности включая текущие и прошлые входные значения. Циклические схемы бывают Особый интерес представляет реализация элементов памяти. В В этом разделе мы обсудим два наиболее часто используемых типа памяти. элементы, D-защелка и D-триггер .

4.7.1. Циклические схемы

Циклическая схема имеет один или несколько контуров , не считая неявные контуры питания.Например, Рисунок 4.50. показаны две циклические схемы с одним контуром в каждой.

Рисунок 4.50: Циклические схемы с одним контуром из двух (слева) и трех (справа) инверторов.

Циклические схемы труднее анализировать, чем ациклические схемы. В частности, схемы, показанные на рисунке 4.50, не даже различают входные и выходные клеммы. Инверторная пара слева на рисунке 4.50 есть два провода: \ (Q_0 \) подключает выход инвертора 0 к входу инвертора 1, и \ (Q_1 \) соединяет выход инвертора 1 со входом инвертора. 0.Аналогично, цикл с тремя инверторами справа имеет три провода, \ (Q_0, \) \ (Q_1, \) и \ (Q_2. \)

Разберем функциональность двухинверторного контура. Выход каждого инвертора может быть 0 или 1. Сначала предположим, что \ (Q_0 = 0. \) Таким образом, вход инвертора 1 равен 0, следовательно, \ (Q_1 = 1. \) Поскольку \ (Q_1 \) – вход инвертора 0, выход инвертора 0 должен быть \ (Q_0 = 0. \) Это то же значение, с которого мы начали. Мы заключаем, что схема усиливает \ (Q_0 = 0 \) и, по симметрия, \ (Q_1 = 1.\) Во-вторых, предположим, что \ (Q_0 = 1. \) Тогда выход инвертора 1 равен \ (Q_1 = 0, \), что вызывает выход инвертора 0 должно быть \ (Q_0 = 1. \) Это также то же значение с началось с. Заметим, что петля с двумя инверторами усиливает его состояние в любом случае \ (Q_0 = 0 \) или \ (Q_0 = 1. \)

Цепь с тремя инверторами ведет себя совсем не так, как цепь с двумя инверторами. петля. Предположим, что \ (Q_0 = 0. \) Поскольку \ (Q_0 \) является входом инвертора 1, выход инвертора 1 должен быть \ (Q_1 = 1. \) Поскольку \ (Q_1 \) – вход инвертора 2, его выход должен быть \ (Q_2 = 0.\) Теперь вход \ (Q_2 \) является входом инвертора 0. Следовательно, выход инвертора 0 должен быть \ (Q_0 = 1, \), что является дополнение к предположению, с которого мы начали. Если мы пройдем по петле во второй раз находим \ (Q_0 = 0, \) то есть провод дополнил снова. Заметим, что схема не усиливает его состояние. Вместо этого значения проводов переключаются со скоростью определяется задержкой распространения инверторов.

Мы заключаем, что контур с двумя инверторами стабилен, тогда как трехинверторного шлейфа нет.Фактически, такое поведение можно наблюдать и в более крупные петли. Каждый контур инвертора с четным числом инверторы работает стабильно. В отличие от контуров инвертора с нечетным числом инверторы как нестабильные. Шлейфы инвертора с нечетными номерами называются кольцом . генераторы , и полезны для измерения средней задержки распространения инвертора в данном производственном процессе. Кольцевые генераторы не используются в качестве логических элементов в цифровых схемах. Напротив, петли с четным числом инверторов – полезные строительные блоки, потому что они бистабильные .Бистабильная схема – это схема с двумя стабильные состояния. Состояние стабильное , если схема не переход в другое состояние без внешнего раздражителя. Два стабильными состояниями бистабильного контура с двумя инверторами являются \ (S_0 = \ {Q_0 = 0, Q_1 = 1 \} \) и \ (S_1 = \ {Q_0 = 1, Q_1 = 0 \}. \) Когда цепь принимает стабильное состояние, инверторы обеспечивают выполнение \ (Q_0 \) и \ (Q_1 \) дополняют друг друга, \ (Q_0 = \ overline {Q_1}. \) Таким образом, на рис. 4.51 мы вызываем провода просто \ (Q \) и \ (\ overline {Q}.\)

Рисунок 4.51: Два состояния бистабильного контура инвертора.

Проблема с бистабильным контуром инвертора на рис. 4.51 заключается в том, что мы не можем контролировать его состояние. Поскольку схема стабильно и не имеет входов, не очевидно, как перейти на цепь из одного стабильного состояния в другое. D-защелка , которую мы обсуждается ниже, устраняет этот недостаток.

4.7.2. D-защелка

A D-latch – бистабильный элемент памяти с вводом данных \ (D, \) вход часов \ (\ phi, \) и выход \ (Q.\) Символ D-защелки показано справа. На рисунке 4.52 изображена D-образная защелка. реализация с бистабильным контуром инвертора и мультиплексором 2: 1 для направить входной сигнал данных в цикл.

Рисунок 4.52: D-защелка, реализованная как бистабильный инверторный контур с входом мультиплексор.

Вход часов \ (\ phi \) D-защелки служит входом выбора мультиплексор, и определяет, подтверждает ли ввод данных \ (D \) состояние бистабильного контура инвертора. Следовательно, мы различаем два режима операция:

\ (\ phi = 1 \): D-образная защелка прозрачная.

Контур инвертора разомкнут, и вход \ (D \) управляет инверторная пара. Поскольку вывод \ (Q \) следует за вводом \ (D, \) мы говорим, что D-защелка прозрачная .

\ (\ phi = 0 \): D-образная защелка непрозрачна.

Контур инвертора замкнут и сохраняет текущее состояние. Поскольку выход \ (Q \) сохраняет свое значение независимо от input \ (D, \) мы говорим, что D-защелка непрозрачна .

На рисунке 4.53 показана схема D-защелки с мультиплексором. заменен на его модель переключателя.Режим работы зависит от положение переключателя мультиплексора. Если \ (\ phi = 1, \) цикл открытый, а вход \ (D \) управляет как выходом \ (Q \), так и инверторная пара. В противном случае, если \ (\ phi = 0, \) замкнутый цикл отключен от входа \ (D, \) и сохраняет значение \ (Q \), потому что петля представляет собой бистабильную циклическую схему.

Рисунок 4.53: Режимы работы D-защелки. D-образная защелка либо (слева) прозрачный: вывод \ (Q \) следует за вводом \ (D, \) или (справа) непрозрачный: контур инвертора сохраняет значение \ (Q.\)

Диаграмма формы сигнала на рис. 4.54 иллюстрирует срабатывание D-защелки с течением времени. На схеме показано напряжение уровни входов часов и данных, а также выхода D-защелки. Первоначально D-защелка непрозрачна и хранит выходное значение \ (Q = 0. \) Вход \ (D \) переходит в 1 перед синхросигналом. Когда D-защелка становится прозрачной, вывод следует за вводом \ (D \) после задержки распространения, обозначенной изогнутой стрелкой от \ (\ phi \) to \ (Q. \) D-защелка остается прозрачной, пока тактовый сигнал равен \ (\ phi = 1.\) Выход \ (Q \) следует за входом \ (D \) после задержки распространения, обозначенной изогнутыми стрелками от переходов \ (D \) к \ (Q. \) Когда часы переходит на \ (\ phi = 0, \) D-защелка сохраняет последнее значение введите \ (D \) перед переходом часов и удерживает это значение для пока D-образная защелка остается непрозрачной. D-защелка называется чувствительный к уровню , потому что его два режима работы зависят от уровень тактового сигнала.

Рисунок 4.54: Диаграмма формы сигнала D-защелки.Когда D-образная защелка прозрачна, выход \ (Q \) следует за входом \ (D. \) В противном случае во время серые заштрихованные временные интервалы, D-защелка непрозрачна, т.е. удерживает вывод \ (Q \) без изменений и блокирует распространение \ (D \) на выход.

Далее мы выводим схему CMOS для D-защелки в Рисунок 4.52. Начнем с реализации Мультиплексор 2: 1 с двумя рычагами выбора, интегрирующий \ (\ overline {\ phi} \) – рычаг в контур инвертора, как показано на Рисунок 4.55. Поскольку эта схема мультиплексора инвертирует выход, мы добавляем инвертор для генерации незавершенного вывод \ (Q.\) На рис. 4.55 показан рычаги выбора мультиплексора трехсторонние инверторы в форме инвертора, который управляет передачей ворота.

Рисунок 4.55: Реализация D-защелки с рычагами выбора мультиплексора, показанными как трехпозиционные инверторы.

Функциональность схемы D-защелки существенно зависит от состояние внутреннего узла \ (X. \) Когда \ (\ phi \) – рука закрыто, он направляет вход \ (D \) в \ (X. \). плечо мультиплексора меняет полярность, мы имеем \ (X = \ overline {D}.\) выходной инвертор заставляет \ (X \) выводить \ (Q, \), так что \ (Q = \ overline {X} = D \), когда ввод часов \ (\ phi = 1, \) и D-защелка прозрачный. В противном случае, когда \ (\ phi = 0, \) \ (\ phi \) – рука открытый и \ (\ overline {\ phi} \) – рука закрыта, затем узел \ (X \) отключен от входа \ (D \) и контура инвертора усиливает \ (X = \ overline {Q}. \) D-образная защелка непрозрачна и выводит \ (Q \) сохраняет свое значение.

Компактная КМОП-реализация мультиплексоров показана на Рисунок 4.56. Мы используем эквивалентность схем в Рисунок 4.39 для реализации каждого плеча мультиплексора с четыре транзистора.

Рисунок 4.56: Реализация D-защелки с разнесенными рычагами выбора мультиплексора.

На рис. 4.57 показана полная 12-транзисторная схема. Схема CMOS для D-защелки, включая модель интерактивного переключателя. Обратите внимание, что выходной сигнал инвертора обратной связи равен \ (Y = \ overline {X}, \) и схема также применяет \ (X = \ overline {Q} \) и \ (Y = Q. \)

Временные характеристики D-защелки зависят от режима работы. Когда D-защелка прозрачна, критический путь простирается от данных вход \ (D \) в выход \ (Q.\) Сигнал распространяется через внутренний узел \ (X, \) и полностью обходит контур обратной связи. В задержка не зависит от тактового сигнала \ (\ phi. \) Когда D-защелка непрозрачный, вывод остается без изменений. Следовательно, это не делает есть смысл говорить о задержке распространения. Поэтому мы обсуждаем задержка распространения прозрачной D-защелки. В частности, мы проанализировать критический путь D-защелки с согласованным транзистором размеры указаны на рисунке 4.58.

Рисунок 4.58: Схема D-защелки с согласованными размерами транзисторов.

Задержка распространения прозрачной D-защелки – это задержка Мультиплексор 2: 1 плюс задержка выходного инвертора: \ (d_ {D \ rightarrow Q} = d_ {mux} + d_ {inv}. \) Предполагая, что вывод \ (Q \) управляет емкостной нагрузкой \ (C_L, \) выходной инвертор имеет электрическое усилие \ (h_ {inv} = C_L / C_ {inv} \) и паразитная задержка \ (p_ {inv} = 1, \) такое, что \ (d_ {inv} = C_L / 3 + 1 \) единиц времени. Далее мы анализируем мультиплексор. Логическое усилие – это ввод емкость \ (C_ {mux} (D) \) входа \ (D \), деленная на вход емкость опорного инвертора \ (C_ {inv} = 3.\) Вход \ (D \) управляет pMOS-транзистором шириной 4 и nMOS транзистор шириной 2 плеча \ (\ phi \). Таким образом, \ (C_ {mux} (D) = 6, \) и логическое усилие ввода \ (D \) из мультиплексор равен \ (g_ {mux} (D) = 6/3 = 2. \) Для определения электрического усилие мультиплексора, обратите внимание, что выход \ (X \) мультиплексора управляет двумя инверторы, инвертор обратной связи и выходной инвертор. Таким образом Емкость нагрузки мультиплексора равна \ (C_L (mux) = 2 C_ {inv} = 6. \) Следовательно, электрическое усилие входа \ (D \) мультиплексора равно \ (h_ {мультиплексор} (D) = C_L (мультиплексор) / C_ {мультиплексор} (D) = 6/6 = 1.\) Паразитический задержка мультиплексора 2: 1 равна \ (p_ {mux} = 4, \) см. мультиплексор. Мы обнаруживаем, что задержка мультиплексора равна \ (d_ {mux} = g_ {mux} (D) h_ {mux} (D) + p_ {mux} = 2 \ cdot 1 + 4 = 6, \) и задержка распространения D-образной защелки составляет

\ [d_ {D \ rightarrow Q} = d_ {mux} + d_ {inv} = 6 + \ frac {C_L} {3} + 1 = \ frac {C_L} {3} + 7 \,. \]

Эта задержка может служить точкой отсчета для цепи оптимизации. Например, мы наблюдаем, что инвертор обратной связи отводит ток с выхода мультиплексора.Если мы сжимаем pMOS транзистор инвертора обратной связи от 2 до 1 ед. нормированной ширины, уменьшаем емкость ответвления и задержку интересующего пути.

Задержка распространения \ (d_ {D \ rightarrow Q} \) – лишь одна из нескольких характерные величины временного поведения D-защелки. Возможно, даже более важным является временное поведение D-защелки. при изменении входа часов. Лаконичнее, если и часы, и входные данные меняются примерно одновременно, D-защелка может стать нестабильный.Цифровые схемы с D-защелками должны избегать этого сценария. во что бы то ни стало, потому что это может отрицательно повлиять на функциональность. Функциональные ошибки, вызванные неосторожным поведением по времени, особенно трудно раскрыть. Мы обсуждаем временные характеристики D-защелки. на рисунке 4.59, где ввод данных \ (D \) переходы в момент времени \ (t = 0 \) и ввод часов \ (\ phi \) в момент времени \ (t = 14. \)

Рисунок 4.59: Схема D-защелки и временной анализ. Входные переходы часов от 1 до 0 в момент времени \ (t = 14. \) D-защелка прозрачна для \ (t <14 \) и непрозрачным для \ (t> 14.\) Непрозрачная D-защелка сохраняет входное значение \ (D = 1. \)

Учитывая размеры транзисторов D-защелки на рис. 4.58 и ёмкость нагрузки \ (C_L = 12, \) задержки цепи элементами D-защелки являются:

\ (d_ {D \ rightarrow X} \): \ (\ quad \ phi \) – задержка руки; \ (d_ {D \ rightarrow X} = d_ {mux} = 6 \)

\ (d_ {X \ rightarrow Y} \): \ (\ quad \) задержка инвертора обратной связи; \ (d_ {X \ rightarrow Y} = 6/3 + 1 = 3 \)

\ (d_ {Y \ rightarrow X} \): \ (\ quad \ overline {\ phi} \) – задержка руки; \ (d_ {Y \ rightarrow X} = d_ {mux} = 6 \)

\ (d_ {X \ rightarrow Q} \): \ (\ quad \) задержка выходного инвертора; \ (d_ {X \ rightarrow Q} = d_ {inv} = C_L / 3 + 1 = 5 \)

С помощью этих задержек элементов мы можем выразить задержку распространения прозрачная D-защелка как \ (d_ {D \ rightarrow Q} = d_ {D \ rightarrow X}) + d_ {X \ rightarrow Q} = 11.\) Диаграмма формы сигнала показывает соответствующие переходы. Изначально D-образная защелка прозрачная. потому что \ (\ phi = 1, \) и \ (\ phi \) – рука закрыта, тогда как \ (\ overline {\ phi} \) – рука открыта. В момент \ (t = 0, \) \ (D \) – вход меняется с 0 на 1. Выход \ (Q \) будет следовать \ (D \) после того, как вход прошел через \ (\ phi \) – руку во внутренний узел \ (X \) в \ (t = 6, \), а затем через выходной инвертор в момент \ (t = 11. \) Изменение внутреннего узел \ (X \) также влияет на узел \ (Y, \), который изменяется со временем \ (t = 9 \) от 0 до 1 после задержки распространения \ (d_ {X \ rightarrow Y} \) инвертора обратной связи.

Когда D-защелка становится непрозрачной в момент времени \ (t = 14, \), она сохраняет значение \ (Q = 1. \) Сигнал часов \ (\ phi = 0 \) закрывается или поворачивается , кнопка \ (\ overline {\ phi} \) – и открывает или выключает \ (\ phi \) – рука. Таким образом, после часового перехода при \ (t = 14, \) сигнал \ (Y = 1 \) принимает задержку распространения \ (d_ {Y \ rightarrow X} = 6 \) единиц времени через инвертирующий \ (\ overline {\ phi} \) – руку на усилить внутренний узел \ (X = 0 \) в момент \ (t = 20. \) Это эта задержка переключения мультиплексора, которая может вызвать проблемы.В в частности, переход входа \ (D \) должен происходить достаточно длительный период времени до отрицательного перехода часов \ (\ phi \) для стабилизации внутреннего узла \ (Y \) через обратную связь инвертор, так как контур обратной связи бистабильный, только если \ (X = \ overline {Y}. \) Если мы заставим \ (X = Y, \), цикл обратной связи будет принять непредсказуемое состояние. Это может произойти, если временной интервал \ (d_ {D \ rightarrow \ phi} \) между переходами входов \ (D \) и \ (\ phi \) слишком малы. Рисунок 4.60 иллюстрирует проблемы синхронизации D-защелки.

Рисунок 4.60: Проблемы синхронизации D-защелки: (слева) в угловом корпусе

\ (d_ {D \ rightarrow \ phi} = d_ {D \ rightarrow X} + d_ {X \ rightarrow

Y} \) D-защелка сохраняет ввод после \ (d_ {D \ rightarrow Q} =

d_ {D \ rightarrow X} + d_ {X \ rightarrow Q}, \) (в центре)

\ (d_ {D \ rightarrow X} На диаграмме осциллограмм слева на рис. 4.60 интервал между переходом входного сигнала \ (D \) и

часы \ (\ phi \) – это \ (d_ {D \ rightarrow \ phi} = d_ {D \ rightarrow

X} + d_ {X \ rightarrow Y}. \) В момент \ (t = 9, \) отрицательные часы

край начинает закрывать \ (\ overline {\ phi} \) – плечо и открывать

\ (\ phi \) – рука. Внутренний узел \ (Y \) следует за \ (D \) прямо в

время в \ (t = 9 \) для усиления внутреннего узла \ (X \) после

задержка мультиплексора \ (d_ {Y \ rightarrow X} = 6 \) единиц времени, поэтому

что \ (X = 0 \) для \ (t> 15.\) Временной интервал

\ (d_ {D \ rightarrow \ phi} = d_ {D \ rightarrow X} + d_ {X \ rightarrow

Y} \) – это наименьший интервал для D-защелки для захвата ввода.

\ (D \) безопасно. Диаграмма формы сигнала в середине рисунка 4.60 предполагает, что интервал \ (d_ {D \ rightarrow \ phi} \) равен

меньше, то есть \ (d_ {D \ rightarrow X} Диаграмма формы сигнала справа на Рисунке 4.60

предполагает еще меньший интервал \ (d_ {D \ rightarrow \ phi} <

d_ {D \ rightarrow X}. \) Отрицательный фронт часов открывает

\ (\ phi \) - рука слишком рано, чтобы подтянуть внутренний узел \ (X \) к нулю.

\ (\ phi \) - рука сражается закрывающей \ (\ overline {\ phi} \) - рукой, которая

удается подтянуть \ (X \) к 1. Как следствие, D-защелка не работает.

для захвата ввода \ (D = 1 \) и продолжает сохранять старое значение

\ (Q = D = 0. \) Выходной инвертор распространяет сбой узла

\ (X \) для вывода \ (Q \) перед восстановлением старого выходного значения

\ (Q = 0.\) Рисунок 4.61: Синхронизация D-защелки: чем меньше интервал между входными переходами

\ (D \) и отрицательный фронт часов, \ (d_ {D \ rightarrow

\ phi}, \) становится, чем больше задержка распространения от входа

\ (D \) для вывода \ (Q, \) \ (d_ {D \ rightarrow Q}, \) становится.

Когда интервал становится слишком маленьким, D-защелка не может захватить

входной переход целиком, см. случай (4). На рисунке 4.61 показаны временные характеристики D-защелки.

в графе, который строит интервал \ (d_ {D \ rightarrow \ phi} \) на

горизонтальная ось и задержка распространения \ (d_ {D \ rightarrow Q} \) на

вертикальная ось.Случай (1) соответствует сценарию в

Рисунок 4.59, где переход входа \ (D \)

происходит достаточно рано до отрицательного фронта тактового сигнала для

D-защелка для безопасного распространения изменения на выход \ (Q. \)

задержка распространения – это сумма задержек \ (\ phi \) – плеча и

выходной инвертор, \ (d_ {D \ rightarrow Q} = d_ {D \ rightarrow X} +

d_ {X \ rightarrow Q}. \) Senarios (2), (3) и (4) соответствуют

три случая, показанные на рис. 4.60. В

ближе переход входа \ (D \) к отрицательным часам

края, увеличивается задержка распространения \ (d_ {D \ rightarrow Q} \).Когда интервал \ (d_ {D \ rightarrow \ phi} \) становится слишком маленьким,

D-защелка не может полностью захватить новый входной сигнал и сохраняет

старое входное значение. Мы наблюдаем, что для безопасной работы

D-защелка, нам нужно гарантировать, что input \ (D \) изменится

достаточно рано до отрицательного фронта тактового сигнала, т.е. интервала

\ (d_ {D \ rightarrow \ phi} \) должен быть достаточно большим. Время установки \ (t_ {setup} \) – минимальное время ввода

\ (D \) должен быть стабильным до отрицательного фронта тактового сигнала для захвата

вводимое значение с разумной задержкой \ (d_ {D \ rightarrow

Q}.\) Например, разумные спецификации определяют \ (t_ {setup} \) как

\ (5 \, \% \) больше, чем задержка распространения прозрачного

D-защелка, \ (t_ {setup} = 1.05 \, (d_ {D \ rightarrow X} +

d_ {X \ rightarrow Q}). \) Рисунок 4.62: Время установки D-защелки и время удержания характеризуют временной интервал вокруг отрицательного фронта тактового сигнала, когда вход \ (D \) может безопасно измениться. Отрицательный фронт часов находится в \ (d_ {D \ rightarrow \ phi} = 0. \) Проблемы синхронизации D-защелки возникают даже при переходе

ввод \ (D \) происходит после отрицательного фронта тактового сигнала.Если ввод

\ (D \) переходы до того, как \ (\ phi \) – рука будет полностью открыта,

сбои могут распространяться на выход \ (Q. \). Рисунок 4.62 иллюстрирует задержку \ (d_ {D \ rightarrow Q} \) как

функция интервала \ (d_ {D \ rightarrow \ phi}. \) Аналогично

время установки, для бесперебойной работы D-защелки мы должны обеспечить

этот вход \ (D \) не переходит до периода времени после

отрицательный фронт часов прошел. Время удержания \ (t_ {hold} \) – минимальное время на входе

\ (D \) должен быть стабильным после отрицательного фронта тактового сигнала для захвата

вводимое значение с разумной задержкой \ (d_ {D \ rightarrow

Q}.\) Время установки и время удержания характеризуют временное поведение

D-защелка вокруг отрицательного фронта часов. Большинство производителей предлагают

D-образные защелки в качестве основных элементов схемы и обеспечивают их питание в зависимости от процесса.

настройте и удерживайте время в своих таблицах данных. Для проектировщика схем,

важно убедиться, что ввод данных не меняется в

интервал вокруг отрицательного тактового фронта D-защелки. Это

причина, по которой тактовый вход D-защелки обычно подключается к

регулярные биения тактового сигнала с четко определенным тактовым периодом.Такой тактовый сигнал ограничивает выбор конструкции, но дает

разработчик эталон чистого времени для допустимого диапазона задержки

схемы, управляющей вводом данных D-защелки. A D-flipflop – бистабильный элемент памяти с вводом данных.

\ (D, \) вход часов \ (\ phi, \) и выход \ (Q. \) A

D-триггер – это элемент памяти , запускаемый по фронту, который активируется

по краю часов. На фронте тактового сигнала срабатывания D-триггер сохраняет

введите \ (D \), пока не появится следующий фронт синхронизации.Этот

поведение отличается от D-защелки, которая чувствительна к уровню .

В то время как D-защелка непрозрачна при низком уровне входного сигнала синхронизации,

D-триггер всегда непрозрачен, за исключением короткого периода времени около

синхронизирующий фронт часов. Тем не менее, D-триггер можно построить

последовательной композицией из двух D-образных защелок с дополненными часами

входы, как показано на рисунке 4.63. В

Символ D-триггера справа имеет треугольник на входе часов для

указывают, что триггер срабатывает по фронту. Рисунок 4.63: D-триггер с положительным фронтом, реализованный с двумя

вставные D-образные защелки и дополненные часы. Первая D-защелка с входом \ (D \) и выходом \ (Q1 \) называется

фиксатор master и отрицательно-чувствительный , потому что он

прозрачный при вводе часов \ (\ phi = 0. \) Вторая D-защелка

с входом \ (Q1 \) и выходом \ (Q \) – это защелка ведомого устройства , а положительно-чувствительный , потому что он прозрачен при вводе часов

\ (\ phi = 1.\) D-триггер – это срабатывание по положительному фронту потому что он хранит ввод \ (D \) на переднем фронте тактового сигнала. Если

мы инвертируем вход часов, триггер будет с отрицательным фронтом

запускается, и сохраняет ввод \ (D \) по заднему фронту тактового сигнала.

На рисунке 4.64 показана схема CMOS для положительного фронта.

сработал D-триггер. Схема экономит четыре транзистора за счет удаления

выходной инвертор мастер-защелки и входной инвертор

рабская защелка. Рисунок 4.64: 20-транзисторная КМОП-схема для срабатывания положительного фронта.

D-триггер сохраняет выходной инвертор мастер-защелки и

входной инвертор ведомой защелки. Чтобы понять функциональность D-триггера, рассмотрим переключатель

модели и соответствующие диаграммы форм сигналов на рисунках 4.65 и 4.66. Рисунок 4.65 иллюстрирует работу во время отрицательного полупериода

часы. Основная защелка прозрачна, и ввод \ (D \) может

распространяются на внутренний узел \ (Q1. \) Поскольку защелка подчиненного устройства непрозрачна,

вход \ (D \) не может распространяться за пределы \ (Q1 \) для вывода

\ (Q. \) Вместо этого защелка ведомого усиливает выходное значение

\ (Q. \) Рисунок 4.65: Модель переключения D-триггера и работа во время отрицательного полупериода

часов. Основная защелка прозрачна, а вспомогательная защелка

непрозрачный. Во время положительного полупериода часов, показанного на

На рис. 4.66 основная защелка непрозрачна, а

отключает вход \ (D \) от внутреннего узла \ (Q1. \) Таким образом,

главная защелка сохраняет последнее значение ввода \ (D \) перед

положительный фронт часов. Защелка ведомого прозрачна, выдвигается

значение \ (Q1 \) для вывода \ (Q, \), которое является последним значением

входа \ (D \) до положительного фронта тактового сигнала. Рисунок 4.66: Модель переключателя D-триггера и работа в течение положительного полупериода

часов. Основная защелка непрозрачна, а вспомогательная защелка

прозрачный. Обратите внимание, что выход \ (Q \) остается неизменным после отрицательных часов.

край, потому что непрозрачная защелка ведомого сохраняет во время отрицательного

полупериод значения, сохраненного мастер-защелкой во время предыдущего

положительный полупериод часов. Синхронизирующий фронт синхросигнала является критическим по времени переходом

D-триггер.В случае срабатывания D-триггера положительным фронтом,

нарастающий фронт часов превращается в спадающий фронт часов мастера