Обозначение цепей питания в иностранных материалах

РадиоКот >Статьи >Обозначение цепей питания в иностранных материалах

Каждый человек увлекающийся электроникой сталкивается с материалами иностранного происхождения. И будь то схема электронного устройства или спецификация на чип, там могут встречаться множество различных обозначений цепей питания, которые вполне могут ввести в замешательство начинающего или незнакомого с этой темой радиолюбителя. В интернете достаточно информации чтобы внести ясность в этот вопрос. Далее кратко изложено то что было найдено о происхождении обозначений и их применении.

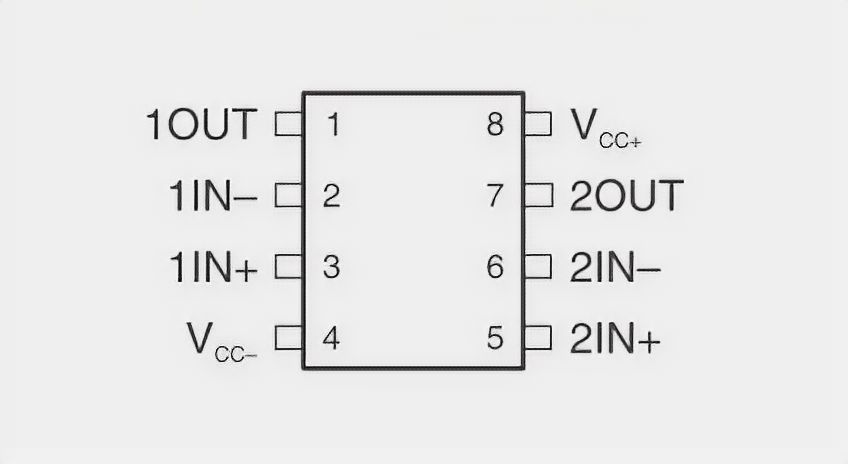

VCC, VEE, VDD, VSS – откуда такие обозначения? Обозначения цепей питания проистекают из области анализа схем на транзисторах, где, обычно, рассматривается схема с транзистором и резисторами подключенными к нему. Напряжение (относительно земли) на коллекторе (collector), эмиттере (emitter) и базе (base) обозначают V Резисторы подключенные к выводам транзистора обозначим RC, RE и RB. Напряжение на дальних (от транзистора) выводах резисторов часто обозначают VCC, VEE и VBB. На практике, например для NPN транзистора включенного по схеме с общим эмиттером, VCC соответствуют плюсу, а VEE минусу источника питания. Соответственно для PNP транзисторов будет наоборот.

Резисторы подключенные к выводам транзистора обозначим RC, RE и RB. Напряжение на дальних (от транзистора) выводах резисторов часто обозначают VCC, VEE и VBB. На практике, например для NPN транзистора включенного по схеме с общим эмиттером, VCC соответствуют плюсу, а VEE минусу источника питания. Соответственно для PNP транзисторов будет наоборот.

Аналогичные рассуждения для полевых транзисторов N-типа и схемы с общим истоком дают объяснение обозначений VDD и VSS (D — drain, сток; S — source, исток): VDD — плюс, VSS — минус.

Обозначения напряжений на выводах вакуумных ламп могут быть следующие: V P (plate, anode), VK (cathode, именно K, не C), VG (grid, сетка).

Как написано выше, Vcc и Vee используются для схем на биполярных транзисторах (VCC – плюс, VEE — минус), а Vdd и Vss для схем на полевых транзисторах (VDD – плюс, VSS — минус). Такое обозначение не совсем корректно, так как микросхемы состоят из комплементарных пар транзисторов. Например, у КМОП микросхем, плюс подключен к P-FET истокам, а минус к N-FET истокам. Тем не менее, это традиционное устоявшее обозначение для цепей питания независимо от типа проводимости используемых транзисторов.

Такое обозначение не совсем корректно, так как микросхемы состоят из комплементарных пар транзисторов. Например, у КМОП микросхем, плюс подключен к P-FET истокам, а минус к N-FET истокам. Тем не менее, это традиционное устоявшее обозначение для цепей питания независимо от типа проводимости используемых транзисторов.

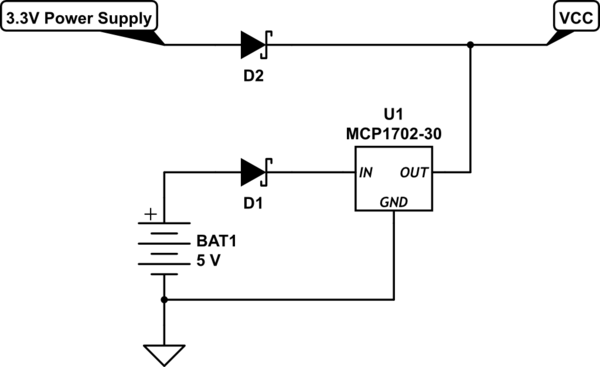

Для схем с двух полярным питанием VCC и VDD могут интерпретироваться как наибольшее положительное, а VEE и VSS как самое отрицательное напряжение в схеме относительно земли.

Для микросхем питающихся от одного или нескольких источников одной полярности минус часто обозначают GND (земля). Земля может быть разной, например, сигнальная, соединение с корпусом, заземление.

Вот перечень некоторых обозначений (далеко не полный).

|

Обозначение |

Описание |

Заметки |

|

GND |

Земля (минус питания) |

Ground |

|

AGND |

Аналоговая земля (минус питания) |

Analog ground |

|

DGND |

Цифровая земля (минус питания) |

Digital ground |

|

Vcc |

Плюс питания |

|

|

Vee |

Земля, минус питания |

|

|

Vref |

Опорное напряжение |

Reference (эталон, образец) |

|

Vpp |

Напряжение программирования/стирания |

(возможно pp = programming power) |

|

VCORE |

Напряжение питания ядра |

Core (ядро) Internal (внутренний) |

|

VIO |

Напряжение питания периферийных схем |

Input/Output (ввод/вывод) |

Как видно, часто обозначения образуются путём добавления слова, одной или нескольких букв (возможно цифр), которые соответствуют буквам в слове отражающем функцию цепи (например, как Vref).

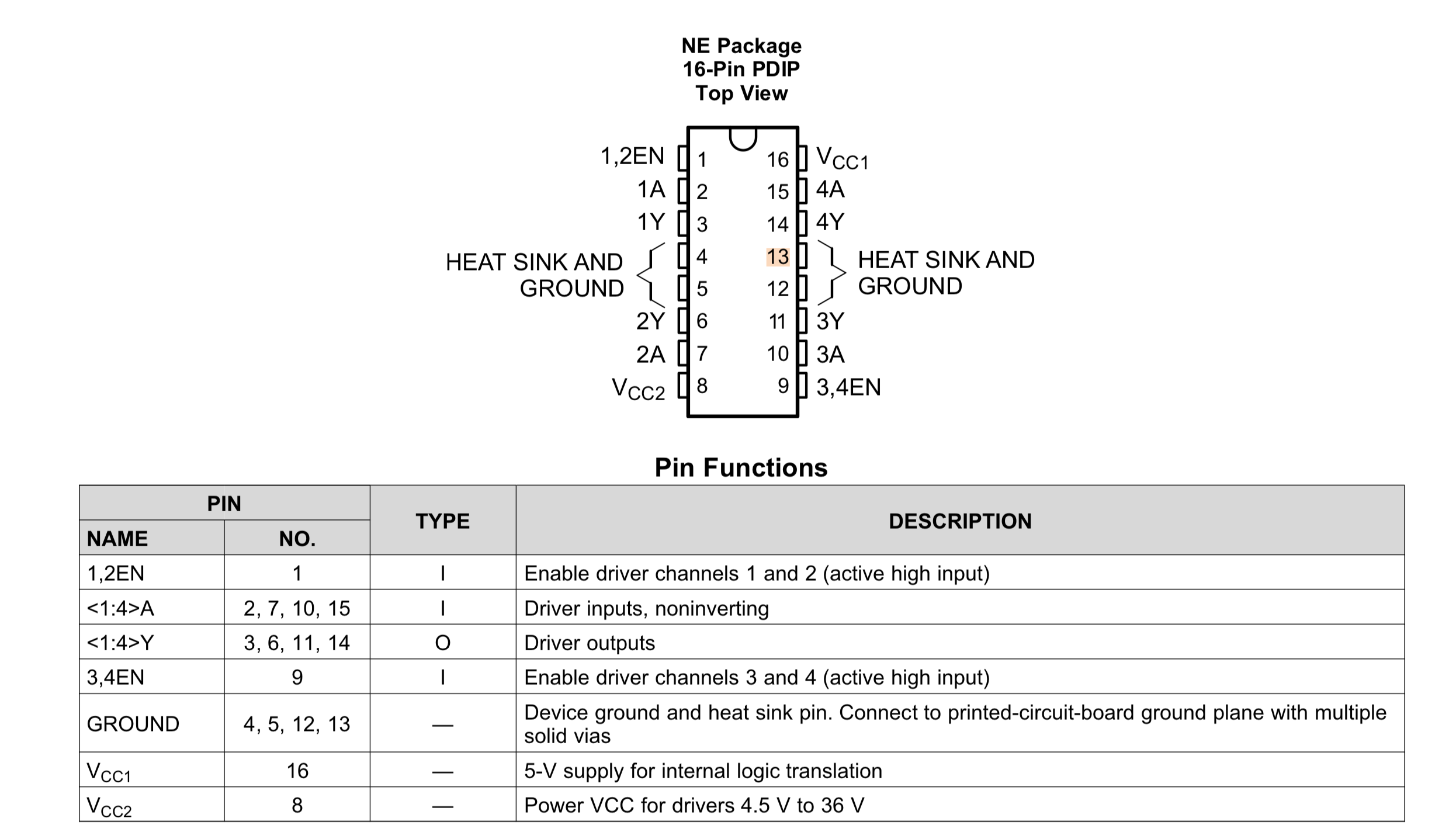

Иногда обозначения Vcc и Vdd могут присутствовать у одной микросхемы (или устройства), тогда это может быть, например, преобразователь напряжения. Так же это может быть признаком двойного питания. В таком случае, обычно, Vcc соответствует питанию силовой или периферийной части, Vdd питанию цифровой части (обычно Vcc>=Vdd), а минус питания может быть обозначен Vss.

Совмещение в современных микросхемах различных технологий, традиции, или какие-то другие причины, привели к тому, что нет чёткого критерия для выбора того или иного обозначения. Поэтому бывает, что обозначения «смешивают», например, используют VCC вместе с VSS или VDD вместе с VEE, но смысл, обычно, сохраняется — VCC > VSS, VDD > VEE. Например, практически повсеместно, можно встретить в спецификации на микросхемы серии 74HC (HC = High speed CMOS), 74LVC и др.

Текстов какого либо стандарта (ANSI, IEEE) по этой теме найти не удалось. Именно поэтому в тексте встречаются слова «может быть», «иногда», «обычно» и подобные. Несмотря на это, приведённой информации вполне достаточно, чтобы чуть лучше ориентироваться в иностранных материалах по электронике.

Информация собрана из различных источников в сети Интернет.

Специально для сайта radiokot.ru

Все вопросы в Форум.

Как вам эта статья? | Заработало ли это устройство у вас? |

GND — что это такое на схеме? (или на материнской плате)

Провод GND на материнской плате/схеме означает земля (масса, минус). Стандартный цвет — черный, белый. Варианты цвета провода питания — красный, синий, зеленый, оранжевый, желтый.

Стандартный цвет — черный, белый. Варианты цвета провода питания — красный, синий, зеленый, оранжевый, желтый.

Пример — обозначение черного провода маркировкой GND на разьеме подключения USB к материнской плате:

РЕКЛАМА

GND на материнской плате/схеме — важная информация

- GND (GROUND, перевод — земля) — точка нулевого потенциала микросхемы.

- VEE (Voltage Emitter Emitter, перевод — напряжение эмиттер) — минус питания относительно GND.

- VCC (Voltage Collector Collector, перевод — коллектор напряжения) — плюс питания относительно GND.

Стоит учитывать также:

- GND (DGND, GNDD) — обозначения цифровой земли.

- AGND (GNDA) — обозначения аналоговой земли.

Важный комментарий по поводу обозначений:

РЕКЛАМА

Простыми словами. Я подключал в компьютерном корпусе дополнительный вентилятор. Ноль вентилятора, черный провод — подключал к проводу молекс-разьема блока питания, который также имеет черный цвет (важно — это и есть GND). Питание на вентиляторе был желтым — его подключал к желтому проводу питания молекса. На молексе главное нужно понимать:

Я подключал в компьютерном корпусе дополнительный вентилятор. Ноль вентилятора, черный провод — подключал к проводу молекс-разьема блока питания, который также имеет черный цвет (важно — это и есть GND). Питание на вентиляторе был желтым — его подключал к желтому проводу питания молекса. На молексе главное нужно понимать:

- Желтый + черный = 12 вольт.

- Красный + черный = 5 вольт.

Еще по поводу молекса. Возможно так задумано, но кажется для подключения нужно использовать провода, которые идут рядышком. Например желтый и черный (12 вольт), красный и черный (5 вольт) — они идут рядом. Два черных провода GND возможно специально предназначены для двух видов подключения.

Под молекс разьемом подразумеваю данный тип коннектора (к нему подключаются жесткие диски например):

РЕКЛАМА

Также на плате/коннекторах можете заметить маркировку POWER — означает питание (плюс).

Подключая устройства, например переднюю панель ПК к материнке — будьте очень аккуратны, читайте инструкцию к материнской плате, чтобы не спалить например порты USB. Также смотрите на коннекторы и гнезда — иногда их конструкция исключает неправильное подключение. На заметку — кнопки компьютера, например включение, перезагрузка — неважно как подключить, дело в том, что здесь главное — замыкание. Неважно где плюс/минус, важно — замыкание контактов на секунду, что и делает кнопка, что и приводит к включению/выключению/перезагрузки компа.

Главное — правильно соблюдайте полярность, перед подключением не ленитесь сто раз проверить, чтобы быть уверенными. Ведь короткое замыкание — почти всегда ведет к неисправности..

Надеюсь информация кому-то пригодилась. Удачи и добра!

На главную! 09.06.2019РЕКЛАМА

Как обрабатывать несколько GND и + 5 В против VCC

Относитесь к каждой силе и земле как к индуктору и резистору с единицами nH и МОм и используйте XL (f) для переходных процессов переключения и шума сдвига земли вместе с законом Ома на нагрузку на источник. Р>

Р>

Поскольку проводник квадратного сечения имеет одинаковую индуктивность для любого размера, заземление и плоскость питания, очевидно, лучше, чем дорожка, но иногда соотношение 100: 1 L: d является адекватным. Р>

Пример, когда он недостаточен, подобен зондам 10: 1 с зажимами заземления 100 мм, которые резонируют с частотой 20 МГц. Вы толстые треки для власти и земли. Р>

Имейте в виду соотношение импеданса индуктивности источника и емкости нагрузки, а также ESR для шума и избегайте контуров заземления и контуров питания, которые действуют как антенна, а также как проводящий шум. Используйте распределенные заземления звезды или плоскости от источника питания и возвращайте для больших токов. Ничего особенного здесь нет, но OLED-дисплею требуется низкий аналоговый шум для передачи видеосигнала на источник. Добавьте 0,01 ~ 0,1 мкФ для страховки на каждый логический чип. Я использовал RLC Nomograph, чтобы избежать умопомрачительных расчетов импеданса для каждого компонента, чтобы понять частотные эффекты деталей и следов. Позже для ВЧ используются стриплайновые или микрополосковые калькуляторы для > 20МГц. Р>

Позже для ВЧ используются стриплайновые или микрополосковые калькуляторы для > 20МГц. Р>

Существуют очевидные основные предложения, которые вы можете прочитать в любом месте для Power Ground. Я просто добавил несколько тонких моментов, которые могут занять некоторое время.

Например, мы часто используем символы аналогового заземления, отличные от логического заземления и заземления, поскольку каждый из них является просто назначенным эталоном 0 В для сигналов, использующих это. То же самое относится к 5V и Vcc. Каждый из них может быть общим или физически развязанным путем понимания путей тока заряда и разряда сильноточных логических импульсов, например, 10 мА / 10 нс = 1 А / мкс, и большие электронные заглушки часто имеют ограничение 1 ~ 100 мкс ESR * C постоянной времени.

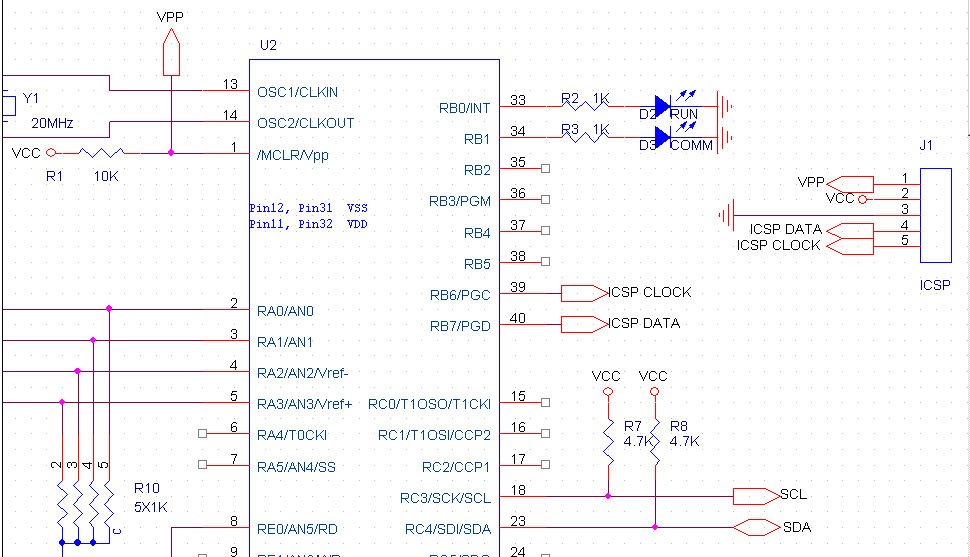

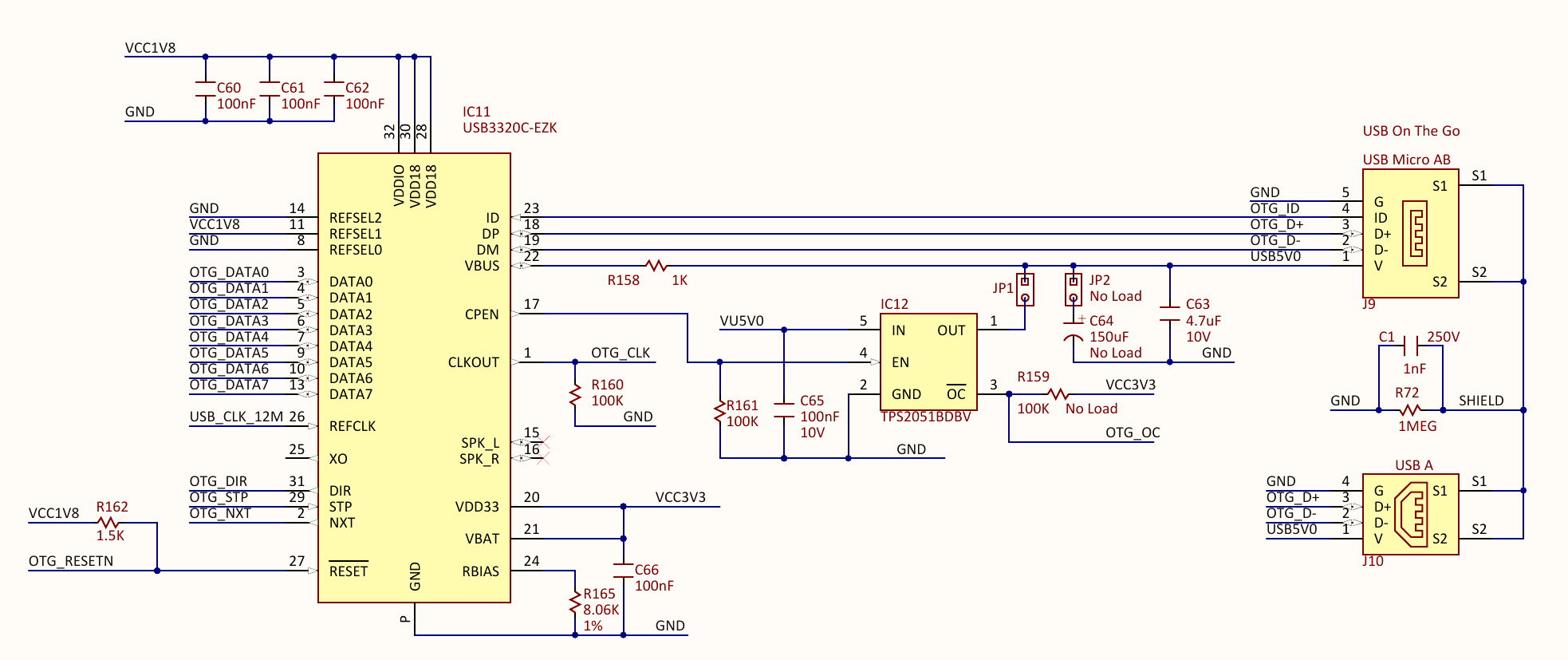

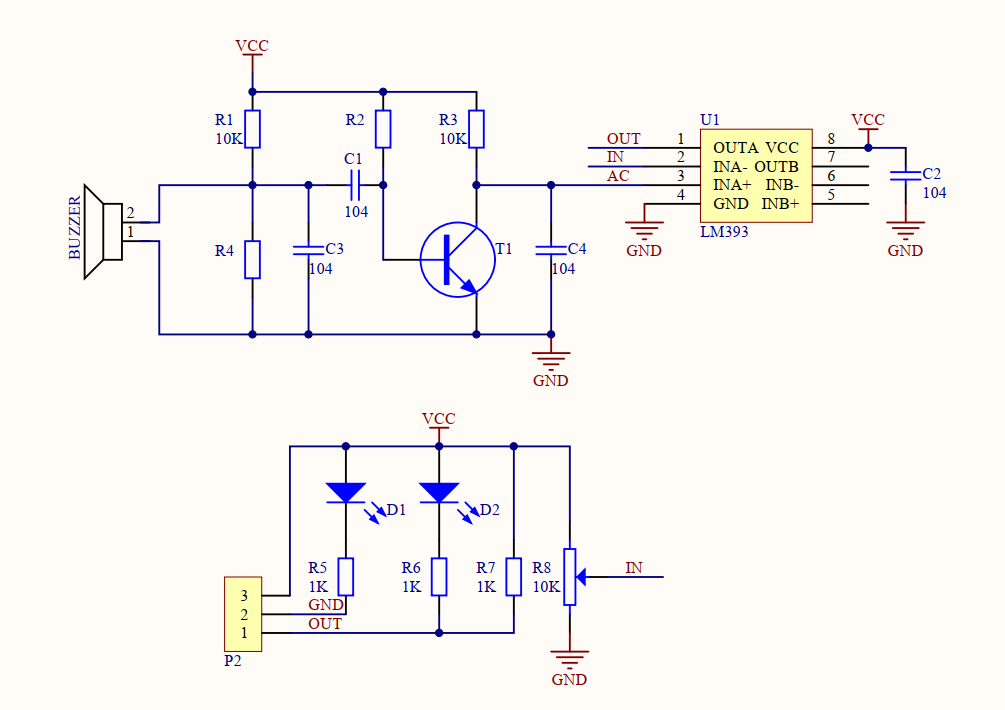

Почему в этой схеме есть короткое замыкание между VCC и GND?

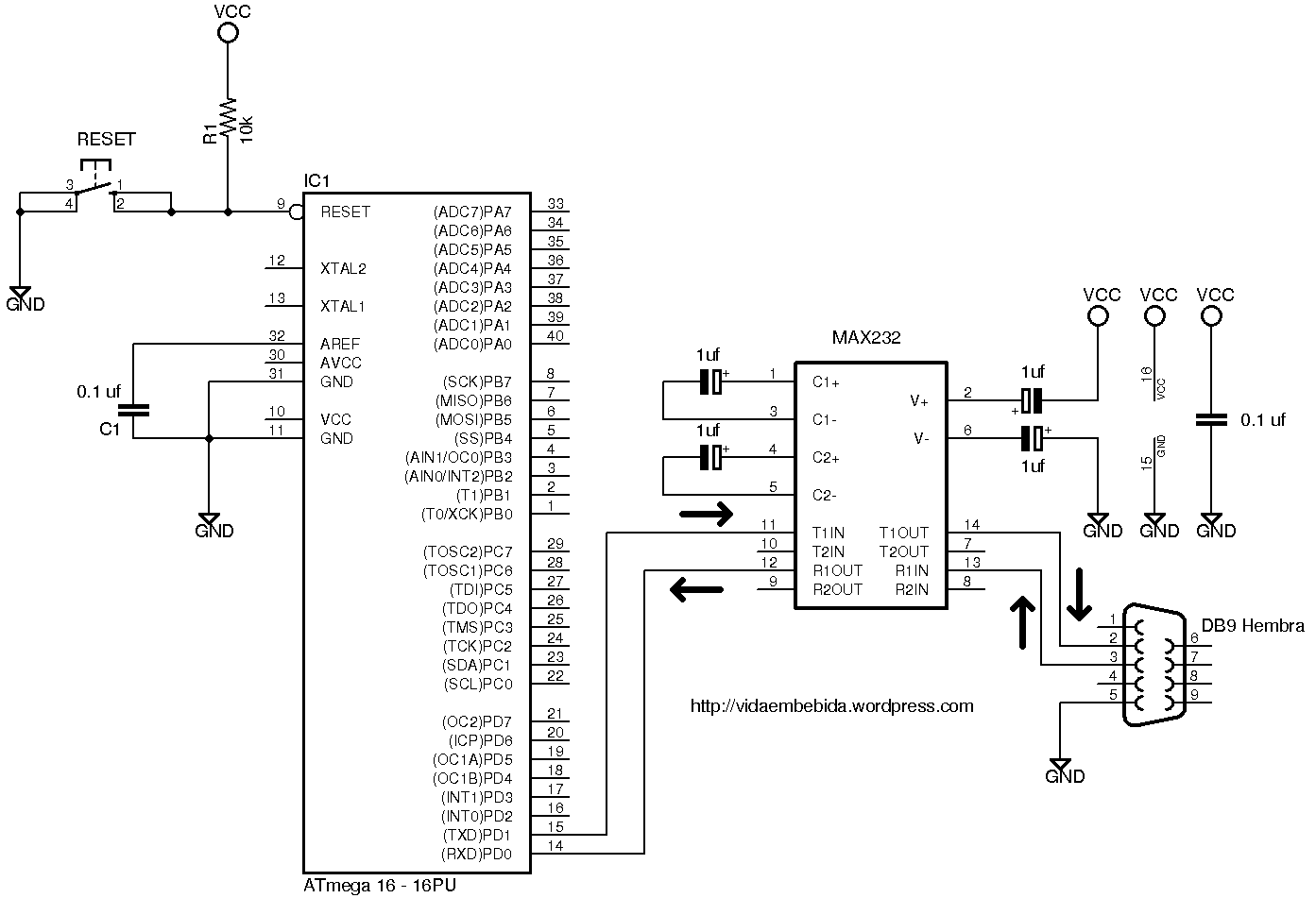

Я делаю проект, где я использую плату FPGA, которая подключается к схеме, которую я разработал. Он имеет четырехкомпонентный компаратор ( LM339N ), несколько резисторов и LDR; два датчика расстояния ( GP2Y0A51SK0F ) соединены с ним проводами, и цепь получает свое напряжение от платы ПЛИС (DE0-Nano, 4. 80 В). Компараторы также питаются от 4.80V от платы.

80 В). Компараторы также питаются от 4.80V от платы.

This is the schematic:

Как вы можете видеть, выход каждого датчика расстояния (этот датчик имеет только 3 контакта, я не мог сделать четвертый скрытый) переходит к компаратору. Дело в том, чтобы превратить датчик расстояния в датчик приближения и вывести «0», когда он видит что-то на определенном расстоянии. Затем FPGA получает это «0» и действует. Совсем то же самое с LDR.

Я могу подтвердить, что все сработало, когда я использовал два разных напряжения, когда тестировал это – один из них – 5 В, который входит в датчик расстояния и один 3,3 В, который идет на компараторы. Оба 3,3 В и 5 В поступали от источника постоянного тока.

Теперь я использую DE0-Nano для питания, единственным источником является один вывод 4,8 В и один вывод GND. Как видно из схемы, все имеет один блок питания.

Моя проблема – вещи не работают с датчиками расстояния; Пытаясь измерить напряжение на выходе каждого из датчиков, я получаю только 0 В, поэтому, очевидно, компараторы ничего не выводят. Я использую мультиметр, чтобы попытаться проверить, в чем проблема, и когда я пытался проверить шорты (с режимом, называемым непрерывностью, я думаю), может произойти одно из следующих действий (или вместе):

Я использую мультиметр, чтобы попытаться проверить, в чем проблема, и когда я пытался проверить шорты (с режимом, называемым непрерывностью, я думаю), может произойти одно из следующих действий (или вместе):

- Короче говоря, между VCC и GND, но между ними нет физической связи, я проверяю это с помощью режима сопротивления.

- Короткое замыкание между контактами VCC и GND LM339N

1 и 2 никогда не произойдет одновременно.

- Короткое замыкание между одним из выходов компараторов (U1 или U2) и VCC. Когда это произойдет, резисторы подтягивания 3K также являются короткими.

Как я уже сказал, физическая связь между VCC и GND отсутствует, поэтому я предполагаю, что короткий, который видит мультиметр, обусловлен тем, что контакты имеют одинаковый потенциал? Возможно ли, что подтягивающие резисторы слишком малы, и поэтому эта проблема возникает? Возможно ли, что я пожарил датчики расстояния?

Спасибо за вашу помощь, я тестировал это в течение нескольких дней и пытался выяснить, в чем проблема.

Изменить – вот несколько снимков экрана из области:

Это силовой контакт:

Это силовой штифт, увеличенный:

Это выход датчика:

Результат остается таким, несмотря ни на что, поэтому на самом деле не похоже, что он работает. возможно, амплитуда увеличивается, но я не думаю, что это имеет значение (это может быть и другой датчик, и я не помню).

Эти снимки экрана относятся только к одному датчику – другие показывают разные результаты, но при проверке их выхода никто, кажется, не реагирует.

Работа с электрическими цепями на схеме

Общие сведения

Цепь – это линия электрической связи, объединяющая компоненты, расположенные на схеме. Одна цепь может иметь неограниченное количество ответвлений. Цепь может состоять из ортогональных сегментов, которые размещаются по линиям базовой сетки схемотехнического редактора.

Размещение цепи

Для размещения электрической цепи на схеме выберите инструмент “Добавить цепь” из панели инструментов.

Допустимые объекты для начала размещения цепи

Если находясь в режиме размещения цепи, курсор наведен на объект, к которому можно подключить цепь, то на данном объекте отобразится зеленый квадрат, указывающий на возможность начала размещения цепи.

Точкой начала размещения цепи может быть:

Запрещенные объекты для начала размещения цепи

Если находясь в режиме размещения цепи, курсор наведен на объект, к которому подключение цепи невозможно, то на таком объекте отобразится красный квадрат.

| Произвольная точка рабочей области | |

| Точка пересечения цепей | |

| Узел соединения цепей с четырьмя подключениями | |

| Графика порта (силового и соединительного) |

Также запрещается проведение цепи поверх размещенного на схеме компонента. Графикой компонента считается вся область находящаяся внутри линий границ компонента, установленных в настройках данного УГО. При проведении цепи запрещается наложение ее сегментов на имеющиеся на схеме цепи и шины.

При проведении цепи запрещается наложение ее сегментов на имеющиеся на схеме цепи и шины.

Способы размещения цепи

Выбрав инструмент размещения цепи и указав точку, с которой будет начинаться цепь, под курсором начнет пунктиром отображаться предварительный вид цепи и ее имя (Рис. 1).

| Рис. 1 – Предварительный вид цепи |

Существуют два способа провести цепь к нужной точке подключения:

- автоматическая прокладка цепи

- ручной режим размещения цепи

Автоматическая прокладка цепи

При автоматической прокладке цепи требуется задать лишь начальную и конечную точки подключения, и цепь будет проложена автоматически. При задании конечной точки цепи она также как и начальная, должна быть доступной для выполнения подключения. При построении цепи будут учтены все области, по которым запрещена прокладка цепи (Рис. 2).

Рис. 2 – Автоматическая прокладка цепи 2 – Автоматическая прокладка цепи |

Однако автоматическая прокладка цепи не всегда обеспечивает оптимальную форму итоговой цепи. Во избежание этого пользователь может использовать ручной режим размещения цепи.

Ручной режим размещения цепи

Цепь в общем случае состоит из сегментов – прямых участков цепи. Ручной режим обеспечивает поэтапное задание этих сегментов. После начала размещения цепи, при перемещении курсора по схеме показывается предварительный вид цепи, состоящей из одного или нескольких сегментов. После нажатия левой кнопки мыши показанные сегменты фиксируются, а инструмент продолжает оставаться активным для последующего размещения цепи. При дальнейшем перемещении курсора показывается предварительный вид цепи, автоматически построенной от последней зафиксированной точки до текущего положения курсора, зафиксированные сегменты остаются неизменными (Рис. 3).

| Рис. 3 – Ручной режим размещения цепи |

Ручной режим размещения и автоматическая прокладка цепи могут быть использованы комбинированно, так как автоматическая прокладка доступна при наличии зафиксированных вручную сегментов.

После того, как была указана конечная точка подключения цепи, цепь принимает свой окончательный вид, все ее сегменты фиксируются. Инструмент остается активным для размещения новой цепи. Для того чтобы выйти из режима размещения цепи, нажмите правую кнопку мыши и в контекстном меню выберите пункт “Выйти из инструмента”.

Также можно завершить цепь в произвольном месте редактора. Для этого зафиксируйте один или несколько сегментов цепи, нажмите правую кнопку мыши и выберите пункт “Завершить”. В этом случае на конце последнего зафиксированного сегмента образуется символ свободного конца проводника (или незавершенной цепи). Этот символ означает, что данная точка доступна для электрического подключения.

|

Рис. 4 – Завершение цепи в произвольном |

Рис. 5 – Завершение цепи в произвольном |

Для того чтобы в режиме размещения цепи удалить все ее построенные сегменты, нажмите правую кнопку мыши и выберите пункт “Отменить”. При этом будут удалены все зафиксированные сегменты и произойдет выход из инструмента размещения цепи.

Редактирование цепи

Вид (траекторию) проложенной цепи можно отредактировать. Для работы с цепью или ее сегментами, их необходимо выделить.

Выделение цепи

- Наведите курсор на цепь. Цепь будет подсвечена и во всплывающей подсказке будет отображено имя цепи (Рис. 6).

- Нажмите левую кнопку мыши. Будет выделен тот сегмент цепи, который находится под курсором мыши (Рис. 7).

- Нажмите левую кнопку мыши еще раз. Цепь будет выделена целиком (Рис. 8). Повторное нажатие левой кнопки мыши опять приведет к выделению сегмента цепи, находящегося под курсором.

| Рис. 6 – Наведение курсора на цепь | Рис. 7 – Выделение сегмента цепи | Рис. 8 – Выделение цепи целиком |

С помощью рамки выделения можно выделить только всю цепь целиком.

Перемещение сегментов цепи

- Выделите сегмент цепи, который нужно переместить (Рис. 9).

- С зажатой левой кнопкой мыши перетащите выделенный сегмент. Сегмент может перемещаться только параллельно своему изначальному положению, за счет изменения соседних сегментов (Рис. 10).

- Отпустите левую кнопку мыши, новое положение сегмента зафиксируется. Если при перемещении сегмент оказался совмещен с другими сегментами, то эти сегменты будут объединены.

| Рис. 9 – Перемещение сегмента (Шаг 1) | Рис. 10 – Перемещение сегмента (Шаг 2) |

Свойства цепи

В зависимости от того, выделен сегмент цепи или вся цепь целиком, в панели “Свойства” будет отображаться разный набор свойств (Рис. 11, 12).

| Рис. 11 – Свойства сегмента цепи | Рис. 12 – Свойства цепи 12 – Свойства цепи |

Параметры в панели “Свойства” можно разделить на три группы:

- Общие свойства цепи

В поле “Имя” отображается текущее имя цепи, которое доступно для редактирования. Имя цепи можно изменить и через свойства сегмента цепи, и через свойства всей цепи. В полях “Лист” и “Проект” отображается справочная информация об имени листа, на котором размещена цепь, и названии проекта. - Стиль отображения цепи

В категории “Линия” отображаются параметры стиля цепи. Данные свойства доступны для редактирования только через свойства всей цепи. - Свойства метки цепи

В свойствах сегмента цепи присутствует категория “Метка”, содержащая параметры отображения метки у данного сегмента. Метка цепи представляет собой текстовую надпись, содержащую имя данной цепи (Рис. 13). Для того чтобы включить отображение метки у сегмента, поставьте флажок в поле “Метка”.

Рис. 13 – Метка сегмента цепи

Настройка отображения метки сегмента

Для метки сегмента цепи доступны следующие возможности редактирования:

- Изменение места отображения

Для этого выделите метку цепи, кликнув на ней левой кнопкой мыши, и перетащите в требуемое место схемы (Рис. 14). При сохранении проекта схемы, также сохранится и новое местоположение метки сегмента цепи.

Рис. 14 – Перемещение метки цепи - Изменение стиля текста метки

Выделите метку, кликнув на ней левой кнопкой мыши, в панели “Свойства” будут показаны свойства этого графического объекта (Рис. 15). В поле “Шрифт” можно изменить стиль текста метки, в поле “Цвет текста” – задать другой цвет текста.

Рис. 15 – Свойства метки цепи

Переименование цепи

При создании новой цепи ей по умолчанию присваивается имя в формате “NETXXXX”, где “XXXX” – номер цепи, то есть “NET0001”, “NET0002” и т. д. Имя цепи можно изменить в панели “Свойства”, выделив сегмент цепи или всю цепь целиком. При этом переименование сегмента цепи приводит к изменению имени всей цепи.

д. Имя цепи можно изменить в панели “Свойства”, выделив сегмент цепи или всю цепь целиком. При этом переименование сегмента цепи приводит к изменению имени всей цепи.

- Выделите требуемую цепь или ее фрагмент

-

В панели “Свойства” нажмите на три точки “…” в поле “Имя” (Рис. 16)

Рис. 16 – Вызов формы переименования цепи -

Откроется форма переименования цепи (Рис. 17). В поле “Текущее название цепи” отображается имя цепи в данный момент. В поле “Введите новое имя…” можно задать новое имя цепи. Если поставить флажок в поле “Использовать генерацию имен цепей”, то поле ввода имени цепи и список цепей проекта станут неактивны. При этом цепи будет присвоено новое имя в формате по умолчанию (“NETXXXX”) с ближайшим незанятым номером. В списке “Выберите имя цепи из списка” отображается список всех цепей проекта.

Если на схеме нет других цепей с тем же именем, что и текущая, то будет выбран и доступен только пункт “Применить действие ко всей цепи”. Если же на схеме есть другие цепи с таким же именем, то пользователь может выбрать способ переименования цепи. Если выбрать пункт “Применить действие ко всей цепи”, то и данная цепь, и все остальные цепи с таким же именем, изменят свое имя на выбранное в данной форме. Если выбрать пункт “Применить действие к фрагменту цепи”, то будет переименована только текущая цепь, все же остальные цепи с данным именем сохранят свои имена.

Если на схеме нет других цепей с тем же именем, что и текущая, то будет выбран и доступен только пункт “Применить действие ко всей цепи”. Если же на схеме есть другие цепи с таким же именем, то пользователь может выбрать способ переименования цепи. Если выбрать пункт “Применить действие ко всей цепи”, то и данная цепь, и все остальные цепи с таким же именем, изменят свое имя на выбранное в данной форме. Если выбрать пункт “Применить действие к фрагменту цепи”, то будет переименована только текущая цепь, все же остальные цепи с данным именем сохранят свои имена.Рис. 17 – Форма переименования цепи - Укажите новое имя цепи в форме переименования и нажмите кнопку “Изменить”.

Соединение цепей

В схемотехническом редакторе цепи могут быть соединены несколькими способами:

- если между ними есть линии электрической связи;

- если они имеют одинаковые имена;

- с помощью портов.

Цепи могут быть соединены как на одном листе, так и на разных листах проекта. Рассмотрим первые два способа

Соединение цепей с помощью линий электрической связи

При подключении одной цепи в редакторе к другой цепи (Рис. 18), в точке их соединения образуется узел соединения, обозначающий, что эти цепи соединены друг с другом (Рис. 19).

| Рис. 18 – Соединение цепей в редакторе (Шаг 1) | Рис. 19 – Соединение цепей в редакторе (Шаг 2) |

У цепей при их физическом соединении линией электрической связи автоматически меняются имена таким образом, что в результате все сегменты итоговой цепи имеют одно и то же имя.

- Если ни на одной из соединяемых цепей нет порта, то итоговое имя определяется порядком подключения.

- При соединении двух размещенных на схеме цепей, итоговая цепь будет иметь имя той цепи, с которой мы начали размещать линию связи (в приведенном выше примере это цепь “NET0002”).

- Если к имеющейся на схеме цепи подсоединяется новая цепь, то независимо от порядка подключения, итоговая цепь будет иметь имя имеющейся (изначальной) цепи.

- При соединении двух размещенных на схеме цепей, итоговая цепь будет иметь имя той цепи, с которой мы начали размещать линию связи (в приведенном выше примере это цепь “NET0002”).

- Если на одной из цепей есть порт (силовой или соединительный), то итоговая цепь будет иметь имя цепи, у которой есть порт.

Соединение свободных концов цепи

Как говорилось выше, в редакторе схем можно продолжить размещение цепи из свободного конца проводника (Рис. 20).

| Рис. 20 – Свободный конец цепи |

Соединить свободный конец проводника с выводом компонента, имеющейся цепью или другим свободным концом цепи можно несколькими способами:

- С помощью инструмента размещения цепи

Для этого нужно выбрать инструмент “Добавить цепь”, выбрать в качестве начальной точки свободный конец проводника, а затем в качестве конечной точки указать необходимый объект. В результате символ свободного конца проводника исчезнет и от него построятся линии электрического соединения.

-

С помощью перетаскивания свободного конца цепи

Для этого нужно выделить символ свободного конца цепи и перетащить его к объекту, к которому необходимо произвести подключение цепи – автоматически произойдет соединение незавершенной цепи и выбранного объекта (Рис. 21, 22).Рис. 21 – Образование соединения при перетаскивании свободного конца цепи (Шаг 1) Рис. 22 – Образование соединения при перетаскивании свободного конца цепи (Шаг 2)

Соединений цепей с помощью их переименования

Соединить цепи в редакторе можно также с помощью задания у этих цепей одинаковых имен. В таком случае цепи считаются соединенными, даже если между ними нет физических линий связи.

- Выделите цепь, которую нужно соединить с другой цепью, или ее сегмент.

- В панели “Свойства” вызовите форму переименования цепи из поля “Имя” (Рис. 16).

- В открывшей форме выберите из списка цепь, с которой нужно произвести соединение (также можно ввести это имя в поле “Введите новое имя…”).

- Нажмите кнопку “Изменить”.

Размещение портов

В отличие от цепей, которые создают физические соединения на схеме, порты используются для создания логических соединений. Порты используются в тех случаях, когда проведение линий электрического соединения либо невозможно (например, соединение между разными листами схемы), либо загромождает схему.

Добавление порта

В программе Delta Design порт создается непосредственно для выбранной цепи. Необходимо завершить цепь в произвольном месте редактора, чтобы образовался символ свободного конца цепи. На месте этого символа и будет создан порт.

Порты делятся на две группы:

- силовые;

- соединительные.

Добавление силового порта

- Выделите символ свободного конца цепи.

-

Нажмите правую кнопку мыши и из контекстного меню выберите пункт “Разместить порт питания” (Рис. 23).

Рис. 23 – Вызов формы для размещения силового порта -

Откроется форма размещения силового порта (Рис. 24).

Рис. 24 – Форма размещения силового порта В поле “УГО порта” выберите символ силового порта (“GND (Земля)”, “GND (Корпус)”, “VCC (Питание)”). Каждому порту соответствует свой символ. В этом же выпадающем списке будут показываться все созданные пользовательские порты с типом “Порт питания”.

В категории “Имя цепи” выберите способ формирования имени цепи, на которой создается порт. “Взять имя цепи из порта” – имя цепи будет взято из имени порта. “Взять имя цепи из схемы” – имя цепи будет взято из схемотехнического редактора, т.е. цепь сохранит свое имя. “Задать имя цепи” – задать новое имя цепи; в этом случае поле ввода, расположенное ниже, станет доступно для ввода нового имени.

Как и в случае с переименованием цепей, если в проекте существуют другие цепи с таким же именем, что и текущая, существует возможность выбора параметров переименования связанных цепей. Если выбрать пункт “Переименовать только часть цепи”, то при образовании порта будет переименована только сама цепь, на которой создается порт. Если выбрать пункт “Переименовать всю цепь”, то будут еще переименованы другие цепи проекта с тем же именем.

-

Выбрав необходимые параметры, нажмите кнопку “OK”. Вместо символа свободного конца цепи будет создан силовой порт (Рис. 25).

Рис. 25 – Силовой порт

Добавление соединительного порта

Соединительные порты используются для образования логического соединения цепей в рамках одного листа или на разных листах проекта.

-

Если в проекте нет созданных соединительных портов, открывшаяся форма размещения соединительного порта будет выглядеть следующим образом (Рис. 27).

Рис. 27 – Форма размещения соединительного порта (новый порт) В поле “Port Symbol” выберите символ соединительного порта (“Внутрилистовой”, “Межлистовой”). Каждому порту соответствует свой символ. В этом же выпадающем списке будут показываться все созданные пользовательские порты с типом “Соединитель”. Так как в проекте нет других соединительных портов, то создаваемый порт пока не будет ни с чем соединен (“First Connector”).

-

Если в проекте уже есть созданные соединительные порты, то при добавлении нового соединительного порта, его можно связать с одним из таких портов. Форма размещения соединительного порта будет выглядеть следующим образом (Рис. 28).

Рис. 28 – Форма размещения соединительного порта (соединение с другим портом) Для соединения нового порта с одним из имеющихся в проекте выберите пункт “Connect To Port”, при этом станет активным выпадающий список расположенный ниже. В нем отображаются все соединительные порты данного проекта. Выберите нужный порт из списка и нажмите кнопку “OK”. Новый порт будет добавлен с тем же именем, что и указанный порт в списке. Соответствующая новому порту цепь тоже будет переименована.

Перемещение порта в редакторе схем

Размещенный на схеме порт (любого типа), также как и свободный конец цепи, можно перемещать на листе схемы. Для этого выделите порт и, с зажатой левой кнопкой мыши, перетащите его на нужное место на листе. При этом стоит отметить, что перерасчет траектории цепи, связанной с портом, будет происходить от точки последнего места размещения этого порта (Рис. 29, 30).

| Рис. 29 – Перемещение порта (Шаг 1) | Рис. 30 – Перемещение порта (Шаг 2) |

По аналогии со свободными концами цепей, можно произвести подключение порта с другим объектом с помощью перетаскивания порта. Если перетащить порт к объекту, с которым возможно произвести подключение, то порт исчезнет и произойдет соединение цепи, связанной с портом, и выбранного объекта.

Изменение типа и символа порта

Изменение типа порта

Чтобы сменить тип порта с силового на соединительный (или наоборот), нужно сначала удалить имеющийся порт, чтобы в результате образовался символ свободного конца цепи. Тогда для него будут снова доступны функции размещения порта, из которых необходимо выбрать нужную.

Изменение символа порта

- Для силовых портов невозможно изменить символ порта, т.е. для того чтобы, например, изменить символ с “GND” на “VCC” нужно удалить силовой порт и разместить на его месте новый порт с требуемым символом.

-

Для соединительных портов доступно изменение символа порта. Для этого выделите соединительный порт в редакторе, в панели “Свойства” раскройте выпадающий список в поле “УГО” и измените символ порта (Рис. 31). При этом изменится графика соединительного порта в редакторе.

Рис. 31 – Изменение символа соединительного порта

Стоит отметить, что пользователь сам контролирует использование соединительных портов и смену их символов. То есть, внутрилистовой порт можно соединить с межлистовым портом или изменить произвольным образом символ соединительного порта. Данные преобразования должны определяться логикой построения электрической схемы.

Удаление порта

Для того чтобы удалить порт, выделите его в редакторе, кликните на нем правой кнопкой мыши и выберите из контекстного меню пункт “Удалить” (Рис. 32).

| Рис. 32 – Удаление порта |

При этом символ силового или соединительного порта исчезнет, и на конце цепи появится символ свободного конца проводника.

- Если происходит удаление соединительного порта, то оставшаяся цепь сохраняет имя удаленного порта. Другими словами, удаление соединительного порта не производит логическое разъединение цепей, которые были объединены с помощью этих портов. Для того чтобы разъединить цепи, нужно явно изменить их имена.

- Если происходит удаление силового порта, то оставшаяся цепь изменяет свое имя на ближайшее свободное имя по умолчанию. Таким образом, удаление силового порта приводит к разъединению соответствующей цепи от остальных силовых портов.

Работа с цепями в панели “Менеджера проекта”

Просмотр списка цепей

Для того чтобы увидеть информацию обо всех электрических цепях проекта, необходимо открыть панель “Менеджер проекта” и перейти на закладку “Цепи” (Рис. 33).

| Рис. 33 – Панель “Менеджер проекта” (Закладка “Цепи”) |

В верхней части панели отображается строка поиска по содержимому активной закладки панели. Внутри узла с именем проекта (“Test_01”) находится список разделов. В папке “Цепи” отображается перечень всех цепей проекта. При выделении какой-либо цепи в нижней части панели показывается информация о подключениях данной цепи к выводам компонентов с указанием имени компонента и названия листа.

Цепи питания

Цепи питания – это цепи, имеющие порты питания, или объединенные с ними цепи. Информацию о силовых цепях можно посмотреть двумя способами:

-

в папке “Цепи питания” на панели “Менеджер проекта” – отображается список всех силовых цепей проекта (Рис. 34).

Рис. 34 – Папка “Цепи питания” -

с помощью формы просмотра силовых выводов – форма вызывается из панели “Менеджер проекта” (Рис. 35).

Рис. 35 – Вызов формы силовых выводов При выборе пункта “Управление контактами цепей питания” откроется форма просмотра силовых выводов (Рис. 36). В таблице представлена информация обо всех силовых цепях и выводах, которые к ним подсоединены. Если поставить флажок в поле “Group by Nets”, данные будут сгруппированы по имени цепи. В этом случае таблица примет вид, аналогичный списку силовых цепей в папке “Цепи питания”.

Помимо цепей питания, непосредственно размещенных в редакторе схем, в таблице также будет показана информация о скрытых силовых выводах компонентов, находящихся на схеме. При добавлении на схему компонента со скрытым выводом, автоматически будет создаваться цепь с именем этого вывода. Так, выводы “7” и “14” у компонента “DD1” на рис. 36 являются скрытыми и не присутствуют в явном виде на схеме, однако для них создаются силовые цепи “GND” и “VCC” соответственно.

Рис. 36 – Форма просмотра силовых выводов

Функции доступные для цепи

В панели “Менеджер проекта” для цепей доступны следующие функции:

Показать цепь на схеме

Выделите необходимую цепь, кликните на ней правой кнопкой мыши и в контекстном меню выберите пункт “Показать на схеме” (Рис. 37). В результате выбранная цепь будет подсвечена в редакторе, при этом все остальные объекты на листе будут отображаться слегка приглушенно. Чтобы выйти из данного режима, кликните в редакторе правой кнопкой мыши и выберите пункт “Выйти из инструмента” (Рис. 38).

| Рис. 37 – Функция “Показать на схеме” | Рис. 38 – Выход из режима подсветки цепи на схеме |

Чтобы подсветить цепь на схеме, можно также дважды кликнуть на ней левой кнопкой мыши в панели “Менеджер проекта”.

Выделить цепь

Выберите необходимую цепь, кликните на ней правой кнопкой мыши и в контекстном меню нажмите пункт “Выделить” (Рис. 39). В результате выбранная цепь окажется выделенной в редакторе, при этом все остальные объекты сохранят свое обычное отображение (Рис. 40). В панели “Свойства” будут показаны свойства выделенной цепи, доступные для редактирования. Если аналогичным образом выделить теперь другую цепь из списка, то она добавится к выделению первой цепи в редакторе. Таким образом, такое последовательное выделение цепей из панели “Менеджер проекта” является аналогом группового выделения в редакторе с помощью клавиши Shift.

| Рис. 39 – Функция “Выделить” | Рис. 40 – Результат работы функции “Выделить” |

Подсветить цепь

Для электрических цепей доступна возможность подсветки цепей разными цветами для более удобного просмотра и анализа схемы. Подсветка цепей не сохраняется при сохранении проекта схемы и используется только как средство текущего момента разработки схемы.

Подсветить цепи можно двумя способами:

Показать / выделить вывод выбранной цепи

При выделении цепи в панели “Менеджер проекта” в нижней части панели показывается информация о выводах компонентов, к которым эта цепь подключена. Из панели “Менеджер проекта” есть возможность подсветить нужный вывод в редакторе схем.

Также как и для самих цепей, для выводов существует две функции:

- Показать вывод на схеме

Кликните по нужному выводу правой кнопкой мыши и из контекстного меню выберите пункт “Показать на схеме” (Рис. 45). При этом вывод будет подсвечен в редакторе, при этом все остальные объекты на листе будут отображаться слегка приглушенно. Чтобы выйти из данного режима, кликните в редакторе правой кнопкой мыши и выберите пункт “Выйти из инструмента”

Рис. 45 – Показать вывод на схеме - Выделить вывод

Кликните по нужному выводу правой кнопкой мыши и из контекстного меню выберите пункт “Выделить” (Рис. 46). Выбранный вывод окажется выделенным в редакторе, при этом все остальные объекты сохранят свое обычное отображение. В панели “Свойства” будут показаны свойства выделенного вывода, доступные для редактирования.

Рис. 46 – Выделить вывод на схеме

Микросхемы УМЗЧ TA8216HQ, TA8258HQ » Паятель.Ру

Микросхемы производятся фирмой Toshiba и представляют собой двухканальные усилители мощности ЗЧ с однополярным питанием для применения в бытовой аудиотехнике TA8216HQ и TA8258HQ аналогичны по конструкции и типовой схеме включения, но различаются по электрическим параметрам, в основном, по мощности и питанию.

Микросхемы выполнены в 12-выводных корпусах HZIP12-P-1 78В Предусмотрен режим блокировки (mute) изменением напряжения на выводе 11. Порог переключения 2,8V (mute-on: +2.8…+10V, mute-off. 0… + 1.5V).

Технические параметры TA8216HQ:

1. Напряжение питания (Vcc), при RL 8 Оm…………………… 10…37V.

2. Напряжение питания (Vcc), при RL4 Оm…………………… 10…24V.

3. Ток покоя не более……… 105mА. (при Vcc = 28V……………. 50mА).

4. Максимальный выходной ток… 3А.

5. Максимальная выходная мощность при Vcc = 28V и КНИ = 10%, при RL 8 Оm ……….. 2×13 W.

6. Максимальная выходная мощность при Vcc = 24V и КНИ = 10%, при RL 4 Оm ……… 2×13 W

7. Выходная мощность при Vcc – 28V и КНИ = 1%, RL 8 Оm … 2x10W.

8. КНИ при выходной мощности 2W не более 0,2% (норм 0,04%).

9. Коэффициент усиления ….. 34dB.

10. Максимально допустимое напряжение питания……..40V.

11. Сопротивление нагрузки (RL) ……. 4-8 Оm.

12. Входное сопротивление……30 kOm.

Технические параметры TA8258HQ:

1. Напряжение питания (Vcc), при … 15 … 42V, (номинальное .. 37V)

2. Ток покоя не более………………. 130mA, (при Vcc = 37V………….. 75mA)

3. Максимальный выходной ток ……….. 3,5А.

4. Максимальная выходная мощность при Vcc = 37V и КНИ = 10% ……… 2×20 W

5. Выходная мощность при Vcc = 37V и КНИ = 1% ……………………….. 2×15 W.

7. КНИ при выходной мощности 2W не более ……………..0,2% (норм. 0,05%).

8. Коэффициент усиления ……………34dB.

9. Максимально допустимое напряжение питания……………………50V.

10. Сопротивление нагрузки…..(RL) 8 Оm.

11. Входное сопротивление…………30 kOm.

12. Степень блокировки (mute)…….-60dB.

Характеристики микросхемы TA8216HQ:

1. Зависимость выходной мощности от напряжении питания.

2. Зависимость коэффициента нелинейных искажений (КНИ) от выходной мощности.

3. Зависимость КНИ от частоты сигнала.

Характеристики микросхемы TA8258HQ:

1. Зависимость выходной мощности от напряжени питания.

2. Зависимость коэффициента нелинейных искажений (КНИ) от выходной мощности.

3. Зависимость КНИ от частоты сигнала

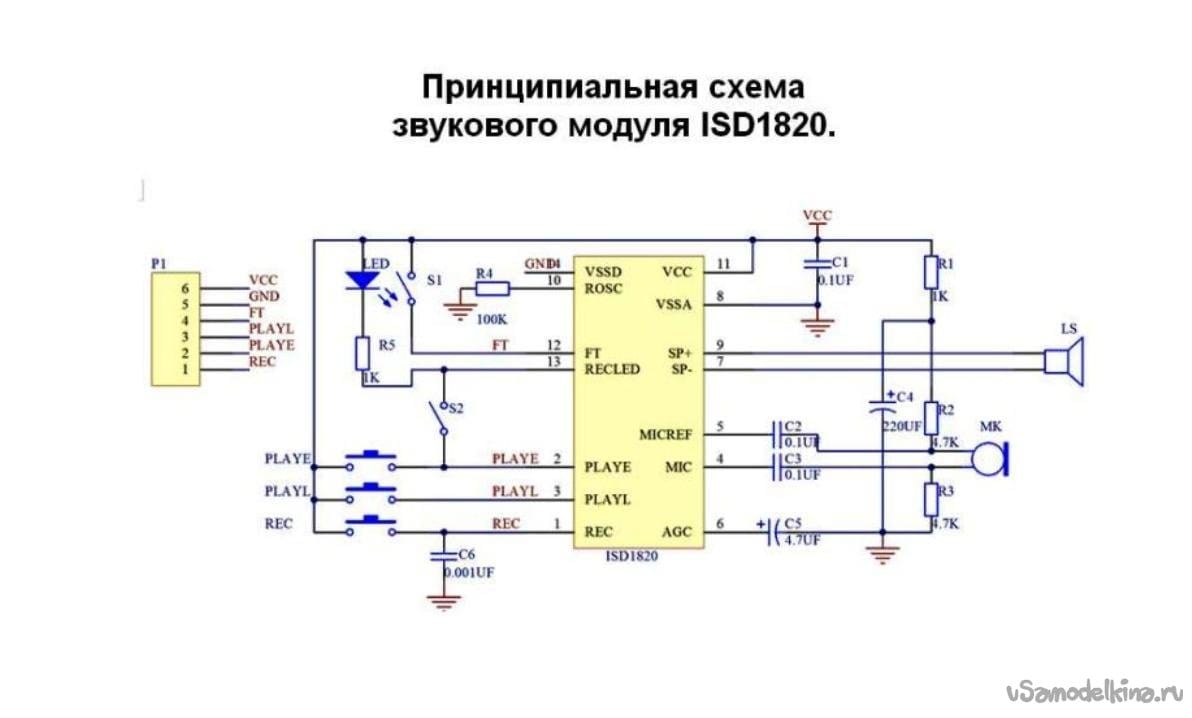

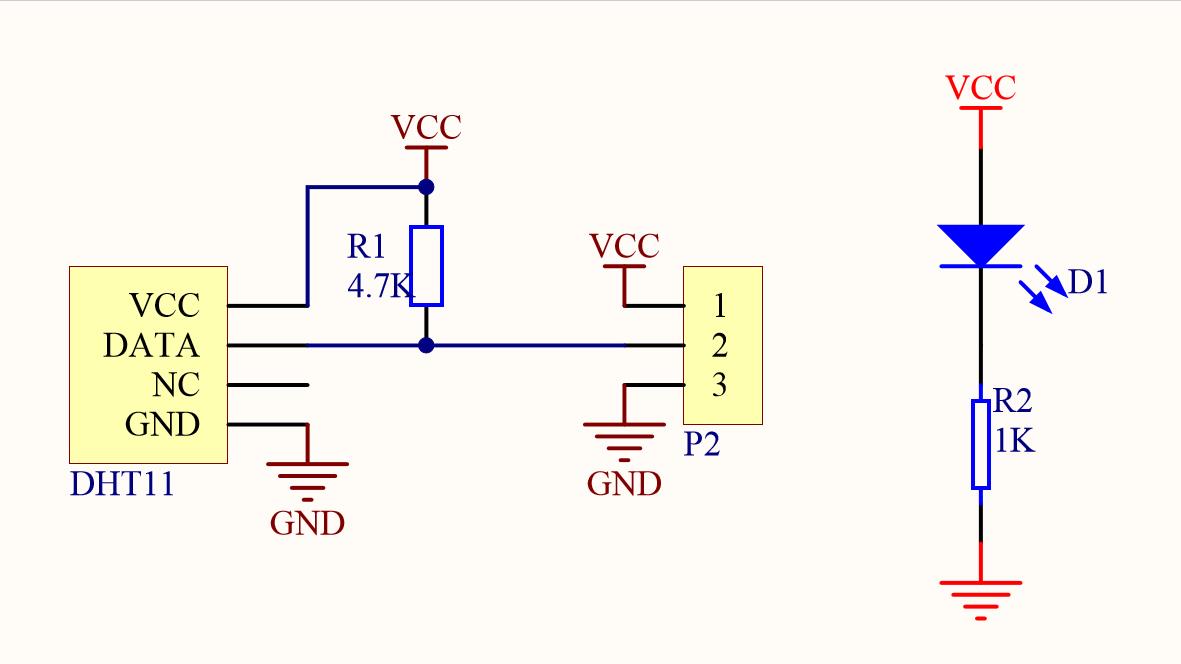

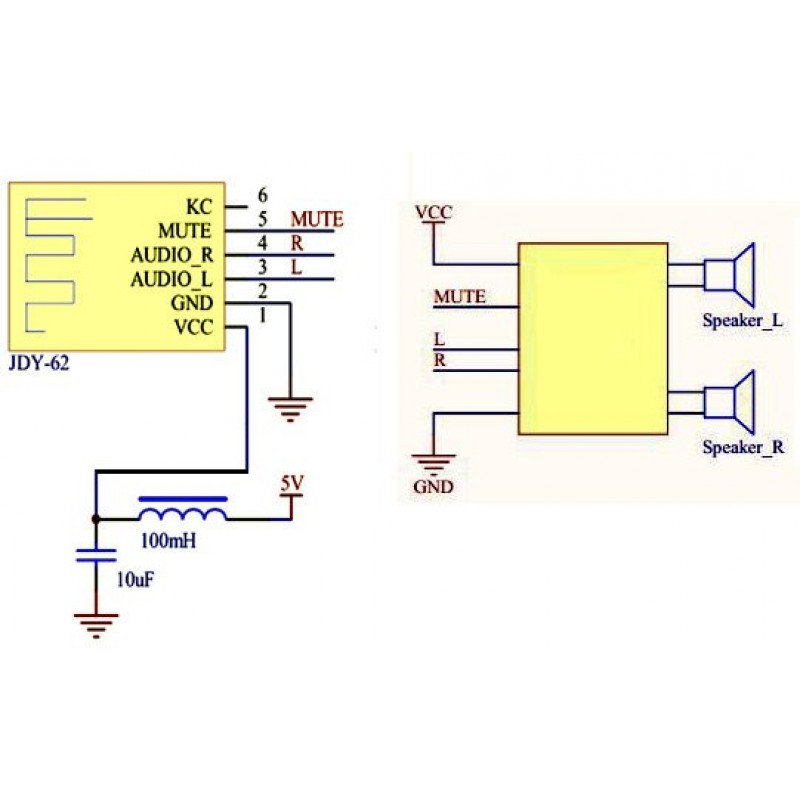

Типовая схема применения одна из инфракрасных передающих и приемных цепей

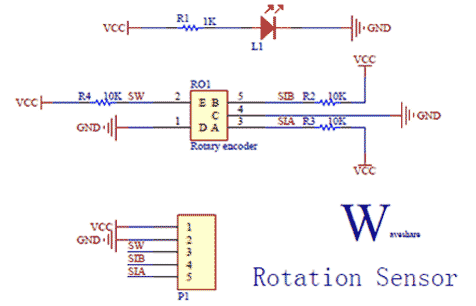

Типовая схема применения инфракрасной приемно-передающей цепи первая: схема компаратора напряжения

Я купил сенсорный модуль на определенном сокровище, и принята схема модуляции постоянного тока, то есть он питается от постоянного тока.С точки зрения цены, это можно использовать только для простой отладки.

Передающая цепь: источник питания VCC через ограничивающее сопротивление сопротивление для питания пусковой трубы, токоограничивающее сопротивление определяет величину тока источника питания, в соответствии со спецификацией пусковой трубы, чем больше ток, тем сильнее пусковая мощность.

Приемная цепь: источник питания VCC через токоограничивающий резистор для питания приемной трубки, эта схема может регулировать чувствительность приема.

Компаратор напряжения: Опорное напряжение определяется делением напряжения скользящего реостата, а расстояние обнаружения может быть установлено.

анализ схем:

Когда нет элемента, приемная трубка не может принимать отраженный инфракрасный свет и не проводит ток. Напряжение на плюсовом полюсе LM393 равно VCC, которое может быть ниже, чем VCC, потому что даже если нет отраженного света, инфракрасный свет слабый по своей природе. Имеется темновой ток, примерно на уровне мкА, обратитесь к спецификации и сравните с + и-полюсным напряжением LM393;

Когда есть предмет, приемная трубка принимает инфракрасные лучи и включается. Напряжение + полюса LM393 будет изменяться в зависимости от силы отраженного света. Чем сильнее отраженный свет, тем ниже напряжение и чем слабее отраженный свет, тем выше напряжение.

1. Проверьте купленную плату.

1. Когда нет препятствий, положительный полюс LM393 – это VCC, отрицательное напряжение полюса LM393 – Vref, а Vref ниже, чем VCC, LM393 выводит высокий уровень VCC, индикатор переключателя не горит; если есть препятствие, положительное напряжение LM393 является инфракрасным После включения приемной трубки импеданс делится на 10 кОм, отрицательное напряжение Vref LM393, Vref выше, чем VCC, выходной уровень LM393 равен 0, и индикатор переключателя горит.

2. Регулируя скользящий реостат, расстояние можно регулировать. Регулировка размера скользящего реостата реализует регулировку размера Vref.Чем больше напряжение Vref, тем больше расстояние обнаружения и, наоборот, тем ближе.

3. Токоограничивающее сопротивление инфракрасной приемной трубки очень важно, это сопротивление зависит от расстояния обнаружения и чувствительности.

2. Проблемы, возникшие при отладке:

1. Во время отладки я использовал приобретенные мной передающую и приемную трубку инфракрасного излучения и обнаружил, что заменил свои собственные передающие и приемные трубки. По сравнению с первоначально купленной платой, я обнаружил, что расстояние обнаружения было меньше.

Причина: исходная конструкция подтягивающего резистора инфракрасного приемника составляла 10 кОм, а внутреннее сопротивление приемной трубки было измерено как 20 кОм; импеданс приемной трубки, который я купил, составлял 50 кОм. Я изменил 10 кОм на 20 кОм, и расстояние обнаружения увеличилось с 25 см до 35 см. В реальных измерениях обнаружено, что увеличение мощности цепи приведет к аномальной чувствительности и ложным срабатываниям.

2. Обратите внимание, что сам LM393 также имеет разность напряжений.Например, положительное напряжение LM393 должно быть больше, чем отрицательное напряжение LM393 ± 0,3 В, прежде чем выход переключается.

Таким образом, конструкция этой схемы требует внимания к величине передаваемого тока, чувствительности приемной трубки и внутренним ошибкам компаратора напряжения LM393. Он подходит только для использования в помещении без солнечного света.

Что означают Vdd и Vss? Vcc и Ви ?? GND?

Всегда было немного интригующе и даже сбивало с толку номенклатура этих напряжений питания ( Vdd и Vss ) или ( Vcc и Vee ).

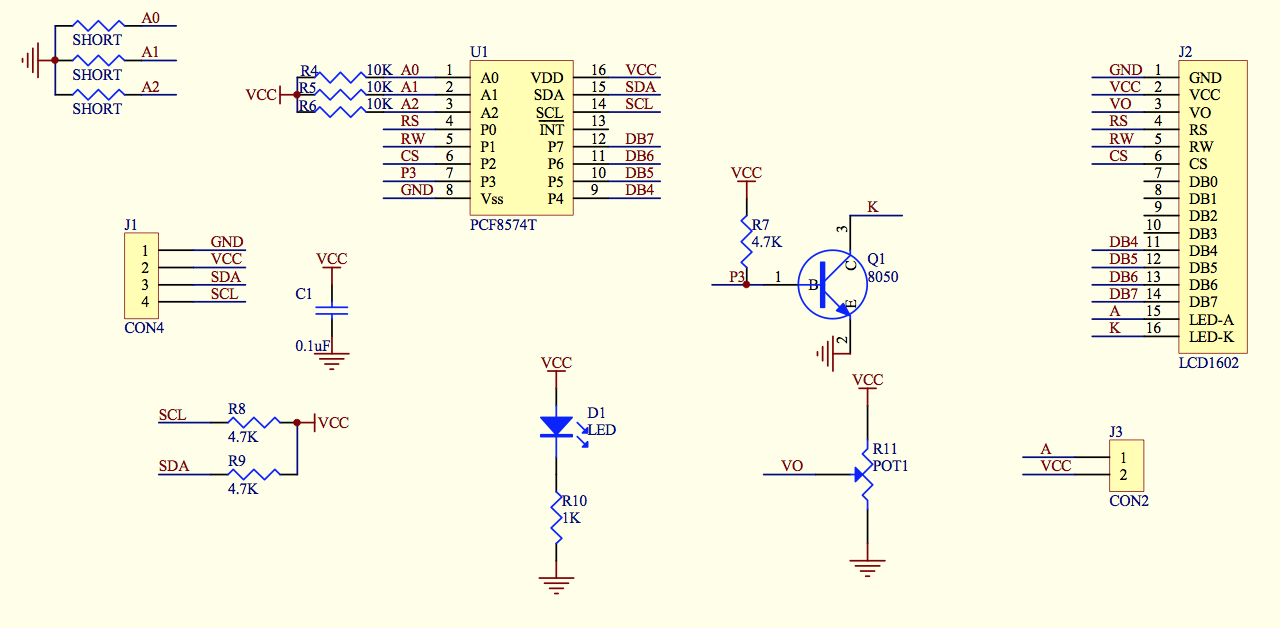

VDD, VSS, Vcc и Vee в CadenceschematicСледующие изображения стоят тысячи слов…

В настоящее время всегда используется Vdd и Vss для обозначения положительного и отрицательного напряжения соответственно. Vdd обычно составлял 5 В, но в настоящее время составляет 3,3 В или даже ниже 1,8 В или 1,2 В. Vss считается нулевым вольт.

Но Меня учили , в старшей школе и в первые годы обучения электронике, что Vcc – это положительное напряжение (обычно 5 вольт), но когда мы добираемся до некоторых схем, мы находим контакты Vdd, Vss и Vdd. Возможно, многих это не заинтриговало, но если вы это читаете, возможно, да. Итак, продолжим:

Что такое номенклатура?Это зависит от типа транзисторов , которые электронное устройство имеет внутри микрочипа, схемы или микроконтроллера.

Если внутренне сформировано биполярных транзисторов (BJT) , то номенклатура будет:

– Vcc для напряжения, приложенного к коллектору транзисторов

– Vee для напряжения, приложенного к транзистор Эмиттер ножка

Если внутри построен полевыми транзисторами (FET, MOSFET ), номенклатура будет:

– Vss для напряжения, приложенного к транзистору Source pin

– Vdd для напряжения, приложенного к стоку транзисторов

Итак, какова полярность каждого из них?

Поскольку в качестве эталона используются транзисторы NPN и NMOS:

Vcc и Vdd – положительные напряжения питания

Vee и Vss – отрицательные напряжения питания или подключены к земле.

Надеюсь, это будет вам полезно!

Типовая маркировка контактов источника питания | MADPCB

В схемах и анализе цепей существуют давние соглашения относительно обозначения напряжений, токов и некоторых компонентов. При анализе биполярного переходного транзистора, например, в конфигурации с общим эмиттером, постоянное напряжение на коллекторе, эмиттере и базе (относительно земли) может быть записано как В C , В E и V B соответственно.Резисторы, связанные с этими выводами транзистора, могут быть обозначены R C , R E и R B . Для создания постоянного напряжения самое дальнее напряжение, помимо этих резисторов или других компонентов, если они присутствуют, часто обозначается как В, CC , В, EE и В, BB . На практике VCC и VEE тогда относятся к положительным и отрицательным линиям питания, соответственно, в общих цепях NPN.Обратите внимание, что VCC будет отрицательным, а VEE будет положительным в эквивалентных схемах PNP.

Точно аналогичные условные обозначения были применены к полевым транзисторам с их выводами стока, истока и затвора. Это привело к созданию V D и V S за счет напряжения питания, обозначенного V DD и V SS в более распространенных схемах. Аналогично разнице между биполярами NPN и PNP, VDD является положительным по отношению к VSS в случае полевых транзисторов с n-каналом и полевыми МОП-транзисторами и отрицательным для схем, основанных на полевых транзисторах с каналом p-типа и полевых МОП-транзисторах.

Несмотря на то, что эти обозначения источников питания для конкретных устройств все еще используются относительно часто, в схемах, в которых используется смесь биполярных и полевых элементов, или в схемах, в которых используются как NPN-, так и PNP-транзисторы, или оба n- и p-типа. -канальные полевые транзисторы. Этот последний случай очень распространен в современных микросхемах, которые часто основаны на технологии CMOS, где C означает дополнительный, что означает, что комплементарные пары n- и p-канальных устройств распространены повсюду.

Эти соглашения об именах были частью более широкой картины, где, чтобы продолжить примеры биполярных транзисторов, хотя полевой транзистор остается полностью аналогичным, можно записать постоянный ток или токи смещения на каждой клемме или на выходе из нее I C , I E и I B .Помимо условий постоянного тока или смещения, многие транзисторные схемы также обрабатывают меньший аудио-, видео- или радиочастотный сигнал, который накладывается на смещение на выводах. Буквы и нижние индексы в нижнем регистре используются для обозначения этих уровней сигналов на клеммах, либо размахов, либо среднеквадратичных значений, в зависимости от требований. Итак, мы видим v c , v e и v b , а также i c , i e и i b .транзистор слабого сигнала, от которого происходит название транзистор путем сжатия. В этом соглашении v i и v o обычно относятся к внешним входным и выходным напряжениям схемы или каскада.

Подобные соглашения были применены к схемам, включающим вакуумные лампы или термоэмиссионные клапаны, поскольку они были известны за пределами США. Таким образом, мы видим V P , V K и V G со ссылкой для пластины (или анода за пределами U.S.), катодное (примечание K , а не C ) и сеточные напряжения при анализе цепей вакуумных триодов, тетродов и пентодов.

Разница между VCC, VDD, VEE и VSS

При проектировании схем и производстве печатных плат часто встречаются символы питания: VCC, VDD, VEE, VSS, какие отношения у них есть?

Сначала объясните

Vcc: c = circuit обозначает значение схемы, то есть напряжение цепи доступа

Vdd: d = device указывает значение устройства, то есть рабочее напряжение внутри устройства;

Vss: s = series указывает на значение общего подключения, обычно обозначаемое как напряжение на клемме общего заземления цепи

Секунда.описание

1, для цифровой схемы VCC – это напряжение питания схемы, VDD – рабочее напряжение микросхемы (обычно VCC> VDD), VSS – это место срабатывания.

2. Некоторые ICS имеют как вывод VDD, так и вывод VCC, что указывает на то, что само устройство имеет функцию преобразования напряжения.

3. В эффекторе присутствия (или устройстве COM) VDD – сток, VSS – исток, а Vdd и VSS относятся к выводу компонента, а не к напряжению питания.Сеть связи DSP DSP Learning First Forum Применение и продвижение технологии DSP Платформа услуг по разработке DSP

4, обычно vcc = аналоговый источник питания, vdd = цифровой источник питания, vss = цифровая земля, vee = отрицательный источник питания

Другое объяснение:

VCC и VDD – это сторона питания устройства. VCC – это плюс биполярного устройства, а VDD – в основном одноступенчатое устройство. Под нижним индексом можно понимать коллектор C NPN-транзистора и электрод стока d PMO или полевой трубки с нмос.Также вы можете видеть Vee и VSS на принципиальной схеме, что означает одно и то же. Поскольку основной структурой микросхем является кремниевый NPN, VCC обычно положительный. Если вы используете структуру PNP, VCC отрицательный. Выбирая микросхему, необходимо видеть электрические параметры.

VCC выводится из напряжения питания коллектора, напряжения коллектора, обычно используемого для биполярных транзисторов, трубка PNP представляет собой отрицательное напряжение питания, иногда обозначается как VCC, трубка NPN представляет собой положительное напряжение. Сеть связи DSP DSP Learning First Forum Применение и продвижение технологии DSP Платформа услуг по разработке DSP

VDD выводится из напряжения питания стока, напряжения стока, для схем МОП-транзисторов и обычно является правильным для источников питания.Поскольку транзисторы PMOS редко используются по отдельности, VDD часто подключается к истоку лампы PMOS в схеме

CMOS.Напряжение источника питания VSS, отрицательный источник питания в цепи CMOS, в одном источнике относится к 0 вольт или заземлению.

Напряжение питания эмиттераVee, напряжение эмиттера, обычно используется для отрицательных напряжений питания схем ECL.

VBB Базовое напряжение питания цепи общей базы биполярных транзисторов. Сеть связи DSP DSP Learning First Forum Применение и продвижение технологии DSP Платформа услуг по разработке DSP

Описание схемы: DSP Сеть связи DSP Learning First Forum Применение и продвижение технологии DSP Платформа DSP Development Service Platform

Единое решение:

VDD: напряжение питания (униполярное устройство), напряжение питания (цифровая цепь серии 4000), напряжение стока (полевая трубка)

VCC: напряжение питания (биполярное устройство), напряжение питания (цифровая цепь серии 74), несущая голоса (несущая с голосовым управлением)

VSS :: Земля или минус питания

VEE: Источник отрицательного напряжения, источник полевой трубки (S)

VPP: Программирование / стирание напряжения.

Детальный

В электронной схеме VCC – это напряжение питания схемы, а VDD – рабочее напряжение микросхемы:

Vcc: c = схема представляет значение схемы, то есть напряжение цепи доступа, d = устройство означает устройство, то есть рабочее напряжение внутри устройства в обычной электронной схеме, обычно VCC> VDD !

Vss: s = series указывает значение публичного подключения, то есть отрицательное.

Некоторые ИС имеют VCC и VDD одновременно, а устройство имеет функцию преобразования напряжения.

В «эффекте поля» – это элемент COM, VDD – это вывод стока CMOS, VSS – вывод источника CMOS, который является символом вывода компонента, у него нет имени «VCC», ваша проблема содержит 3 символа, Vcc / vdd / vss, что явно является символом цепи.

993554.indd

% PDF-1.4 % 135 0 объект > эндобдж 122 0 объект > эндобдж 134 0 объект > поток PScript5.dll Версия 5.2.22008-05-28T13: 01: 11-05: 002008-05-28T13: 01: 11-05: 00application / pdf

Шум на Vcc для последовательной передачи данных | 2014-06-10

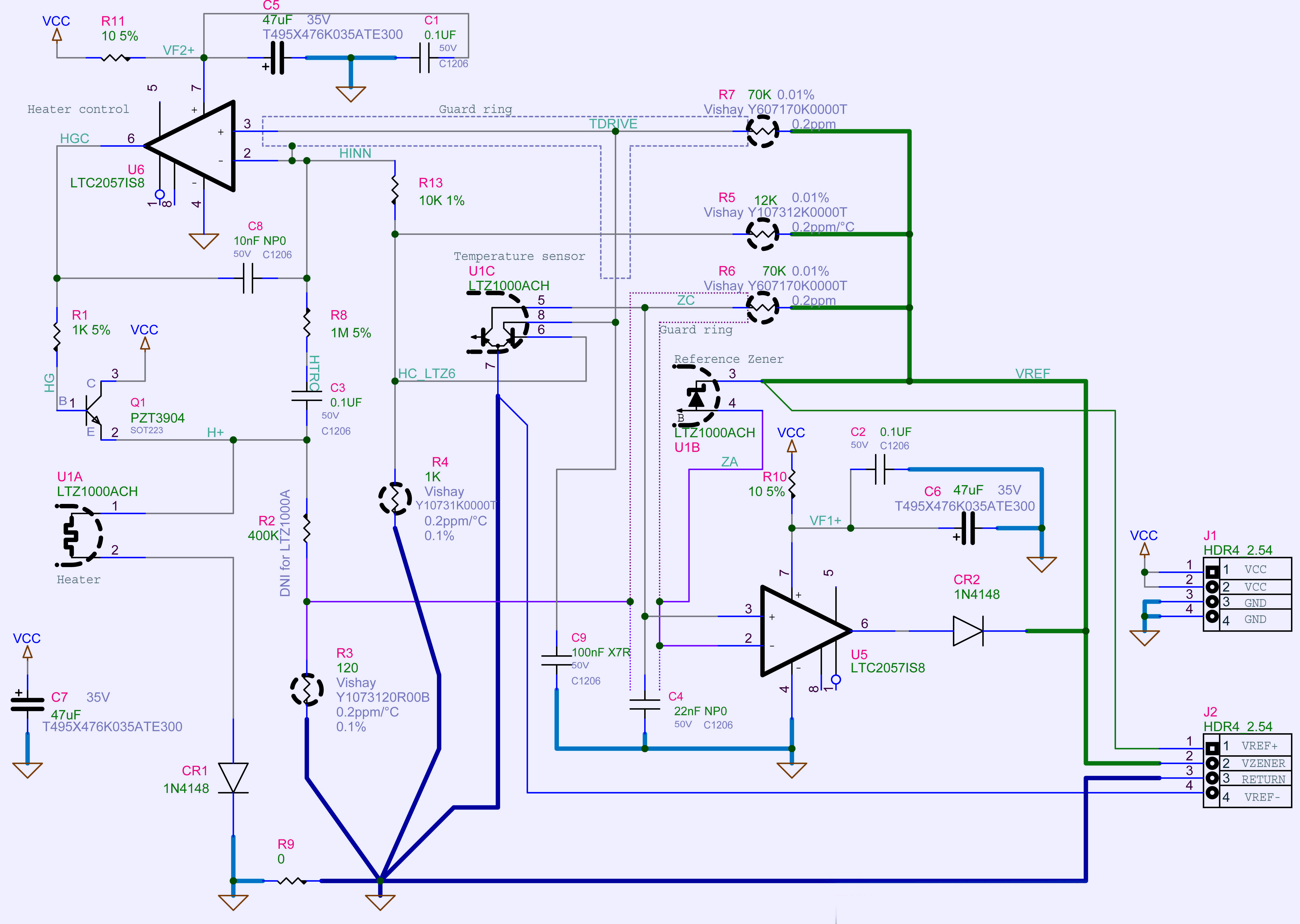

Рисунок 1 Блок-схема JV9000.

Спецификация напряжения питания (Vcc) является ключевым параметром почти для всех спецификаций интегральных схем (IC). Если его требования не выполнены, невозможно узнать, будут ли действительны остальные спецификации IC.Поэтому перед определением рабочего диапазона напряжения питания устройства разработчики, специалисты по верификации и качеству используют результаты обширных испытаний, чтобы убедиться, что ИС соответствует всем требованиям спецификации в пределах испытанного диапазона напряжения Vcc. За исключением спецификации коэффициента отклонения источника питания (PSRR) некоторых аналоговых и радиочастотных ИС, часто не указывается или игнорируется невосприимчивость ИС к шумам и импульсам, возникающим из-за напряжения питания.

Проверочные испытания конструкции ИС обычно проводятся с использованием чистых лабораторных источников питания и хорошо экранированных кабелей питания для обеспечения базовой производительности в идеальных условиях.Тем не менее, эти условия почти никогда не являются рабочими условиями и средой IC в реальных схемах и приложениях. В результате почти все производители ИС предоставляют эталонные конструкции и методы компоновки плат, чтобы минимизировать шум на Vcc. В конце концов, ответственность за обеспечение чистого Vcc для IC возлагается на разработчика платы, чье конкретное приложение и операционная среда могут потребовать принятия дополнительных мер предосторожности, помимо рекомендаций по дизайну из таблицы данных и рекомендаций по схемам приложений.Если производитель ИС не предоставит конкретную информацию о помехозащищенности устройства, разработчик платы может быть вынужден переконструировать вспомогательную схему, что не всегда возможно с учетом ограничений по месту и стоимости. Дизайнеру, возможно, придется сделать обоснованные предположения или он будет вынужден спланировать дополнительное вращение доски, чтобы убедиться, что нет проблем с иммунитетом. Дополнительная работа неизбежно может задержать выпуск продукта и увеличить стоимость разработки.

Хотя концепция шума на Vcc не является чем-то новым, достижения в технологии кристаллов ИС за последнее десятилетие поставили новые задачи.В основном за счет усадки матрицы были достигнуты более высокие уровни интеграции и более низкие напряжения питания, что привело к повышению надежности, стоимости и производительности, таким как уменьшение количества деталей, повышение энергоэффективности и тепловых характеристик. Между тем, разработчик уровня платы IC столкнулся с новыми проблемами проектирования, связанными с более низким напряжением питания и ввода-вывода. То, что когда-то было незначительным шумом на Vcc цепи 3,3 или 5 В, больше нельзя игнорировать на микросхеме 1,2 В из-за более низкого запаса шума.Кроме того, интеграция цифровых, аналоговых и радиочастотных функций на одной ИС, работающей на все более высоких скоростях передачи данных, может генерировать более высокий внутренний шум, делая низковольтное и высокоскоростное устройство более восприимчивым к дополнительному внешнему шуму и пульсации на Vcc.

Рисунок 2 Схема испытательной установки.

Шум от Vcc влияет на широкий спектр приложений и схем. В приемопередатчиках чувствительность приемника и характеристики побочного излучения передатчика могут ухудшаться из-за шума на Vcc аналого-цифрового преобразователя (АЦП) и цифро-аналогового преобразователя (ЦАП).Точно так же для схем тактирования и гетеродина (LO) с PLL / VCO и PLL / VCXO / XO, используемых в конструкциях приемопередатчиков, шум на Vcc может генерировать джиттер тактового сигнала и фазовый шум гетеродина, влияя на паразитные излучения и чувствительность приемника. В схемах высокоскоростной последовательной передачи данных джиттер тактового сигнала, вызванный шумом и паразитами на Vcc схемы PLL / XO, может вызвать дрожание данных, потенциально снижающее производительность BER.

Рис. 3 «Чистый» канал без ошибок BER = 0 (J7000 и JV9000 оба выключены, шум отсутствует).

В этом примечании к применению мы рассмотрим ИС высокоскоростного буфера данных / тактовой частоты, DUT и влияние шума на его Vcc на общую производительность системы. При характеристике производительности системы тестирование BER используется для измерения производительности системы и дополняется глазковыми диаграммами в качестве визуального инструмента. Инъекция аддитивного белого гауссовского шума (AWGN) и непрерывных тонов в тракт Vcc тестируемого устройства выполняется с помощью устройства Noisecom JV9000. Устройство принимает чистое напряжение источника питания и подает тоны CW и / или сигнал AWGN контролируемым образом с 0.Точность 1 дБ (см. Рисунок 1 ).

Мы также используем генератор джиттера для снижения производительности канала BER. Устройство вводит шум AWGN в последовательные данные, который, в свою очередь, вызывает случайное дрожание Rj. Джиттер создается во время переходов от 0 к 1 или от 1 к 0, когда шум, добавленный к сигналу в течение этого переходного периода, заставляет приемник неправильно интерпретировать синхронизацию перехода. Результирующая неопределенность синхронизации называется джиттером, а в случае AWGN она случайна.Высокий выходной пик-фактор устройства позволяет генерировать реалистичные пики, что делает его идеальным для тестирования BERT и может использоваться в качестве источника случайного джиттера для различных приложений последовательной шины данных, включая PCI Express Gen I и II, Serial ATA, Fibre Channel, 10. , 40 и 100 ГБ Ethernet (802.3).

В испытательной установке генератор шаблонов BERT используется в качестве высокоскоростного дифференциального последовательного источника данных, а выход BERT подключен к J7000. Обратите внимание, что J7000 работает в режиме байпаса (без добавления шума) в начальной части теста.Он включен на втором этапе нашего теста, чтобы снизить производительность последовательного канала из-за внесения случайного джиттера. Выход J7000 питает DUT, выход DUT затем управляет входом детектора BERT, возвращая сигнал обратно в приемник BERT. Vcc тестируемого устройства поступает от JV9000, также изначально сконфигурированного с отключенными всеми его шумовыми и паразитными сигналами, обеспечивая чистое напряжение питания на плате eval для базового тестирования. Блок-схема установки показана на Рис. 2 .

Рисунок 4 Зависимость BER от частоты CW (паразита).

Чтобы имитировать, как разработчик ИС или инженер по верификации будет проверять невосприимчивость ИС к шумам и выбросам напряжения постоянного тока, байпасные конденсаторы платы оценки ИУ были удалены; позволяя тестеру увидеть, какие частоты на Vcc имеют наибольшее влияние на производительность системы. Перед представлением процедуры и результатов тестирования важно отметить, что для проверки фактических характеристик ИС разработчик или инженер-испытатель, вероятно, будет использовать специальное приспособление, свободное от паразитных эффектов оценочной платы, чтобы измерить исходную производительность платы. IC.В этой настройке теста весьма вероятно, что паразитные эффекты платы eval играют роль в результате. Фактически, испытательная установка может быть ближе к тому, как разработчик печатной платы будет проверять помехозащищенность схемы при конкретной компоновке платы и ее паразитных характеристиках.

Рисунок 5 BER = 1 E-07 (J7000 вводит шум AWGN –10 дБм, JV9000 выключен).

Процедура тестирования

- Источники шума и паразитных помех JV9000 и J7000 отключены, чтобы установить базовую производительность с BER = 0 (см. Рисунок 3 ). Тракт

- JV9000 AWGN включен, и уровень инжектируемого шума медленно увеличивается по мере отслеживания BER. Источник шума

- JV9000 AWGN отключается, и непрерывные тоны 10 кГц, 100 кГц, 1 МГц, 10 МГц и 100 МГц вводятся по одному, чтобы увидеть, как изменяется BER на каждой частоте. Обратите внимание, что связь CW от Vcc к выходам данных вызовет детерминированный джиттер, Dj.

- И, наконец, шаг 3 повторяется с включенным шумом AWGN, чтобы увидеть комбинированный эффект, который оказывают споры AWGN и CW на производительность BER.

- Затем мы отключаем весь широкополосный шум и сигналы CW на JV9000 и снижаем BER канала до 1E-07, вводя AWGN в линии данных с помощью генератора джиттера J7000 и создавая случайный джиттер Rj. Те же тесты, которые выполняются на этапах 2, 3 и 4, повторяются на канале 1 E-7 BER, чтобы увидеть комбинированное воздействие шума AWGN и паразитных импульсов на Vcc на уже ухудшенный канал.

Результаты тестов можно суммировать, отметив, что, когда начальный BER канала равен 0, а шум AWGN и тоны CW, введенные в Vcc, находятся на максимальных стандартных уровнях (тоны 0 дБм на упомянутых частотах и 0 дБм в целом по AWGN. мощность от 500 Гц до 2 ГГц) мы не могли внести каких-либо значительных битовых ошибок, хотя добавленный шум можно было легко увидеть на глазковой диаграмме.Таким образом, есть свидетельства существования утечки шума от вывода Vcc к выводам вывода данных, но это не влияет на производительность BER. Однако, когда BER снижается до 1 E-07 путем введения шума AWGN в линии данных, создавая случайное дрожание, добавленный шум и паразиты действительно играют очень важную роль, где BER теперь снижается с 1 E-07 до 7. E-05, когда вводится тональный сигнал CW 1 МГц. Также стоит отметить, что импульсные источники питания обычно переключаются на частотах от 100 кГц до нескольких МГц, поэтому помехозащищенность микросхемы Vcc на этих низких частотах важна в большинстве конструкций.

Результаты тестирования представлены в табличном формате в Таблица 1 , где базовый уровень BER канала равен 1 E-07. Для графического представления того, как тестируемое устройство реагировало на различные вводимые частоты на его Vcc, см. Рисунок 4 .

Введение широкополосного шума (AWGN) от 500 Гц до 2 ГГц в Vcc ИС (DUT) увеличивает BER системы чуть более чем в два раза. Однако, когда вводимая мощность сконцентрирована на одной частоте (CW), влияние намного сильнее.По мере того, как частота вводимого тона постоянной мощности на вывод Vcc IC изменяется, влияние на приемник также меняется. Мы видим резонанс BER около 1 МГц, где BER ухудшается больше всего, когда вводится тон CW на 1 МГц.

Рисунок 6 BER = 9 E-05 (J7000 вводит шум AWGN, JV9000 вводит шум AWGN и 1 МГц CW).

На рисунках 3, 5 и 6 показаны глазковые диаграммы для различных условий испытаний. На рисунке 3 показана глазковая диаграмма, когда BER = 0 и все источники шума выключены. Рисунок 5 показывает глазковую диаграмму BER = 1 E-07, когда только J7000 вносит шум (источники шума JV9000 выключены). На рисунке 6 показана глазковая диаграмма для принятого сигнала при наихудшем случае паразитных выбросов и шумов (1 МГц CW + AWGN), когда базовые характеристики канала BER равны 1E-07.

Заключение

Поскольку уровни Vcc и логические уровни IC падают, а интеграция нескольких функций в среде со смешанными сигналами генерирует больше шума внутри IC, необходимо проверить влияние шума и паразитных импульсов на Vcc на работу IC становится все более важным.Цель этой заметки по применению – показать, как инженеры по проверке рабочих характеристик ИС и разработчики схем могут охарактеризовать работу ИС или схемы при наличии шума и выбросов на Vcc. Результаты тестов показывают, что ИС может быть более чувствительной к шумам и помехам, возникающим на ее Vcc на определенных частотах. Кроме того, сочетание джиттера данных и шума Vcc может повлиять на характеристики приемника совсем иначе, чем можно предположить из отдельных независимых тестов. Если пойти дальше, то тестирование, выполняемое в соответствии с этим указанием по применению, также необходимо, когда разработчику ИС, инженеру по применению или разработчику схем необходимо решить, какая фильтрация требуется на Vcc для оптимальной работы ИС.

Для проведения этих испытаний принято множество самодельных решений. Когда необходимо построить несколько испытательных станций или команды разработчиков в разных географических регионах должны работать вместе, интегрированная система тестирования позволяет инженерам по тестированию и верификации выполнять свои испытания с повторяемостью и под контролем. Также имеется экономия, связанная с программированием, размером рабочего стола, настройкой и проверкой системы.

Шум Noisecom на Vcc для последовательной передачи данных

Опубликовано: 10 июня, 2014

Виталий Пенсо, Noisecom, компания группы беспроводной связи, Парсиппани, штат Нью-Джерси,

| Рисунок 1 Блок-схема JV9000. |

Спецификация напряжения питания (Vcc) является ключевым параметром почти для всех таблиц данных интегральных схем (IC). Если его требования не выполнены, невозможно узнать, будут ли действительны остальные спецификации IC. Поэтому перед определением рабочего диапазона напряжения питания устройства разработчики, специалисты по верификации и качеству используют результаты обширных испытаний, чтобы убедиться, что ИС соответствует всем требованиям спецификации в пределах испытанного диапазона напряжения Vcc.За исключением спецификации коэффициента отклонения источника питания (PSRR) некоторых аналоговых и радиочастотных ИС, часто не указывается или игнорируется невосприимчивость ИС к шумам и импульсам, возникающим из-за напряжения питания.

Проверочные испытания конструкции ИС обычно проводятся с использованием чистых лабораторных источников питания и хорошо экранированных кабелей питания для обеспечения базовой производительности в идеальных условиях. Тем не менее, эти условия почти никогда не являются рабочими условиями и средой IC в реальных схемах и приложениях.В результате почти все производители ИС предоставляют эталонные конструкции и методы компоновки плат, чтобы минимизировать шум на Vcc. В конце концов, ответственность за обеспечение чистого Vcc для IC возлагается на разработчика платы, чье конкретное приложение и операционная среда могут потребовать принятия дополнительных мер предосторожности, помимо рекомендаций по дизайну из таблицы данных и рекомендаций по схемам приложений. Если производитель ИС не предоставит конкретную информацию о помехозащищенности устройства, разработчик платы может быть вынужден переконструировать вспомогательную схему, что не всегда возможно с учетом ограничений по месту и стоимости.Дизайнеру, возможно, придется сделать обоснованные предположения или он будет вынужден спланировать дополнительное вращение доски, чтобы убедиться, что нет проблем с иммунитетом. Дополнительная работа неизбежно может задержать выпуск продукта и увеличить стоимость разработки.

Хотя концепция шума на Vcc не является чем-то новым, достижения в технологии кристаллов ИС за последнее десятилетие поставили новые задачи. В основном за счет усадки матрицы были достигнуты более высокие уровни интеграции и более низкие напряжения питания, что привело к повышению надежности, стоимости и производительности, таким как уменьшение количества деталей, повышение энергоэффективности и тепловых характеристик.Между тем, разработчик уровня платы IC столкнулся с новыми проблемами проектирования, связанными с более низким напряжением питания и ввода-вывода. То, что когда-то было незначительным шумом на Vcc цепи 3,3 или 5 В, больше нельзя игнорировать на микросхеме 1,2 В из-за более низкого запаса шума. Кроме того, интеграция цифровых, аналоговых и радиочастотных функций на одной ИС, работающей на все более высоких скоростях передачи данных, может генерировать более высокий внутренний шум, делая низковольтное и высокоскоростное устройство более восприимчивым к дополнительному внешнему шуму и пульсации на Vcc.

Рисунок 2 Схема испытательной установки.

Шум от Vcc влияет на широкий спектр приложений и схем. В приемопередатчиках чувствительность приемника и характеристики побочного излучения передатчика могут ухудшаться из-за шума на Vcc аналого-цифрового преобразователя (АЦП) и цифро-аналогового преобразователя (ЦАП). Точно так же для схем тактирования и гетеродина (LO) с PLL / VCO и PLL / VCXO / XO, используемых в конструкциях приемопередатчиков, шум на Vcc может генерировать джиттер тактового сигнала и фазовый шум гетеродина, влияя на паразитные излучения и чувствительность приемника.В схемах высокоскоростной последовательной передачи данных джиттер тактового сигнала, вызванный шумом и паразитами на Vcc схемы PLL / XO, может вызвать дрожание данных, потенциально снижающее производительность BER.

| Рис. 3 «Чистый» канал без ошибок BER = 0 (J7000 и JV9000 оба выключены, шум отсутствует). |

В этом примечании к применению мы рассмотрим высокоскоростную ИС буфера данных / тактовой частоты, DUT и влияние шума на его Vcc на общую производительность системы.При характеристике производительности системы тестирование BER используется для измерения производительности системы и дополняется глазковыми диаграммами в качестве визуального инструмента. Инъекция аддитивного белого гауссовского шума (AWGN) и непрерывных тонов в тракт Vcc тестируемого устройства выполняется с помощью устройства Noisecom JV9000. Устройство принимает чистое напряжение источника питания и подает тоны CW и / или сигнал AWGN контролируемым образом с точностью до 0,1 дБ (см. Рисунок 1 ).

Мы также используем генератор джиттера для снижения производительности канала BER.Устройство вводит шум AWGN в последовательные данные, который, в свою очередь, вызывает случайное дрожание Rj. Джиттер создается во время переходов от 0 к 1 или от 1 к 0, когда шум, добавленный к сигналу в течение этого переходного периода, заставляет приемник неправильно интерпретировать синхронизацию перехода. Результирующая неопределенность синхронизации называется джиттером, а в случае AWGN она случайна. Высокий выходной пик-фактор устройства позволяет генерировать реалистичные пики, что делает его идеальным для тестирования BERT и может использоваться в качестве источника случайного джиттера для различных приложений последовательной шины данных, включая PCI Express Gen I и II, Serial ATA, Fibre Channel, 10. , 40 и 100 ГБ Ethernet (802.3).

В испытательной установке генератор шаблонов BERT используется в качестве высокоскоростного дифференциального последовательного источника данных, а выход BERT подключен к J7000. Обратите внимание, что J7000 работает в режиме байпаса (без добавления шума) в начальной части теста. Он включен на втором этапе нашего теста, чтобы снизить производительность последовательного канала из-за внесения случайного джиттера. Выход J7000 питает DUT, выход DUT затем управляет входом детектора BERT, возвращая сигнал обратно в приемник BERT.Vcc тестируемого устройства поступает от JV9000, также изначально сконфигурированного с отключенными всеми его шумовыми и паразитными сигналами, обеспечивая чистое напряжение питания на плате eval для базового тестирования. Блок-схема установки показана на Рис. 2 .

| Рисунок 4 BER в зависимости от частоты CW (паразита). |

Чтобы имитировать, как разработчик ИС или инженер по верификации будет проверять невосприимчивость ИС к шуму и выбросам напряжения постоянного тока, байпасные конденсаторы платы оценки DUT были удалены; позволяя тестеру увидеть, какие частоты на Vcc имеют наибольшее влияние на производительность системы.Перед представлением процедуры и результатов тестирования важно отметить, что для проверки фактических характеристик ИС разработчик или инженер-испытатель, вероятно, будет использовать специальное приспособление, свободное от паразитных эффектов оценочной платы, чтобы измерить исходную производительность платы. IC. В этой настройке теста весьма вероятно, что паразитные эффекты платы eval играют роль в результате. Фактически, испытательная установка может быть ближе к тому, как разработчик печатной платы будет проверять помехозащищенность схемы при конкретной компоновке платы и ее паразитных характеристиках.

| Рис. 5 BER = 1 E-07 (J7000 вводит шум AWGN –10 дБм, JV9000 выключен). |

Процедура испытания

- Источники шума и паразитов JV9000 и J7000 отключены, чтобы установить базовые характеристики с BER = 0 (см. Рисунок 3). Тракт

- JV9000 AWGN включен, и уровень инжектируемого шума медленно увеличивается по мере отслеживания BER. Источник шума

- JV9000 AWGN отключается, и непрерывные тоны 10 кГц, 100 кГц, 1 МГц, 10 МГц и 100 МГц вводятся по одному, чтобы увидеть, как изменяется BER на каждой частоте. Обратите внимание, что связь CW от Vcc к выходам данных вызовет детерминированный джиттер, Dj.

- И, наконец, шаг 3 повторяется с включенным шумом AWGN, чтобы увидеть комбинированный эффект, который оказывают споры AWGN и CW на производительность BER.

- Затем мы отключаем весь широкополосный шум и сигналы CW на JV9000 и снижаем BER канала до 1E-07, вводя AWGN в линии данных с помощью генератора джиттера J7000 и создавая случайный джиттер Rj.Те же тесты, которые выполняются на этапах 2, 3 и 4, повторяются на канале 1 E-7 BER, чтобы увидеть комбинированное воздействие шума AWGN и паразитных импульсов на Vcc на уже ухудшенный канал.

Результаты тестов можно суммировать, отметив, что, когда начальный BER канала равен 0, а шум AWGN и тоны CW, введенные в Vcc, находятся на максимальных стандартных уровнях (тоны 0 дБм на упомянутых частотах и 0 дБм в целом по AWGN. мощность от 500 Гц до 2 ГГц) мы не могли внести каких-либо значительных битовых ошибок, хотя добавленный шум можно было легко увидеть на глазковой диаграмме.Таким образом, есть свидетельства существования утечки шума от вывода Vcc к выводам вывода данных, но это не влияет на производительность BER. Однако, когда BER снижается до 1 E-07 путем введения шума AWGN в линии данных, создавая случайное дрожание, добавленный шум и паразиты действительно играют очень важную роль, где BER теперь снижается с 1 E-07 до 7. E-05, когда вводится тональный сигнал CW 1 МГц. Также стоит отметить, что импульсные источники питания обычно переключаются на частотах от 100 кГц до нескольких МГц, поэтому помехозащищенность микросхемы Vcc на этих низких частотах важна в большинстве конструкций.

Результаты тестирования представлены в табличном формате в Таблица 1 , где базовый уровень BER канала равен 1 E-07. Для графического представления того, как тестируемое устройство реагировало на различные вводимые частоты на его Vcc, см. Рисунок 4 .

Введение широкополосного шума (AWGN) от 500 Гц до 2 ГГц в Vcc ИС (DUT) увеличивает BER системы чуть более чем в два раза. Однако, когда вводимая мощность сконцентрирована на одной частоте (CW), влияние намного сильнее.По мере того, как частота вводимого тона постоянной мощности на вывод Vcc IC изменяется, влияние на приемник также меняется. Мы видим резонанс BER около 1 МГц, где BER ухудшается больше всего, когда вводится тон CW на 1 МГц.

| Рисунок 6 BER = 9 E-05 (J7000 вводит шум AWGN, JV9000 вводит AWGN и 1 МГц CW). |

На рисунках 3, 5 и 6 показаны глазковые диаграммы для различных условий испытаний.На рисунке 3 показана глазковая диаграмма, когда BER = 0 и все источники шума выключены. Рисунок 5 показывает глазковую диаграмму BER = 1 E-07, когда только J7000 вносит шум (источники шума JV9000 выключены). На рисунке 6 показана глазковая диаграмма для принятого сигнала в наихудшем случае паразитных выбросов и шумов (1 МГц CW + AWGN), когда базовые характеристики канала BER равны 1E-07.

Заключение

Поскольку уровни Vcc и логические уровни IC падают, а интеграция нескольких функций в среде со смешанными сигналами генерирует больше шума внутри IC, необходимо проверить влияние шума и паразитных импульсов на Vcc на работу IC становится все более важным.Цель этой заметки по применению – показать, как инженеры по проверке рабочих характеристик ИС и разработчики схем могут охарактеризовать работу ИС или схемы при наличии шума и выбросов на Vcc. Результаты тестов показывают, что ИС может быть более чувствительной к шумам и помехам, возникающим на ее Vcc на определенных частотах. Кроме того, сочетание джиттера данных и шума Vcc может повлиять на характеристики приемника совсем иначе, чем можно предположить из отдельных независимых тестов. Если пойти дальше, то тестирование, выполняемое в соответствии с этим указанием по применению, также необходимо, когда разработчику ИС, инженеру по применению или разработчику схем необходимо решить, какая фильтрация требуется на Vcc для оптимальной работы ИС.