1.2 Микросхемы комбинационного типа малой степени интеграции.

1.2. Микросхемы комбинационного типа малой степени интеграции

Существует много типов микросхем ТТЛ малой степени интеграции, различающихся по функциональному назначению, нагрузочной способности, схеме выходного каскада. Работа логических элементов этих микросхем достаточно проста. Для элементов И выходной уровень лог. 1 формируется при подаче на все входы элемента уровней лог. 1, для элемента ИЛИ для формирования уровня лог. 1 на выходе достаточно подачи хотя бы на один вход уровня лог. 1. Элементы И-НЕ (основной элемент серий ТТЛ) и ИЛИ-НЕ дополнительно инвертируют выходной сигнал, элемент И-ИЛИ-НЕ состоит из нескольких элементов И, выходы которых подключены к входам элемента ИЛИ-НЕ.

По нагрузочной способности микросхемы можно разделить на стандартные (№10 для серий К 155 и КР531 и N = 20 и 40 для микросхем серий К555 и КР1533 соответственно), микросхемы с повышенной нагрузочной способностью (N = 30 и более), микросхемы со специальным выходным каскадом, обеспечивающим значительно более высокую нагрузочную способность в одном из логических состояний. Некоторые типы микросхем выпускают с так называемым «открытым» коллекторным выходом.

Отдельно следует отметить специальный класс микросхем с третьим состоянием выходного каскада, называемым также еще «высокоимпедансным», или «Z-состоянием», при котором микросхема отключается по своему выходу от нагрузки. Это, как правило, буферные элементы с относительно большой нагрузочной способностью.

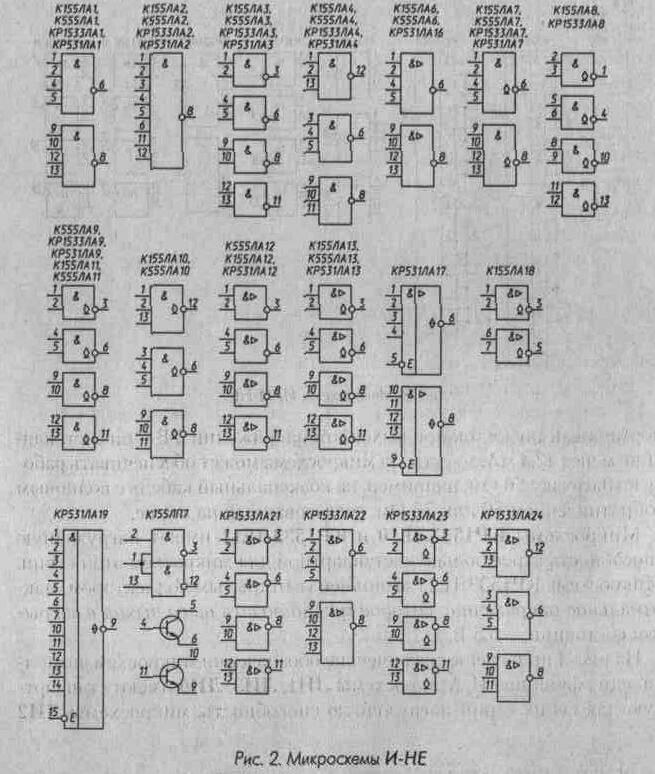

На рис. 2 приведены графические обозначения микросхем ТТЛ, выполняющих функции И-НЕ – самой многочисленной группы простых логических микросхем.

МикросхемыЛА1 -ЛА4 имеют стандартную для своей серии нагрузочную способность, микросхемыЛА6 иЛА12 всех серий, КР1533ЛА21 – КР1533ЛА24 – втрое большую (здесь и далее в тексте в названии оставлена только та его часть, которая определяет тип триггера, счетчика, логического элемента и т. п., если такие же обозначения используются в микросхемах нескольких серий).

МикросхемыЛА7 – ЛА11,ЛА13, КР1533ЛА23 выполнены с открытым коллектором, нагрузочная способность для ЛА7- ЛА11 в состоянии лог. 0 стандартная, для ЛА13 и КР1533ЛА23 – втрое большая. Максимально допустимое напряжение, которое можно подавать

на выход микросхемы ЛА11, находящейся в состоянии лог. 1, – 12 В, для остальных – 5,5 В.

МикросхемаКР531ЛА16 (рис. 2) – два мощных магистральных усилителя, выполняющих функцию 4И-НЕ. Нагрузочная способность каждого усилителя 60 мА в состоянии лог. 0 и 40 мА в состоянии лог. 1 при выходном напряжении 2 В, что позволяет работать на линию связи с волновым сопротивлением 50 Ом, нагруженную на конце. Кроме того, гарантируется, что при выходном напряжении 2,7 В в состоянии лог. 1 выходной ток составляет не менее 3 мА.

МикросхемаКР531ЛА17 (рис. 2) – два элемента 4И-НЕ с возможностью перевода выхода в высокоимпедансное состояние при подаче на вход Е лог. 1. При подаче на вход Е лог. 0 выходы активны, допустимые выходные токи составляют 50 мА в состоянии лог. 0 и 32 мА в состоянии лог. 1 при выходном напряжении 2 В, что обеспечивает возможность работы на линию связи с волновым сопротивлением 75 Ом. Дополнительно гарантируется, что при выходном напряжении 2,7 В в состоянии лог. 1 выходной ток составляет не менее 3 мА.

Входные токи микросхем КР531ЛА12, КР531ЛА13, КР531ЛА16, КР531ЛА17 по сигнальным входам в состоянии лог. 0-4 мА, по входам Е – 2 мА.

Микросхема К155ЛА18 (рис. 2) выполнена с открытым коллектором, ее выходное напряжение в состоянии лог. 0 не более 0,5 В при выходном втекающем токе 100 мА и не более 0,8 В при токе 300 мА. Максимальное напряжение на выходе в состоянии лог. 1 — 30 В, что позволяет коммутировать нагрузку мощностью до 9 Вт – электромагнитные реле, маломощные электродвигатели. Лампы накаливания, однако, можно использовать на номинальный ток не более 60 мА, так как сопротивление нити лампы в холодном состоянии значительно меньше номинального.

МикросхемаКР531ЛА19(рис. 2) – двенадцативходовый элемент И-НЕ с возможностью перевода выхода в высокоимпедансное состояние при подаче лог. 1 на вход Е. В состоянии лог. 1 при выходном напряжении 2,4 В микросхема допускает выходной ток до 6,5 мА, в состоянии лог. 0-20 мА.

Микросхема К155ЛП7 (рис. 2) – два стандартных логических элемента И-НЕ с двумя объединенными входами и два n-р-n транзистора с предельно допустимым коллекторным напряжением 30 В и максимальным током коллектора 300 мА. Подложка микросхемы подключена к выводу 8, что позволяет, подключив ее к источнику отрицательного напряжения, коммутировать транзистором и отрицательные сигналы, не выходящие по амплитуде за напряжение этого источника.

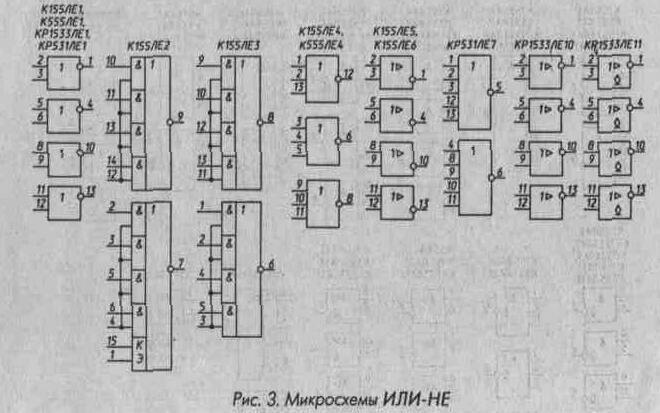

На рис. 3 приведены графические обозначения микросхем, выполняющих функцию ИЛИ-НЕ. На входах микросхемК155ЛЕ2

нормирован также ток при выходном напряжении 2 В – он составляет не менее 42,4 мА, то есть эта микросхема может обеспечивать работу на нагрузку 50 Ом, например, на коаксиальный кабель с волновым сопротивлением 50 или 75 Ом, согласованный на конце.

МикросхемыКР1533ЛЕ10и КР1533ЛЕ11 имеют нагрузочную способность втрое большую стандартной для микросхем этой серии. Микросхема КР1533ЛЕ11 выполнена с открытым коллектором, максимальное напряжение, которое можно подать на ее выход в закрытом состоянии, – 5,5 В.

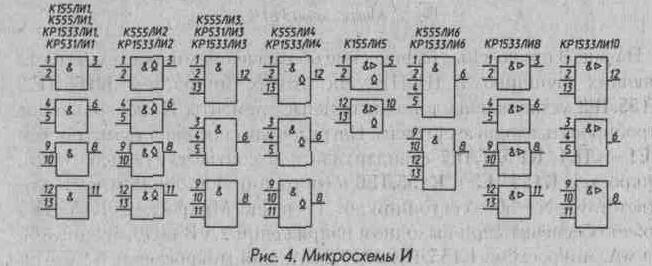

На рис. 4 приведены графические обозначения микросхем, выполняющих функцию И. МикросхемыЛИ1, ЛИЗ, ЛИ6 имеют стандартную для своих серий нагрузочную способность, микросхемыЛИ2

и ЛИ4 выполнены с открытым коллектором, их нагрузочная способность в состоянии лог. 0 стандартная, в состоянии лог. 1 допускается подача напряжения 5,5 В.

МикросхемаК155ЛИ5 выполнена с открытым коллектором, ее нагрузочная способность такая же, как у К155ЛА18.

МикросхемыКР1533ЛИ8 и КР1533ЛИ10

имеют нагрузочную способность втрое большую стандартной для микросхем этой серии.

На рис. 5 приведены графические обозначения микросхем, выполняющих функцию ИЛИ. Микросхема ЛЛ1 имеет стандартную нагрузочную способность, микросхема К155ЛЛ2 выполнена с открытым коллектором и имеет нагрузочную способность такую же, как К155ЛА18.

МикросхемаКР1533ЛЛ4 имеет нагрузоч ную способность втрое большую стандартной для микросхем этой серии

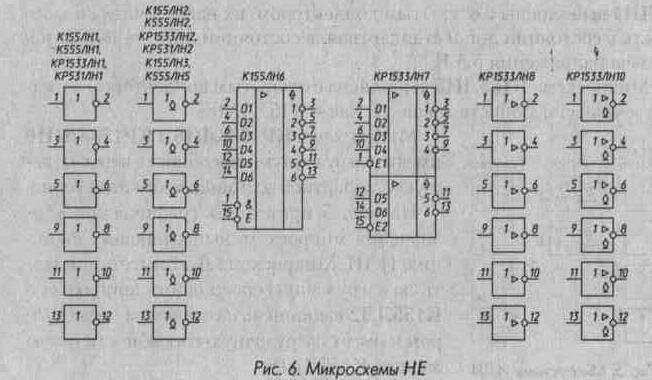

На рис. 6 приведены графические обозначения микросхем, выполняющих функцию НЕ (инверторы). МикросхемыЛН1 имеют стандартную нагрузочную способность, аЛН2, К155ЛНЗ, К155ЛН5 выполнены с открытым коллектором и имеют стандартную нагрузочную способность в состоянии лог. 0. Для К155ЛНЗ и К155ЛН5 дополнительно гарантируется, что при втекающем токе 40 мА выходное напряжение в состоянии лог. 0 не превышает 0,7 В. Допустимое напряжение на выходе микросхемы в состоянии лог. 1 составляет 5,5, 30 и 15 В для ЛН2, К155ЛНЗ и К155ЛН5 соответственно.

МикросхемаК155ЛН6 (рис. 6) – шесть мощных инверторов с возможностью перевода выходов в высокоимпедансное состояние. Управление состоянием выходов производится по двум равноправным входам управления Е (1 и 15), собранным по схеме, выполняющей функцию И. При подаче на оба указанных входа лог. 0 выходы инверторов переходят в активное состояние и инвертируют входные сигналы, при подаче хотя бы на один вход лог. 1 – переходят в высокоимпедансное состояние.

Нагрузочная способность инверторов довольно велика – при лог. 0 на выходе выходной втекающий ток может достигать 32 мА, при этом выходное напряжение не более 0,4 В, при лог. 1 на выходе выходной вытекающий ток – до 5,2 мА при выходном напряжении 2,4 В.

МикросхемаКР1533ЛН7 (рис. 6) – шесть инверторов с повышенной нагрузочной способностью и возможностью перевода выходов в высокоимпедансное состояние. Инверторы объединены в две группы,

у каждой из которых свой вход управления. Подача лог. 0 на вход Е1 включает инверторы с выходами 1-4, на вход Е2 – с выходами 5 и 6. Нагрузочная способность микросхемы 12 мА при 0,4 В в состоянии лог. 0 и 3 мА при 2,4 В в состоянии лог. 1.

МикросхемаКР1533ЛН8 (рис. 6) – шесть инверторов с повышенной нагрузочной способностью; максимальный уровень в состоянии лог. 0 -0,4 В при втекающем токе 12 мА и 0,5 В при 24 мА, минимальный уровень в состоянии лог. 1 2,4 В при вытекающем токе 3,0 мА и 2,5 В при 0,4 мА.

МикросхемаКР1533ЛН10 имеет нагрузочную способность втрое большую стандартной для микросхем этой серии. Микросхема выполнена с открытым коллектором, максимальное напряжение, которое можно подать на ее выход в закрытом состоянии – 5,5 В.

На рис. 7 приведены графические обозначения микросхем, выполняющих функцию И-ИЛИ-НЕ и расширителей И-ИЛИ. Все микросхемы И-ИЛИ-НЕ имеют стандартные выходы, кромеКР531ЛР10 , которая выполнена с открытым коллектором, допустимое напряжение для нее в состоянии лог. 1 – 5,5 В. Следует отметить различие микросхемК155ЛР4 и К555ЛР4, КР1533ЛР4, а такжеК555ЛР11, КР1533ЛР11 и КР531ЛР11. МикросхемыК155ЛР1, К155ЛРЗ, К155ЛР4 имеют входы для подключения расширителей И-ИЛИ К155ЛД1 и К155ЛД2, увеличивающих число групп И в функции ИЛИ этих микросхем. Аналогичные входы для расширения числа входов по ИЛИ имеет микросхемаК155ЛЕ2.

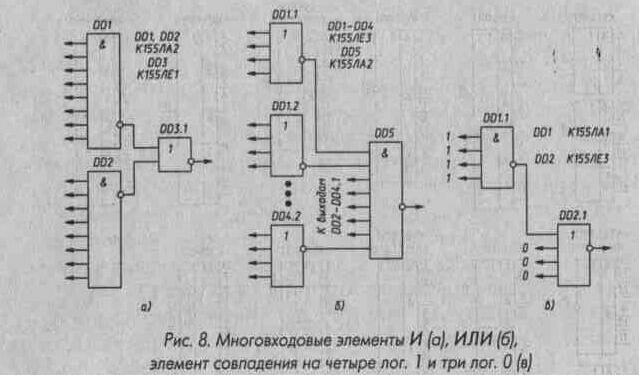

Однако более простой способ построения элементов И или ИЛИ с большим числом входов – каскадное соединение микросхем,

выполняющих функции И-НЕ и ИЛИ-НЕ. На рис. 8 (а) приведена схема элемента И на 16 входов, на рис. 8 (б) – элемента ИЛИ на 32 входа. На рис. 8 (в) приведена схема элемента совпадения, формирующего на своем выходе лог. 1 при лог. 1 на четырех верхних по схеме входах и лог. 0 на трех нижних. Такой элемент может использоваться для дешифрации определенных состояний счетчиков и других устройств.

На рис. 9 приведены графические обозначения микросхем – повторителей входного сигнала.

МикросхемаЛП8 – четыре повторителя входного сигнала с высокоимпедансным состоянием. При лог. 0 на управляющем входе Е сигналы с входа D элемента проходят на выход элемента без инверсии. При лог. 1 на входе Е выход элемента переходит в высокоимпедансное состояние. При лог. 0 на выходе микросхема К155ЛП8 обеспечивает втекающий ток 16 мА, при лог. 1 – вытекающий 5,2 мА, К555ЛП8 – 24 мА и 2,6 мА соответственно.

МикросхемаК155ЛП9 (рис. 9) – шесть повторителей входного сигнала с открытым коллектором, ее выходные параметры такие же, как и у К155ЛНЗ.

МикросхемаК155ЛП10 (рис. 9) – шесть мощных повторителей с возможностью перевода выходов в высокоимпедансное состояние.

Логика управления и нагрузочная способность этой микросхемы такие же, как и у К155ЛН6.

МикросхемаК155ЛП11 (рис. 9) – шесть мощных повторителей, подобных повторителям микросхемы К155ЛП10, но разбитых на две группы, каждая из которых имеет свой вход управления. Подача лог. 0 на вход Е1 включает повторители с выходами 1-4, вход Е2 управляет выходами 5 и 6. Нагрузочная способность микросхемы К155ЛП11 такая же, как у К155ЛН6.

МикросхемыКР1533ЛП16 и КР1533ЛП17 имеют нагрузочную способность втрое большую стандартной для микросхем этой серии. Микросхема КР1533ЛП17 выполнена с открытым коллектором,

максимальное напряжение, которое можно подать на ее выход в закрытом состоянии – 5,5 В.

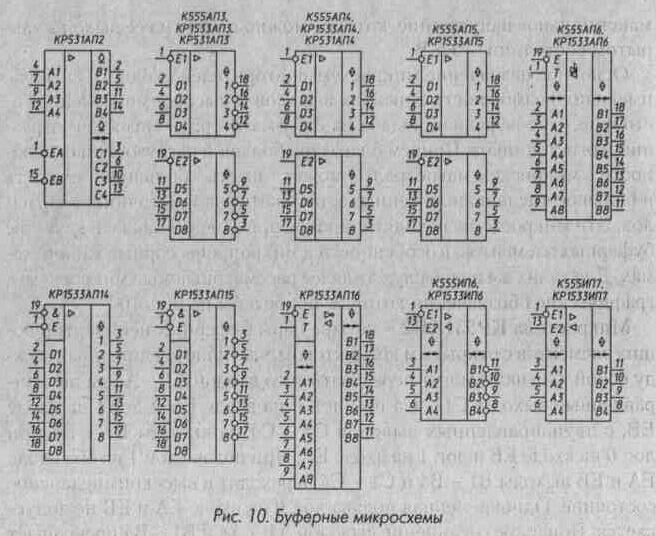

Основное назначение микросхем-повторителей входного сигнала, имеющих возможность перевода выходов в высокоимпедансное состояние, – поочередная подача на одну магистраль сигналов от различных источников. Причем благодаря большой нагрузочной способности микросхем магистраль может иметь большую емкость и большое число подключенных к ней нагрузок и источников сигналов. Эти микросхемы находят широкое применение также в качестве буферных элементов, в особенности в микропроцессорных микросхемах. Для таких же целей служат далее рассматриваемые микросхемы, графические обозначения которых приведены на рис. 10.

МикросхемаКР531АП2 – четыре пары буферных неинвертирующих элементов с открытым коллектором, частично соединенных между собой. Сигналы могут передаваться со входов А1 – А4 на двунаправленные выходы С1 – С4 при лог. 0 на входе ЕА и лог 1 на входе ЕВ, с двунаправленных выводов С1 – С4 на выходы В1 – В4 при лог. 0 на входе ЕВ и лог. 1 на входе ЕА. При подаче лог. 1 на оба входа ЕА и ЕВ выходы В1 – В4 и С1 – С4 переходят в высокоимпедансное состояние. Одновременная подача лог. 0 на входе ЕА и ЕВ не допускается. Попарное соединение выводов А1 – А4 и В1 – В4 превращает микросхему в четыре двунаправленных ключа, максимальный выходной ток в состоянии лог. 0-60 мА, максимальные входное и выходное напряжения в состоянии лог. 1-10,5 В, входной ток в состоянии лог. 0 не превышает 0,15 мА.

МикросхемаАПЗ (рис. 10) – восемь инвертирующих буферных элементов с повышенной нагрузочной способностью и возможностью перевода выходов в высокоимпедансное состояние. Элементы разбиты на две группы по четыре, у каждой из групп свой вход управления для включения элементов и их перевода в третье состояние (Е1 и Е2). Включение элементов каждой группы происходит при подаче на соответствующий вход (Е1 и Е2) лог. О, переход в высокоимпедансное состояние – при подаче лог. 1. Выходной втекающий ток микросхемы К555АПЗ в состоянии лог. О при напряжении на выходе 0,5 В может достигать 24 мА, вытекающий в состоянии лог. 1 при напряжении на выходе 2 В – 15 мА. Для микросхем КР1533АПЗ максимальный уровень лог. 0 0,4 В при втекающем токе 12 мА и 0,5 В при 24 мА. Минимальный уровень лог. 1 2,4 В при вытекающем токе 3 мА и 2,5 В при 0,4 мА. Нагрузочная способность микросхемы КР531АПЗ в состоянии лог. 0 64 мА, в состоянии лог. 1 3 мА при выходном

напряжении 2,4 В и 15 мА при 2 В. Входные токи по сигнальным входам D1 – D8 в состоянии лог. 0 0,4 мА.

МикросхемаАП4 (рис. 10) – восемь аналогичных буферных элементов без инверсии. Отличие ее в том, что один из входов включения элементов и их перевода в третье состояние (El) – инверсный, подобно АПЗ, второй (Е2) – прямой. Нагрузочная способность этой микросхемы такая же, как у АПЗ.

МикросхемаАП5 (рис. 10) – восемь неинвертирующих буферных элементов, обе группы которых имеют инверсные входы управления включением. В остальном эта микросхема аналогична АП4.

Микросхемы АПЗ – АП5 служат для буферизации и коммутации сигналов в микропроцессорных устройствах, например, сигналов адреса, сигналов управления при организации внутренних и внешних шин микро-ЭВМ. Основное их назначение – обеспечение однонаправленной передачи информации. Однако при необходимости с их помощью можно обеспечить и двунаправленную передачу. На рис. 11 в качестве примера показано соединение выводов микросхемы АП4 для получения двунаправленного буферного элемента. При подаче лог. 0 на объединенные между собой входы Е1 и Е2 происходит передача сигнала

от расположенных слева по рисунку выводов микросхемы (входы А1 -А4) к правым (В1 – В4), при подаче лог. 1 – наоборот: от В1 – В4 к А1 -А4. Два треугольника в среднем поле графического обозначения микросхемы символизируют усиление и направление передачи сигнала, верхний – при подаче активного сигнала на вход Е1 (для инверсного входа – лог. 0), нижний – на вход Е2 (для прямого входа – лог. 1).

Интересно отметить, что расположение информационных входов и выходов микросхем АПЗ – АП5 сделано специально такое, как показано на рис. 11, – для удобного их соединения.

Однако для организации двунаправленной передачи информации удобнее использовать специально предназначенные для этой цели микросхемы, описываемые далее.

Микросхема АП6 (см. рис. 10) – восемь двунаправленных неинвертирующих буферных элементов. Кроме двух групп информационных выводов А1 – А8 и В1 – В8, микросхема имеет два входа управления – Е и Т. Сигнал лог. 0, подаваемый на

вход Е, разрешает включение буферных элементов, лог. 1 – переводит все выводы микросхемы в Z-состояние. Сигнал на входе Т действует при лог. 0 на входе Е и определяет направление передачи сигналов – при лог. 1 на входе Т выводы А1 – А8 являются входами, В1 – В8 – выходами, при лог. 0 – наоборот; В1 – В8 – входы, А1 – А8 – выходы. Два треугольника у входа Т символизируют усиление и направление распространения сигнала, верхний – при лог. 1 на входе Т, нижний – при лог. 0.

Микросхема АП6 по своему функционированию (но, к сожалению, не по разводке выводов) соответствует микросхеме КР580ВА86, но потребляет в 1,7 раза меньшую мощность (К555АП6).

МикросхемаКР1533АП14 (рис. 10) содержит восемь однонаправленных буферных элементов с возможностью перевода их выходов в высокоимпедансное состояние. При подаче на оба входа разрешения Е лог. 0 выходы микросхемы переходят в активное состояние и на них появляются без инверсии сигналы с соответствующих входов D1 – D8. При поступлении на любой из входов Е лог. 1 выходы переходят в высокоимпедансное состояние. Микросхема КР1533АП15 (рис. 10) аналогична микросхеме КР1533АП14, только она инвертирует входные сигналы.

МикросхемаКР1533АП16 (рис. 10) состоит из восьми двунаправленных буферных элементов и, в основном, аналогична микросхеме

КР1533АП6. Она инвертирует сигналы при передаче их с выводов А на выводы В и не инвертирует их при передаче в обратном направлении. На графическом изображении микросхемы КР1533АП16 для отражения этого свойства у вывода Т, определяющего направление передачи информации, верхний треугольник, символизирующий передачу сигналов с выводов А на выводы В при подаче на вход Т лог. 1, дополнен кружком инверсии, а нижний треугольник (на входе Т – лог. 0) показан без такого кружка.

МикросхемаИП6 (рис. 10) – четыре двунаправленных инвертирующих буферных элемента. Логика работы входов управления Е1 и Е2

следующая: при лог. 0 на обоих входах передача сигналов происходит от выводов А1 – А4 к выводам В1 – В4, при лог. 1 на обоих входах – от выводов В1 – В4 к А1 – А4. При лог. 1 на входе Е1 и лог. 0 на входе Е2 все информационные выводы микросхемы переходят в Z-состояние, подача лог. 0 на вход Е1 и лог. 1 на вход Е2 одновременно недопустима. Треугольники на графическом обозначении микросхемы и входов Е1 и Е2 символизируют усиление и направление распространения информации при подаче активных сигналов на эти входы.

Нагрузочная способность микросхемы ИП6 такая же, как у АПЗ.

МикросхемаИП7 отличается от ИП6 только тем, что не инвертирует сигналы.

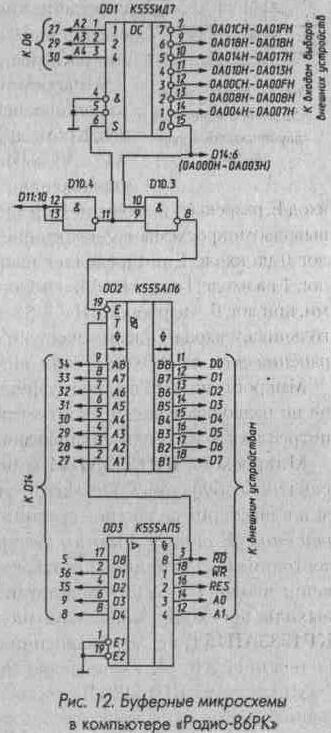

На рис. 12 в качестве примера показано использование буферных микросхем для подключения внешних устройств к компьютеру «Радио-86РК». Если из всех внешних устройств ограничиться лишь таймером КР580ВИ53, его вполне можно смонтировать на

плате компьютера без буферных элементов. Если же предполагается подключение нескольких внешних устройств (таймер, часы, АЦПУ, модем и др.), из-за малой нагрузочной способности центрального процессора КР580ВМ80 необходимы буферные элементы.

На рис. 12 микросхема DD3 обеспечивает буферизацию управляющих сигналов RD, WR, RES и двух младших адресов АО и А1. Микросхема DD2 буферизирует двунаправленную шину данных. Включение этой микросхемы по входу Е должно происходить лишь при обращении к внешним устройствам, что обеспечивается микросхемой DD1 и элементами D10.4 и D10.3.

В основном варианте компьютера «Радио-86РК» адреса А000Н -BFFFH использованы для микросхемы D14. Практически используются только четыре адреса – А000Н, А001Н, А002Н, А00ЗН. Установкой дешифратора DD1 можно обеспечить при сохранении этих адресов для D14 использование следующих четырех адресов А004Н, АООЗН, А006Н, А007Н – для первого внешнего устройства, например таймера;

следующих четырех А00ЗН – А00ВН – для второго; следующих четырех А00СН – A00FH – для третьего и т. д., всего можно будет подключить семь дополнительных внешних устройств, для каждого из которых будет отведено четыре адреса. Если входы 1,2,4 дешифратора DD1 подключить к другим выходам адреса микропроцессора D6, например, А10, All, A12, на каждое внешнее устройство будет отведено по 1024 адреса.

Элементы D10.4 и D10.3 необходимы для выключения DD2 при обращении микропроцессора к D14, то есть по адресам А000Н – А00ЗН. В этом случае лог. 0 с выхода О DD1 включает D10.3 и лог. 1 с его выхода выключает DD2. Направление передачи сигнала через DD2 определяется сигналом RD. При чтении из внешнего устройства сигнал RD

принимает значение лог. 0 и происходит передача сигналов через DD2 от внешнего устройства к микропроцессору, в остальных случаях – от микропроцессора к внешнему устройству.

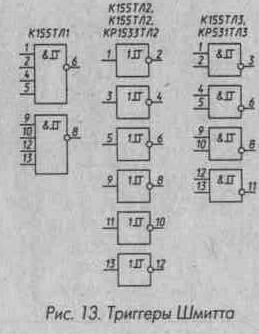

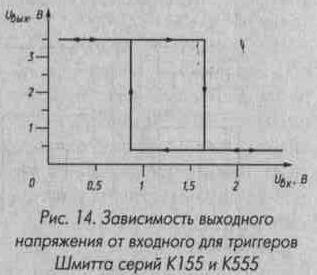

На рис. 13 приведены микросхемы -инвертирующие триггеры Шмитта. Микросхема К155ТЛ1 – два четырехвходовых элемента И-НЕ, микросхемаТЛЗ – четыре двухвходовых, микросхемаТЛ2 – шесть инверторов.

Указанные микросхемы при плавном изменении входного сигнала обеспечивают

скачкообразное переключение выходного (рис. 14). При повышении напряжения на входе элемента микросхемы от нуля выходное напряжение скачком изменяется с лог. 1 на лог. 0 при напряжении на входе около 1,65 В. При снижении напряжения на входе обратное изменение выходного напряжения происходит при напряжении на входе около 0,85 В для триггеров Шмитта серий К155 и К555ТЛ2 и около 1,2 В для КР531ТЛЗ.

Триггеры Шмитта применяют для формирования ТТЛ-сигнала из синусоидального, для приема сигналов при большом уровне помех, в формирователях и генераторах импульсов и в других случаях.

На рис. 15, а показана схема формирователя импульса сброса при включении питания, обеспечивающего крутой фронт при большой длительности импульса, на рис. 15, б – простейшего генератора импульсов.

Изучение работы более сложных микросхем удобно продолжить с микросхем последовательностного типа.

lib.qrz.ru

Цифровые микросхемы. Логический элемент НЕ (INV)

Всем доброго времени суток! Как дом строят из кирпичей, так и цифровые устройства состоят из простых элементов – цифровых микросхем. Наиболее простые из них – логические элементы (или вентили, gates). В одной микросхеме может содержаться только строго определённое количество логических элементов, их может быть или 1, или 2, или 3, или 4, или 8 в одной микросхеме. Соответственно каждый логический элемент может иметь от 1 до 12 входов и 1 выход. При этом связь между входами и выходом соответствует таблице истинности. Логические элементы относятся к так называемым комбинационным микросхемам, и у них отсутствует какая-либо внутренняя память.

Достоинством логических вентилей является высокое быстродействие и небольшая потребляемая мощность, но на их основе довольно трудно реализовать сложную функциональность, поэтому чаще всего они используются в качестве дополнения к более сложным цифровым микросхемам или микроконтроллерам.

Логический элемент НЕ (Hex Inverters)

Начнём с наиболее простого из логических элементов – логического элемента НЕ (INV) или как его ещё называют инвертора. Как понятно из названия инвертор применяется для инвертирования, то есть изменения уровня сигнала (например, на вход поступает логическая «1», а на выходе получаем логический «0»). Как самый простой из логических элементов инвертор содержит всего один вход и один выход. Инверторы могут быть с тремя типами выходов: 2С, ОК или с Z – состоянием. Как указывалось в этой статье логический элемент НЕ имеет следующую таблицу истинности:

Таблица истинности логического элемента НЕ

На принципиальных схемах логические элементы НЕ (инверторы) имеют следующее обозначение

Обозначения логических элементов НЕ (Hex Inverters): ANSI (слева) и DIN (справа).

Микросхемы инверторов содержат обычно шесть логических элементов НЕ (INV) и обозначаются префиксом ЛН (например, К155ЛН1, К561ЛН2). Как говорилось ранее, для ТТЛ микросхем с выходом ОК необходим выходной нагрузочный резистор (pull-up). Величина которого рассчитывается очень просто: R > U/IOL, где U – напряжение источника питания, к которому подключается резистор.

Применение инверторов

Обычно, элементы НЕ применяются для преобразования уровней сигнала (из высокого в низкий или из низкого в высокий уровень). Второе предназначение – увеличения нагрузочной способности (буферизации) с инвертирование выходов более сложных микросхем. Например, когда сигнал с выхода микросхемы необходимо подать на несколько других, а выходной ток недостаточен.

Но существует и несколько нестандартных применений инверторов: построение генераторов и в случае, когда необходимо создать задержку сигнала.

Схема генератора на логических элементах НЕ

Схемы генераторов представляют собой обыкновенные RC-генераторы, но характеристики можно рассчитать только приблизительно, так как она зависит от напряжения питания и типа применённой микросхемы. Частота генератора будет равна

[math]f \approx \frac{1}{2RC}[/math]Генераторы данного типа можно применять там, где не важна стабильность частоты, а важен лишь факт генерации импульсов. Более стабильные по частоте генераторы получаются, если вместо конденсатора применить кварцевый резонатор.

Схема кварцевого генератора на логических элементах НЕ

Довольно часто в цифровых схемах необходимо получит некоторую задержку сигнала, в этом случае инверторы могут пригодиться, на большую задержку рассчитывать не приходится (примерно до 100 нс). Для получения задержки сигнала инверторы соединяют последовательно.

Схема для создания задержки сигнала на инверторах

Величину задержки можно рассчитать приблизительно по сумме задержек входного и выходного сигналов (tPLH и tPHL) для данной микросхемы. Например, для четырёх инверторов величину задержки можно оценить по формуле

[math]t_{З} = 2t_{PLH} + 2t_{PHL}[/math]но необходимо учитывать, что значения реальных задержек сильно отличаются от тех что даны в справочнике (в справочнике даны максимальные величины, а реальные могут обличаться более, чем в 2 раза).

Более значительные величины задержки сигнала можно получить, используя интегрирующие RC-цепи, но и здесь нельзя точно говорить о величине задержки, потому что разные типы цифровых микросхем срабатывают при разном уровне сигнала и разных напряжениях питания.

Схема для создания задержки сигнала c интегрирующей цепью

Ниже приведена таблица некоторых семейств микросхем, которые имеют в своём составе инверторы

| Серия | Номер микросхемы | |||||||

| ЛН1 | ЛН2 | ЛН3 | ЛН5 | ЛН6 | ЛН7 | ЛН8 | ЛН10 | |

| К155 | 6НЕ | 6НЕ(ОК) | 6НЕ(ОК) | 6НЕ(ОК) | 6НЕ(Z) | 6НЕ(Z) | — | — |

| К555 | 6НЕ | 6НЕ(ОК) | — | — | — | 6НЕ(Z) | — | — |

| КР1533 | 6НЕ | 6НЕ(ОК) | — | — | — | 6НЕ(Z) | 6НЕ | 6НЕ(ОК) |

| К561 | 6НЕ(Z) | 6НЕ | 6НЕ(Z) | — | — | — | — | — |

| КР1554 | 6НЕ | — | — | — | — | — | — | — |

| КР1564 | 6НЕ | — | — | — | — | 6НЕ(Z) | — | — |

Теория это хорошо, но без практического применения это просто слова.Здесь можно всё сделать своими руками.

www.electronicsblog.ru

Описание микросхемы К155ЛА3 | joyta.ru

Микросхема К155ЛА3 является, по сути, базовым элементом 155-ой серии интегральных микросхем. Внешне по исполнению она выполнена в 14 выводном DIP корпусе, на внешней стороне которого выполнена маркировка и ключ, позволяющий определить начало нумерации выводов (при виде сверху — от точки и против часовой стрелки).

В функциональной структуре микросхемы К155ЛА3 имеется 4 самостоятельных логических элементов 2И-НЕ. Одно лишь их объединяет, а это линии питания (общий вывод — 7, вывод 14 – положительный полюс питания) Как правило, контакты питания микросхем не изображаются на принципиальных схемах.

Каждый отдельный 2И-НЕ элемент микросхемы К155ЛА3 на схеме обозначают DD1.1, DD1.2, DD1.3, DD1.4. По правую сторону элементов находятся выходы, по левую сторону входы. Аналогом отечественной микросхемы К155ЛА3 является зарубежная микросхема SN7400, а все серия К155 аналогична зарубежной SN74.

Таблица истинности микросхемы К155ЛА3

Опыты с микросхемой К155ЛА3

На макетную плату установите микросхему К155ЛА3 к выводам подсоедините питание (7 вывод минус, 14 вывод плюс 5 вольт). Для выполнения замеров лучше применить стрелочный вольтметр, имеющий сопротивление более 10 кОм на вольт. Спросите, почему нужно использовать стрелочный? Потому, что, по движению стрелки, можно определить наличие низкочастотных импульсов.

После подачи напряжения, измерьте напряжение на всех ножках К155ЛА3. При исправной микросхеме напряжение на выходных ножках (3, 6, 8 и 11) должно быть около 0,3 вольт, а на выводах (1, 2, 4, 5, 9, 10, 12, и 13) в районе 1,4 В.

Для исследования функционирования логического элемента 2И-НЕ микросхемы К155ЛА3 возьмем первый элемент. Как было сказано выше, его входом служат выводы 1 и 2, а выходом является 3. Сигналом логической 1 будет служить плюс источника питания через токоограничивающий резистор 1,5 кОм, а логическим 0 будем брать с минуса питания.

Опыт первый (рис.1): Подадим на ножку 2 логический 0 (соединим ее с минусом питания), а на ножку 1 логическую единицу (плюс питания через резистор 1,5 кОм). Замерим напряжение на выходе 3, оно должно быть около 3,5 В (напряжение лог. 1)

Вывод первый: Если на одном из входов лог.0, а на другом лог.1, то на выходе К155ЛА3 обязательно будет лог.1

Опыт второй (рис.2): Теперь подадим лог.1 на оба входа 1 и 2 и дополнительно к одному из входов (пусть будет 2) подключим перемычку, второй конец которой будет соединен с минусом питания. Подадим питание на схему и замерим напряжение на выходе.

Оно должно быть равно лог.1. Теперь уберем перемычку, и стрелка вольтметра укажет напряжение не более 0,4 вольта, что соответствует уровню лог. 0. Устанавливая и убирая перемычку можно наблюдать как «прыгает» стрелка вольтметра указывая на изменения сигнала на выходе микросхемы К155ЛА3.

Вывод второй: Сигнал лог. 0 на выходе элемента 2И-НЕ будет только в том случае, если на обоих его входах будет уровень лог.1

Следует отметить, что неподключенные входы элемента 2И-НЕ («висят в воздухе»), приводит к появлению низкого логического уровня на входе К155ЛА3.

Опыт третий (рис.3): Если соединить оба входа 1 и 2, то из элемента 2И-НЕ получится логический элемент НЕ (инвертор). Подавая на вход лог.0 на выходе будет лог.1 и наоборот.

Источник: «Энциклопедия начинающего радиолюбителя», Никулин С.А

www.joyta.ru

Справочник “Цифровые Интегральные Микросхемы”

Справочник “Цифровые Интегральные Микросхемы” [ Содержание ]2.4.2 Микросхемы типа ЛА, ЛИ

Чтобы рассмотреть схемотехнику, составим таблицу функций элементов И, И-НЕ для двух входов А и В (простейший вариант). Каждая переменная А и В моделируется электронным ключом, который можно замкнуть или разомкнуть. Если ключи соединены последовательно, то они работают согласно логике И: ток в цепи появится, если замкнуть оба ключа: и А и В. Если активными входными сигналами считать замыкание ключей А и В и назвать это событие логической 1, то, последовательно перебирая состояние этих ключей, составим таблицу входных и выходных данных для элементов И и И-НЕ.

| Логический элемент | Входные переменные | Выходная функция | ||

|---|---|---|---|---|

| А | B | И | НЕ-И | |

| 0 | 0 | 0 | 1 | |

| 0 | 1 | 0 | 1 | |

| 1 | 0 | 0 | 1 | |

| 1 | 1 | 1 | 0 | |

Рассмотрим способ реализации логической операции И-НЕ на элементах ТТЛ. На рис. 2.8, а приведена принципиальная схема двухвходового логического элемента И-НЕ.

Рис. 2.8.а. Принципиальная схема логического элемента.

Подавая от ключей S1 и S2 на входы А и В напряжение высокого В и низкого Н уровней, составим таблицу выходных уровней элемента.

| Вход | Выход Q(НЕ-И) | Вход | Выход Q(НЕ-И) | ||

|---|---|---|---|---|---|

| А | B | A | B | ||

| Н | Н | В | 0 | 0 | 1 |

| Н | В | В | 0 | 1 | 1 |

| В | Н | В | 1 | 0 | 1 |

| В | В | Н | 1 | 1 | 0 |

Напряжение низкого уровня Н появляется на выходе Q, когда на обоих входах А и В присутствует высокое напряжение В. Условное графическое обозначение двухвходового логического элемента показано на рис 2.8, в

Рис 2.8.в. Условное обозначение элемента.

Среди простейших ИС ТТЛ преобладают элементы И, И-НЕ. Каждый из корпусов ИС типа ЛА и ЛИ содержит от двух до четырех логических элементов, а микросхемы ЛА2 и ЛА19 содержат по одному логическому элементу И-НЕ на восемь и двенадцать входов соответственно.

Цоколевки микросхем типа ЛА и ЛИ и их условные графические обозначения приведены на рис. 2.9, а основные параметры даны в табл. 2.3.

Рис 2.9. Условные обозначения и цоколевки микросхем ЛИ

Рис 2.9. Условные обозначения и цоколевки микросхем ЛА

Следует особо выделить группу микросхем, логические элементы которых имеют выходы с открытым коллектором (ЛА7…ЛА11, ЛА13. ЛА18), (ЛИ2, ЛИ4, ЛИ5). Схема двухвходового логического элемента И-НЕ с открытым коллектором показана на рис. 2.10, а.

Рис. 2.10а. Принципиальная схема логического элемента И-НЕ

Для формирования выходного перепада напряжения к выходу такого элемента необходимо подключить внешний нагрузочный резистор Rн. Такие микросхемы применяются для обслуживания сегментов индикаторов, зажигания ламп накаливания, светодиодов (рис. 2.10,б).

Рис. 2.10б. Схема подключения ламп накаливания и светодиодов

При необходимости в схемах можно использовать элемент ТТЛ с двухтактным выходом. Для некоторых микросхем с открытым коллекторным выходом (ЛА11) нагрузку можно подключать к более высоковольтному источнику питания (рис. 2.10,в).

Рис. 2.10в. Схема подключения нагрузки к высоковольтному источнику

Такое включение необходимо для зажигания газоразрядных и электролюминесцентных индикаторов. Выходы с открытого коллектора используют для подключения обмоток реле.

Выходы нескольких элементов с открытым коллектором можно присоединять к общей нагрузке Rн (рис. 2.10, г).

Рис. 2.10г. Схема подключения нескольких элементов к общей нагрузке

Такое подключение позволяет реализовать логическую функцию И, называемую «монтажное И». Схему (рис. 2.10. г) используют для расширения числа входов логического элемента.

Следует помнить, что двухтактные выходы ТТЛ нельзя соединять параллельно, это приводит к токовой перегрузке одного из элементов.

Многовходовые составные логические элементы с открытым коллектором и общим сопротивлением нагрузки Rн реализуются наиболее просто, однако они не позволяют получить предельное быстродействие. Более лучший способ увеличения числа входов осуществляется с помощью специальной микросхемы-расширителя, имеющей дополнительные выводы коллектора и эмиттера фазоразделительного каскада VT2 (рис. 2.11). Одноименные вспомогательные выводы нескольких таких элементов можно объединять.

Рис. 2.11а. Принципиальная схема 2И-НЕ с дополнительными выводами коллектора и эмиттера.

Рис. 2.11б. Условное обозначение расширителя и способ соединения нескольких микросхем.

Микросхема К531ЛА16 (магистральный усилитель) может передавать данные в линию с сопротивлением 50 Ом.

Микросхемы ЛА17, ЛА19 – это логические элементы И-НЕ с тремя состояниями на выходе, т. е. они имеют дополнительный вход /ЕО (Enable output), дающий разрешение по выходу. На рис. 2.12 показана схема элемента, который имеет третье выходное состояние Z, когда выход размыкается.

Рис. 2.12. Принципиальная схема логического элемента с тремя состояниями на выходе.

Для этой цели в схему стандартного сложного инвертора ТТЛ вводится дополнительный инвертор DDI и диод VD2. Если на этот вход /ЕО подать от переключателя S1 напряжение высокого уровня – 1, то выходное напряжение инвертора DD1 станет низким, т. е. катод диода VD2 будет практически соединен с корпусом. Из-за этого коллектор транзистора VT2 будет иметь нулевой потенциал, т. е. транзистор VT2 будет закрыт. Транзисторы VT3 и VT4 будут находиться в режиме отсечки, т. е. оба закрыты. Следовательно, выходной вывод как бы «висит» в воздухе, микросхема переходит в состояние Z с очень большим выходным сопротивлением. Если на вход ЕО подается разрешающий низкий уровень – О, то логический элемент И-НЕ работает как в обычном режиме.

| Вход | Выход | ||

|---|---|---|---|

| /EO | I | /Y | |

| 0 | 0 1 | 1 0 | |

| 1 | 0 1 | Z | |

Такие логические элементы разработаны специально для обслуживания проводника шины данных. Если к такому проводнику присоединить много выходов, находящихся в состоянии Z, то они не будут влиять друг на друга. Активным передающим сигналом должен быть лишь один логический элемент, только от его выхода в проводник шины данных будет поступать информация. Следовательно, соединенные вместе выходы не должны быть одновременно активными.

Чтобы сигналом разрешения (низкий уревень – О) , подаваемым на вход /EO, подключался к проводнику выход только одного логического элемента, необходимо предусмотреть дополнительный (защитный) временной интервал, т. е. переключать входы /ЕО различных элементов с паузой. Сигналы разрешения, даваемые выходам разных элементов, не должны перекрываться.

Микросхема К531ЛА19-это 12-входовый логический элемент И-НЕ с дополнительным инверсным входом /ЕО. Сигнал появится на его выходе, если на вход /ЕО подано напряжение низкого уровня – О. Выход логического элемента перейдет в разомкнутое состояние Z, если на вход /ЕО подается напряжение высокого уровня. В состоянии Z элемент потребляет ток Iпот.z=25 мА. Время задержки перехода выхода к разомкнутому состоянию tзд.1z= 16 нс, время задержки перехода выхода tзд.0z= 12 нс (от напряжения низкого выходного уровня), при условии, что Сн = 15 пФ [1].

www.asvcorp.ru

Логические элементы и их типы, микросхемы и основы цифровой электроники

Существует три основных типа логических схем:

- Схема отрицания НЕ инвертор. Схема является одновходовой, на выходе которой сигнал «Y» возникает при отсутствии сигнала «х» на входе. На принципиальных схемах элемент НЕ изображается в виде прямоугольников (рис. 20.1). Его условным символом служит цифра 1, расположенная внутри прямоугольника в левом верхнем углу, и кружок, обозначающий линию выхода. Расположенная возле изображения логического элемента таблица истинности позволяет сделать вывод, каким будет сигнал на выходе при определенной комбинации логических сигналов на входе.

- Схема совпадения И представляет собой многовходовую схему, на выходе которой сигнал «Y» возникает только при наличии сигналов «Хі, х2 … хп» одновременно на всех выходах. На рис. 20.2 приведено графическое изображение логического элемента с двумя входами -2И и его таблица истинности. Характерным отличием этого элемента на схемах, является наличие внутри прямоугольника английского знака «&» (английский союз «и» логическое умножение), в левом верхнем углу.

- Схема сборки ИЛИ многовходовая схема, сигнал «у» на выходе которой, появляется при наличии сигнала хотя бы на одном из входов. На рис. 20.3 представлено графическое изображение схемы и ее таблица истинности.

Рис. 20.1. Условное графическое обозначение логического элемента НЕ (а) и таблица истинности (б)

Рис. 20.2. Условное графическое обозначение логического элемента И (а) и таблица истинности (б)

Рис. 20.3. Условное графическое обозначение логического элемента ИЛИ (а) и таблица истинности (б)

Существуют и более сложные логические схемы, представляющие собой соединение нескольких простейших схем. Для запоминания результатов преобразований, которые выполняются логическими схемами применяют элемент памяти триггер. Его схема имеет два выхода (единичный и нулевой) и несколько входов. Триггер может находиться в одном из возможных состояний: единичном или нулевом. Состояние триггера зависит от вида (1 или 0) дискретного сигнала, поступающего на его вход.

Микросхемы серии 155

Большой популярностью среди радиолюбителей пользуются микросхемы серии 155, которые построены на основе так называемой транзисторно-транзисторной логики (ТТЛ). Эта серия включает многовходовые элементы И-НЕ, триггеры, счетчики, дешифраторы, запоминающие устройства и т.д. Напряжение питания микросхем серии 155 составляет 5±0,25 В, которое подается на выводы 14 (+5 В) и 7 (общий провод). При изображении логических элементов на принципиальных схемах подключение к ним источника питания, как правило, не показывают. Рассмотрим практическое использование в радиоэлектронных конструкциях микросхем серии 155. Наиболее часто в конструкциях используется микросхема K155ЛA3. Условное графическое изображение K155JIA3 приведено на рис. 20.4.а. В состав микросхемы входит четыре элемента 2И-НЕ, каждый из которых выполняет операцию логического умножения сигналов по двум входам с последующей инверсией результата на выходе. Следует отметить, что логический элемент, входящий в микросхему, может работать отдельно независимо от других, в связи с этим на принципиальных схемах элементы, составляющие микросхему, изображаются отдельно один от другого. На принципиальных схемах этот факт отмечают в буквенно-цифровом обозначении, например, DD1.1, DD1.2, DD1.3 и DD1.4 (рис. 20.4.6). Принципиальная схема одного логического элемента дана на рис. 20.5.

Рис. 20.4. Условное графическое изображение интегральной микросхемы К155ЛАЗ: а без деления на элементы, б с выделением входящих элементов 2И-НЕ

Как видно из представленной схемы, входящие в нее транзисторы имеют непосредственную связь. В схеме транзистор VT1 имеет два эмиттера и выполняет логическое умножение, VT2 усиление, ѴТЗ усиление, a ѴТ4 инверсию сигнала. Необходимый режим работы транзисторов задается резисторами R1…R4. Диоды VD1…VD3 предназначены для защиты цепей от напряжения обратной полярности. В момент поступления напряжения на один или оба входа логического элемента (выводы 1 и 2), транзистор VT1 открыт. В то время, как транзистор VT2 закрыт, на базу транзистора VT4 поступает напряжение низкого логического уровня, которое закрывает этот транзистор. В то же время, транзистор ѴТЗ открыт, так как напряжение на его базе, наоборот, соответствует уровню логической 1.

Рис. 20.5. Принципиальная схема логического элементов 2И-НЕ, входящего в интегральную микросхему К155ЛАЗ

В итоге на выходе (вывод 3) элемента оказывается напряжение высокого логического уровня и через нагрузку проходит ток. Если подать на оба входа элемента сигнал, соответствующий логической единицы, то транзистор VT1 закроется, a ѴТ2 откроется. Транзисторы ѴТЗ и ѴТ4 переключатся в противоположные состояния, на выходе появится логический 0 и через нагрузку не будет идти ток. Основными параметрами логической микросхемы, состоящей из элементов И-НЕ, являются:

- Напряжение питания Un.

- Потребляемая от источника питания номинальная мощность Рном.

- Пороговое напряжение Unop переключения логического элемента из одного состояния в другое.

- Выходное напряжение Uвых логического 0 и единицы.

- Время включения tвкл и выключения tвыкл.

- Коэффициент разветвления по выходу Краз показывающий, какую из микросхем можно подключить к выходу данного элемента.

Литература: В.М. Пестриков. Энциклопедия радиолюбителя.

nauchebe.net

Схемная реализация логических элементов И-ИЛИ-НЕ и других

Для выполнения логических операций и решать логические задачи с помощью средств электроники были изобретены логические элементы. Их создают с помощью диодов, транзисторов и комбинированных элементов (диодно-транзисторные). Такая логика получила название диодной логики (ДЛ), транзисторной (ТЛ) и диодно–транзисторной (ДТЛ). Используют как полевые, так и биполярные транзисторы. В последнем случае предпочтение отдается устройствам типа n-p-n, так как они обладают большим быстродействием.

Логический элемент «ИЛИ»

Схема логического элемента «ИЛИ» представлена на рисунке 1 а. На каждый из входов может подаваться сигнал в виде какого-то напряжения (единица) или его отсутствия (ноль). На резисторе R появиться напряжение даже при его появлении на каком – либо из диодов.

Рис. 1

Рис. 1Элементы или могут иметь несколько логических входов. Если используются не все входы, то те входы которые не используются следует соединять с землей (заземлять), чтобы избежать появления посторонних сигналов.

На рисунке 1б показано обозначение на электрической схеме элемента, а на 1в таблица истинности.

Логический элемент «И»

Схема элемента приведена на рис. 2. Если хотя – бы к одному из входов будет сигнал равный нулю, то через диод будет протекать ток. Падение напряжения на диоде стремится к нулю, соответственно на выходе тоже будет ноль. На выходе сможет появится сигнал только при условии, что все диоды будут закрыты, то есть на всех входах будет сигнал. Рассчитаем уровень сигнала на выходе устройства:

Рис.2

Рис.2на рис. 2 б – обозначение на схеме, в – таблица истинности.

Логический элемент «НЕ»

В логическом элементе «НЕ» используют транзистор (рис.3 а). при наличии положительного напряжения на входе х=1 транзистор открывается и напряжение его коллектора стремится к нулю. Если х=0 то положительного сигнала на базе нет, транзистор закрыт, ток не проходит через коллектор и на резисторе R нет падения напряжения, соответственно на коллекторе появится сигнал Е. условное обозначение и таблица истинности приведены на рис. 3 б,в.

Рис.3

Рис.3Логический элемент «ИЛИ-НЕ»

При создании различных схем на логических элементах часто применяют элементы комбинированные. В таких элементах совмещены несколько функций. Принципиальная схема показана на рис. 4 а.

Рис.4

Рис.4Здесь диоды Д1 и Д2 выполняют роль элемента «ИЛИ», а транзистор играет роль инвертора. Обозначение элемента на схеме и его таблица истинности рис. 4б и в соответственно.

Логический элемент «И-НЕ»

Показана схема на рис. 5 а. Здесь диод Д3 выполняет роль так сказать фильтра во избежание искажения сигнала. Если на вход х1 или х2 не подан сигнал (х1=0 или х2=0), то через диод Д1 или Д2 будет протекать ток. Падение на нем не равно нулю и может оказаться достаточным для открытия транзистора. Последствием чего может стать ложное срабатывание и на выходе вместо единицы мы получим ноль. А если в цепь включить Д3, то на нем упадет значительная часть напряжения открытого на входе диода, и на базу транзистора практически ничего не приходит. Поэтому он будет закрыт, а на выходе будет единица, что и требуется при наличии нуля на каком либо из входов. На рис. 5б и в показаны таблица истинности и схемное обозначение данного устройства.

Рис.5

Рис.5Логические элементы получили широчайшее применение в электронике и микропроцессорной технике. Многие системы управления строятся с использованием именно этих устройств.

elenergi.ru

Микросхема 74266

74266

Описание

Описание

Микросхема 74266 содержит четыре отдельных логических элемента ИСКЛЮЧАЮЩЕЕ ИЛИ-НЕ с двумя входами каждый. Выходы имеют открытый коллектор.

Работа схемы

Работа схемы

Все четыре логических элемента ИСКЛЮЧАЮЩЕЕ ИЛИ-НЕ микросхемы 74266 можно использовать независимо друг от друга.

Когда сигнал высокого уровня присутствует только на одном из входов микросхемы 74266, на выходе логического элемента формируется напряжение низкого уровня. Если же на оба входа подается напряжение высокого или низкого уровня, то на выходе формируется напряжение высокого уровня.

Логический элемент микросхемы 74266 можно использовать в качестве цифрового компаратора, в котором на выходе устанавливается напряжение высокого уровня при поступлении на входы сигналов одного и того же логического уровня. Если же на входы приходят сигналы разных логических уровней, то на выходе создается напряжение низкого уровня. Логический элемент может также работать как управляемый инвертор, поскольку напряжение высокого уровня на входе позволяет всегда передавать сигнал, подаваемый на второй вход, без изменения. И наоборот, напряжение низкого уровня на одном входе позволяет передавать на выход инвертированное значение напряжения со второго входа.

Выходы с открытым коллектором микросхемы 74266 дают возможность использовать микросхему в качестве 4-разрядного компаратора.

Применение

Применение

Реализация логической операции ИСКЛЮЧАЮЩЕЕ ИЛИ-НЕ, формирование и проверка на чётность-нечётность; сумматор/вычитатель, логические компараторы. Производится следующая номенклатура микросхем: 74LS266.

| Тип микросхемы | 74LS266 |

|---|---|

| Максимальное выходное напряжение, В | 5,5 |

| Время задержки прохождения сигнала, нс | 18 |

| Ток потребления, мА | 8 |

| Входы | Выход | |

|---|---|---|

| A | B | Y |

| 0 | 0 | 1 |

| 0 | 1 | 0 |

| 1 | 0 | 0 |

| 1 | 1 | 1 |

www.microshemca.ru