Микроконтроллеры на ядре ARM Cortex M4/M4f

Компания Microchip предлагает следующие семейства микроконтроллеров на ядре Cortex M4/M4f:

|

SAMG55 – серия микроконтроллеров, построенных на вычислительном ядре Cortex M4. Микроконтроллеры SAMG55 адаптированы для применения в системах промышленной автоматики. Вычислительные ресурсы

|

|

Память

|

|

Аналоговые периферийные модули

|

Периферийные модули

|

|

Микроконтроллеры SAMG55 выпускаются в корпусах 49/WLCSP, 64/LQFP и 64/VQFN.

Наличие на складе |

|

|

SAME51/E54 – серия микроконтроллеров, построенных на вычислительном ядре Cortex M4f. Микроконтроллеры SAME51/E54 адаптированы для применения в системах домашней и промышленной автоматики.

|

|

Память

|

|

Аналоговые периферийные модули

|

Периферийные модули

|

|

Микроконтроллеры SAME51/E54 выпускаются в корпусах от 48 до 128 выводов, которые различаются по размеру памяти.

Наличие на складе |

|

По техническим вопросам и условиям поставки микроконтроллеров Microchip обращайтесь к специалисту компании «ЭФО» Мялкину Никите: nsm@efo. ru.

ru.

Производители

Новости

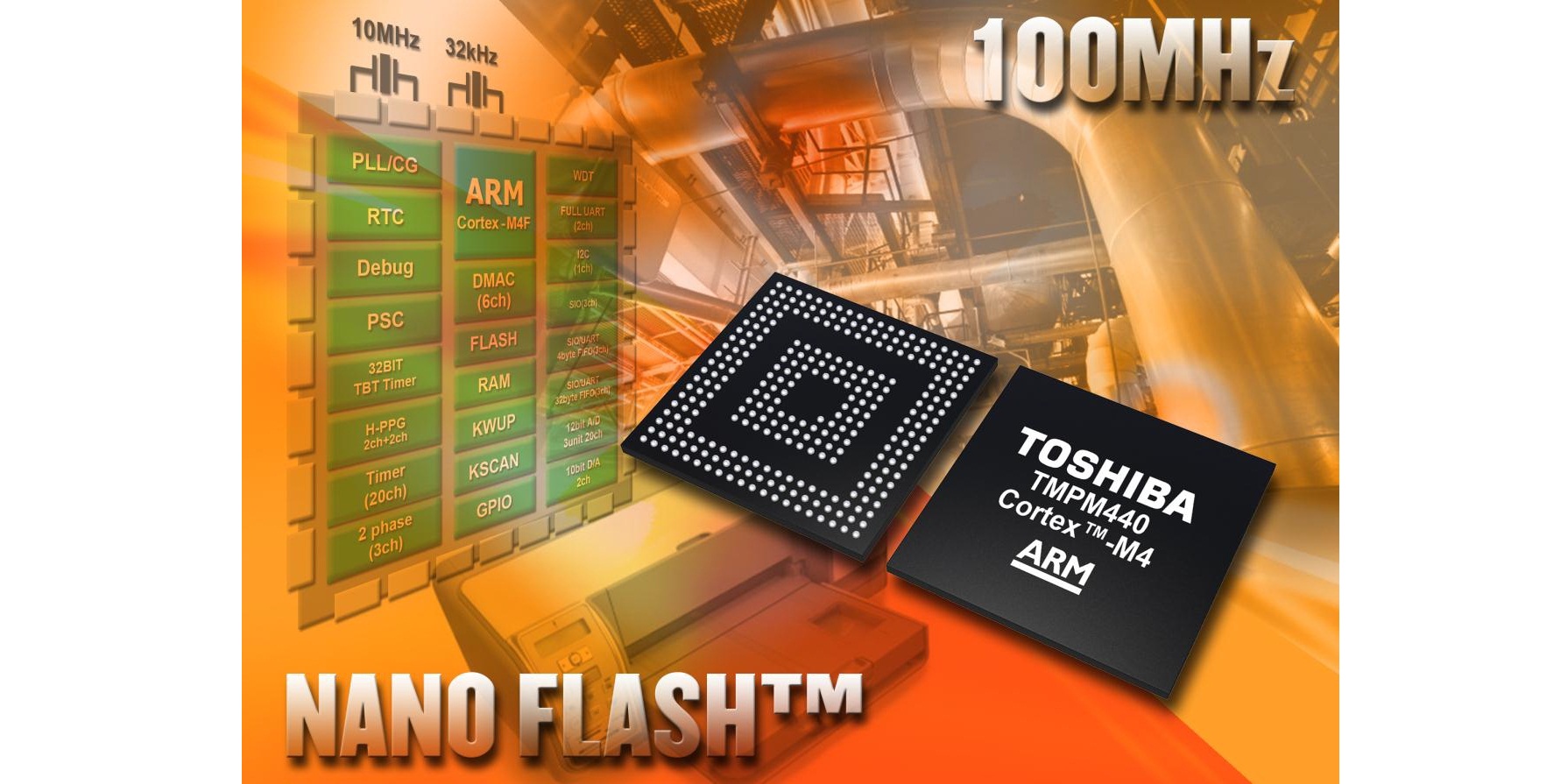

ARM Cortex-M4F от Texas Instruments

14 декабря 2011

Компания Texas Instruments представила новое поколение микроконтроллеров Stellaris на базе ARM Cortex-M4F — LM4Fx. Представленные микроконтроллеры выполнены по 65 нм технологии, что позволяет достичь хорошего соотношения между такими параметрами, как высокая производительность, малое энергопотребление и цена.

Представленные микроконтроллеры выполнены по 65 нм технологии, что позволяет достичь хорошего соотношения между такими параметрами, как высокая производительность, малое энергопотребление и цена.

Семейство Stellaris ARM Cortex- M4F, получившее название Stellaris LM4F, по сути является расширением популярного семейства ARM Cortex- M3, включающее дополнительные DSP-подобные инструкции, а также модуль операций с плавающей точкой. Процессор ARM Cortex-M4 поддерживает широкий набор одноцикловых команд умножения с накоплением (MAC), команды централизованного управления потоком данных (SIMD) и арифметические команды «с насыщением», а также имеет модуль обработки операций с плавающей запятой (FPU) .

Основными областями применения семейства LM4F являются микроконтроллеры общего назначения, USB контролеры, контролеры для промавтоматики и управления двигателями.

Для ускорения процесса разработки программного обеспечения Texas Instruments предоставляет бесплатное программное обеспечение StellarisWare®, поддерживающее все контроллеры семейства LM4F.

Основные характеристики LM4F:

Архитектура Stellaris M4F

- ядро ARM Cortex-M4F c модулем обработки операций с плавающей точкой (FPU) с одинарной точностью;

- до 256кБ встроенной Flash памяти и 32кБ ОЗУ;

- 2кБ встроенного EEPROM;

- до двух 12-бит АЦП с 24 входными каналами;

- до двух CAN контроллеров;

- три аналоговых компаратора;

- опционально интерфейс USB 2.0 с поддержкой Device, Host, OTG режимов;

- расширенные функции управления двигателями при помощи использования до 16 ШИМ котроллеров и двух интерфейсов квадратурного энкодера;

- большой выбор последовательных интерфейсов:

- до 8 модулей UART;

- до 6 каналов I2C;

- до 4 каналов SPI / SSI;

- режимы пониженного энергопотребления в том числе «спящий режим»;

- корпуса 64-LQFP, 100-LQFP и 144-LQFP.

Основные преимущества:

- новый 12 бит АЦП с частотой выборки 1Msps позволяет достичь точности +/-1бит во всём диапазоне температур;

- ядро ARM Cortex-M4F со встроенным FPU ускоряет выполнение математических операций и упрощает процесс обработки цифровых сигналов;

- первый микроконтроллер ARM Cortex-M, выполненный в 65нм технологическом процессе, обеспечивает хорошее соотношение между высокой производительностью и малым энергопотреблением, а также низкой ценой;

- время просыпания меньше 500 мкс;

- ток в рабочем режиме менее 370 мкA/МГц;

- ток энергопотребления в ждущем режиме 1.6 мкA;

- цена от 1,5 долларов;

- минимальное количество циклов перезаписи Flash памяти более 100000 циклов;

- широкий диапазон совместимой памяти и вариантов корпусов позволяют сделать оптимальный выбор устройства;

- обширный выбор периферии на кристалле открывает возможности применения в различных приложениях включая 1-D сканеры, микропринтеры, цифровое питание, управление двигателями, управление светодиодным табло, устройства промавтоматики.

Быстрый старт:

Отладочный набор Stellaris LM4F232

Texas Instruments представляет линейку новых отладочных наборов для микроконтроллеров серии LM4F.

Отладочный набор Stellaris® LM4F232 USB+CAN — это компактный и универсальный набор для демонстрации возможностей микроконтроллера Stellaris LM4F232,

Набор позволяет показать доступные в микроконтроллере LM4F232 функции, а именно: контроллер USB 2.0 в режимах OTG/Host/Device, CAN контроллер, аналоговые функции и возможности низкого энергопотребления.

В комплект также входит множество примеров в исходном коде, для быстрого начала программирования в С коде.

Отладочный набор включает в себя следующие компоненты:

- микроконтроллер Stellaris LM4F232H5QD c 256 кБ внутренней Flash памятью в корпусе 144-LQFP;

- 99х64 цветной OLED дисплей, обеспечивающий функции интерфейса;

- разъём USB Micro-AB для макетирования USB применений;

- слот для карт памяти microSD;

- 5-мм винтовые клеммы для подключения внешних датчиков и других аналоговых входов;

- прецизионное опорное напряжение для точного аналогово-цифрового преобразования;

- датчик температуры для измерения температуры;

- 3-осевой акселерометр для детектирования положения;

- контрольные точки для всех линий ввода/вывода, что позволяет легко анализировать сигналы при отладке;

- пять навигационных кнопок для ввода данных пользователем;

- один пользовательский светодиод;

- 10-pin JTAG обеспечивающий стандартный интерфейс для отладки;

- набор кабелей:

- USB Mini-B кабель для отладки;

- USB переходной кабель Micro-A-в-Std-A;

- Кабель USB Micro-B-USB-A;

- USB Flash накопитель;

- литиевую батарею 3В — CR2032;

- СD диск содержащий:

- полную документацию;

- пакет разработчика Stellaris Firmware с примерами исходных кодов;

- приложения для быстрого старта с исходными кодами;

- Windows приложения для быстрого старта;

- ознакомительная версия среды разработки одна из следующего списка:

- EKK-LM4F232 — Keil™ RealView® Microcontroller Development Kit;

- EKI-LM4F232 — IAR Embedded Workbench® development tools;

- EKC-LM4F232 — Sourcery CodeBench development tools;

- EKT-LM4F232 — Code Red Technologies Red Suite;

- EKS-LM4F232 — Texas Instruments Code Composer Studio™ IDE.

В данный момент на складе КОМПЭЛ можно приобрести отладочные наборы на базе CORTEX-M4F. Поставки контроллеров ожидаем в ближайшее время.

•••

Наши информационные каналы

Микроконтроллер Edgeless EAI-серии с двумя ядрами Arm Cortex-M4 оснащен 300 GOPS CNN-NPU

Микроконтроллеры будут играть важную роль в приложениях AIoT (AI + IoT), поскольку они обеспечивают наименьшую стоимость и энергопотребление. Производительность ограничена, но мы уже рассматривали микроконтроллеры с AI-ускорителями, такие как многоядерный микроконтроллер RISC-V GreenWaves GAP9 или микроконтроллер Kendryte K210 RISC-V с KPU AI-ускорителем.

Другой вариант — компания Edgeless Semiconductor Co. Ltd (零 边界 集成电路 有限公司), расположенная в Чжухай, Китай, представила ее микроконтроллер Edgeless EAI-cthbb с двумя ядрами Arm Cortex-M4, оснащенные CNU NPU 300 GOPS.

Микроконтроллеры Edgeless EAI-серии доступны в различных вариантах от 40-контактного QFN до 176-контактного LQFPТехнические характеристики Edgeless EAI:

- CPU — два ядра Arm Cortex-M4F @ до 200 МГц, с инструкциями DSP, I/D-кешем для высокой производительности; 500 DMIPS/1,25 DMIPS/МГц (Dhrystone2.

1)

- AI-ускоритель — CNN-NPU с тактовой частотой до 300 МГц с пиковой пропускной способностью 300 GOPS; 144MAC/цикл, EER до 1 TOPS/W, для сценария распознавания изображений.

- Поддержка основных моделей CNN, включая Resnet-18,

Resnet-34, Vgg16, GoogleNet, Lenet и др. - Поддержка ядра сверточной нейронной сети размером 1 ~ 7

- Поддержка канала/областей до 512

- Поддержка максимальных/средних слоев пула

- Точность арифметики: 16-битная фиксированная точка

- Поддержка основных моделей CNN, включая Resnet-18,

- Память

- До 384 Кб SRAM, 256 Кб для CNN-NPU (разделяется с ЦП)

- До 8 Мб SIP-SDRAM

- Гибкое управление внешней памятью: SRAM, PSRAM,

- Память — 4 Кб OTP для системного BootROM, внешняя SPI NOR/NAND Flash, 1x SD/MMC, передача данных до 25 Мб/с в 8-битном режиме

- Блок вычисления CRC

- Частота, перезагрузка и управление питанием

- 1,7 ~ 3,6 В для питания и ввода/вывода

- POR, PDR, PVD и LVD

- Кварцевый генератор от 4 до 26 МГц

- Внутренний RC 8 МГц (точность 1%)

- PLL — частота PLLKDP 300 МГц; частота PLL 180 ~ 216 МГц; частота PLLSAI 192 МГц; частота PLLI2S 48 МГц

- Внутренний RC 30 кГц для сторожевого таймера или RTC

- 32,768 кГц внешний кристалл для RTC

- Режимы низкой мощности

- Запуск, Сон, Stop 1/2, Ожидание, Выключение

- Резервное снабжение домена VBAT для RTC

- 12-битный 2,4-мегапиксельный SAR-ADC с 16 каналами

- Один модуль аналогового компаратора (ACMP) с

12-разрядный ЦАП уровня 4096 - Выделенный ускоритель 2D-графики

- IMP поддерживает копирование изображений, преобразование формата,

смешивание, масштабирование и определение угла Харриса - VIN, 8–14-битные параллельные интерфейсы камеры, DVP

режим, до 54 Мбайт/с - VOUT с поддержкой многоформатного TFT-LCD видео

выход до разрешения 1024 × 768

- IMP поддерживает копирование изображений, преобразование формата,

- 16-канальный DMA с шлюзами для M2M, P2M,

M2P, P2P транзакция данных с FIFO и пакетной передачей - Модули безопасности

- CRYPTO, алгоритм шифрования/дешифрования данных, AES / 3DES / DES и HASH / HMAC

- TRNG, генератор случайных чисел

- OTP, защищенные данные и код BootROM

- До 18 таймеров

- До 4x 16-битных и 2x 32-битных таймеров до 200 МГц, каждый с 4 IC / OC или счетчиком импульсов и генерацией сигналов ШИМ

- 1x RTC (резервный домен аккумулятора)

- 1x WWDG (сторожевой таймер)

- 1x IWDG (независимый сторожевой таймер)

- 1x таймер SysTick

- Другие периферийные устройства

- До 3-х интерфейсов I2C

- До 8x UART с полнодуплексным обменом данными,

- До 2x SPI, полнодуплексный синхронный и однопроводный двунаправленный режим и 4–16-битные текстовые фреймы

- До 1х интерфейса CAN 2.

0B

0B - 1x USB 2.0 высокоскоростное устройство / хост / OTG контроллер с внешней микросхемой

- 2x SAI (последовательный аудиоинтерфейс) и 4x PDM

- До 161х порта ввода-вывода с возможностью прерывания

- Отладка — последовательная проводная отладка (SWD), Cortex-M4 Trace Macrocell

- Корпуса (QFN, LQFP):

- EAI60 — QFN40 с 2 Мб SDRAM

- EAI68 — QFN40 с 8 Мб SDRAM

- EAI80 — QFN80 с 8 Мб SDRAM

- EAI88 — LQFP128

- EAI90 — LQFP144

- EAI98 — LQFP176

У компании, похоже, нет веб-сайта, но мы нашли таблицу в частной группе Banana Pi в Facebook, так как Banana Pi в настоящее время разрабатывает плату разработки EAI80.

Плата также включает в себя модуль ESP8266 WiFI, 40-контактный интерфейс GPIO, разъемы для ЖК-дисплея и камер, два микрофона, порт USB-C, разъем шины CAN и разъем аккумулятора. Это напоминает нам Maixduino SBC , но кроме того, что последняя основано на RISC-V, оно основано на Arm и имеет модуль ESP8266 вместо модуля с ESP32. Оба подключаются к камере и дисплею и выполняют вывод AI (компьютерное зрение / обработка звука) на слабом оборудовании.

Оба подключаются к камере и дисплею и выполняют вывод AI (компьютерное зрение / обработка звука) на слабом оборудовании.

Это вся информация, которая у нас есть на данный момент, и никаких подробностей о SDK до сих пор не просочилось. Вероятно, пройдет немного больше времени, прежде чем такие SoC и плата станут доступными.

Выражаем свою благодарность источнику из которого взята и переведена статья, сайту cnx-software.com.

Оригинал статьи вы можете прочитать здесь.

ADuCM4050 Техническое описание и информация о продукте

Подробнее о продукте

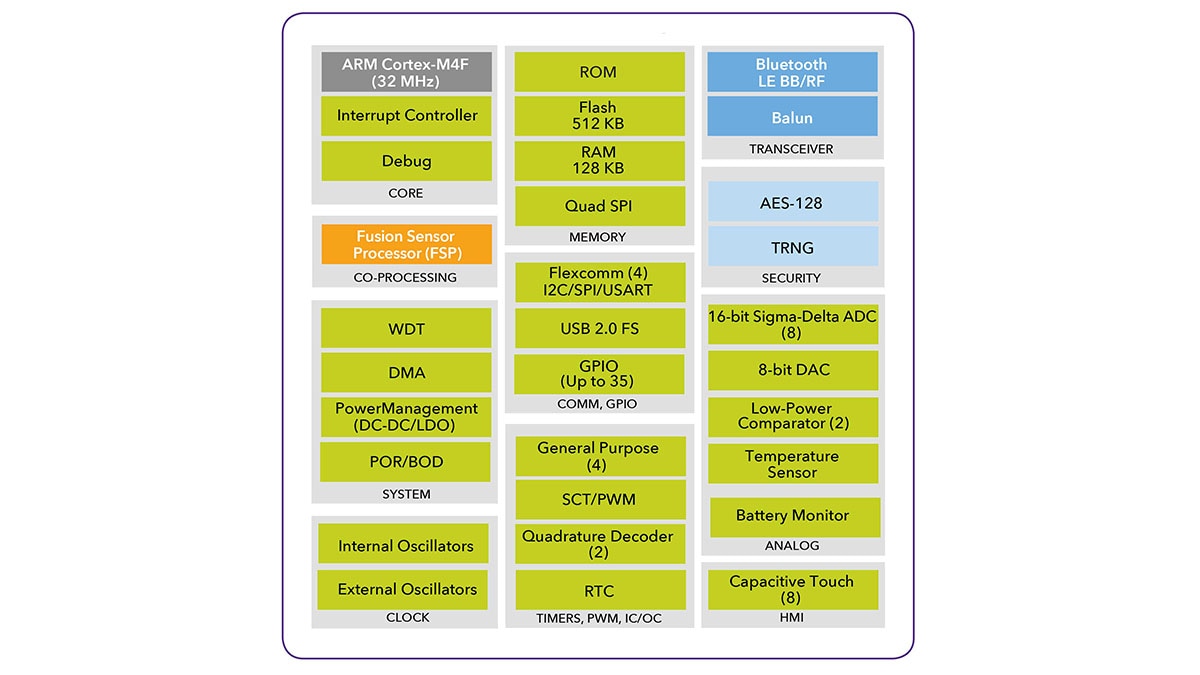

The ADuCM4050 microcontroller unit (MCU) is an ultra low power integrated microcontroller system with integrated power management for processing, control, and connectivity. The MCU system is based on the ARM® Cortex®-M4F processor. The MCU also has a collection of digital peripherals, embedded static random access memory (SRAM) and embedded flash memory, and an analog subsystem that provides clocking, reset, and power management capabilities in addition to an analog-to-digital converter (ADC) subsystem.

This data sheet describes the ARM Cortex-M4F core and memory architecture used on the ADuCM4050 MCU. It does not provide detailed programming information about the ARM processor.

The system features include an up to 52 MHz ARM Cortex-M4F processor, 512 kB of embedded flash memory with error correction code (ECC), an optional 4 kB cache for lower active power, and 128 kB system SRAM with parity. The ADuCM4050 features a power management unit (PMU), multilayer advanced microcontroller bus architecture (AMBA) bus matrix, central direct memory access (DMA) controller, and beeper interface.

The ADuCM4050 features cryptographic hardware supporting advanced encryption standard (AES)-128 and AES-256 with secure hash algorithm (SHA)-256 and the following modes: electronic code book (ECB), cipher block chaining (CBC), counter (CTR), and cipher block chaining-message authentication code (CCM/CCM*) modes.

The ADuCM4050 has protected key storage with key wrap/ unwrap, and keyed hashed message authentication code (HMAC) with key unwrap.

The ADuCM4050 supports serial port (SPORT), serial peripheral interface (SPI), I2C, and universal asynchronous receiver/ transmitter (UART) peripheral interfaces.

The ADuCM4050 features a real-time clock (RTC), general-purpose and watchdog timers, and programmable general-purpose input/output (GPIO) pins. There is a hardware cyclic redundancy check (CRC) calculator with programmable generator polynomial. The device also features a power on reset (POR) and power supply monitor (PSM), a 12-bit successive approximation register (SAR) ADC, a red/green/blue (RGB) timer for driving RGB LED, and a true random number generator (TRNG).

To support low dynamic and hibernate power management, the ADuCM4050 MCU provides a collection of power modes and features such as dynamic- and software-controlled clock gating and power gating.

For full details on the ADuCM4050 MCU, refer to the ADuCM4050 Ultra Low Power ARM Cortex-M4F MCU with Integrated Power Management Hardware Reference.

Product Highlights

- Ultra low power consumption.

- Robust operation.

- Full voltage monitoring in deep sleep modes.

- ECC support on flash.

- Parity error detection on SRAM memory.

- Leading edge security.

- Fast encryption provides read protection to user algorithms.

- Write protection prevents device reprogramming by unauthorized code.

- Failure detection of 32 kHz low frequency external crystal oscillator (LFXTAL) via interrupt.

- SensorStrobe™ for precise time synchronized sampling of external sensors. Works in hibernate mode, resulting in drastic current reduction in system solutions. Current consumption reduces by 10 times when using, for example, the ADXL363 accelerometer. Software intervention is not required after setup. No pulse drift due to software execution.

Applications

- Internet of Things (IoT)

- Smart agriculture, smart building, smart metering, smart city, smart machine, and sensor network

- Wearables

- Fitness and clinical

- Machine learning and neural networks

Микроконтроллеры Cortex-M0/M3/M4

Микроконтроллеры Cortex-M0/M3/M4

Микроконтроллеры Cortex-M стали сегодня одними из самых популярных процессоров, применяемых при разработке и изготовлении электронной техники. Высокая вычислительная мощность, широкий набор периферии и низкая стоимость делают эти устройства привлекательными для самого широкого круга разработчиков. При этом каждый желающий может выбрать наиболее подходящий вариант для решения конкретной задачи. Производители предлагают огромное количество разнообразных микросхем, общим для которых остается только процессорное ядро. На сегодняшний день распространение получили 3 варианта ядер: Cortex-M0, Cortex-M3, Cortex-M4. Отличия этих моделей не всегда явно прослеживаются, поэтому данная статья делает попытку разобраться в особенностях этих вариантов.

Высокая вычислительная мощность, широкий набор периферии и низкая стоимость делают эти устройства привлекательными для самого широкого круга разработчиков. При этом каждый желающий может выбрать наиболее подходящий вариант для решения конкретной задачи. Производители предлагают огромное количество разнообразных микросхем, общим для которых остается только процессорное ядро. На сегодняшний день распространение получили 3 варианта ядер: Cortex-M0, Cortex-M3, Cortex-M4. Отличия этих моделей не всегда явно прослеживаются, поэтому данная статья делает попытку разобраться в особенностях этих вариантов.

Микроконтроллеры Cortex-M представляют собой одно из направлений развития микропроцессорных ядер, предлагаемых фирмой ARM. Фактически, под общей торговой маркой Cortex можно увидеть три типа процессоров (профилей), обозначаемых буквами A, R, M. Задачей профиля A стало достижение большой вычислительной мощности. Изделия с этой маркировкой – Cortex-A, представляют собой классические микропроцессоры, являющиеся дальнейшей эволюцией разработок ARM. Профиль R нацелен на использование во встраиваемых системах, поэтому эти процессоры модернизированы для исполнения задач в реальном времени. Основной задачей профиля M заявлена простота и низкая стоимость. Технически Cortex-M представляют сильно упрощенные варианты старших моделей. Тем не менее, даже такие «урезанные» контроллеры обладают вычислительной мощностью, значительно превышающей многие аналоги. Также отличием от «больших» ARM стала поддержка битовых операций, необходимая в микроконтроллерах для работы с периферией.

Профиль R нацелен на использование во встраиваемых системах, поэтому эти процессоры модернизированы для исполнения задач в реальном времени. Основной задачей профиля M заявлена простота и низкая стоимость. Технически Cortex-M представляют сильно упрощенные варианты старших моделей. Тем не менее, даже такие «урезанные» контроллеры обладают вычислительной мощностью, значительно превышающей многие аналоги. Также отличием от «больших» ARM стала поддержка битовых операций, необходимая в микроконтроллерах для работы с периферией.

Cortex-M0

Микроконтроллеры, использующие ядро Cortex-M0, позиционируются производителями в качестве замены 8-ми разрядных моделей. Их отличительной особенностью стала предельно низкая стоимость и малое энергопотребление, при сохранении многих возможностей архитектуры ARM.

По своей структуре ядро Cortex-M0 – это конфигурируемый мультистадийный 32-разрядный RISC процессор. В его основе лежит архитектура ARMv6-M. Основное отличие от классической «большой» ARMv6 заключается в использовании только набора 16-разрядных инструкций, под общим названием Thumb. Дополнительно поддерживаются некоторые команды более нового набора Thumb2. Такое решение, при незначительном падении вычислительной мощности, максимально упростило процессор относительно старших моделей и позволило использовать дешевую 16-ти разрядную память. Благодаря использованию современных технологий проектирования, количество транзисторов, из которых построено данное ядро, составляет примерно 12 тысяч. Такое количество обеспечило низкое энергопотребление и невысокую стоимость. Для сравнения процессор i8086 имел 32 тысячи транзисторов при намного меньших возможностях. Энергопотребление процессора M0, в зависимости от исполнения и решаемых задач, колеблется от 73 до 4мкВт/МГц.

Дополнительно поддерживаются некоторые команды более нового набора Thumb2. Такое решение, при незначительном падении вычислительной мощности, максимально упростило процессор относительно старших моделей и позволило использовать дешевую 16-ти разрядную память. Благодаря использованию современных технологий проектирования, количество транзисторов, из которых построено данное ядро, составляет примерно 12 тысяч. Такое количество обеспечило низкое энергопотребление и невысокую стоимость. Для сравнения процессор i8086 имел 32 тысячи транзисторов при намного меньших возможностях. Энергопотребление процессора M0, в зависимости от исполнения и решаемых задач, колеблется от 73 до 4мкВт/МГц.

Быстродействие ядра Cortex-M0 составляет 0.84 DMIPS / МГц. Это значит, что на максимальной частоте работы ядра в 50Мгц, достигается производительность 45 DMIPS. Данное значение превышает возможности 8-ми разрядных систем в несколько десятков раз, и на порядок выше, чем у 16-разрядных моделей.

Разработчики, в архитектуре Cortex, попытались получить законченное процессорное ядро. Поэтому в его состав включены: контроллер прерываний на 32 вектора, интерфейс для периферийных устройств в виде 32-разрядной шиной ASB-Lite, отладчик. При необходимости процессор может оснащаться контроллером «спящего» режима.

Поэтому в его состав включены: контроллер прерываний на 32 вектора, интерфейс для периферийных устройств в виде 32-разрядной шиной ASB-Lite, отладчик. При необходимости процессор может оснащаться контроллером «спящего» режима.

Процессорное ядро Cortex-M3

Процессорное ядро Cortex-M3 стало наиболее популярным вариантом архитектуры ARM у производителей и разработчиков микроконтроллеров. Структурно, это также мультистадийный RISC процессор. Но в отличие от M0, данное ядро основано на архитектуре ARMv7-M и полностью реализует наборы команд Thumb и Thumb2. Из особенностей следует упомянуть аппаратное умножение 32-разрядных чисел за 1 цикл, а также деление чисел подобной разрядности (от 2 до 12 циклов). Производительность процессора составляет 1.25DMIPS/МГц. Энергопотребление примерно в два раза выше, чем у варианта M0. Количество физических прерываний увеличено до 240. В ядре предусмотрен механизм защиты памяти.

Cortex-M3, в отличие от классической ARMv7, выполнен по Гарвардской архитектуре и поддерживает несколько периферийных шин. Следует отметить, что ARMv7 является основой только процессоров под обозначением Cortex и имеет мало общего с некогда сверхпопулярной ARM7 и ее вариантами. Хотя именно с ARM7 часто сравнивают возможности Cortex-M3.

Следует отметить, что ARMv7 является основой только процессоров под обозначением Cortex и имеет мало общего с некогда сверхпопулярной ARM7 и ее вариантами. Хотя именно с ARM7 часто сравнивают возможности Cortex-M3.

Cortex-M4

Вариант микроконтроллерного ядра Cortex-M4, по сравнению с Cortex-M3, не характеризуется ростом общих показателей. Фактически M4 тот же самый M3, но дополнительно оснащенный DSP-инструкциями. Наличие последних существенно ускоряет обработку потоковых данных, что в свою очередь делает M4 весьма привлекательным для использования в системах управления и обработки информации.

Возможности DSP, входящего в состав M4, позволяют параллельно выполнять четыре операции сложения/вычитания для 8-ми разрядных чисел или две операции сложения/вычитания с16-ти разрядными операндами. Также реализовано умножение за один цикл, при этом для 16-ти разрядных чисел возможно параллельное исполнение двух операций.

В серии M4 есть еще один вариант, под обозначением Cortex-M4F. В нем, дополнительно к DSP, установлен блок операций для чисел с плавающей точкой – FPU.

В нем, дополнительно к DSP, установлен блок операций для чисел с плавающей точкой – FPU.

Кроме вышеназванных, существуют и другие варианты процессоров. Большинство из них представляют модернизированные варианты основных ядер. Несколько особняком стоит малоизвестный Cortex-M1, предназначенный для использования в программируемых логических матрицах. Основные характеристики этого процессора практически совпадают с вариантом M0, но при этом он реализован только в виде программной модели.

В отличие от профиля А, Cortex-M развивается не столь бурно. Когда и какими будут будущие микроконтроллеры неизвестно. Можно только предположить, что развитие пойдет по пути «больших» систем и в скором времени привычными станут двух-, трех или четырехядерные контроллеры.

You have no rights to post comments

ARM Cortex – M4 вычислительные возможности ( DSP, MAC , FPU , SIMD )

Бинарная совместимость ядер Cortex- M

Сравнение ядер Cortex–M

| Cortex-M0 | Cortex-M3 | Cortex-M4 |

Architecture Version | V6M | v7M | v7ME |

Instruction set architecture | Thumb, Thumb-2 System Instructions | Thumb + Thumb-2 | Thumb + Thumb-2, DSP, SIMD, FP |

DMIPS/MHz | 0.9 | 1.25 | 1.25 |

Bus interfaces | 1 | 3 | 3 |

Integrated NVIC | Yes | Yes | Yes |

Number interrupts | 1-32 + NMI | 1-240 + NMI | 1-240 + NMI |

Interrupt priorities | 4 | 8-256 | 8-256 |

Breakpoints, Watchpoints | 4/2/0, 2/1/0 | 8/4/0, 2/1/0 | 8/4/0, 2/1/0 |

Memory Protection Unit (MPU) | No | Yes (Option) | Yes (Option) |

Integrated trace option (ETM) | No | Yes (Option) | Yes (Option) |

Fault Robust Interface | No | Yes (Option) | No |

Single Cycle Multiply | Yes (Option) | Yes | Yes |

Hardware Divide | No | Yes | Yes |

WIC Support | Yes | Yes | Yes |

Bit banding support | No | Yes | Yes |

Single cycle DSP/SIMD | No | No | Yes |

Floating point hardware | No | No | Yes |

Bus protocol | AHB Lite | AHB Lite, APB | AHB Lite, APB |

CMSIS Support | Yes | Yes | Ye |

3.1. Характеристики ядра Cortex-M4

· Архитектура ARMv7-ME

· Полная совместимость с Cortex–M3

· Модуль MAC (Single-cycle multiply-accumulate)

· Оптимизированные инструкции SIMD (single instruction multiple data )

· Инструкции насыщения (Saturating)

· Модуль Floating–Point Unit одинарной точности (FPU), опционально

· Аппаратное деление (2-12 цикла), также как в Cortex–M3

· Использование DSP инструкций в задачах с 16-бит данными

· Cortex–M4 имеет преимущество от 30% до 70%

· Использование DSP инструкций в задачах с 32-бит данными

· Cortex–M4 имеет преимущество от 25% до 60%

Необходимая частота в МГц для декодирования MP3

· Модуль умножения позволяет выполнить за 1 цикл инструкции MUL или MAC:

o Signed/Unsigned Multiply

o Signed/Unsigned Multiply-Accumulate

o Signed/Unsigned Multiply-Accumulate Long (64-бит)

· Возможности:

o 2 операции 32-бит MAC

o До 7 операции 8-бит MAC

o 4 операции 16-бит MAC (двойной 16-бит MAC)

OPERATION | INSTRUCTIONS | CM3 | CM4 |

16 x 16 = 32 | SMULBB, SMULBT, SMULTB, SMULTT | n/a | 1 |

16 x 16 + 32 = 32 | SMLABB, SMLABT, SMLATB, SMLATT | n/a | 1 |

16 x 16 + 64 = 64 | SMLALBB, SMLALBT, SMLALTB, SMLALTT | n/a | 1 |

16 x 32 = 32 | SMULWB, SMULWT | n/a | 1 |

(16 x 32) + 32 = 32 | SMLAWB, SMLAWT | n/a | 1 |

(16 x 16) ± (16 x 16) = 32 | SMUAD, SMUADX, SMUSD, SMUSDX | n/a | 1 |

(16 x 16) ± (16 x 16) + 32 = 32 | SMLAD, SMLADX, SMLSD, SMLSDX | n/a | 1 |

(16 x 16) ± (16 x 16) + 64 = 64 | SMLALD, SMLALDX, SMLSLD, SMLSLDX | n/a | 1 |

32 x 32 = 32 | MUL | 1 | 1 |

32 ± (32 x 32) = 32 | MLA, MLS | 2 | 1 |

32 x 32 = 64 | SMULL, UMULL | 5-7 | 1 |

(32 x 32) + 64 = 64 | SMLAL, UMLAL | 5-7 | 1 |

(32 x 32) + 32 + 32 = 64 | UMAAL | n/a | 1 |

32 ± (32 x 32) = 32 (upper) | SMMLA, SMMLAR, SMMLS, SMMLSR | n/a | 1 |

(32 x 32) = 32 (upper) | SMMUL, SMMULR | n/a | 1 |

Все вышеперечисленный операции выполняются за 1 цикл на Cortex–M4

· Предотвращение переполнения переменных отсечением мин/макс границ и снижение нагрузки на ядро

· Пример

o Аудио-приложения

· Single Instruction Multiple Data

· Оперирование пакетированными данными (packed data)

· Параллельная работа с несколькими операндами 8-бит или 16-бит данных

o двойной 16-бит MAC (Результат = 16 x 16 + 16 x 16 + 32)

· Преимущества

o Параллельность операций

o Минимизация количества инструкций загрузки/хранения для обмена между памятью и банком регистров, 2 или 4 транзакции данных за 1 цикл, если нет необходимости в 32-бит данных

· Байт или 2 байта пакетируются в слова

· Более эффективный доступ к структурам данных

· Использование SIMD-инструкций

· Инструкции капсуляции и инкапсуляции данных

· DSP библиотека для Cortex-M4

o Быстрое освоение

o Абстракция от низкоуровневого программирования

· Анализ конкурентных режимов при одинаковых условиях

· Ускорение использования наработок сторонних производителей

· Простота использования для полшьзователя

o Минимальный барьер – простота освоения и использования

· Одна стандартная библиотека – во всех проектах

o ARValueM библиотека DSP + ваше приложение

o Использование совместно с другими средствами проектирования – матлаб и т.д.

· Базовая математика – векторная математика

· Быстрые тригоном. функции sin, cos, sqrt и т.д.

· Интерполяция – линейная, билинейная

· Комплексная математика

· Статистика – макс, мин, и т.д.

· Фильтрация – IIR, FIR, LMS и т.д.

· Преобразования – БПФ и т.д.

· Функции для работы с матрицами

· ПИД – контроллер

· Поддержка функций – копия/заполнение массивов, конвертирование типов данных

· Matlab / Simulink

o Генрация готового кода

o Mathworks

o В разработке (возможно в конце года)

o Aimagin (Rapidstm32)

· Дизайн фильтров

o Очень много продуктов, большинство платные:

o http://www.dspguru.com/dsp/links/digital-filter-design-software

FPU : Floating Point Unit

Стандартизирован IEEE.754-2008

o Количество форматов

o Арифметические операции

o Количество преобразований

o Определение значений

o режима округления

o исключений

ARM Cortex-M FPU ISA

· Поддержка

o Add, subtract, multiply, divide

o Умножение и аккумулирование Вычисление квадратного корня

Сравнение времени выполнения КИХ – фильтра по 29 коэффициентам(32 бита) с и без FPU (Библиотека CMSIS)

Cortex M1 и Cortex M3 в открытом доступе.

Приветствую тебя!

Мир встраиваемых систем потрясла новость о том, что компания ARM совместно с компанией Xilinx подготовили платформу и выкинули в открытый доступ исходники ядра Cortex M1 и Cortex M3, правда они зашифрованные, но это не страшно, т.к. того что есть, уже достаточно для работы, и потому уже смело можно поменять MicroBlaze софт ядра на ARM Cortex M3 или ARM Cortex M1. Возможно компания пошла на такой замечательный шаг и за боязни конкуренции со стороны RISC-V, т.к. это архитектура процессора набирает очень большую популярность и количество участников, которые поддерживает уже данную архитектуру велико, на самом деле лично меня сильно потрясает сколько там участников, список участников.

Заходим по этой ссылке, проходим регистрацию и преступаем к работе над проектами.

Так же компания ARM подготовила видео уроки по работе с данными исходниками, проекты открываются с помощью Xilinx Vivado 2018.2 (либо более старшей версии).

И на последок ARM действительно боится конкуренции со стороны RISC-V, был сделан сайт arm-basics.com, где ARM сопоставляется RISC-V, правда этот сайт был закрыт 15 июля 2018 года 23:59:59, по лондонскому времени, но добрые люди сохранили это в истории здесь.

Corstone-101 – Arm Developer

Комплект для проектирования системы Cortex-M

Комплект для проектирования системы Cortex-M (CMSDK) включает:

- Набор компонентов инфраструктуры AMBA AHB и APB

- Основные периферийные устройства, такие как GPIO, таймеры, сторожевой таймер и UART

- Примеры систем для процессоров Cortex-M0, Cortex-M0 +, Cortex-M3 и Cortex-M4

- Скрипты компиляции и моделирования для среды Verilog

- Программные драйверы и примеры программ

Комплект для проектирования системы Cortex-M Пример системы

CMSDK предоставляет примеры систем AMBA, чтобы как можно быстрее довести разработчика до работающей системы, предлагая библиотеку основных периферийных устройств и создание соединений с помощью программных драйверов и примеров.

Примеры систем CMSDK значительно отличаются от подсистем Arm. Например, подсистема SSE-050 разработана для архитектуры Arm, предварительно интегрирована и полностью проверена. SSE-050 используется в качестве основы IoT SoC с процессором Cortex-M3.

Примеры систем CMSDK, однако, предназначены для использования двумя способами:

- В качестве учебного пособия для понимания того, как интегрировать компоненты CMSDK с процессорами Armv6-M и Armv7-M.

- Для использования в качестве тестовой среды (готовой к использованию), чтобы показать, что каждый компонент CMSDK работает и ведет себя должным образом в соответствии с конфигурацией каждого модуля.Система примеров не предназначена для использования в качестве испытательного стенда для верификации.

Пример системы для Cortex-M0 и Cortex-M0 + показан на следующей диаграмме:

Система в качестве примера поддерживает множество параметров конфигурации, например:

- DMA option – если контроллер DMA Arm CoreLink DMA-230 лицензирован, вы можете подключить контроллер DMA и сразу же использовать его в системе. Вы также можете изменить дизайн, чтобы использовать собственный контроллер DMA.

- Обертка битовой полосы – если системе требуется совместимость битовой полосы с Cortex-M3 или Cortex-M4, эта функция может быть включена.

- Boot ROM – этот вариант демонстрирует, как спроектировать систему с ROM загрузчика в дополнение к памяти пользовательских программ, например, Flash.

Расширение примера системы и подключение других периферийных устройств несложно. Для дизайнеров, плохо знакомых с AMBA, примеры подчиненных устройств AHB и APB являются хорошей отправной точкой для вашего дизайна.

Также включен пример системы для процессоров Cortex-M3 и Cortex-M4, как показано на следующей диаграмме:

Система Cortex-M3 или Cortex-M4 имеет ту же карту памяти и назначения прерываний, что и системы Cortex-M0 и M0 +. Он также использует ту же подсистему AMBA APB, что и пример Cortex-M0 и Cortex-M0 +. Опять же, интеграция контроллера DMA и загрузчика не является обязательной.

Компоненты CMSDK

Комплект для проектирования системы Cortex-M состоит из следующих компонентов:

| Компоненты APB | Компоненты Advanced AHB-Lite | Модели памяти | Проверочные компоненты |

| Пример подчиненного устройства APB | Матрица шины AHB | Обертка модели ROM | Устройство проверки протокола AHB-Lite |

| Таймер APB | ИБП AHB | Обертка модели RAM | Устройство проверки протокола APB |

| APB UART | Устройство понижения массы AHB | Поведенческая модель SRAM с интерфейсом AHB | Мастер шины чтения файлов AHB (FRBM) |

| Двойной таймер APB | Асинхронный мост от AHB к APB | Модель поведения 32-битной флэш-памяти | |

| Сторожевой таймер APB | Асинхронный мост от AHB к AHB и APB | Модель поведения 16-битной флэш-памяти | |

| Подчиненный мультиплексор APB | Синхронный мост от AHB к AHB | SRAM синтезируемая (для FPGA) модель | |

| Подсистема APB | AHB к мосту синхронизации AHB | ПЗУ ПЛИС | |

| Монитор тайм-аута APB | AHB к мосту синхронизации AHB | Внешняя асинхронная 8-битная SRAM | |

| Внешняя асинхронная 16-битная SRAM |

| Вт FLASH | Состояния ожидания ЦП, работа из флэш-памяти, кэш отключен | 0 | 2 | ||||||

| Вт ФЛЭШ-КАСС | Состояния ожидания ЦП, запуск из флэш-памяти, кэш включен | 0 | 3 | ||||||

| Вт RAM | Состояния ожидания ЦП, запущенные из ОЗУ | 0 | |||||||

| Я DDFLASHCACHE | Ток ЦП, запуск из флэш-памяти, кэш включен, LDO | 7.4 | мА | ||||||

| Я DDFLASHCACHEDCDC | Ток ЦП, запуск из флэш-памяти, кэш включен, DCDC 3V | 3.7 | мА | ||||||

| Я DDFLASH | Ток ЦП, запуск из флэш-памяти, кэш отключен, LDO | 8.0 | мА | ||||||

| Я DDFLASHDCDC | Ток ЦП, запуск из флэш-памяти, кэш отключен, DCDC 3V | 3.9 | мА | ||||||

| Я DDRAM | Ток ЦП, работа из ОЗУ, LDO | 6.7 | мА | ||||||

| Я DDRAMDCDC | Ток ЦП, работающий от ОЗУ, DCDC 3V | 3.3 | мА | ||||||

| I DDFLASH / МГц | Эффективность ЦП, работа с флэш-памяти, кеш-память включена, LDO | 125 | мкА / МГц | ||||||

| I DDFLASHDCDC / МГц | Эффективность ЦП, работа с флэш-памяти, кеш-память включена, DCDC 3V | 58 | мкА / МГц | ||||||

| CM FLASH | CoreMark 1 , работает с флэш-памяти, кэш включен | 215 | CoreMark | ||||||

| CM FLASH / МГц | CoreMark на МГц, работа с флэш-памятью, кеш-память включена | 3.36 | CoreMark / МГц | ||||||

| CM FLASH / mA | CoreMark на мА, запуск из флэш-памяти, кэш включен, DCDC 3 В | 58 | CoreMark / мА |

ARM микроконтроллер, ARM Cortex-M4F микроконтроллеры, 32 бит, 120 МГц, 512 КБ, 192 КБ, 64 контакта: Amazon.com: Industrial & Scientific

- Убедитесь, что это подходит введя номер вашей модели.

- Цена для: Каждая линейка продуктов: Микроконтроллеры ARM Cortex-M4F Количество бит: 32 бит Скорость процессора: 120 МГц Размер памяти программы: 512 КБ Размер памяти ОЗУ: 192 КБ Количество контактов: 64 контакта Стиль корпуса MCU: QFN Количество входов / выходов: Архитектура ввода-вывода 51: ARM Cortex-M4F Тип встроенного интерфейса: CAN, I2S, QSPI, USB Мин. Напряжение питания: 1,7 В Макс. Напряжение питания: 3,6 В Упаковка: Каждый

Характеристики

| Фирменное наименование | МИКРОЧИП |

|---|---|

| Номер модели | ATSAME51J19A-MU |

| Кол-во позиций | 1 |

| Номер детали | ATSAME51J19A-MU |

| Код КПСС ООН | 32100000 |

rust-embedded / cortex-m-quickstart: шаблон для разработки приложений с нуля для микроконтроллеров Cortex-M

Шаблон для сборки приложений для микроконтроллеров ARM Cortex-M

Этот проект разработан и поддерживается командой Cortex-M.

Зависимости

Для создания встроенных программ с использованием этого шаблона вам потребуется:

Rust 1.31, 1.30-beta, nightly-2018-09-13 или более новый набор инструментов. например

rustup по умолчанию бетаCargo

создает подкоманду. Монтаж инструкции.- Компоненты

rust-std(предварительно скомпилированный крейт ядра

$ rustup target добавить thumbv6m-none-eabi thumbv7m-none-eabi thumbv7em-none-eabi thumbv7em-none-eabihf

Использование этого шаблона

ПРИМЕЧАНИЕ : Это очень короткая версия, которая охватывает только программы сборки.Для длинная версия, которая дополнительно охватывает перепрошивку, запуск и отладку программы, проверьте встроенную книгу Rust.

- Прежде чем мы начнем, вам необходимо определить некоторые характеристики цели. устройство, поскольку они будут использоваться для настройки проекта:

Ядро ARM. например Cortex-M3.

Включает ли ядро ARM FPU? Ядра Cortex-M4 F и Cortex-M7 F подходят.

Сколько флэш-памяти и оперативной памяти у целевого устройства? е.грамм. 256 Кбайт из Флэш-память и 32 КБ ОЗУ.

Где в адресном пространстве отображаются флэш-память и оперативная память? например Оперативная память обычно находится по адресу

0x2000_0000.

Вы можете найти эту информацию в техническом паспорте или справочном руководстве вашего устройство.

В этом примере мы будем использовать STM32F3DISCOVERY. Эта доска содержит Микроконтроллер STM32F303VCT6. У этого микроконтроллера:

Ядро Cortex-M4F, которое включает FPU одинарной точности

256 КБ флэш-памяти, расположенной по адресу 0x0800_0000.

40 КиБ оперативной памяти, расположенной по адресу 0x2000_0000. (Есть еще одна область ОЗУ, но для простоты мы его проигнорируем).

- Создайте экземпляр шаблона.

$ Cargo сгенерировать --git https://github.com/rust-embedded/cortex-m-quickstart Название проекта: приложение Создание проекта под названием `app` ... Сделанный! Создан новый проект / tmp / app $ cd app

- Установить цель компиляции по умолчанию. Есть четыре варианта, как указано в

низ

.груз / конфиг. Для STM32F303VCT6 с Cortex-M4F core, мы выберем цельthumbv7em-none-eabihf.

[сборка] # Выберите ОДНУ из этих целей компиляции # target = "thumbv6m-none-eabi" # Cortex-M0 и Cortex-M0 + # target = "thumbv7m-none-eabi" # Cortex-M3 # target = "thumbv7em-none-eabi" # Cortex-M4 и Cortex-M7 (без FPU) target = "thumbv7em-none-eabihf" # Cortex-M4F и Cortex-M7F (с FPU)

- Введите информацию об области памяти в память

.xфайл.

$ cat memory.x

/ * Скрипт компоновщика для STM32F303VCT6 * /

ОБЪЕМ ПАМЯТИ

{

/ * ПРИМЕЧАНИЕ 1 K = 1 KiBi = 1024 байта * /

ВСПЫШКА: ПРОИСХОЖДЕНИЕ = 0x08000000, ДЛИНА = 256 КБ

RAM: ORIGIN = 0x20000000, LENGTH = 40K

} - Создайте шаблон приложения или один из примеров.

VS Код

Этот шаблон включает конфигурации запуска для отладки программ CortexM с кодом Visual Studio, расположенным в каталоге .vscode / .

См.vscode / README.md для получения дополнительной информации.

Если вы не используете VS Code, вы можете безопасно удалить каталог из сгенерированного проекта.

Этот шаблон находится под лицензией

на ваше усмотрение.

Вклад

Если вы явно не укажете иное, любой вклад, преднамеренно представленный для включения в вашу работу, как определено в лицензии Apache-2.0, должен быть двойная лицензия, как указано выше, без каких-либо дополнительных условий.

Кодекс поведения

Вклад в этот ящик организован в соответствии с положениями Кодекса ржавчины Conduct, разработчик этого ящика, команда Cortex-M, обещает вмешиваться и соблюдать этот кодекс поведения.

Cortex-M4F нацелен на подключенные встроенные приложения

Новая линейка Tiva от Texas Instruments (TI) основана на Arm Cortex-M4F. Он включает в себя ряд периферийных устройств управления и связи. Микроконтроллеры Tiva C Series TM4C123x ранее были известны как микроконтроллеры Stellaris® LM4F (см. Cortex-M4 Sips Power с плавающей точкой). Новые чипы начинаются с 2,15 доллара и идеально подходят для автоматизации зданий и промышленных предприятий, где часто используются CAN и управление двигателем. Он также может подключаться к ряду беспроводных интерфейсов от Wi-Fi до Zigbee с помощью внешних трансиверов.

Tiva C 80 МГц основана на 65-нм технологии Texas Instrument (рис. 1) . Он включает в себя блок с плавающей запятой и интеллектуальную подсистему ШИМ, которая может легко справиться с большинством рутинных операций по управлению двигателем. Система включает 256 Кбайт флеш-памяти и 2K EEPROM с аппаратным выравниванием износа. Существует также ПЗУ с поддержкой загрузчика, а также TivaWare (формально StellarisWare) с поддержкой драйверов, а также полезные элементы, такие как таблицы AES для ускорения шифрования.

% {[data-embed-type = “image” data-embed-id = “5df275e6f6d5f267ee20c40d” data-embed-element = “aside” data-embed-align = “left” data-embed-alt = “Electronicdesign Com Sites Electronicdesign com Загрузка файлов 2013 04 63491 Fig1sm “data-embed-src =” https://img.electronicdesign.com/files/base/ebm/electronicdesign/image/2013/04/electronicdesign_com_sites_electronicdesign.com_files_uploads_2013_04_63491__fig1 = 1440 “data-embed-caption =” “]}% Рисунок 1.Tiva C 80 МГц основана на архитектуре Arm Cortex-M4F. Он поставляется с TivaWare в ПЗУ, включая поддержку загрузчика.На аналоговой стороне Tiva C имеет пару 12-битных АЦП, которые работают со скоростью 1 млн отсчетов в секунду. Есть 3 аналоговых компаратора и встроенный датчик температуры. Также имеется встроенный стабилизатор напряжения LDO.

Система имеет два сторожевых таймера для приложений с высокой надежностью. DMA имеет 32 канала, позволяя процессору выполнять рутинную работу, отличную от управления периферией.

На стороне подключения есть 2 интерфейса CAN, 6 последовательных портов, 6 портов I , 2 порта C, 4 порта SSI / SPI и полноскоростной USB со встроенными физическими уровнями. Чип поддерживает до 40 выходов ШИМ. Из них 16 поступают от контроллера ШИМ с генератором зоны нечувствительности, есть еще 24 выхода ШИМ от таймеров, которые также имеют поддержку CCP (сравнение захвата). Также есть два квадратурных энкодера.

Чип может потреблять всего 1,6 мкА. Период пробуждения составляет 500 мкс.

Чип поддерживается широким спектром программных средств TI и сторонних производителей. Это включает в себя Code Composer Studio на основе Eclipse от TI. Он также поддерживает TI-RTOS (см. Новые сборки RTOS на основе корней DSP), облегченную RTOS. TivaWare на основе ПЗУ работает с TI-RTOS, операционными системами сторонних производителей, а также с базовыми системами. Пакетная поддержка позволяет разработчикам быстро приступить к работе менее чем за 10 минут.

ARM Cortex-M4 | Hackaday

Бейджис каждым годом становятся все сложнее.DEFCON, LayerONE, Shmoocon, The Next Hope, Open Hardware Summit, EMF, SAINTCON, SXSW Create, The Last Hope, TROOPERS11, ZaCon V и, конечно же, CCC, на протяжении многих лет имели отличные значки. В этом году значок CCCamp 2015 rad1o поднимает вещи на несколько ступеней выше. Мероприятие продлится с 13 по 17 августа 2015 года.

Значок rad1o содержит полнофункциональный приемопередатчик SDR (программно определяемое радио), работающий в диапазоне частот около 50 МГц – 4000 МГц , и программно совместим с платформой SDR с открытым исходным кодом HackRF One.Значок использует приемопередатчик Wimax, который отправляет образцы I / Q (синфазный / квардратурный) в диапазоне от 2,3 до 2,7 ГГц на процессор ARM Cortex M4. ЦП может обрабатывать данные автономно для различных приложений, таких как FM-радио, отображение спектрограмм, РЧ-управляемые розетки и т. Д., Или передавать образцы в компьютер с помощью USB 2.0, где может принимать участие дальнейшая обработка сигналов, например используя GnuRadio. Частотный диапазон можно расширить, вставив в тракт ВЧ смеситель. У него есть бортовая антенна, настроенная на двоих.5 ГГц, или можно припаять разъем SMA для подключения внешней антенны. Есть ЖК-экран Nokia 6100 130 × 130 пикселей и джойстик, который также использовался на более раннем значке CCCamp 2011, известном как r0ket.

Аудиоразъем TRRS 3,5 мм позволяет легко подключить наушники и динамик. Батарею LiPo можно заряжать через один из портов USB, а другой порт USB можно использовать для обновлений программного обеспечения и ввода-вывода данных в программное обеспечение SDR, такое как GnuRadio. Ознакомьтесь с деталями проекта в их репозитории Github и прочтите подробную информацию о программном и аппаратном обеспечении в вики.Также есть аккаунт в Твиттере, если вы хотите следить за ходом проекта.

В этом году Open Hardware Summit также обещает отличный значок, который можно взломать. Вероятно, мы представим его перед сентябрьской конференцией OHS2015.

Спасибо [Andz] за то, что сообщил нам об этом замечательном значке.

Будьте осторожны: операции с плавающей запятой в ARM Cortex-M4F

Моя мантра – * не * использовать какие-либо типы данных с плавающей запятой во встроенных приложениях или, по крайней мере, избегать их, когда это возможно: для большинства приложений они не нужны и могут быть заменены операциями с фиксированной точкой.Не только операции с плавающей запятой имеют числовые проблемы, но они также могут привести к проблемам с производительностью, как в следующем (упрощенном) примере:

#define NOF 64

статические образцы uint32_t [NOF];

статический поплавок Fsamples [NOF];

float fZeroCurrent = 8.0;

static void ProcessSamples (void) {

int i;

for (i = 0; i & lt; NOF; i ++) {

Fsamples [i] = samples [i] * 3.3 / 4096.0 - fZeroCurrent;

}

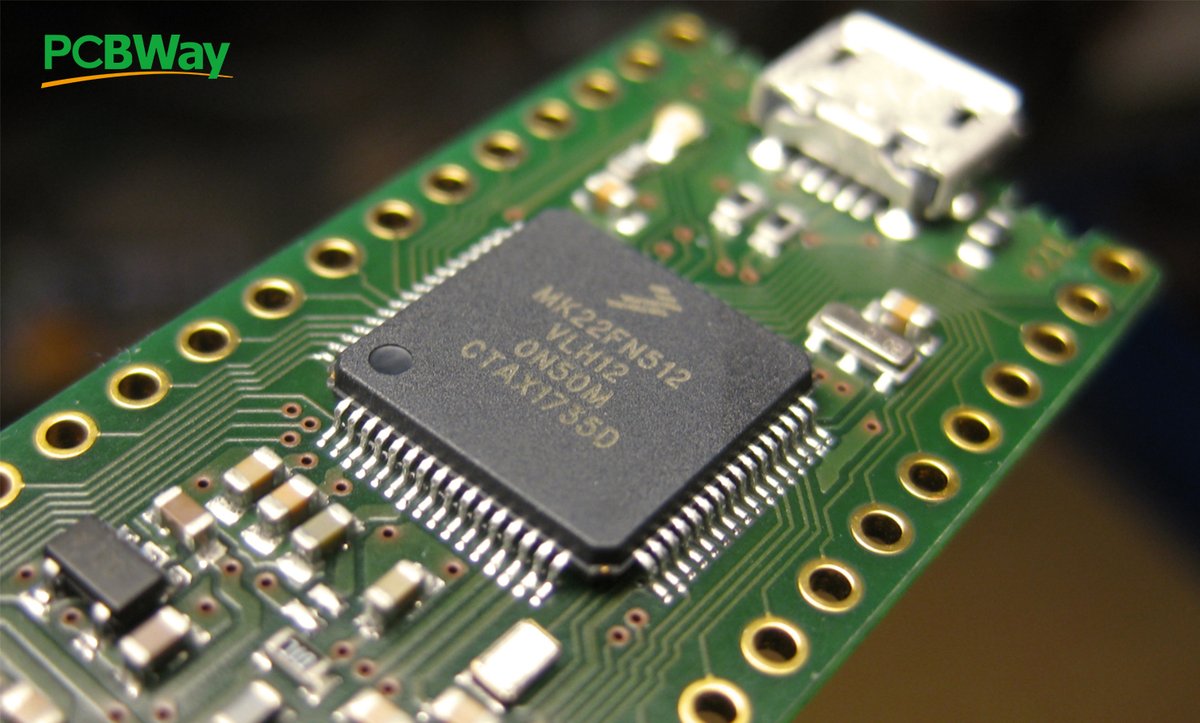

} ARM разработала архитектуру Cortex-M4 таким образом, чтобы можно было добавить FPU.Например, NXP ARM Cortex-M4 на плате FRDM-K64F имеет FPU.

MK64FN1M0VLL12 на FRDM-K64F

Вопрос: сколько времени потребуется этой функции для выполнения операций?

Глядя на петлю, она показывает:

Fsamples [i] = samples [i] * 3.3 / 4096.0 - fZeroCurrent; Который должен загрузить 32-битное значение, затем выполнить умножение с плавающей запятой, за которым следует деление с плавающей запятой и вычитание с плавающей запятой, а затем сохранить результат обратно в массив результатов.

NXP MCUXpresso IDE имеет интересную функцию, показывающую количество затраченных циклов ЦП (см. Измерение затраченных циклов ЦП ARM Cortex-M с помощью представления регистров MCUXpresso Eclipse). Итак, запуск этой функции (без каких-либо специальных настроек оптимизации в компиляторе занимает:

Дельта цикла

0x4b9d или 19’357 циклов ЦП для всего цикла. Измерение только одной итерации цикла занимает 0x12f или 303 цикла, может возникнуть вопрос, почему это занимает так много времени, если у нас есть FPU?

Ответ находится в коде сборки:

Это на самом деле показывает, что он не использует FPU, а вместо этого использует программные операции с плавающей запятой из стандартной библиотеки?

Ответ заключается в том, как операция написана на C:

Fsamples [i] = samples [i] * 3.3 / 4096.0 - fZeroCurrent; У нас есть uint32_t, умноженный на число с плавающей запятой:

образцов [i] * 3,3 Дело в том, что константа «3.3» в C имеет тип * double *. Таким образом, операция сначала преобразует uint32_t в double, а затем выполнит умножение как операцию double.

То же для деления и вычитания: выполняется как двойная операция:

образцов [i] * 3,3 / 4096,0 То же самое для вычитания с переменной с плавающей запятой: поскольку результат левой операции двойной, он должен выполняться как двойная операция.

образцов [i] * 3.3 / 4096.0 - fZeroCurrent Наконец, результат преобразуется из числа с двойной точностью в число с плавающей запятой, чтобы сохранить его в массиве:

Fsamples [i] = samples [i] * 3.3 / 4096.0 - fZeroCurrent; Теперь вызываемые библиотечные подпрограммы должны быть ясны в приведенном выше коде сборки:

- __aeabi_ui2d : преобразовать unsigned int в double

- __aeabi_dmul : двойное умножение

- __aeabi_ddiv : двойное деление

- __aeabi_f2d : преобразование с плавающей точкой в двойное

- __aeabi_dsub : двойное вычитание

- __aeabi_d2f : преобразование двойного числа в число с плавающей запятой

Но почему это делается программно, а не аппаратно, как у нас FPU?

Ответ заключается в том, что ARM Cortex-M4F имеет только FPU * одинарной точности * (float), а не FPU двойной точности (double).Таким образом, он может выполнять только операции с плавающей запятой аппаратно, но не для типа double.

Решение в этом случае – использовать константы типа float (а не double). В языке C суффикс «f» может использоваться для обозначения констант как float:

. Fsamples [i] = samples [i] * 3.3f / 4096.0f - fZeroCurrent; При этом код меняется на:

Использование инструкций FPU одинарной точности

Итак, теперь он использует инструкции одинарной точности FPU.Это займет всего 0x30 (48) циклов для одной итерации или 0xc5a (3162) для всего: в 6 раз быстрее.

Пример можно дополнительно оптимизировать с помощью:

Fsamples [i] = samples [i] * (3.3f / 4096.0f) - fZeroCurrent; Другие соображения

Использование float или double само по себе неплохо: все зависит от того, как они используются и действительно ли они необходимы. Использование арифметики с фиксированной точкой сопряжено с проблемами, а стандартные функции sin / cos используют double, поэтому вам не захочется заново изобретать колесо.

ЦЕННОСТИ

Один из способов использования типа поплавка, скажем, для значения температуры:

температура поплавка; / * например, -37,512 * / Вместо этого было бы лучше использовать целочисленную переменную типа «санти-температура» или «милли»:

int32_t centiTemperature; / * -37512 соответствует -37,512 * / Таким образом, можно использовать обычные целочисленные операции.

GCC ЕДИНАЯ ПОСТОЯННАЯ ТОЧНОСТЬ

Компилятор GNU GCC предлагает рассматривать двойные константы как 3.0 как константы одинарной точности (3.0f), используя следующую опцию:

-fsingle-precision-constant вызывает загрузку констант с плавающей запятой с одинарной точностью, даже если это неточно. Это позволяет избежать преобразования операций с переменными одинарной точности в двойную точность, как в x + 1.0 / 3.0. Обратите внимание, что здесь также используются константы одинарной точности в операциях с переменными двойной точности. Это может улучшить производительность за счет меньшего трафика памяти.

См. Https: // gcc.gnu.org/wiki/FloatingPointMath

ОСРВ

Другое соображение: при использовании FPU это означает потенциально большее количество регистров. Это возможная проблема производительности для ОСРВ, такой как FreeRTOS (см. Https://www.freertos.org/Using-FreeRTOS-on-Cortex-A-Embedded-Processors.html). ARM Cortex-M4 поддерживает «кружевное стекирование» (см. Https://stackoverflow.com/questions/38614776/cortex-m4f-lazy-fpu-stacking). Таким образом, если используется FPU, это означает больше регистров с накоплением. Если FPU не используется, то в FreeRTOS лучше выбрать порт M4:

M4 и M4F в FreeRTOS

Резюме

Я рекомендую не использовать типы данных float и double, если в этом нет необходимости.И если у вас есть FPU, обратите внимание, если это только FPU одинарной точности, или если оборудование поддерживает FPU как одинарной, так и двойной точности. Если у вас есть только FPU одинарной точности, использование суффикса «f» для констант и приведение вещей к (float) может иметь большое значение. Но имейте в виду, что float и double имеют разную точность, поэтому это может не решить все проблемы.

Счастливого плавания!

PS: Если вам нужен FPU с двойной точностью, обратите внимание на ARM Cortex-M7 (e.грамм. Первые шаги: ARM Cortex-M7 и FreeRTOS на NXP TWR-KV58F220M или Первые шаги с платой NXP i.MX RT1064-EVK)

0

0

0 / CAN-FD 1.0

0 / CAN-FD 1.0