Что хорошего в CMOS?

Оли и Олин объяснили сильные стороны CMOS, но позвольте мне сделать шаг назад.

TL: DR: дополнительная логика допускает колебание выходного напряжения от шины к шине, а транзисторы MOSFET являются очень масштабируемой технологией (миллиарды транзисторов могут быть получены на небольшой поверхности) с некоторыми очень полезными свойствами (по сравнению с BJT).

Почему CMOS?

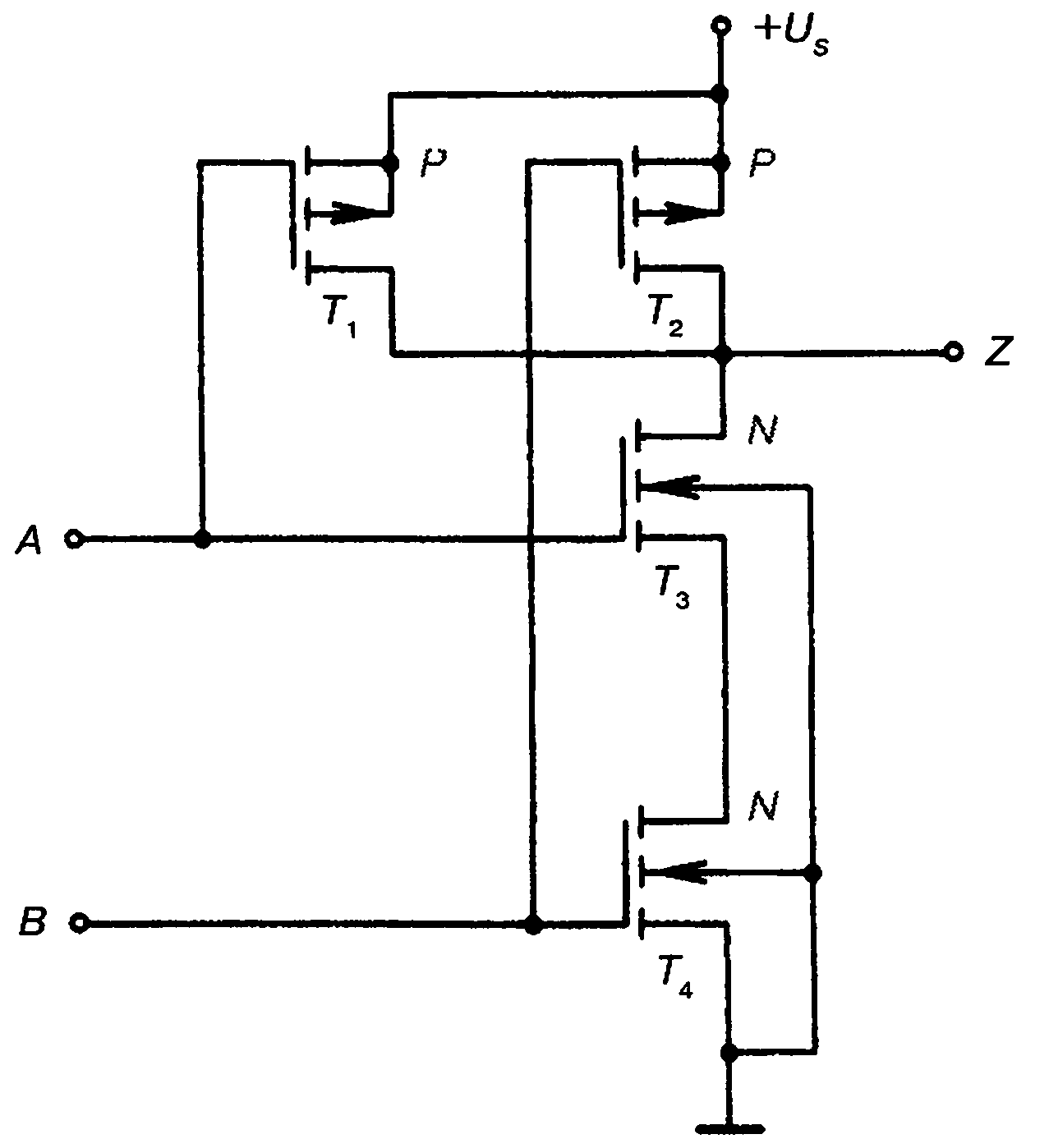

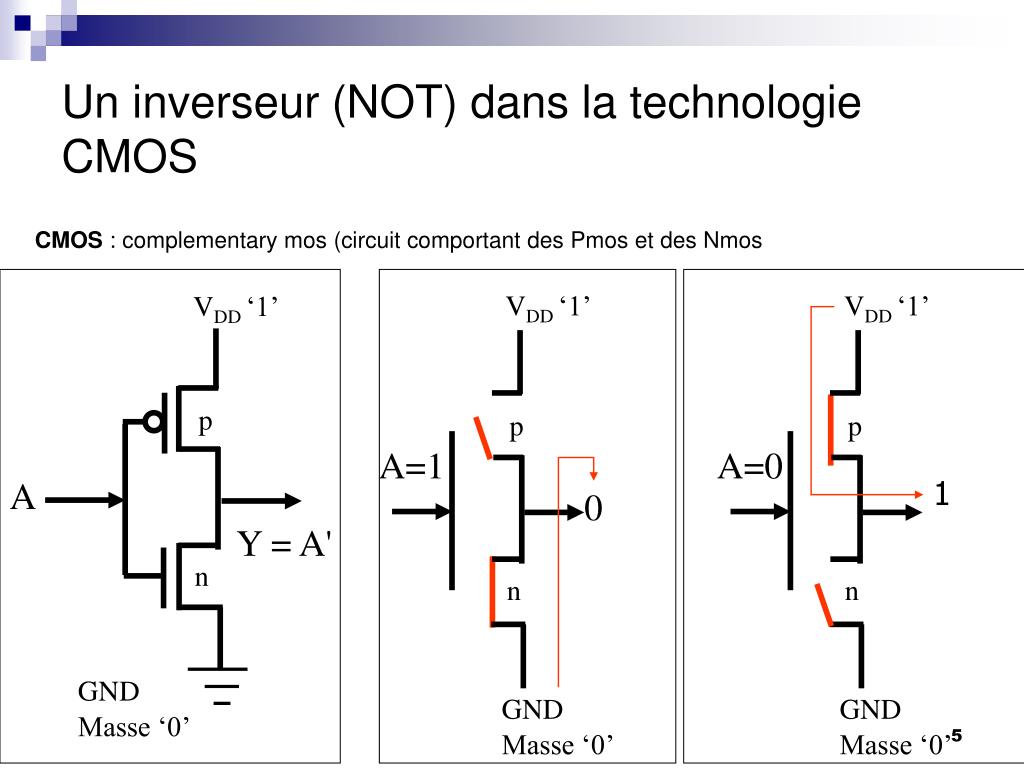

Потребность в дополнительных воротах обусловлена тем фактом, что простейшая концепция ворот основана на идее подтягивания и опускания; это означает, что есть устройство (транзистор или набор транзисторов), которое повышает выходной сигнал (до «1»), и другое устройство, которое понижает его (до «0»).

ВG S> VT> 0,7 ВВгS>ВT>0.7В

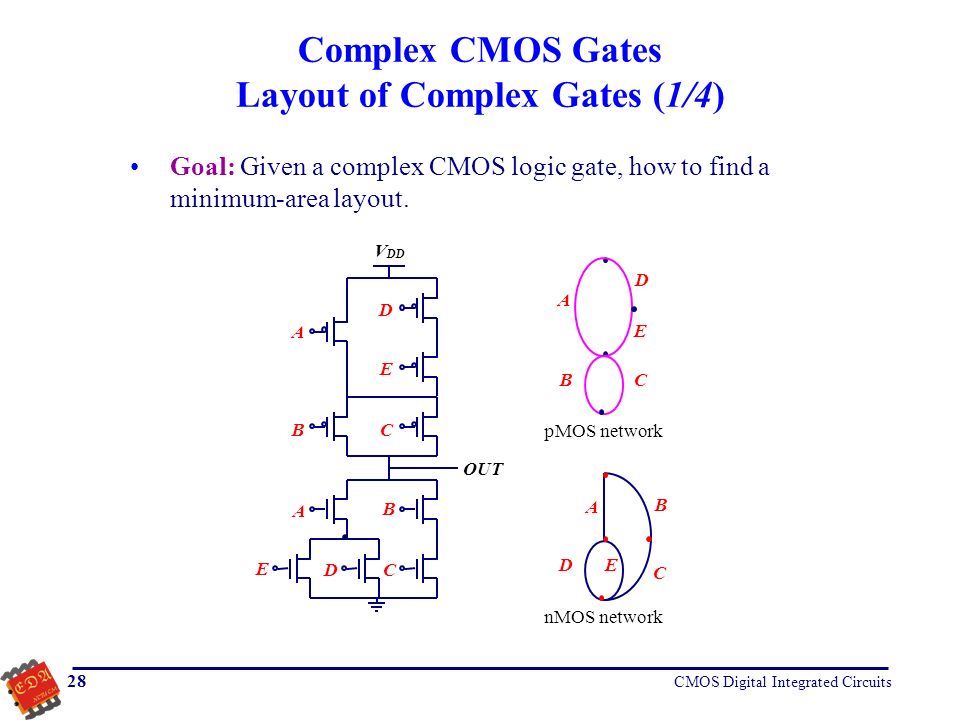

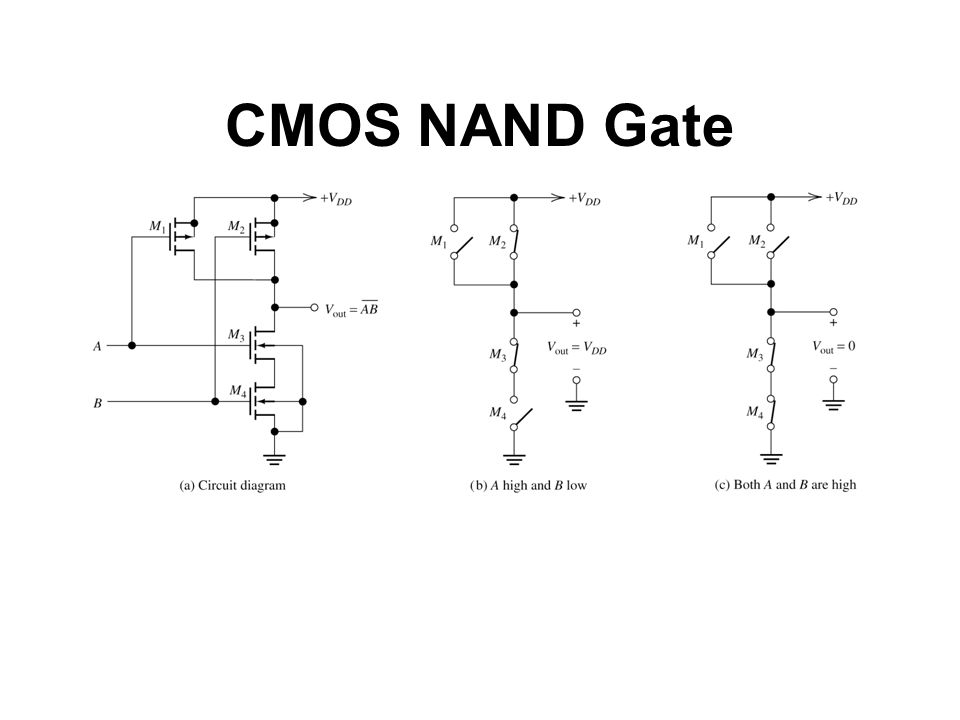

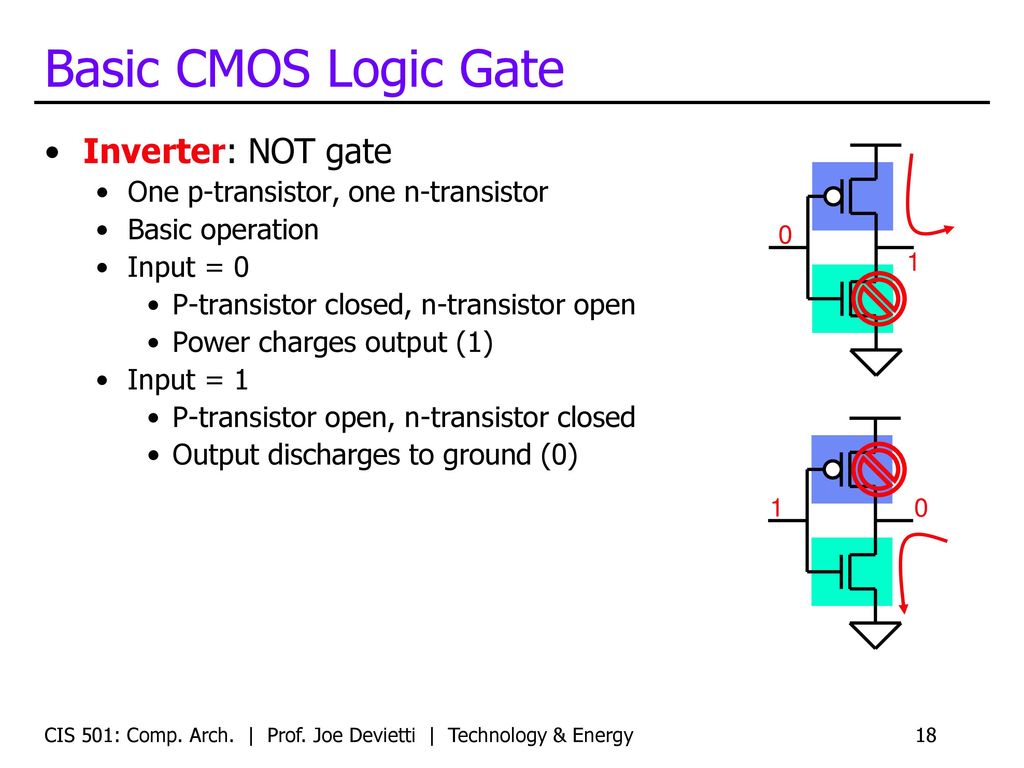

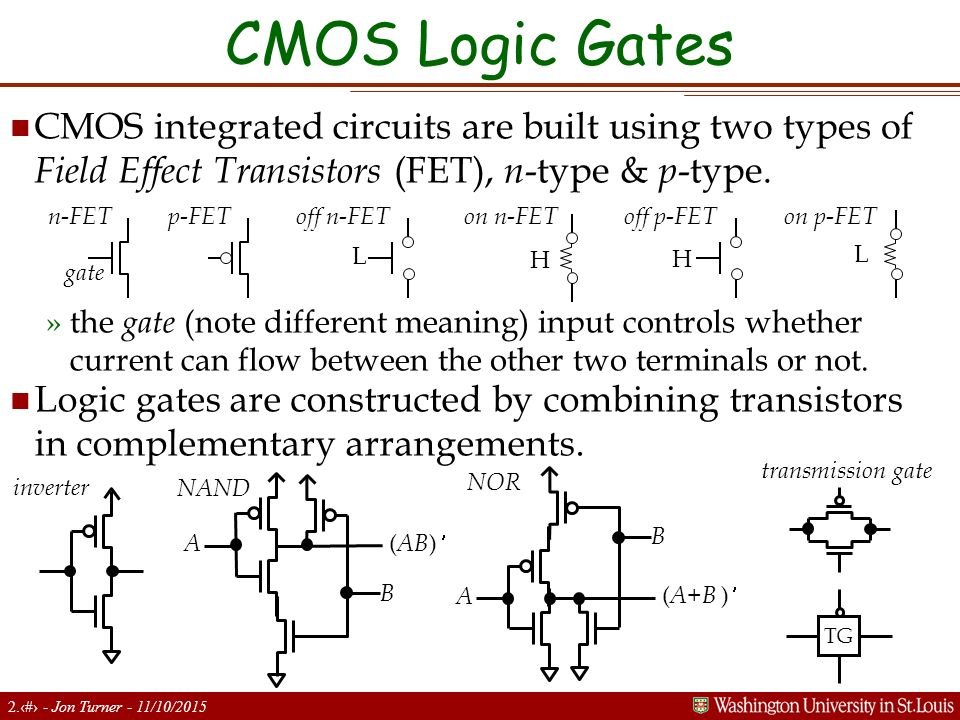

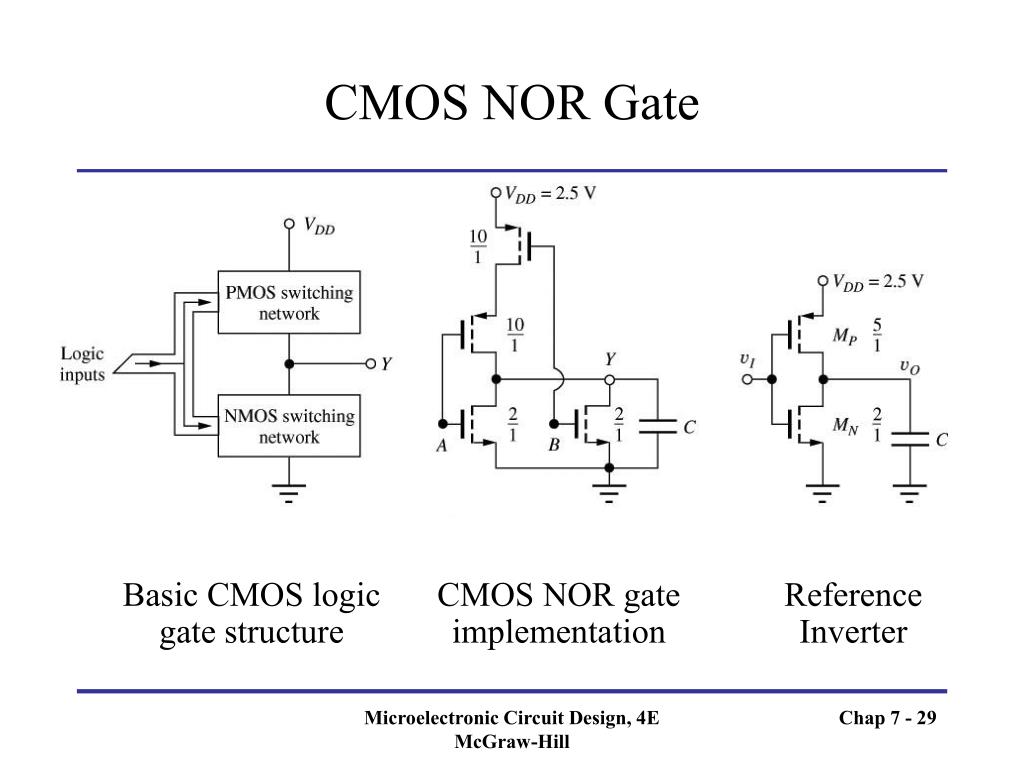

Так дополняют («C» в CMOS), потому что вы используете два устройства, которые ведут себя противоположным образом и, таким образом, дополняют друг друга. Затем логика инвертируется, потому что nMOS (который понижается) требует высокого входного напряжения (‘1’) для включения, а pMOS требует низкого напряжения (‘0’).

Но почему MOS хорош?

И некоторые дополнительные сведения: как сказал Олин, главная причина распространения технологии MOSFET заключается в том, что это плоское устройство, что означает, что его можно изготовить на поверхности полупроводника.

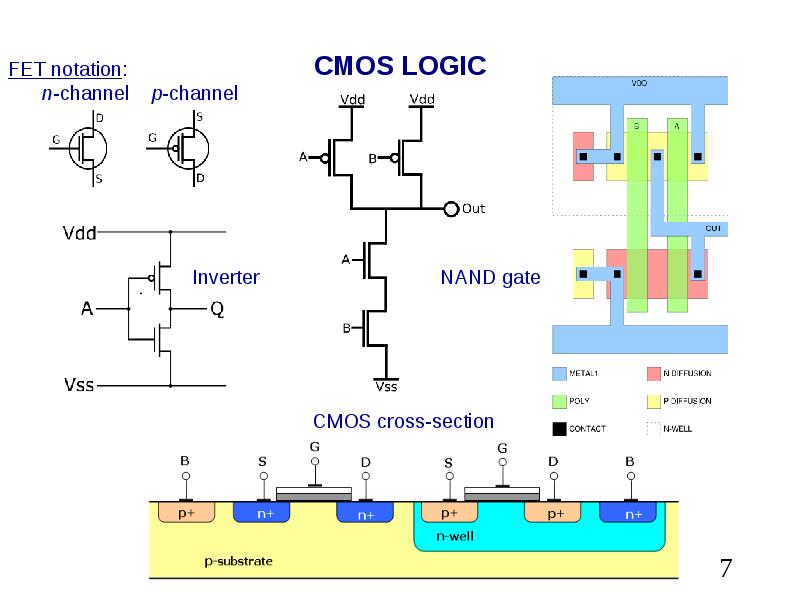

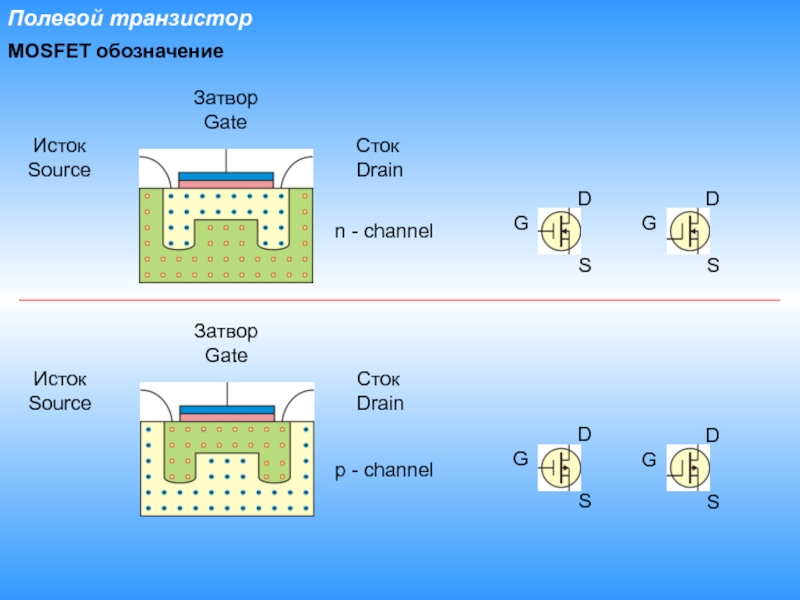

Это потому, что, как вы можете видеть на рисунке, построение MOSFET (это n-канал, p-канал в той же подложке требует дополнительной легированной области, называемой n-ямой) в основном состоит в легировании двух n + областей и сдача ворот и контактов (очень очень упрощенно).

BJT-транзисторы сегодня также изготавливаются по технологии, подобной MOS, что означает «травление» на поверхности, но в основном они состоят из трех слоев полупроводника, по-разному легированных, поэтому они в первую очередь предназначены для дискретных технологий. Фактически, способ, которым они теперь построены, создает эти три слоя на разных глубинах в кремнии, и (просто чтобы дать представление), в недавней технологии они занимают площадь в квадрате порядка микрометра или около того, в то время как МОП-транзисторы могут быть встроенная технология <20 нм (регулярно обновляйте это значение), с общей площадью, которая может быть порядка менее 100 нм². (картинка справа)

(картинка справа)

Таким образом, вы можете видеть, что, в дополнение к другим свойствам, MOSFET-транзистор намного лучше подходит (в современной технологии) для достижения интеграции очень большого масштаба, или VLSI.

В любом случае, биполярные транзисторы по-прежнему широко используются в аналоговой электронике из-за их лучших свойств линейности. Кроме того, BJT быстрее, чем полевой МОП-транзистор, построенный по той же технологии (подразумевается как размеры транзистора).

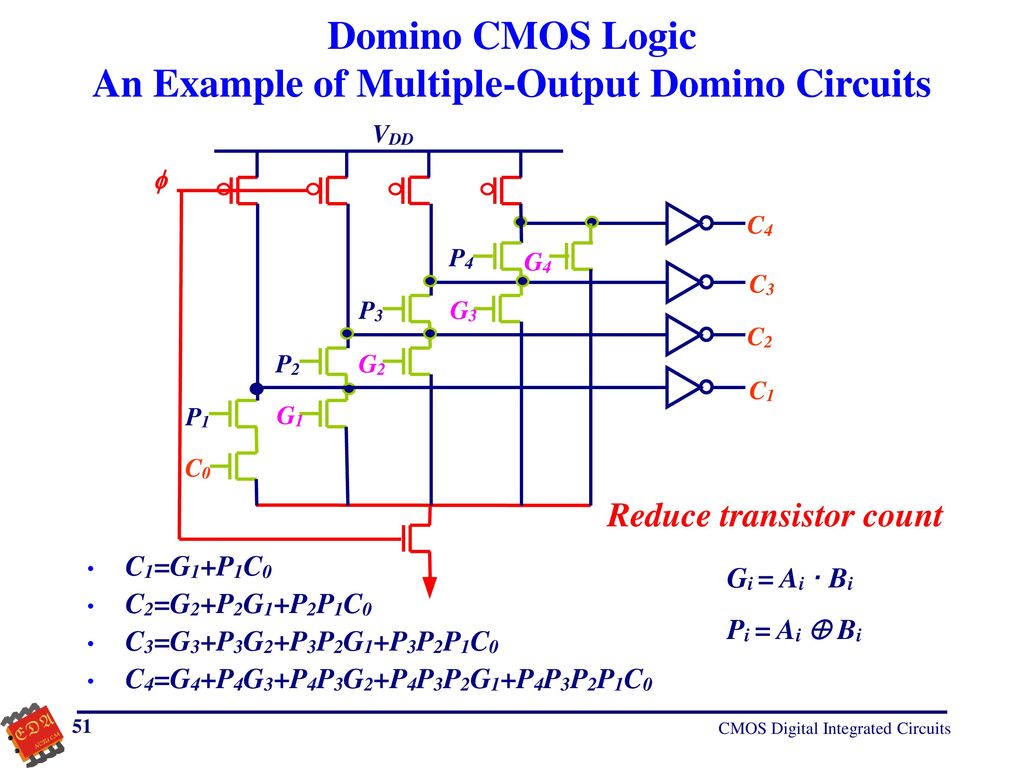

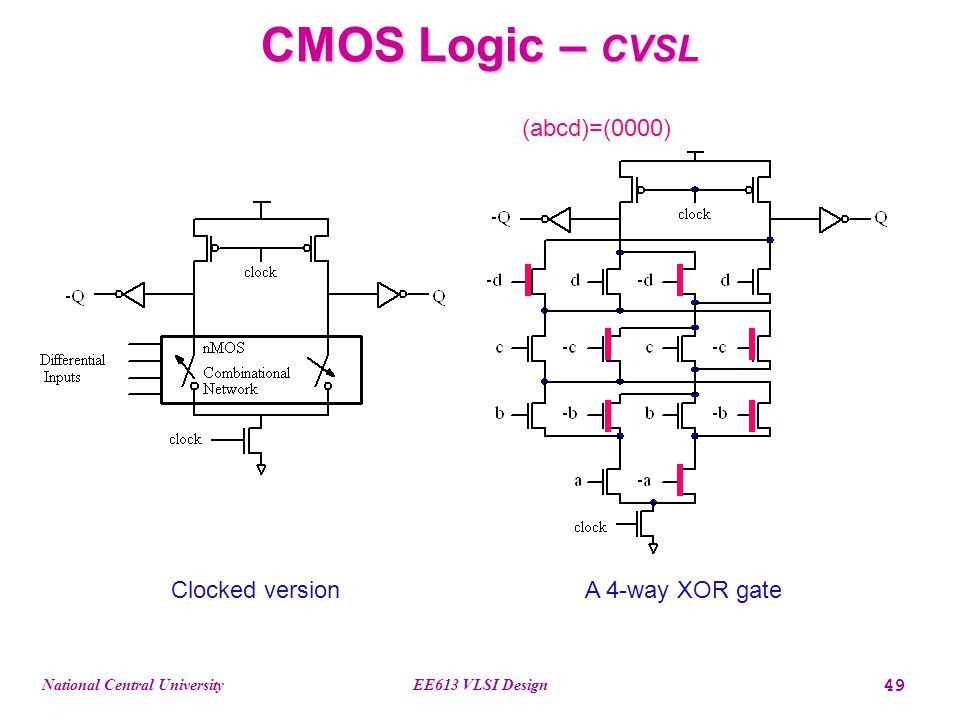

CMOS против MOS

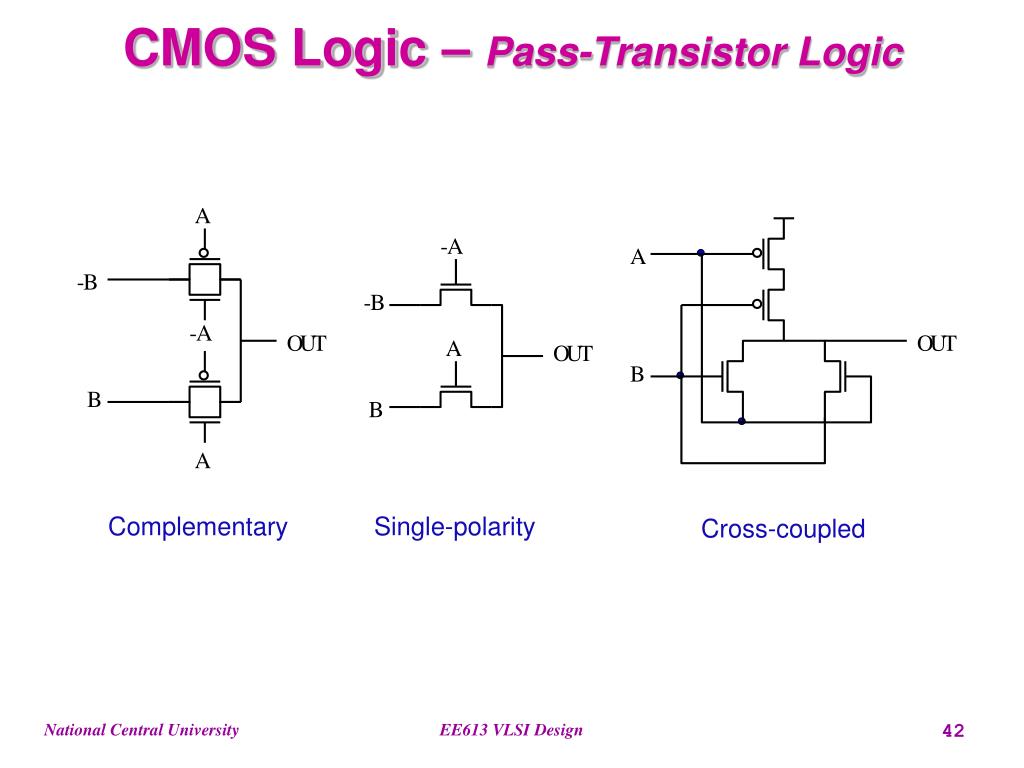

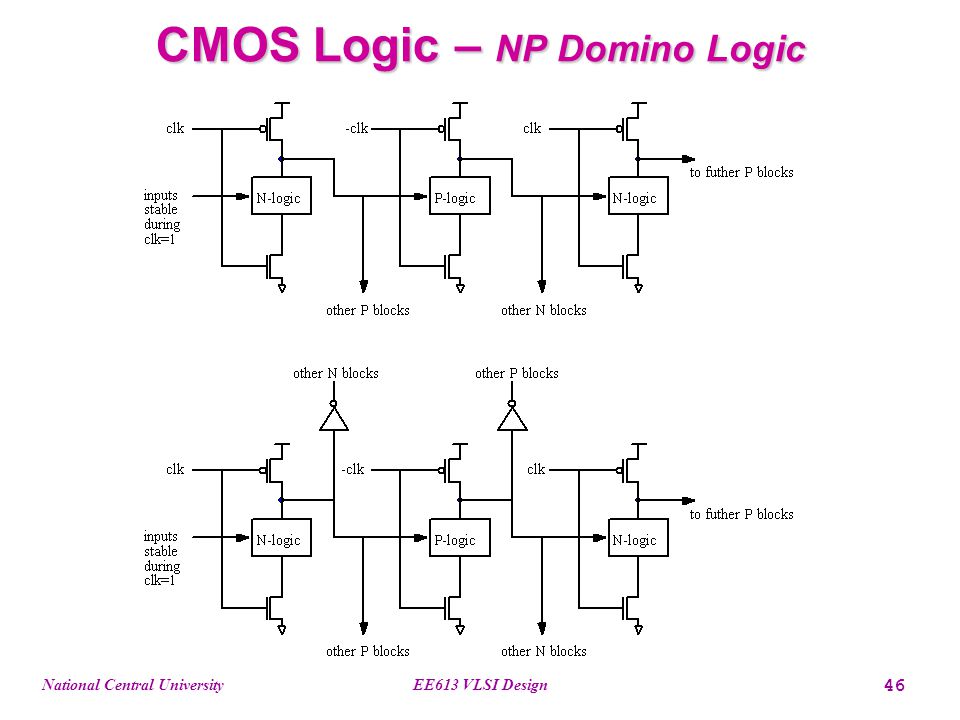

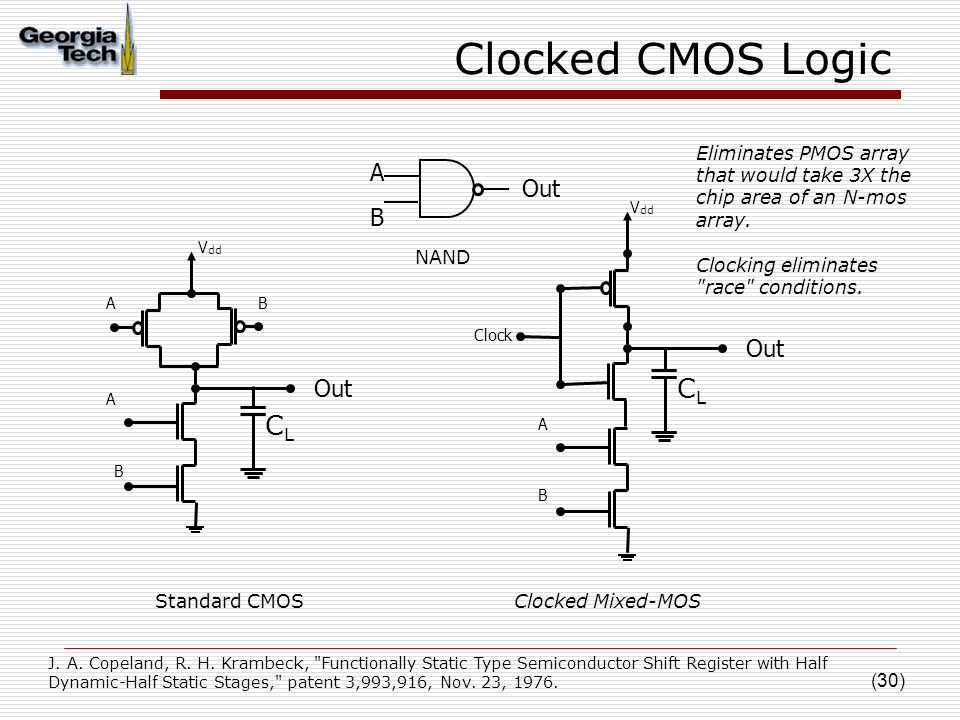

Обратите внимание, что CMOS не эквивалентен MOS: поскольку C предназначен для «дополняющего», это особая (даже если широко используемая) конфигурация для затворов MOS, в то время как высокоскоростные схемы часто используют динамическую логику, которая направлена на снижение входной емкости ворота. Фактически, попытка довести технологию до предела, наличие двух входных емкостей (как у CMOS) на входе является причиной потери производительности. Можно сказать, что достаточно увеличить ток, подаваемый на предыдущем этапе, но, например, для 2-кратной скорости зарядки требуется 2-кратный зарядный ток, что означает 2-кратную проводимость, которая достигается при 2-кратной ширине канала, и, что удивительно, удваивает входная емкость.

Другие топологии, такие как логика пассивного транзистора, могут упростить структуру определенных затворов и иногда достичь более высокой скорости.

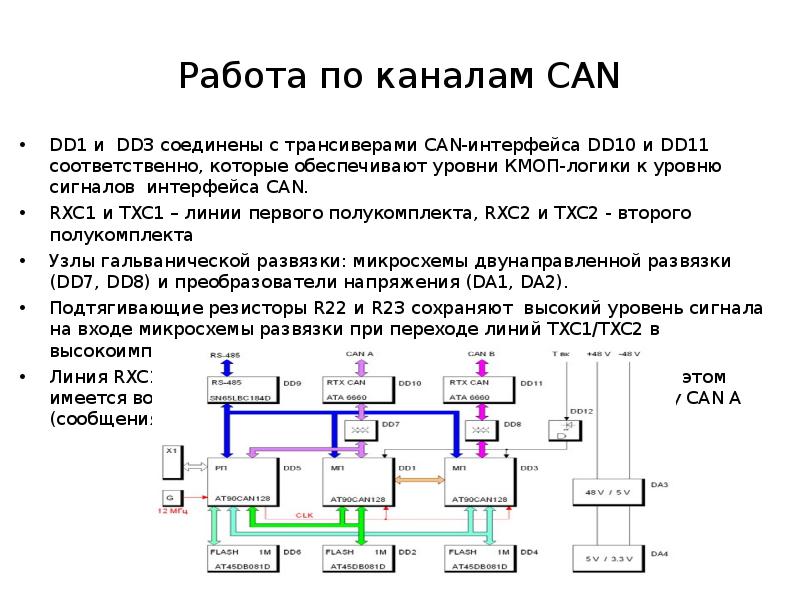

Об интерфейсах

При изменении темы, когда речь идет о микроконтроллерах и интерфейсах, важно помнить, что высокий входной импеданс вентилей CMOS делает очень важным, чтобы контакты ввода / вывода никогда не оставались плавающими (если они имеют защиту, это обеспечивается внутри), так как их Ворота могут подвергаться внешнему шуму и принимать непредсказуемые значения (с возможной фиксацией и повреждением). Заявление о том, что устройство имеет характеристики CMOS, также должно сообщить вам об этом.

| Обозначение | Прототип | Функциональное назначение | Тип корпуса | ||

|---|---|---|---|---|---|

| К561ИД1 | CD4028AN | Двоично-десятичный дешифратор | 2103Ю. | ||

| К561ИЕ8 | CD4017AN | Десятичный счетчик-делитель | 2103Ю.16-Д | ||

| К561ИЕ10 | CD4520AN | Два четырехразрядных счетчика | 2103Ю.16-Д | ||

| К561ИЕ11 | CD4516AN | Четырехразрядный двоичный реверсивный счетчик | 2103Ю.16-Д | ||

| К561ИЕ14 | CD4029AN | Двоично/двоично-десятичный четырехразрядный реверсивный счетчик с предварительной установкой | 2103Ю. | ||

| К561ИЕ16 | CD4020AN | Четырнадцатиразрядный двоичный счетчик-делитель | 2103Ю.16-Д | ||

| К561ИР2 | CD4015AN | Два четырехразрядных регистра сдвига | 2103Ю.16-Д | ||

| К561ИР6 | CD4034AN | 2142.24-А | |||

| К561КП1 | CD4052AN | Двойной четырехканальный мультиплексор | 2103Ю. | ||

| К561КП2 | CD4051AN | Восьмиканальный мультиплексор | 2103Ю.16-Д | ||

| К561КП6 | KT8592 | Четырехразрядный коммутатор для АТС со встроенной памятью состояния матрицы ключей | 2103Ю.16-Д | ||

| К561КТ3 | CD4066AN | Четыре двунаправленных переключателя | 2102Ю.14-В | ||

| К561ЛА7 | CD4011AN | Четыре логических элемента “2И-HЕ” | 2102Ю. | ||

| К561ЛА8 | CD4012AN | Два логических элемента “4И-HЕ” | 2102Ю.14-В | ||

| К561ЛА9 | CD4023AN | Три трехвходовых логических элемента “И-HЕ” | 2102Ю.14-В | ||

| К561ЛЕ5 | CD4001AN | Четыре логических элемента “2ИЛИ-HЕ” | 2102Ю.14-В | ||

| К561ЛЕ6 | CD4002AN | Два логических элемента “4ИЛИ-HЕ” | 2102Ю. | ||

| К561ЛЕ10 | CD4025AN | Три трехвходовых логических элемента “ИЛИ-HЕ” | 2102Ю.14-В | ||

| К561ЛН1 | CD4502AN | Шесть логических элементов “HЕ” с блокировкой и запретом | 2103Ю.16-Д | ||

| К561ЛН2 | CD4049AN | Шесть логических элементов “HЕ” | 2102Ю.14-В | ||

| К561ЛН5 | CD4069AN | Шесть логических элементов “HЕ” | 2102Ю. | ||

| К561ЛП2 | CD4030AN | Четыре логических элемента “Исключающее ИЛИ” | 2102Ю.14-В | ||

| К561ЛП13 | Три трехвходовых мажоритарных логических элемента | 2102Ю.14-В | |||

| К561ЛС2 | CD4019AN | Четыре логических элемента “И-ИЛИ” | 2103Ю.16-Д | ||

| К561ПУ4 | CD4050AN | Шесть преобразователей уровня | 2103Ю. | ||

| К561ТЛ1 | CD4093AN | Четыре триггера Шмитта с входной логикой “2И-HЕ” | 2102Ю.14-В | ||

| К561ТМ2 | CD4013AN | Два триггера D-типа | 2102Ю.14-В | ||

| К561ТР2 | CD4043AN | Четыре триггера R-S | 2103Ю.16-Д | ||

| ЭКР561ПУ8 | CD40116AN | Шесть преобразователей уровня без инверсии | 2102Ю. 14-В 14-В | ||

| ЭКФ561ПУ8 | CD40116AD | Шесть преобразователей уровня без инверсии | 4306.14-A |

Уровни напряжения логических схем «0» и «1» и согласование транзисторно-транзисторной логики ТТЛ и КМОП логики с помощью обратной связи, резисторов, транзистора

Логические элементы оперируют сигналами двух типов: “высокий логический уровень” (1) и “низкий логический уровень” (0), которые характеризуются различным уровнем напряжения: полное напряжение питания принимается в качестве уровня “логической единицы”, а нулевое напряжение – в качестве уровня “логического нуля”.

В идеальном случае все сигналы логических элементов существовали бы в виде этих двух предельных уровней напряжения, и никогда бы от них не отклонялись (например, ниже полного напряжения для “высокого уровня”, или выше нуля для “низкого уровня”. ) Однако в реальности уровни напряжения цифровых сигналов практически никогда не достигают этих идеальных величин.

) Однако в реальности уровни напряжения цифровых сигналов практически никогда не достигают этих идеальных величин.

Вследствие наличия паразитных падений напряжения в схемах на транзисторах, наводок, длины линии передачи сигнала и т.д.. Поэтому для логических схем интерпретируют сигналы как логическую единицу или логический нуль, даже в тех случаях, когда напряжение сигналов лежит в диапазоне между полным напряжением питания и нулём, то есть номинально не соответствует ни тому ни другом показателю.

Номинальное напряжение питания для логических радиоэлементов (микросхем) и номинальное значение логического 0 и логической 1

Элементы ТТЛ работают при номинальном напряжении питания 5 вольт, +/- 0,25 вольт. В идеале, сигнал высокого логического уровня должен быть равен ровно 5,00 В, а сигнал низкого уровня – ровно 0,00 вольт. Однако в реальных элементах ТТЛ не могут быть обеспечены подобные точные уровни напряжения, поэтому они могут принимать сигналы высокого и низкого уровней даже при значительном отклонении напряжения от идеальных величин. “Приемлемые” напряжения входного сигнала лежат в диапазоне от 0 до 0,8 вольт для низкого логического уровня, и от 2 до 5 вольт для высокого логического уровня. “Приемлемые” напряжения выходного сигнала (уровни напряжения, гарантируемые производителем элемента в указанных вариантах нагрузки) лежат в диапазоне от 0 до 0,5 вольт для низкого логического уровня, и от 2,7 до 5 вольт для высокого логического уровня.

“Приемлемые” напряжения входного сигнала лежат в диапазоне от 0 до 0,8 вольт для низкого логического уровня, и от 2 до 5 вольт для высокого логического уровня. “Приемлемые” напряжения выходного сигнала (уровни напряжения, гарантируемые производителем элемента в указанных вариантах нагрузки) лежат в диапазоне от 0 до 0,5 вольт для низкого логического уровня, и от 2,7 до 5 вольт для высокого логического уровня.

Если бы на вход элемента ТТЛ поступил сигнал напряжения в диапазоне от 0,8 до 2 вольт, то мы не получили бы гарантированной реакции схемы. Подобный сигнал будет рассматриваться как неопределённый, и в этом случае ни один производитель не даст гарантии того, к какому логическому уровню отнесёт схема подобный сигнал.

Как вы видите, диапазон допусков по уровням выходного сигнала меньше, чем в случае для входного сигнала. Это необходимо для обеспечения того, что цифровой сигнал, поступающий с выхода одного элемента логики на вход другого элемента, воспринимался бы таковым же, но с учетом условий потери и воздействия на него. Разница допусков между входным и выходным сигналами называется запасом схемы по помехоустойчивости. Для ТТЛ-схем, запас помехоустойчивости для низкого логического уровня представляет разность между 0,8 В и 0,5 В (т.е. 0,3 В), в то время как запас помехоустойчивости для высокого уровня равен 0,7 В (2,7 В – 2,0 В). Проще говоря, запас помехоустойчивости есть некий запас на паразитное или шумовое напряжение, которое может быть наложено на исходный сигнал, прежде чем принимающая схема может неверно его проинтерпретировать.

Разница допусков между входным и выходным сигналами называется запасом схемы по помехоустойчивости. Для ТТЛ-схем, запас помехоустойчивости для низкого логического уровня представляет разность между 0,8 В и 0,5 В (т.е. 0,3 В), в то время как запас помехоустойчивости для высокого уровня равен 0,7 В (2,7 В – 2,0 В). Проще говоря, запас помехоустойчивости есть некий запас на паразитное или шумовое напряжение, которое может быть наложено на исходный сигнал, прежде чем принимающая схема может неверно его проинтерпретировать.

Спецификации входных и выходных сигналов схем КМОП логических элементов совершенно отличны от уровней напряжения, используемых для ТТЛ-элементов. Для КМОП-элементов, работающих при напряжении питания 5 вольт, приемлемые напряжения входного сигнала лежат в диапазоне от 0 до 1,5 вольт для низкого логического уровня, и от 3,5 до 5 вольт для высокого логического уровня. “Приемлемые” напряжения выходного сигнала (уровни напряжения, гарантируемые производителем элемента при указанном варианте нагрузки) лежат в диапазоне от 0 до 0,05 вольт для низкого логического уровня, и от 4,95 до 5 вольт для высокого логического уровня.

Представленные значения дают понять, что запас помехоустойчивости КМОП логических элементов гораздо больше аналогичного показателя ТТЛ-элементов: 1,45 вольт как для логического нуля, так и для логической единицы, против максимального запаса в 0,7 В в случае ТТЛ. Другими словами, КМОП-схемы могут выдержать более чем вдвое высокий наложенный шум на входе без ошибок интерпретации сигнала как логического нуля или единицы.

Запас помехоустойчивости КМОП логических схем становится ещё больше при более высоких рабочих напряжениях. В отличие от элементов ТТЛ, напряжение питания которых не превышает 5 вольт, напряжение питания КМОП-схем может достигать 15 (а в некоторых случаях и 18) вольт. Ниже показаны приемлемые уровни логических нуля и единицы, для выхода и входа КМОП-ИС, работающих при напряжении питания 10 и 15 вольт соответственно:

Запас помехоустойчивости может быть выше того, что показано на предыдущем рисунке. На рисунке показан худший из возможных вариантов поведения сигнала на основании спецификаций производителя. На практике логическая схема может выдержать сигналы высокого логического уровня со значительно меньшим напряжением и сигналы низкого логического уровня с гораздо большим напряжением чем указано.

На практике логическая схема может выдержать сигналы высокого логического уровня со значительно меньшим напряжением и сигналы низкого логического уровня с гораздо большим напряжением чем указано.

И наоборот, исключительно малые показанные запасы помехоустойчивости – гарантирующие выходное состояние сигналов высокого и низкого логических уровней с точностью до 0,05 вольта напряжения питания – практически реальны. Такие “добротные” уровни выходного напряжения будут доступны только при минимальной нагрузке. При значительном втекающем или вытекающем токе схемы выходное напряжение не будет поддерживаться на этих оптимальных уровнях, что обусловлено наличием внутреннего сопротивления каналов выходных МОП-транзисторов логических элементов.

Помехоустойчивость при единичных (разовых) скачках напряжения, появления помехи (наводки)

В пределах “неопределённого” диапазона для любого входа логического элемента, будет иметься точка разделения актуального сигнала низкого уровня от диапазона действительного входного сигнала высокого уровня. То есть, где-то между наименьшим напряжением сигнала высокого логического уровня и наибольшим напряжением сигнала низкого логического уровня гарантированного производителем, существует порог напряжения, при котором логическая схема будет менять интерпретацию сигнала с высокого на низкий и наоборот. В случае большей части логических схем, это напряжение соответствует одной определённой точке:

То есть, где-то между наименьшим напряжением сигнала высокого логического уровня и наибольшим напряжением сигнала низкого логического уровня гарантированного производителем, существует порог напряжения, при котором логическая схема будет менять интерпретацию сигнала с высокого на низкий и наоборот. В случае большей части логических схем, это напряжение соответствует одной определённой точке:

При наличии шумового напряжения переменного тока, наложенного на входной сигнал постоянного тока единственная точка, в которой схема переменит интерпретацию логического уровня будет обуславливать ошибочный сигнал на выходе.

Подобная проблема характерна также для аналоговых ОУ-компараторов напряжения. В случае одиночной пороговой точки смены логического уровня наличие значительного шума может привести к неверной интерпретации логического уровня на выходе.

Эту проблему можно решить путём введения в цепь усилителя положительной обратной связи. В случае операционного усилителя необходимо соединить выход с неинвертирующим входом через резистор. Схемы подобного типа называются триггерами Шмитта. Триггеры Шмитта идентифицируют логический уровень сигнала согласно двум пороговым уровням: при нарастающем напряжении (VT+), и при падающем напряжении (VT-):

В случае операционного усилителя необходимо соединить выход с неинвертирующим входом через резистор. Схемы подобного типа называются триггерами Шмитта. Триггеры Шмитта идентифицируют логический уровень сигнала согласно двум пороговым уровням: при нарастающем напряжении (VT+), и при падающем напряжении (VT-):

На схемах триггеры Шмитта изображаются с символом «гистерезиса». Гистерезис, вызванный положительной обратной связью в схеме логического элемента, придаёт схеме дополнительную помехоустойчивость. Триггеры Шмитта часто используются в схемах с высокой вероятностью шума на входе, а также в тех случаях когда ошибочно интерпретированный сигнал на выходе приведёт к некорректной работе системы в целом.

Различные требования по уровням напряжения ТТЛ- и КМОП-элементов создают определённые проблемы при использовании в одной схеме элементов двух типов. Хотя работа КМОП логических элементов может осуществляться при том же напряжении питания 5,00 В, которое необходимо для элементов ТТЛ, выходные уровни напряжения ТТЛ логики несовместимы с входными требованиями по напряжению для КМОП-схем.

Возьмём к примеру ТТЛ-элемент НЕ-И, сигнал с выхода которого подаётся на вход КМОП-инвертора. Питание обоих элементов составляет 5,00 В (Vcc). Если с выхода элемента ТТЛ приходит сигнал логического нуля (т.е. между 0 и 0,5 В), то он будет верно интерпретирован на входе КМОП-схемы как сигнал низкого логического уровня (т.е. сигнал между 0 и 1,5 В):

Однако, если с выхода элемента ТТЛ приходит сигнал логической единицы (т.е. между 5 и 2,7 В), то он может быть неверно интерпретирован на входе КМОП-схемы как сигнал высокого логического уровня (т.е. ожидается сигнал между 5 и 3,5 В):

Такое несоответствие может привести к тому, что “правильный” сигнал высокого уровня на выходе ТТЛ- элемента (правильный с точки зрения стандартов ТТЛ) будет лежат в “неопределённом” диапазоне входа КМОП-схемы, и быть неверно воспринят как сигнал логического нуля принимающим элементом. Простым решением этой проблемы может стать повышение сигнала логической единицы элемента ТТЛ с помощью нагрузочного повышающего резистора:

Однако потребуется гораздо более серьёзная переделка схемы, если питание КМОП-схемы выше 5 вольт:

Проблемы не возникнет в случае логического нуля, однако всё обстоит совершенно иначе в случае сигнала высокого логического уровня с выхода элемента ТТЛ. Диапазон выходного напряжения 2,7-5 В с выхода элемента ТТЛ совершенно не соответствует приемлемому диапазону 7-10 В КМОП логической схемы. Если мы используем ТТЛ-схемы с открытым коллектором, то нагрузочный резистор, включённый в шину питания Vdd 10 вольт, поднимет сигнал высокого логического уровня до полного напряжения питания КМОП логической схемы. Поскольку в схеме с открытым коллектором в наличии только втекающий ток, напряжение логической единицы полностью определяется тем напряжением питания, к которому подключён повышающий резистор, что помогает решить проблему несоответствия уровней напряжения.

Диапазон выходного напряжения 2,7-5 В с выхода элемента ТТЛ совершенно не соответствует приемлемому диапазону 7-10 В КМОП логической схемы. Если мы используем ТТЛ-схемы с открытым коллектором, то нагрузочный резистор, включённый в шину питания Vdd 10 вольт, поднимет сигнал высокого логического уровня до полного напряжения питания КМОП логической схемы. Поскольку в схеме с открытым коллектором в наличии только втекающий ток, напряжение логической единицы полностью определяется тем напряжением питания, к которому подключён повышающий резистор, что помогает решить проблему несоответствия уровней напряжения.

Благодаря прекрасным характеристикам выходного напряжения КМОП схем, проблем при подключения ТТЛ элемента к выходу КМОП схемы обычно не возникает. Единственной серьёзной проблемой может стать токовая нагрузка, поскольку КМОП-схема должна обеспечивать втекающий ток на каждый вход элемента ТТЛ в случае логического нуля.

Если КМОП-схема питается от источника напряжения выше 5 вольт (Vcc), то возникнет проблема. Напряжение логической единицы КМОП-схемы выше 5 вольт не будет находиться в диапазоне допустимых входные параметров элемента ТТЛ. Решением этой проблемы может стать инвертор с “открытым коллектором” на дискретном NPN-транзисторе, используемом для соединения двух логических схем:

Напряжение логической единицы КМОП-схемы выше 5 вольт не будет находиться в диапазоне допустимых входные параметров элемента ТТЛ. Решением этой проблемы может стать инвертор с “открытым коллектором” на дискретном NPN-транзисторе, используемом для соединения двух логических схем:

Повышающий резистор Rpullup используется опционально, поскольку входы элементов ТТЛ принимают высокий логический уровень, когда находятся в плавающем состоянии, что и произойдёт, когда выход КМОП-схемы будет низким, а транзистор будет находиться в состоянии отсечки. Конечно, важным последствием такого решения является логическая инверсия, создаваемая транзистором: когда на выходе КМОП-схемы будет сигнал логического нуля, элемент ТТЛ будет “видеть” логическую единицу и наоборот. Однако, если принимать эту инверсию во внимание, то корректная работа схемы не будет нарушена.

| Тип | Особенности |

| 4001 | КМОП Quad 2-вход NOR Gate |

| 4011 | КМОП Quad 2-вход NAND Gate |

| 4013 | Двойной d-образный флип-флоп CMOS |

| 4017 | Счетчик КМОП с 10 декодированными выходами |

| 4021 | 8-ступенчатый статический сдвиг CMOS |

| 4022 | КМОП восьмиугольный счетчик с 8 декодированными выходами |

| 4023 | КМОП тройной 3-вход NAND ВОРОТА |

| 4025 | КМОП тройной 3-вход NOR Gate |

| 4026 | Счетчик/делитель CMOS с декодированным 7-сегментным дисплеем |

| 4027 | КМОП Двойной J-K мастер-раб флип-флоп |

| 4028 | CMOS BCD-to-Decimal или Binary-to-Octal декодеры/драйверы |

| 4043 | CMOS Quad NOR R/S защелка с 3-мя выходами |

| 4046 | КМОП микропитание фазоблокированная петля |

| 4049 | CMOS шестигранный перевернутый Буфер/конвертер |

| 4050 | CMOS шестигранный неинвертирующий Буфер/конвертер |

| 4051 | CMOS одноканальный 8-канальный аналоговый мультиплексор/демплексор с преобразованием логического уровня |

| 4052 | CMOS дифференциальный 4-канальный аналоговый мультиплексор/демплексор с преобразованием логического уровня |

| 4053 | CMOS тройной 2-канальный аналоговый мультиплексор/демплексор с преобразованием логического уровня |

| 4060 | КМОП 14-ступенчатый пульсационный бинарный счетчик/делитель и осциллятор |

| 4066 | КМОП Quad Двусторонний переключатель |

| 4069 | Шестигранный инвертор CMOS |

| 4070 | КМОП четырехъядерный эксклюзивный-или ворота |

| 4071 | КМОП Quad 2-вход или ворота |

| 4072 | CMOS двойной 4-вход или ворота |

| 4073 | КМОП тройной 3-вход и ворота |

| 4075 | КМОП тройной 3-вход или ворота |

| 4081 | КМОП Quad 2-вход и ворота |

| 4082 | CMOS двойной 4-вход и ворота |

| 4093 | CMOS Quad 2-вход NAND Schmitt триггеры |

| 4094 | CMOS 8-Stage Shift-and-Store Bus Register |

Часто бывает необходимо подобрать серию микросхем логики под определенные требования – энергопотребление, предельная рабочая частота, уровни напряжений логики и питания, нагрузочная способность и т. Параметры серий обобщенно закодированы в названиях серий: HCT, ALS, F, LVC и т. п. Для начала давайте разберемся, что обозначают буквы, составляющие название серий. К сожалению, это общие обозначения, смысл букв иногда может меняться, потому что многие серии являются одновременно и торговыми марками производителей микросхем. A – advanced, т. е. улучшенный, продвинутый. Показывает, что эта серия основана на базовой, с улучшением каких-то параметров (обычно это скорость работы и уменьшение энергопотребления). Примеры: AC – семейство Advanced CMOS. С помощью таблицы быстрого выбора, размещенной ниже выберите самый важный для Вас параметр – скорость переключения, минимальное потребление, нагрузочная способность, устойчивость к помехам – и определите, какое семейство больше подходит. Затем с помощью дополнительной справочной информации уточните Ваш выбор. Таблица 1. Быстрый выбор серии микросхем (основные характеристики серий).

Обозначения: High Speed высокая скорость. Рис. 1. Эволюция развития серий микросхем логики. Таблица 2. Общее описание возможностей различных серий.

Примечания: (1) CROSSVOLT™, марка FAIRCHILD Semiconductor. Параметр задержки распространения сигнала вместе с временем нарастания и спада на выходе определяют максимальную рабочую частоту серии. Таблица 3. Величина задержки распространения сигнала(1). Примечания: (1) Даны максимальные значения из даташита на указанные модели микросхем. Таблица 4. Время нарастания и спада уровня(1). Примечания: (1) Даны значения для логики ‘244, емкость нагрузки CLOAD = 50 пФ, сопротивление нагрузки RL = 500 Ω. Таблица 5. Уровень генерируемого шума(1). VOLP уровень положительного выброса, VOLV уровень отрицательного выброса. Примечания: (1) Даны значения для логики ‘244, емкость нагрузки CLOAD = 50 пФ, сопротивление нагрузки RL = 500 Ω, типовые значения сопротивлений для 4.5V, переключение семи выходов, минимальный наклон перепадов на входе. Таблица 6. Динамическое потребление тока (мА)(1).

Примечание (1): даны значения для логики ‘244, емкость нагрузки CLOAD = 50 пФ. Все значения представляют типовые параметры. Рис. 2. Различные серии микросхем преобразователей уровней. Примечания: † Устройства с автоматическим определением направления передачи данных не требуют для этого специальных выводов управления. Таблица 7. Сравнение параметров семейств.

Примечания: * Для примеров применялась логика функции ’244, если не указано нечто другое. Ниже приведена сравнительная таблица размеров и параметров корпусов различного типа. Примечание (1): в скобках приведены коды корпусов компании FAIRCHILD Semiconductor. [Ссылки] 1. Logic Selection Guide site:fairchildsemi.com. | |||||||

|

Справочник описывает микросхемы КМОП серий 164, 176, 564, 561, 1561. От составителя

Микросхемы: АГ1 – два одновибратора

Соответствие отечественных КМОП-микросхем зарубежным

аналогам

|

Этот справочник является продолжением серии справочников

по цифровым микросхемам и включает в себя описания КМОП микросхем стандартных

серий.

При составлении справочника широко использовались стандартные сокращения и обозначения, распространенные среди западных изготовителей микросхем. Так например, L- означает низкий потенциал (логический нуль при положительной логике), H- высокий потенциал и X- безразлично L или H. Qa=L означает, что соответствующий выход имеет на выходе низкий потенциал. Для сокращения объема справочника было использовано

два приема.

Для полноты охвата, в справочник включены также и микросхемы не имеющие западного аналога. Для таких ТТЛ-микросхем приведены, естественно, данные из отечественных источников. Справочник составлен в 1991 году, переведен в HTML в 2000 году. Мы надеемся, что Вам понравится наш справочник. |

Для начинающих. ТТЛ, КМОП и т.д. | Старый радиолюбитель

Настало время познакомить вас с разнообразием серий логических элементов на разной элементной базе.

Начнем с ТТЛ (транзисторно-транзисторная логика). Элементной базой этих серий являются биполярные транзисторы. Широко используются многоэмиттерные транзисторы. Эти транзисторы сконструированы таким образом, что отдельные эмиттеры не оказывают влияния друг на друга. Каждому эмиттеру соответствует свой p-n-переход. Такая логика используется в наших сериях К155 и К131. Максимальная частота для серии К155 – 10МГц, для серии К131 – 15 МГц. Напряжение питания – +5 В с точностью 0,5В. В качестве примера приведу схему элемента ИЛИ-НЕ серии К155.

Рис. !. Схема элемента ИЛИ-НЕ серии К155.В микросхемах РИс. 2. Схема элемент используются диоды и транзисторы с барьером Шоттки, что, с одной стороны, позволяет снизить потребляемую мощность, а с другой – повысить максимальную частоту. В качестве примера приведу схему 3ИЛИ-НЕ.

Рис.2 Схема элемента 3И – НЕ серии К531.Элемент, приведенный на рис. 2, потребляет мощность, сравнимую с серией К155, но имеет максимальную частоту около 60 МГц, а такой же элемент серии К555 имеет потребляемую мощность в пять раз меньше, чем у серии К155, но такую же максимальную частоту. По напряжению питания и логическим уровням серии ТТЛ и ТТЛШ полностью совместимы.

Дальнейшим развитием логических элементов на биполярных транзисторах явилось появление серий ЭСЛ. Эми́ттерно-свя́занная ло́гика (ЭСЛ, ECL) — способ построения логических элементов на основе дифференциальных транзисторных каскадов. ЭСЛ является самой быстродействующей из всех типов логики, построенной на биполярных транзисторах. Это объясняется тем, что транзисторы в ЭСЛ работают в линейном режиме, не переходя в режим насыщения, выход из которого замедлен. Низкие значения логических перепадов в ЭСЛ-логике способствуют снижению влияния на быстродействие паразитных ёмкостей. Быстродействие этих серий – прядка 500 МГц. У нас самыми известной у радиолюбителей была серия К500. Отличием микросхем ЭСЛ от ТТЛ и ТТЛШ является отрицательное напряжение питания, поэтому они напрямую несовместимы. В качестве примера – элемент 2ИЛИ-НЕ.

Рис. 3. Схема элемента серии ЭСЛ К500.Обратите внимание, что в состав элемента включен источник опорного напряжения (ИОН) (диоды VD1, VD2, R3, R7 и транзистор VT3. Кроме того, выходы элемента – с открытым эмиттером, т.е. при подключении нужно установить внешние нагрузочные резисторы между выводами выходов и выводом питания. Мы в радиокружке выпаивали микросхемы этой серии из плат ЭВМ Минск, которую утилизировали в Гидрометеоцентре. Несколько этих микросхем храню до сих пор.

Рис. 4. Микросхемы серии К500.В настоящее время элементы, выполненные на биполярных транзисторах, почти полностью вытеснили элементы на полевых транзисторах. Это позволило сократить потребление энергии на три порядка. Кроме того, элементы на полевых транзисторах имеют высокое входное сопротивление, т.е. малый входной ток. Правда, и максимальный выходной ток у них менее 1 мА, поэтому, при использовании их в разных конструкциях, приходится ставить на выходе эмиттерные повторители, как в схеме реле из предыдущей статьи.

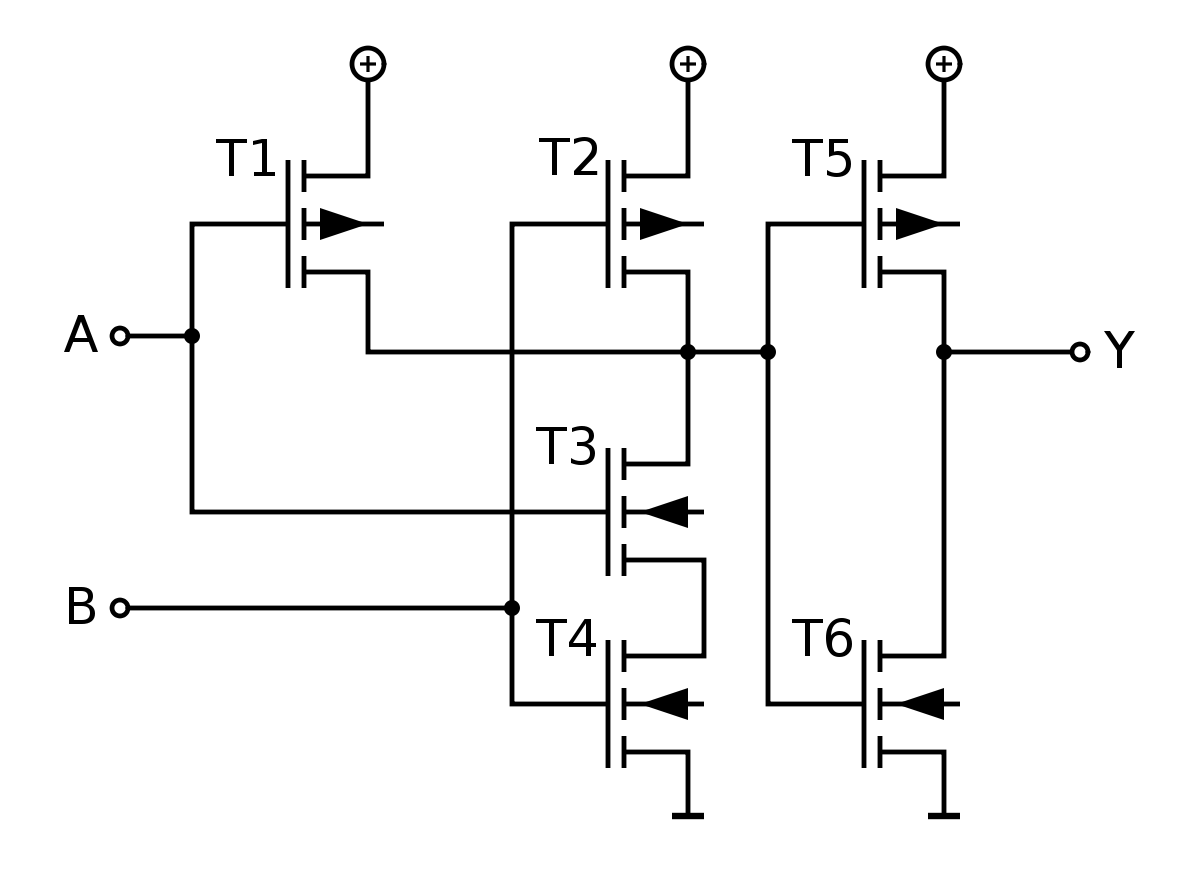

Наибольшее распространение сейчас получили серии КМОП (комплементарная структура металл-оксид-полупроводник; ( англ. CMOS, complementary metal-oxide-semiconductor). Как видно их названия, элементы этой серии собраны из комплементарных транзисторов, обычно с изолированным затвором. Общая закономерность построения таких элементов заключается в том, что параллельное соединение транзисторов с каналами p-типа сопровождается последовательным соединением транзисторов с каналами n-типа и наоборот. Давайте рассмотрим работу простейшего элемента – инвертора.

Рис. 5. Схема элемента НЕ серии КМОП.Транзистор VT1 имеет канал р-типа, поэтому закрывающим для него будет Uпит, так как в этом случае напряжение между его затвором и истоком будет равно нулю. А откроется этот транзистор, если его затвор соединить с общим проводом, ведь тогда напряжение между его затвором и истоком будет равно напряжению питания. Для транзистора VT2, имеющего канал n-типа, все будет наоборот: если его затвор соединить с общим проводом, он будет закрыт, а если затвор соединить с питанием, то он откроется. Вы помните, что канал открытого полевого транзистора имеет низкое сопротивление (доли Ом – единицы Ом), а канал закрытого – десятки МОм.

Итак, как работает наш инвертор? Если на входе Х напряжение низкого уровня, то VT2 закрыт, а VT1 – открыт и через его отрытый канал на выход попадает напряжение питания (низкий ЛУ). Если на входе напряжение высокого логического уровня, то VT1 закрыт, а VT2 – открыт и через его отрытый канал выход элемента замкнут на общий провод (высокий ЛУ). Как видите, ничего сложного и ничего лишнего в схеме.

Рассмотрим работу еще одного логического элемента, знакомого вам – ИЛИ-НЕ.

Рис. 6. Схема элемента ИЛИ-НЕ серии КМОП.Здесь p-канальные транзисторы включены последовательно (VT3, VT4), а n-канальные – параллельно (VT2, VT3). Если на обоих входах Х1, Х2 ,будет низкий ЛУ, то транзисторы VT1, VT2 будут закрыты, а транзисторы VT3, VT4 – открыты. На выходе будет присутствовать высокий ЛУ. Если хотябы на одном из входов Х1, Х2 ,будет высокий ЛУ, то один из транзисторов ры VT1, VT2 будет открыт, а один из транзисторов VT3, VT4 – закрыт. На выходе будет присутствовать низкий ЛУ.

В элементе нет ни одного резистора, а это говорит о том, что греться здесь нечему, т.к. транзисторы находятся или в закрытом состоянии (протекающий через них ток ничтожен), или в открытом состоянии (их сопротивление очень мало). Основное потребление тока происходит только в моменты переключения.

В настоящее время КМОП-технологии являются доминирующими при производстве цифровых интегральных схем и практически вытеснили логику на основе биполярных транзисторов. КМОП-логика используется в цифровых интегральных схемах как малой (1–10 логических элементов на кристал- 303 ле) и средней (10–100 ЛЭ), так и большой степени интеграции. Это обусловлено следующими причинами.

1. Логические элементы, изготовленные по КМОП-технологии, потребляют значительно меньшую мощность, чем логические элементы на основе биполярных транзисторов как в статическом, так и в динамическом режимах. Потребление мощности КМОП-элементами обусловлено в основном перезарядом паразитных емкостей при переключении элемента из одного логического состояния в другое.

2. Поскольку входы схем являются изолированными затворами МОП-транзисторов, то входные токи очень малы. Поэтому коэффициент разветвления по выходу очень высок. Высокое входное сопротивление МОП-транзисторов позволяет использовать накопленный заряд для хранения входной информации. Это свойство широко используется в микросхемах памяти.

3. МОП-транзистор занимает на кристалле значительно меньшую площадь, чем биполярный. Современные технологии производства СБИС позволяют создавать МОП-транзисторы с длиной канала 0.06 мк. Уменьшение геометрических размеров, а также малое потребление мощности дают возможность изготавливать СБИС, которые содержат десятки миллионов МОП транзисторов.

Тут нужно различать МОП (метал-оксид-проводник) – структуру отдельного элемента и КМОП – технология логических элементов, состоящих из МОП – транзисторов.

Совместимы ли серии КМОП и ТТЛ. ТТЛШ? Так как диапазон питания КМОП лежит в пределах 3 – 15В, то при напряжении 5В можно подключать элементы КМОП к выходу элементов ТТЛ или ТТЛШ. А вот подключать к выходам элементов КМОП элементы ТТЛ или ТТЛШ не рекомендуется из-за низкой нагрузочной способности элементов КМОП. Но грустить не надо. В сериях КМОП (К176 и К561) есть специальные микросхемы преобразователей уровня (ПУ), а в крайнем случае можно установить эмиттерный или истоковый повторитель.

И, наконец, сводная таблица.

Рис. 7. Основные свойства логических элементов разных серий.Безусловно, серий микросхем огромное множество и охватить их все, или даже существенную часть, я не могу. Да и это ни к чему, так как встретив незнакомую микросхему, посмотрите ее datasheet. Сравнив ее характеристики с таблицей, в первом приближении, к какому типу она относится. Хотя, используя переводчик Googl все можно узнать и по даташту.

По нашим отечественным микросхемам есть отличный справочник В.Л. Шило “Популярные цифровые микросхемы”. Пользуюсь ей уже не один десяток лет. Эту книгу можно скачать здесь: https://booksee.org/book/391484

Всем здоровья и успехов.

Вот как быстро собрать аудиодорожки в Logic Pro X: macProVideo.com

Создание аудиодорожек – важный навык для создания идеального исполнения. В этом видео Букер Эдвардс показывает вам, как это сделать в Logic Pro.

Logic Pro – одна из самых мощных универсальных DAW на рынке, а ее инструменты редактирования аудио особенно мощны. В этом коротком 4-минутном видео из курса Logic Pro FastTrack 201: Расширенные советы по редактированию аудио эксперт по Logic Pro Букер Эдвардс углубляется в один из наиболее продвинутых методов – создание композитных аудиозаписей, или «композиций».

Букер использует практический пример многополосной аудиодорожки, записанной за несколько проходов, а затем демонстрирует, как использовать инструменты компоновки, такие как быстрое смахивание, ножницы и обрезка, чтобы взять лучшие части из нескольких дублей и объединить их в один. идеальный дубль. Вы увидите, как корректировать тайминг, перемещая различные части дублей, и как перемещать разделы композиции между дорожками. Это простой пример, который поможет вам при составлении любого аудиоматериала для достижения идеального результата! Просмотрите остальные видеоролики курса, чтобы узнать более сложные советы по редактированию звука в Logic Pro.

Посмотрите полный курс Logic Pro FastTrack 201: Advanced Audio Editing Tips в Ask Audio Academy здесь.Logic Pro FastTrack 201: расширенные советы по редактированию аудио

Знаете ли вы все функции, которые интегрированы в составление Quick Swipe? Как насчет разницы между циклами, копиями и клонами и когда их лучше всего использовать? Как насчет эффективности групп редактирования и всех способов сжатия и расширения звука в главном окне? Затем есть «карманные» барабаны с помощью функции звука Phased Locked в Logic Pro.Эти и другие советы быстро вводятся прямо в ваш мозг в этом лазерно-ориентированном курсе Букера Эдвардса.

Logic Pro часто называют DAW, которую вы используете для создания музыки, а не для редактирования и микширования. Но это действительно миф. Apple и вся команда Logic при каждой возможности добавляли все больше и больше расширенных функций редактирования звука. Мы считаем, что Logic сейчас на одном уровне или даже более продвинута, чем ее старый друг Pro Tools! И этот курс докажет это!

Так что посмотрите этот курс FastTrack ™ Букера Эдвардса и быстро узнайте секреты расширенного редактирования звука в Logic Pro!

Посмотрите полный курс Logic Pro FastTrack 201: Advanced Audio Editing Tips в Ask Audio Academy здесь.Холлин ДжонсХоллин Джонс был классическим пианистом, но счел соблазн блюза и джаза слишком сильным, чтобы сопротивляться. Переходя от групп к композиции, а затем к продюсированию, он наслаждается возможностью играть на клавишах на чем угодно. Когда-то преподавал видеографию, производство музыки и пост-продакшн фотографий, Холлин более десяти лет был внештатным писателем по музыкальным технологиям и темам Apple, попутно опубликовав несколько книг по звуковому программному обеспечению.Он был ведущим автором ряда известных музыкальных и технических изданий. Помимо консультирования, постоянной журналистики, видеопроизводства и профессиональной фотографии, он иногда играет Хаммонда, Родса и других ключей для людей, которые вежливо просят. Холлин – старший редактор Ask.Audio.

Логика в области компьютерных наук и искусственного интеллекта Intelligence

COMP 409/509: логика в компьютерных науках и искусственном интеллекте Интеллект Составлено Моше Ю.Варди, который не уважает тех, кто не уважает логику.P.R.H. АнонимныйЕсли вы считаете, что ваша статья пуста,

Используйте функциональное исчисление первого порядка.

Тогда это становится логикой,

И, как по волшебству,

Очевидное провозглашается чудесным.

Логику называют «исчислением информатики». Аргумент состоит в том, что логика играет фундаментальную роль в компьютере. наука, подобная той, в которую играют исчисления в физических науках и традиционные инженерные дисциплины.Действительно, логика играет важную роль в таких разных областях компьютерных наук, как искусственный интеллект (автоматическое мышление), архитектура (логические вентили), программная инженерия (спецификация и верификация), языков программирования (семантика, логическое программирование), базы данных (реляционная алгебра и SQL), алгоритмы (сложность и выразительность), и теория вычислений (общие понятия вычислимости).

COMP 409/509 дает студенту подробное введение в вычислительная логика, подробно охватывающая темы синтаксиса, семантика, процедуры принятия решений, формальные системы и определимость как для логики высказываний, так и для логики первого порядка.Материал преподается с точки зрения информатики, с упором на алгоритмы автоматического мышления. Цель – подготовить студентов к использованию логики в качестве формального инструмента. в области информатики в целом и искусственного интеллекта в частности.

Материал курса:

Ссылки

В 2005 году: Курс предлагается осенью.Весной эта веб-страница неактивна.

логических уровней – learn.sparkfun.com

Добавлено в избранное Любимый 73Уровни логики TTL

Большинство используемых нами систем используют уровни TTL 3,3 или 5 В. TTL – это аббревиатура от Transistor-Transistor Logic. Он основан на схемах, построенных на биполярных транзисторах для переключения и поддержания логических состояний. Транзисторы в основном представляют собой переключатели с электрическим управлением.Для любого логического семейства необходимо знать несколько уровней порогового напряжения. Ниже приведен пример стандартных уровней TTL 5 В:

В OH – Минимальный уровень выходного напряжения, который устройство TTL обеспечивает для сигнала ВЫСОКОГО уровня.

В IH – Минимальный уровень ВХОДНОГО напряжения считается ВЫСОКИМ.

В OL – Максимальный ВЫХОДНОЙ уровень напряжения, который устройство обеспечивает для НИЗКОГО сигнала.

В IL – Максимальный уровень входного напряжения все еще считается НИЗКИМ.

Вы заметите, что минимальное выходное ВЫСОКОЕ напряжение (В OH ) составляет 2,7 В. В основном это означает, что выходное напряжение устройства, управляющего ВЫСОКИМ, всегда будет не менее 2,7 В. Минимальное входное ВЫСОКОЕ напряжение (В IH ) ) равно 2 В, или в основном любое напряжение, которое составляет не менее 2 В, будет считываться как логическая 1 (ВЫСОКАЯ) для устройства TTL.

Вы также заметите, что существует подушка 0,7 В между выходом одного устройства и входом другого. Иногда это называют запасом шума.

Аналогично, максимальное выходное НИЗКОЕ напряжение (В OL ) составляет 0,4 В. Это означает, что устройство, пытающееся отправить логический 0, всегда будет ниже 0,4 В. Максимальное входное НИЗКОЕ напряжение (В IL ) составляет 0,8. V. Таким образом, любой входной сигнал ниже 0,8 В будет по-прежнему считаться логическим 0 (НИЗКИЙ) при считывании в устройство.

Что произойдет, если у вас напряжение между 0,8 В и 2 В? Что ж, ваше предположение так же хорошо, как и мое. Честно говоря, этот диапазон напряжений не определен и приводит к недопустимому состоянию, часто называемому плавающим.Если выходной контакт на вашем устройстве «плавает» в этом диапазоне, нет уверенности в том, к чему приведет сигнал. Он может произвольно колебаться между HIGH и LOW.

Вот еще один способ взглянуть на допуски ввода / вывода для обычного устройства TTL.

← Предыдущая страница

Актив-низкий и активный-высокий

VocALign ARA2 для Logic Pro уже доступен – Блог

VocALign ARA2 для Logic Pro уже доступен

Мы очень рады сообщить о выходе новых ARA2 версий VocALign Project и VocALign Pro для Logic Pro 10.5.1 или новее теперь доступны на нашей странице загрузки. Это означает, что пользователи Logic Pro теперь могут выравнивать свой вокал быстрее, чем когда-либо, всего несколькими щелчками мыши.

Что такое ARA?

Если вы его пропустили, ARA или Audio Random Access – это революционное расширение звукового плагина, которое обеспечивает беспрецедентную мгновенную связь между плагинами с поддержкой ARA и DAW.

Чем полезна ARA?

Огромное преимущество экономии времени для пользователей VocALign заключается в том, что больше нет необходимости в захвате звука в реальном времени, поскольку аудиофайлы могут быть мгновенно захвачены и возвращены в DAW.С ARA2 в Logic рабочий процесс выглядит следующим образом:

Обратите внимание, что на приведенном выше видео показана работа с VocALign Pro, но основной процесс такой же, как и с VocALign Project, вам просто нужно захватить вокал, который вы хотите выровнять отдельно.

Подводя итог, ваш вокал отправляется в VocALign по:

- Сначала выбираем звуковые дорожки в Logic.

- Затем нажмите

, а затем быстро в Logic. - Затем выберите Guide audio e.грамм. ведущий вокал и нажмите кнопку Capture Guide в VocALign.

- Наконец, выберите Dub аудио, например. бэк-вокал в Logic и нажмите кнопку Capture Dub в VocALign.

Дубляж будет мгновенно согласован с Руководством и автоматически возвращен в Logic Pro X.

Весь процесс занимает всего несколько секунд, и более того, в VocALign Pro вы можете выбирать, записывать и выравнивать несколько копий одновременно.

ФункциональностьVocALign ARA2 уже доступна в совместимых DAW VST3, таких как Cubase, Studio One, Reaper и Cakewalk от Bandlab.

Доступны бесплатные 14-дневные демонстрационные версии, а VocALign ARA2 for Logic – бесплатное обновление для зарегистрированных владельцев.

Процедура установки VocALign ARA AU

В связи с тем, как Apple решила реализовать ARA, в настоящее время необходимо выполнить несколько дополнительных шагов для установки наших подключаемых модулей ARA в Logic:

- Установите версию аудиоустройства ARA2 вашего продукта VocALign, которую можно найти на нашей странице загрузки

- Стартовая логика

- В Logic откройте любой проект или создайте пустой

- Добавьте базовую (не-ARA) версию VocALign AU в качестве вставки на любой трек в проекте, на этом этапе вы не увидите версию (и) VocALign ARA

- Выйти из логики без сохранения

- Перезапустить логику.Logic теперь должен распознавать версии подключаемых модулей AU и ARA, и они обе должны появиться в диспетчере подключаемых модулей Logic. К имени ARA-версии подключаемого модуля добавлено «(ARA)».

Важное примечание

Перед тем, как начать пробовать наши плагины VocALign ARA2 для Logic, обязательно прочтите инструкции.

Самое главное не забудьте нажать

Один простой трюк для записи вокала в Logic Pro X! – RobPRocks.com

Мне очень приятно сообщить, что я нашел решение одной из моих самых больших проблем при переходе с Pro Tools на Logic Pro X! (Я сравнил их в предыдущем посте). Эффективный рабочий процесс, на который я полагался при записи вокала в Pro Tools, стал неудобным в LPX, но после нескольких глубоких погружений в группы пользователей и форумы я наткнулся на одну маленькую особенность, которая изменила правила игры.Да, как и в случае с заголовками кликбейтов в Интернете, я обнаружил «одну простую уловку», позволяющую улучшить ваш голосовой рабочий процесс.

Чтобы сэкономить ваше время, уловка – это функция «Pack Take Folder», и если вы хотите пропустить мое объяснение того, как ее использовать, перейдите к разделу «Pack Take Folder» ниже. Сначала я объясню, почему я вообще искал что-то подобное и почему это было так важно для меня при записи вокала.

Проблема

Как я упоминал в своем эссе по сравнению PT и LPX, способ, которым LPX автоматически создает папки дублей, делает рабочий процесс записи вокала абсолютным беспорядком.Каждый раз, когда вы вставляете вокальную дорожку, даже если это всего лишь пара слов или один куплет, он создает новый дубль, добавляя к вертикальной стопке дублей и заполняя пространство экрана. Чем больше занимает экран, тем труднее скомпилировать финальную вокальную дорожку, потому что вы постоянно прокручиваете вверх и вниз к разделам аудио для прослушивания. Даже если у вас включена функция «Заменить запись», которая должна записывать новый звук в текущую дорожку, она работает только в первый раз в песне.После того, как вы создадите папку дублей и начнете второе полноценное вокальное исполнение, каждый удар, даже с включенной функцией Replace Record, создает новый дубль. И эти дубли быстро складываются.

Ни в одном из руководств, которые я видел по созданию вокала в LPX, эта проблема не рассматривалась. У каждого из них были певцы, которые с радостью пели всю песню три или четыре раза, в результате чего в папке дублей оставалось всего три или четыре дубля. Кто так записывает? Невозможно добиться наилучшего исполнения, пропев всю песню целиком несколько раз.Вам нужно будет нажать на кнопку, чтобы подобрать слово или фразу. Главный вокал подобен кадру крупным планом в кино, каждая деталь и нюанс увеличены, и вам нужно добиться наилучшего и наиболее убедительного исполнения для каждой строчки.

Вертикально расположенные папки дублей занимают место в Logic Pro X.В Pro Tools вы можете вручную создать новый дубль (их термин – «список воспроизведения») и вставлять в него по мере необходимости. Вы можете потратить время на то, чтобы получить хорошую полную версию песни – строчку за строчкой, если хотите, – прежде чем приступить к следующему полноценному исполнению.Этот процесс дает вам четыре или пять (или сколько угодно) исполнений всей песни, и когда приходит время компилировать вокальную дорожку, вам нужно только перемещаться по четырем или пяти дорожкам, расположенным вертикально.

Было невероятно обидно и почти нарушило условия сделки, что невозможно было использовать этот рабочий процесс записи голоса Pro Tools в Logic Pro X.

Кроме того, вы можете.

Используя этот простой трюк! Функцию «Упаковать и взять папку», скрытую во всплывающем меню, можно получить, только щелкнув несколько аудиорегионов!

Скрывается во всплывающем меню, только когда выбрано несколько аудио регионов!Папка для сбора пакетов

Чтобы использовать эту функцию, чтобы сделать запись голоса в Logic Pro X более похожей на Pro Tools, вам необходимо записывать каждое вокальное исполнение на новую дорожку.Когда у вас есть все ваши полнометражные выступления там, где вы хотите – исправляя ошибки, переходя стих за стихом, что угодно, – вы используете «Pack Take Folder», чтобы объединить треки в папку дублей. Оттуда вы можете использовать Quick Swipe Comping, чтобы скомпилировать финальную вокальную дорожку. Уточню:

Первым шагом в этом рабочем процессе является установка LPX в режим «замена записи», чтобы вы могли вставлять вокальную дорожку без создания новых дублей. Вы можете записывать по одному куплету за раз, вставлять, чтобы исправить взорванную ноту или плохую дикцию, и все это без создания новой папки дублей.Бери папки – твой враг (пока)!

Когда вы довольны первым полноценным исполнением песни и хотите начать второе, вместо создания нового дубля продублируйте всю вокальную дорожку. Я делаю это, щелкая заголовок дорожки вокального трека и перетаскивая его вниз, пока вы не увидите прозрачную копию дорожки, плавающую под вашей мышью. Отпустите кнопку мыши, и новый трек будет создан с теми же плагинами и отправками по шине. Я переименовал треки «vox take 1», «vox take 2» и т. Д., удалите скопированные аудиорегионы на новой дорожке, отключите звук предыдущей дорожки и затем начните запись.

Вы можете пробивать каждый трек по мере необходимости, получая полезные полные характеристики на каждом. Повторяйте этот процесс до тех пор, пока вы не будете уверены, что у вас достаточно хороших исполнений всей песни, чтобы сделать финальную композицию, или пока ваш певец не сдастся и не скажет: «Сделай так!»

Теперь пришло время упаковать Take Folder, функцию, настолько похороненную, что я не знал, что она существует целый проклятый год. Щелкните заголовки дорожек всех ваших вокальных дорожек с зажатой клавишей Shift, чтобы выбрать все звуковые регионы на всех дорожках (они должны быть выделены).Затем щелкните правой кнопкой мыши (или щелкните правой кнопкой мыши) одну из выделенных звуковых областей, чтобы открыть всплывающее меню. Выберите слово «Папка» в нижней части всплывающего меню для подменю, затем выберите «Упаковать и взять папку». Вы также можете нажать Command-Option-Control-F, если у вас достаточно пальцев и вы это помните.

Теперь все ваши отдельные вокальные треки перемещены в папку дублей на верхнем треке. Новая папка дублей ведет себя так же, как и любая другая, позволяя выполнять Quick Swipe Comp, создавать альтернативные композиции и т. Д.

Очистка вокального рабочего процесса

После того, как вы собрали вокальную композицию (существует множество руководств по компиляции), есть еще один шаг, отражающий рабочий процесс Pro Tools: экспорт скомпилированного вокала в новую дорожку. Для этого щелкните букву вверху папки дублей, чтобы открыть раскрывающееся меню, а затем выберите «Экспортировать активную композицию в новую дорожку». Это создает новую дорожку с скомпилированным вокалом в качестве звуковых регионов, а не папки дублей. Вам нужно сделать это, чтобы убрать тишину, добавить затухание в начало и конец каждой звуковой области, а также выполнить другие операции по очистке вокала, которые вам нужно сделать перед микшированием.Я предпочитаю экспортировать композицию, а не сглаживать ее, потому что, как только вы сгладите композицию, вы не сможете вернуться! Я сохраняю исходный скомпилированный вокальный трек, содержащий папку дублей (и, конечно, отключу его) на случай, если я захочу вернуться и выбрать другой дубль для слова или строки, что, если вы записываете для клиентов, они буду всегда делать захочется.

Вот и все: один простой прием, который очень помог мне, упростив мой вокальный рабочий процесс и сделав его более эффективным и похожим на Pro Tools.Я по-прежнему предпочитаю, как Pro Tools обрабатывает плейлисты, а не дубль-папки Logic Pro X, но с этим обходным решением разница гораздо более управляема, и, что наиболее важно, страх перед громоздкой дубл-папкой не помешает мне попытаться вставить строку просто верно.

Сообщите мне, работает ли этот процесс для вас или у вас есть какие-либо мысли, вопросы или предложения!

Я также разместил это на Medium и linkedin, потому что, ну, в социальных сетях.

УчебникLogic: станьте опытным пользователем. Часть 2 – Quick Swipe Comping

Использование всей мощи Quick Swipe Comping позволяет вашим сессиям проходить более плавно и эффективно.Марк Казинс оттачивает свое выступление.

Если вам не повезло работать с музыкантом, который постоянно доставляет «чудеса одного дубля», весьма вероятно, что ваша законченная запись будет составлена из мозаики из разных дублей. Однако использование функции Quick Swipe Comping в Logic Pro X может значительно упростить задачу записи и сборки готовой «композиции», позволяя вам записывать несколько дублей и относительно легко переключаться между ними. Тем не менее, хотя базовую компоновку достаточно легко достичь, стоит взглянуть на некоторые более глубокие функциональные сложности Quick Swipe Comping, чтобы максимально использовать эту важную функцию.

По сути, функция Quick Swipe Comping – это удобный способ записи нескольких проходов одной и той же музыкальной партии, будь то вокал или партия инструмента. На верхнем уровне регион может казаться любой другой аудиозаписью, но разверните папку Take, и вы увидите полную серию дублей вместе с точными точками редактирования, используемыми для создания финальной композиции. Эта функция не только упрощает работу с несколькими дублями, но также позволяет с легкостью экспериментировать с различными точками редактирования, вплоть до возможности создания нескольких композиций с разными названиями из одного и того же материала.

Однако, как мы увидим, запись и создание вашей композиции – это только начало процесса компиляции. После того, как вы внесли изменения, вам необходимо рассмотреть варианты того, как аудио будет размещаться в вашем сеансе. Одним из вариантов может быть «сглаживание» композиции – процесс, который отображает ее как серию регионов, которые затем можно отполировать и усовершенствовать с помощью обычных инструментов редактирования звука Logic Pro X. Если вы хотите сохранить возможность вернуться к исходной композиции позже, стоит изучить такие параметры, как «Экспорт активной композиции в новую дорожку».

Немного попрактиковавшись, вы скоро начнете записывать, редактировать и выравнивать свои собственные композиции, сохраняя чистоту области треков и создавая почти идеальное исполнение.

Работа с комбайнами

1: Каждый раз, когда вы записываете поверх существующего исполнения, Logic создает так называемую папку дублей. Система папок дублей полезна как для обработки нескольких различных дублей одной и той же музыкальной партии, так и для создания композиций, при которых вносятся правки для переключения между разными фразами или словами в исполнении.

2: Папка Take выглядит иначе, чем обычная звуковая область – обратите внимание на добавление некоторых важных значков, добавленных в ее верхний левый угол. Стрелка, например, позволяет свернуть или развернуть папку, отображая различные исходные дубли, а также точку редактирования (обозначенную цветной штриховкой), используемую для переключения между различными исполнениями.

3: щелчок по второму значку открывает меню Quick Swipe Comping, в котором есть ряд функций и функций, позволяющих прослушивать и редактировать дубли.Например, на самом верхнем уровне вы можете увидеть каждый дубль. Это отличный способ прослушивания каждого выступления, независимо от того, насколько далеко вы зашли в монтажный процесс.

4: Чтобы создать свою композицию, выберите в раскрывающемся меню опцию «Создать новую композицию». Первая композиция с префиксом A создается в результате вашей записи. Ваша новая композиция с префиксом B может быть создана путем перетаскивания точек редактирования или щелчка и перетаскивания соответствующего дубля. Финальный дубль можно увидеть на верхнем уровне.

5: Теоретически после создания композиции вы можете оставить папку дублей как есть. Однако существует ряд ситуаций, в которых вы можете захотеть сгладить, экспортировать или распаковать композицию. Сглаживание композиции (через меню Quick Swipe Comping) особенно полезно, когда вы хотите улучшить кроссфейды между дублями.

6: Сглаживание композиции приведет к рендерингу редактирования как серии регионов на одной дорожке с предопределенным кроссфейдом между каждым дублем.В большинстве случаев кроссфейд по умолчанию подойдет, но если вы сгладили композицию, вы можете использовать инструмент Crossfade (или изменение размера области в режиме X-Fade Edit), чтобы вручную настроить каждую точку редактирования.

7: Единственным недостатком процесса выравнивания является то, что вы теряете возможность вернуться к Quick Swipe Comp позже в процессе производства. Альтернативой является использование опции меню «Экспортировать активную композицию в новую дорожку», которая создает плоскую композицию на соседней новой дорожке.Просто отключите исходную дорожку, чтобы не слышать одновременное воспроизведение двух треков.

8: Если вы хотите получить полный доступ к содержимому папки Take, вам нужно будет использовать опцию Unpack. Использование Unpack будет рендерить все текущие композиции, а также размещать каждый дубль на отдельной дорожке. Это полезно, если вы хотите исследовать совершенно другое творческое направление с записанным вами исходным материалом.

9: Как мы видели во всех вариантах распаковки и выравнивания, финальная композиция рендерится с серией кроссфейдов по умолчанию.Настройка времени кроссфейда по умолчанию является частью Logic’s Preferences, находящейся на вкладке General в Audio Preferences. Значение по умолчанию – 10 мс, что обычно подходит для большинства операций редактирования.

10: Сопоставить между дублями достаточно просто, но что, если вам нужно пропустить дубль или его часть вовремя? Хитрость здесь в том, что можно отключить редактирование Quick Swipe Comping как часть папки Take. Вы можете сделать это, щелкнув третий значок в верхнем левом углу, переключив его в режим «Ножницы».

11: Если функция Quick Swipe Comping отключена, вы сможете использовать стандартные инструменты редактирования Logic – в частности, инструменты «Ножницы» и «Указатель» – как средства вырезания и изменения положения любых дублей. Обратите внимание, как композиция остается на месте – вы просто редактируете папку дублей через другой портал.

12: Если вы хотите переместить композицию в другую DAW, стоит знать, как визуализировать ее как один непрерывный файл. Один из вариантов – использовать функцию Flatten and Merge, которая сгладит и отразит готовую композицию как новый аудиофайл.Если вы уже выполнили сглаживание, рассмотрите возможность использования функции соединения для достижения той же цели.

.

16-Д

16-Д 16-Д

16-Д 14-В

14-В

14-В

14-В 16-Д

16-Д д. Так же проблемой бывает подобрать отечественный аналог для импортной микросхемы, и наоборот. В этой статье сделана попытка предоставить такую информацию.

д. Так же проблемой бывает подобрать отечественный аналог для импортной микросхемы, и наоборот. В этой статье сделана попытка предоставить такую информацию.

2-3V

2-3V

3V и 2.5V, с 3.6V-толерантными входами и выходами.

3V и 2.5V, с 3.6V-толерантными входами и выходами.