Универсальный JK-триггер.

Триггер такого типа имеет два информационных входа J и K, динамический тактовый вход С и статические входы R, S. При этом входы R и S имеют приоритет над всеми остальными входами. Это делает его похожим на RS-триггер, однако у него благодаря наличию входов J и K все-таки есть целый ряд отличий. Специфика работы такого триггера следующая.

Вход J (от англ. Jump — прыжок) аналогичен входу S у RS-триггера. Если подать на него логическую единицу при К=0, то при совпадении этого сигнала по времени (момент t1 на диаграмме рис.7) с сигналом синхронизации С, выход Q перейдет в состояние логической 1. Вход K (от англ. Kill — отключение) аналогичен входу R у RS-триггера. Если подать на этот вход логическую 1 при J=0 (момент времени t2 на диаграмме), то выход Q перейдет в состояние логического 0. Логика работы JK-триггера такова, что при подаче логической единицы на оба входа J и K состояние выхода триггера изменяется на противоположное (момент времени t3 на диаграмме).

Рисунок 7 – Условное обозначение и временная диаграмма JK -триггера

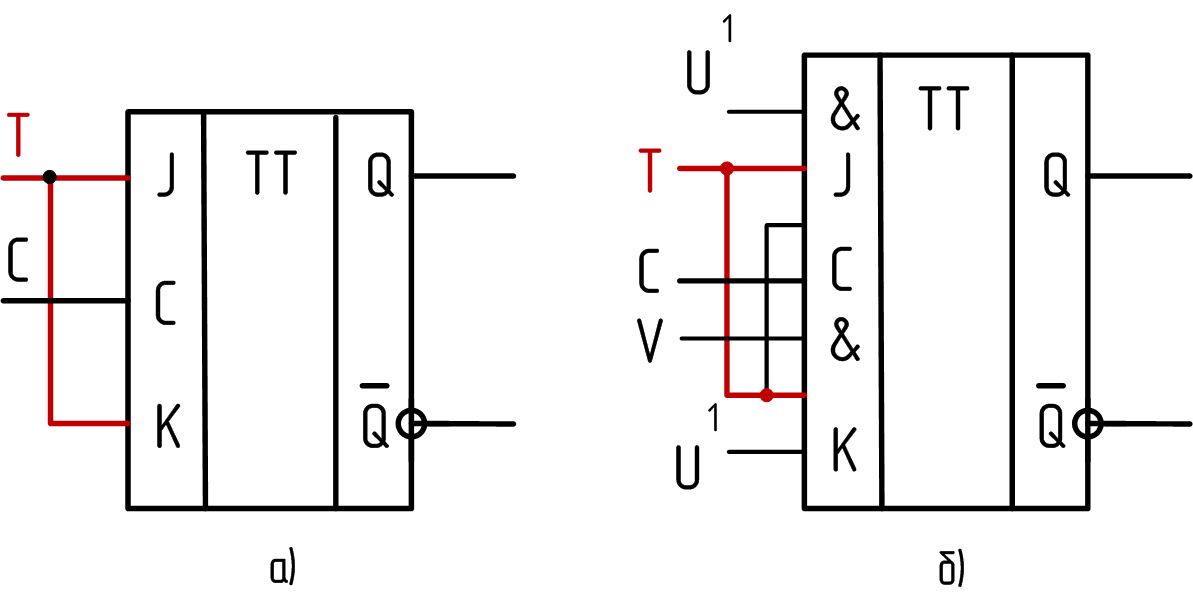

JK-триггер называют универсальным из-за того, что из него легко можно получить D-триггер или Т-триггер. Он переходит в инверсное состояние каждый раз при одновременной подаче на входы J и K логической 1. К примеру, если объединить эти входы, то получим Т-триггер

Вопросы

1. Дайте определение триггеру.

2. Чем различаются асинхронный и синхронный триггеры?

3. Чем различаются статический и динамический триггеры?

4. При каком условии на прямом выходе асинхронного RS-триггера будет 1?

5. При каком условии на прямом выходе асинхронного RS-триггера будет 0?

При каком условии на прямом выходе асинхронного RS-триггера будет 0?

Тема 15 Системы автоматики и их элементы

План

1. Виды, структурные схемы и особенности систем автоматики.

2. Элементы систем автоматики

3. Реле

1.Виды, структурные схемы и особенности систем автоматики.

Автоматизация производственных процессов облегчает условия работы людей, повышает производительность труда, надежность работы производственных машин и механизмов, улучшает качество продукции, уменьшает расход материалов и энергии.

Различают следующие системы автоматики:

1. Системы автоматического контроля (измерения)

2. Системы автоматического управления

3. Системы автоматического регулирования

В автоматике применяют пневматические, гидравлические, механические, электронные, оптические и другие элементы, но самыми многочисленными являются электрические и магнитные элементы.

По структуре системы автоматики могут быть замкнутые и разомкнутые. Замкнутые системы имеют цепь обратной связи.

Система автоматического контроля (САК) предназначена для автоматического контроля различных физических величин (параметров), сведения о которых необходимы при управлении объектом.

Рисунок 1 – Структурная схема системы автоматического контроля

ОК – объект контроля (уровень жидкости, температура, давление и т.д.)

ИП – измерительный преобразователь. Он воспринимает измеряемую величину преобразует ее в электрическую величину. В связи с теми функциями, которые выполняют измерительные преобразователи, их еще называют чувствительными элементами или датчиками.

КС – канал связи. Он может содержать усилительные элементы, шифраторы, дешифраторы и др.

УО – управляющий орган

ВО – воспринимающий орган.

Конечные элементы ВО или УО на объект контроля никакого обратного воздействия не оказывают, т. е. система автоматического контроля разомкнутая.

е. система автоматического контроля разомкнутая.

Система автоматического управления предназначена для частичного или полного (без участия человека) управления объектом либо технологическим процессом. Эти системы широко применяют для автоматизации, например, процессов пуска, регулирования частоты вращения и реверсирования электродвигателей в электроприводах всех назначений.

Данная схема является разомкнутой. В такой системе управления функция контроля отсутствует. На управляющий орган УО воздействует оператор или сигнал через задающий орган ЗО поступает сигнал от другой системы автоматики. Задание оператора может быть введено в соответствии с ранее подготовленной программой, например включить или выключить электродвигатель, закрыть или открыть задвижку в водопроводе или газопроводе и т.д.

Управляющий сигнал через канал связи КС поступает на исполнительный орган ИО (если не требуется предварительная расшифровка и усиление сигнала), который воздействует на объект управления ОУ.

Разновидностью подобной системы автоматического управления является система автоматической защиты, назначение которой – прервать процесс при возникновении того или иного предельного режима.

Система автоматического регулирования(САР) поддерживает регулируемую величину в заданных пределах.

Рисунок 3 – Структурная схема системы автоматического регулирования

Система автоматического регулирования объединяет в себе функции контроля и управления, в ней осуществляется замкнутая цепь воздействий: объект регулирования – измерительный преобразователь – управляющий орган – исполнительный орган, который снова воздействует на объект управления.

Измерительный преобразователь ИП измеряет регулируемую величину и преобразует ее в величину другого вида, более удобную для воздействия на управляющий орган УО.

Управляющий орган воспринимает воздействие и срабатывает при достижении одного из заданных значений регулируемой величины, т. е. дает команду на работу исполнительного органа ИО, который в свою очередь, воздействует нужным образом на объект регулирования ОР.

е. дает команду на работу исполнительного органа ИО, который в свою очередь, воздействует нужным образом на объект регулирования ОР.

Если разность между верхним и нижним пределами регулируемой величины сокращать, то можно представить себе систему, которая поддерживает с определенной точностью одно заданное значение регулируемой величины (уровня жидкости, скорости вращения вала или других величин).

К системам автоматического регулирования относятся также: система программного регулирования, в которой все операции управления выполняются по заранее заданной программе; следящая система, воспроизводящая на выходе с определенной точностью входное задающее воздействие, изменяющееся по заранее неизвестному закону.

Узнать еще:

JK-триггер. Чем он отличается от остальных триггеров?

Устройство и принцип работы JK-триггера

Наиболее сложный по конструкции триггер широко используется в цифровой технике благодаря своей универсальности. Это, так называемый, JK-триггер.

Это, так называемый, JK-триггер.

К уже известным входам R (Reset) – сброс, S (Set) – установка, С – тактовый вход добавлены ещё два. Это входы J (Jump) и K (Kill).

Благодаря наличию этих дополнительных входов появляется возможность несложными схемными средствами достигать интересных результатов.

Логика работы основных входов (C, J, K) реализована следующим образом. Если на входе J высокий потенциал, а на входе K – ноль, то триггер установится в единичное состояние по спаду тактового импульса на входе С. Если на входе J – ноль, а на входе К высокий потенциал то по спаду тактового импульса триггер “сбросится” в нулевое состояние. Когда J=K=0 независимо от тактовых импульсов состояние триггера не меняется.

Благодаря такой логике работы появляется возможность довольно гибко настраивать алгоритм работы триггера. Такая универсальность позволяет использовать JK-триггер в устройствах со сложной логикой работы.

На JK-триггерах несложно реализовать делитель частоты на десять. Если мы подадим на вход импульсы с частотой 10 кГц, то на выходе получим уже 1 кГц. Такие схемы называют декадным делителем или декадой.

Делители с различным коэффициентом пересчёта раньше активно использовались радиолюбителями при изготовлении электронных часов и несложных музыкальных инструментов. Данная схема очень неэкономична и займёт много места, если собирать её на дискретных элементах, так как в ней используется четыре триггера и элемент 2И.

В широко распространённую серию К155 на базе ТТЛ логики входит универсальный JK-триггер К155ТВ1 (КМ155ТВ1). Зарубежными аналогами этой микросхемы являются SN7472N, 7472, SN7472J. Этот триггер построен по двухступенчатой схеме и имеет сложную входную логику, где три входа J и три входа K объединены по схеме логического И. Кроме того триггер имеет прямой и инверсный выходы, входы установки и сброса (S и R) и вход тактовых импульсов С. Вот так он обозначается на схеме.

Зарубежными аналогами этой микросхемы являются SN7472N, 7472, SN7472J. Этот триггер построен по двухступенчатой схеме и имеет сложную входную логику, где три входа J и три входа K объединены по схеме логического И. Кроме того триггер имеет прямой и инверсный выходы, входы установки и сброса (S и R) и вход тактовых импульсов С. Вот так он обозначается на схеме.

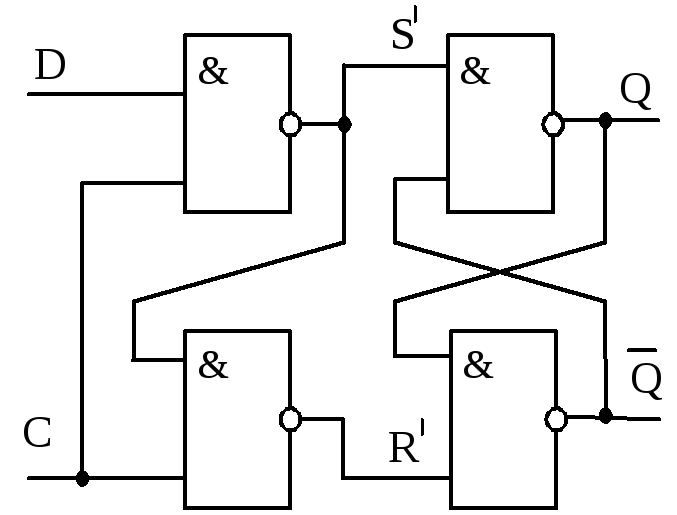

Вот так выглядит его внутренняя структура. Те, кто знаком с базовыми логическими элементами и устройством простейшего RS-триггера разберутся в устройстве JK-триггера без особых трудностей.

Этот триггер, как видно на схеме, организован на основе логических элементов И – НЕ с различным числом входов. В схеме присутствуют элементы: 2И – НЕ, 3И – НЕ, и 6И – НЕ. Наличие элементов 6И – НЕ, а также двухступенчатой структуры делает триггер многоцелевым и универсальным. В зависимости от конечной задачи, входы триггера могут объединяться или подключаться к другим логическим элементам схемы.

На микросхеме К155ТВ1 можно собрать несложную схему наглядно демонстрирующую работу JK-триггера. Как у почти всех микросхем этой серии 7 вывод – это корпус, а 14 вывод – это напряжение питания +5V. На 12 вывод (вход тактовых импульсов), и на прямой и инверсный выходы триггера, (выводы 8 и 6), необходимо подключить светодиоды через токоограничивающие резисторы.

После подключения питания один из выходных светодиодов загорается. Теперь можно проверить работу триггера по входам установки и сброса. Для этого необходимо поочерёдно подавать на выводы 2 (R) и 13 (S) низкий потенциал или “корпус”.

Светодиодные индикаторы будут попеременно загораться и гаснуть, индицируя в каком состоянии находится триггер. Это проверка работоспособности. Теперь можно посмотреть работу триггера в счётном режиме. Для этого можно объединить входы J и K и соединить их с напряжением питания +5V через резистор.

Этого можно и не делать. По определению любой вывод микросхемы ТТЛ-логики, если он просто “висит” в воздухе и никуда не подключен, находится под высоким потенциалом (уровень логической единицы). Соединение свободных выводов микросхем с плюсом источника питания производится для предотвращения случайных срабатываний, то есть для повышения помехозащищённости.

По определению любой вывод микросхемы ТТЛ-логики, если он просто “висит” в воздухе и никуда не подключен, находится под высоким потенциалом (уровень логической единицы). Соединение свободных выводов микросхем с плюсом источника питания производится для предотвращения случайных срабатываний, то есть для повышения помехозащищённости.

Теперь можно подать на вход С импульсы такой частоты, чтобы их было визуально видно по работе светодиода HL1. Светодиоды, подключенные к выходам триггера, будут срабатывать с частотой в два раза меньше. То есть в этом режиме JK-триггер делит частоту входного сигнала на два.

Для тестирования триггера понадобится источник внешнего тактового сигнала, чтобы подать последовательность импульсов на вход C.

Простейший генератор прямоугольных импульсов можно собрать, используя микросхему К155ЛА3.

Она содержит четыре элемент 2И – НЕ. Для генератора достаточно двух элементов. Период следования импульсов можно ориентировочно рассчитать по формуле T=1,4*R1*C1. Частота генератора прямоугольных импульсов в таком случае приблизительно будет равна f = 1/T. Для тех номиналов резистора R1 и конденсатора C1, что показаны на схеме, период генератора ориентировочно равен: T = 1,4 * 1000 * 0,00047 = 0,658 (с). Частота f = 1/0,658 = 1,5197… ~ 1,5 (Гц). В дальнейшем этот простейший генератор можно использовать для проверки работоспособности различных цифровых устройств.

Частота генератора прямоугольных импульсов в таком случае приблизительно будет равна f = 1/T. Для тех номиналов резистора R1 и конденсатора C1, что показаны на схеме, период генератора ориентировочно равен: T = 1,4 * 1000 * 0,00047 = 0,658 (с). Частота f = 1/0,658 = 1,5197… ~ 1,5 (Гц). В дальнейшем этот простейший генератор можно использовать для проверки работоспособности различных цифровых устройств.

Главная » Цифровая электроника » Текущая страница

Также Вам будет интересно узнать:

14 Триггеры – СтудИзба

Тема: Триггеры.

Вопрос 1.

Триггерами называют электронные устройства, обладающие двумя состояниями устойчивого равновесия и способные под воздействием управляющего сигнала переходить скачком из одного состояния в другое. Каждому состоянию триггера соответствует определенный (высокий или низкий) уровень выходного напряжения, который может сохраняться как угодно долго. Поэтому триггеры относятся к цифровым автоматам с памятью. В настоящее время триггеры выполняются на основе логических элементов в виде интегральных микросхем (ИМС). Они включены почти во все серии ИМС.

Поэтому триггеры относятся к цифровым автоматам с памятью. В настоящее время триггеры выполняются на основе логических элементов в виде интегральных микросхем (ИМС). Они включены почти во все серии ИМС.

Триггеры применяются как переключающие элементы самостоятельно или входят в состав более сложных цифровых устройств, таких как счетчики, делители частоты, регистры и др.

В общем случае триггер имеет два выхода: прямой (Q) и инверсный (), сигналы на которых противоположны по уровню. Количество входов триггера зависит от его типа. Входы делятся на информационные и командные.

По способу записи информации триггеры делятся на асинхронные, у которых информационные и командные входы совмещены, и синхронные или тактируемые. Последние срабатывают только при поступлении на один из командных входов (синхровход) разрешающего импульса.

По числу ступеней триггеры делятся на однотактные и двутактные. В однотактных информация на выходах появляется практически одновременно с приходом информационного или синхроимпульса. Такие схемы срабатывают по перепаду сигнала 0-1 (по фронту синхроимпульса). В двухтактных триггерах переключение элементов происходит в два приема и сигнал на выходе появляется с задержкой. Они срабатывают по перепаду сигнала 1-0 (по спаду импульса).

Такие схемы срабатывают по перепаду сигнала 0-1 (по фронту синхроимпульса). В двухтактных триггерах переключение элементов происходит в два приема и сигнал на выходе появляется с задержкой. Они срабатывают по перепаду сигнала 1-0 (по спаду импульса).

В зависимости от логической структуры схемы управления различают RS-, D-, T-, JK-триггеры и др.

Рекомендуемые файлы

Работа триггера может быть описана логическим уравнением, связывающим состояние входов и выходов триггера до его срабатывания (t) и после срабатывания (t+1). Состояние триггера можно задать таблицей переходов или временной диаграммой его работы.

Вопрос 2. RS – триггеры.

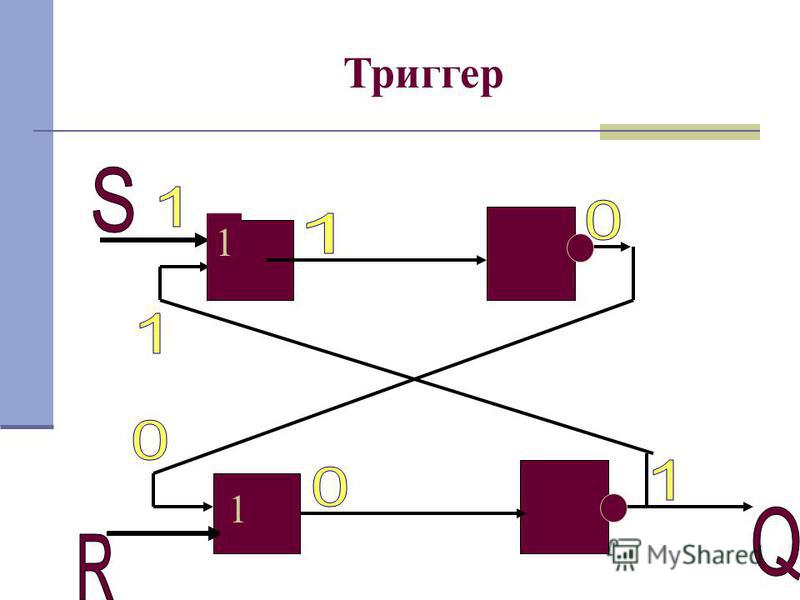

Асинхронный RS – триггер имеет два установочных входа R и S. Схема триггера на ЛЭ 2ИЛИ-НЕ и его условное обозначение показаны на рис.12.1. При S=R=0 схема устойчива. Это режим хранения информации. Если Q=1, то на входах DD2 оказываются 1 и 0, при которых =0.

Таблица 12.1

R | Qt+1 | |

1 | 0 | 0 |

0 | 1 | 1 |

0 | 0 | Qt |

1 | 1 | X |

На входах DD1 – 0,0, что сохраняет этот элемент с состоянии Q=1. Для изменения состояния триггера на его входы надо подать комбинацию сигналов R=1, S=0. Тогда на входах DD1 появятся высокие уровни и этот элемент перейдет в состояние Q=0. На входах DD2 установятся сигналы 0, 0 и логический элемент перейдет в состояние Q=1. Комбинация S=1, R=0 возвратит триггер в состояние Q=1, =0. При комбинации S=1, R=1 состояние триггера неопределенно, эта комбинация запрещена. Работа триггера иллюстрируется таблицей переключений (табл.12.1). Триггер с таким же законом работы можно выполнить на логических элементах 2И-НЕ.

Комбинация S=1, R=0 возвратит триггер в состояние Q=1, =0. При комбинации S=1, R=1 состояние триггера неопределенно, эта комбинация запрещена. Работа триггера иллюстрируется таблицей переключений (табл.12.1). Триггер с таким же законом работы можно выполнить на логических элементах 2И-НЕ.

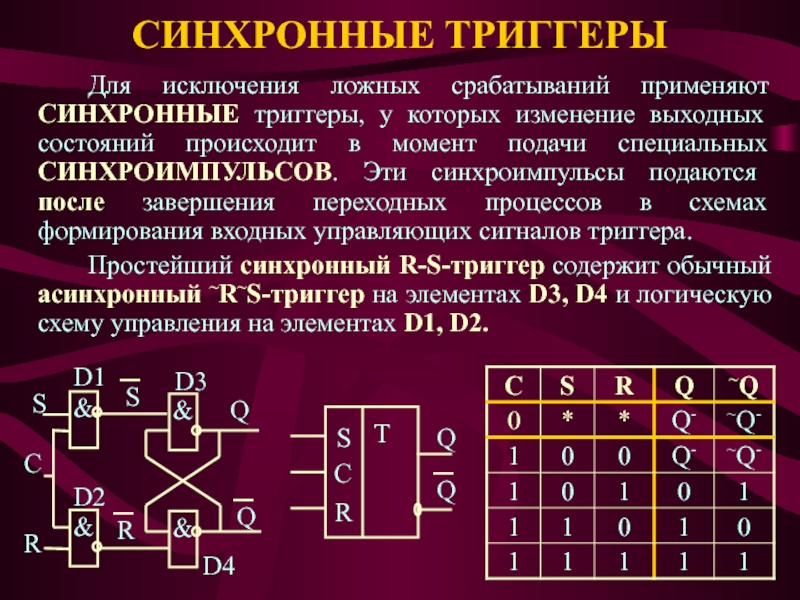

Синхронные RS – триггеры имеют два информационных входа R и S и синхровход С. Схема триггера и его условное обозначение показаны на рис.12.2. Асинхронный RS – триггер дополнен схемой управления на ЛЭ DD1-2, которая формирует сигналы и , поступающие на его установочные входы. Управление осуществляется низким уровнем сигнала (0), поэтому на входах показан знак инверсии. При =1 любая комбинация и дает на выходах 0, и асинхронный триггер на элементах DD3-4 находятся в режиме хранения информации. Схема управления сработает только при поступлении низкого уровня на синхровход (=0). Тогда =1 и =0 приведет к =0 и =1. Триггер перейдет с состояние Q=1, а при =0, =1 – в состояние Q=0. Комбинация ===0 запрещена. Так как при = 1 любое изменение сигналов на входах иигнорируется, синхронные триггеры защищены от воздействия помех.

Комбинация ===0 запрещена. Так как при = 1 любое изменение сигналов на входах иигнорируется, синхронные триггеры защищены от воздействия помех.

Вопрос 3. D – триггеры.

Синхронный D – триггер состоит из асинхронного RS-триггера и схемы управления на ЛЭ. Он имеет информационный вход D и синхровход С. Его схема и условное обозначение показаны на рис.12.3. ЛЭ DD3-4 представляют собой RS-триггер, управляемый инверсными сигналами. Его устойчивое состояние обеспечивается комбинацией 1. При С=0 выходах обоих ЛЭ И-НЕ DD1-2 независимо от значения сигнала на входе D будут поддерживаться высокие уровни и триггер сохраняет предыдущее состояние. С приходом синхроимпульса С=1, при D=1 =0, а =1, и RS-триггер оказывается в состоянии Q=1. При D=0 =1, =0, и триггер переходит в состояние Q=0. Это значение не может измениться до прихода следующего синхроимпульса. Поэтому D-триггеры называют триггерами задержки – они задерживают информацию на такт. На схеме пунктиром показан вход Е, объединяющий два дополнительных И-входа. Этот вход расширяет возможности схемы. Его называют разрешающим. При Е=1 триггер работает в нормальном режиме, Е=0 дает возможность сохранить информацию при изменении сигналов на D– и С-входах. Такой триггер называют DV-триггером с разрешающим входом.

На схеме пунктиром показан вход Е, объединяющий два дополнительных И-входа. Этот вход расширяет возможности схемы. Его называют разрешающим. При Е=1 триггер работает в нормальном режиме, Е=0 дает возможность сохранить информацию при изменении сигналов на D– и С-входах. Такой триггер называют DV-триггером с разрешающим входом.

Широкое применение получили двухтактны D – триггеры. Схема и условное обозначение приведены на рис.12.4а,б. Он состоит из D-триггера и синхронного RS-триггера с объединенными через инвертор С-входами. Принцип работы триггера можно проследить по временной диаграмме (рис.12.4в). Сигнал со входа D записывается в Т1 по фронту синхроимпульса. При этом С1=0 и Т2 сохраняет прежнюю информацию. После окончания синхроимпульса С=0, и Т1 отключается от D-входа, С1=1 и Т2 переписывает информацию их Т1.

Вопрос 4. JK – триггеры.

JK – триггеры.

JK – триггер является универсальным. Его условное обозначение приведено на рис.12.5а. Он имеет два установочных входа R и S, информационные входы J и K и синхровход С.

Установочные входы обладают приоритетом над другими. С их помощью триггер устанавливают в состояние Q=1 или Q=0 независимо от сигналов на всех других входах.

J– и K-входы работают по разрешающему импульсу на С-входе. При комбинации J=1 и K=0 на выходе Q=1. При J=0 и K=1 триггер переходит в состояние Q=0, а если J=K=1, то с приходом каждого синхроимпульса он меняет состояние. Работу триггера можно описать логическим уравнением

На основе JK-триггера можно построить любой другой тип триггера. Поэтому они массово производятся практически во всех сериях ИМС.

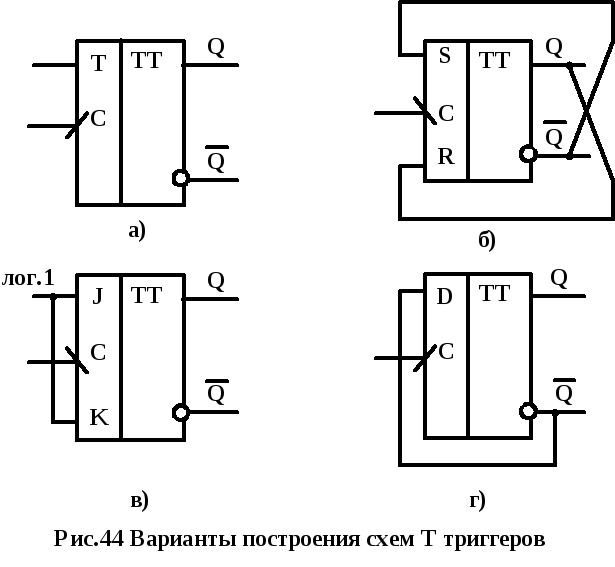

Вопрос 5. Т – триггеры.

Т-триггер или счетный триггер имеет один информационный вход Т. Каждый импульс на этом входе переводит его в новое состояние. Его логическое уравнение .Оно соответствует уравнению JK-триггера при K=J=1.

Каждый импульс на этом входе переводит его в новое состояние. Его логическое уравнение .Оно соответствует уравнению JK-триггера при K=J=1.

Такой же триггер можно получить на основе D-триггера (рис.12.5б). Поэтому производить Т-триггеры в виде самостоятельных изделий нет смысла и их нет в сериях ИМС.

Т-триггеры используются как делители частоты на 2 или счетчики по модулю 2.

Триггер типа ТV имеет, кроме информационного входа Т, разрешающий вход Е, уровень напряжения на котором запрещает или разрешает его работу.

Контрольные вопросы

1.Что называют триггером?

2. Как классифицируются триггеры по способу записи информации и по функциям?

3. Как работают RS-триггеры?

4. Чем отличаются D– и DV-триггеры?

Бесплатная лекция: “8 Понятие о рН” также доступна.

5. Зачем нужен разрешающий вход Е?

6. Почему JK-триггеры называют универсальными?

7. Для чего используют Т-триггеры?

Для чего используют Т-триггеры?

8. Как получить Т-триггер на основе D– или JK-триггеров?

9. Начертите схему делителя частоты на 8. Поясните его работу на временной диаграмме.

энциклопедия киповца

Триггер – это устройство, имеющее одно или два устойчивых состояния (выхода), из которых он выходит под воздействием определённых входных сигналов, после чего, в зависимости от входов и своего предыдущего состояния, триггер переходит в это же или другое устойчивое состояние.

Триггеры с одним устойчивым состоянием называются несимметричными и используются в качестве пороговых устройств, преобразователей сигналов произвольной формы в прямоугольные и т.д. Примером несимметричного триггера является триггер Шмитта.

Триггеры

с двумя устойчивыми состояниями

называются симметричными и обычно

используются в качестве элементов памяти

цифровых автоматов.

Далее будем рассматривать только симметричные триггеры.

В триггерах выделяют два вида входных сигналов: информационные и синхронизирующие.

Информационные сигналы определяют состояние триггера и присутствуют в любых триггерах. По типу информационных сигналов осуществляется классификация триггеров: D, T, RS, JK и т.д.Синхронизирующие сигналы не являются обязательными и вводятся в триггерах с целью фиксации момента перехода в новое состояние, задаваемое информационными входами. На синхровход триггера поступают тактирующие импульсы задающего генератора, синхронизирующего работу цифрового автомата. Период следования импульсов соответствует одному такту автоматного времени.

Триггеры,

у которых есть только информационные

сигналы называются асинхронными, а

триггеры, у которых есть и информационные

и синхронизирующие сигналы называются

синхронными.

D-триггер – это элемент задержки, он имеет один информационный вход D и один выход Q и осуществляет задержку поступившего на его вход сигнала на один такт.

Условное обозначение и таблица переходов D-триггера изображены на рисунке.

С- синхроввод (для синхронизирующего сигнала)

D – сигнал на информационном входе триггера в такте t.

Qt – выход триггера в такте t.

Qt+1 – выход триггера в такте t+1 (в следующем такте).

Проиллюстрируем таблицу переходов на временной диаграмме:

D1=0, Q1=0 => Q2=0

D2=1, Q2=0 => Q3=1

D3=1, Q3=1 => Q4=1

D4=0, Q4=1 => Q5=0

D1,D2,D3,D4

– состояние входов на соответствующих

тактах.

Q1,Q2,Q3,Q4,Q5 – состояние выходов на соответствующих тактах.

С – состояние синхроввода

T-триггер – триггер со счетным входом, он имеет один информационный вход T и один выход Q и осуществляет суммирование по модулю два значений сигнала T и состояния Q в заданный момент времени.

Условное обозначение и таблица переходов T-триггера изображены на рисунке.

RS-триггер – триггер с раздельными входами.Этот триггер имеет два информационных входа: R и S и один выход – Q.

Условное обозначение и таблица переходов RS-триггера изображены на рисунке. (в данном случае изображен асинхронный триггер, у синхронного есть также вход С)

Вход S (set) – вход установки в единицу

Вход

R (reset) – вход установки в ноль.

Анализируя таблицу переходов можно заметить, что переход триггера из 0 в 0 возможен при подаче комбинации R=0, S=0 или R=1, S=0, т.е. этот переход будет при R=X (безразличное состояние), S=0. Исходя из этого таблицу переходов можно изобразить в сокращенном виде:

При подаче комбинации S=R=1 состояние перехода Qt+1 не определено и эта комбинация сигналов является запрещенной для RS-триггера.

JK-триггер

– работает аналогично RS-триггеру, однако,

в отличие от RS-триггера,

входная комбинация J=1,

K=1 не является запрещённой

(при такой комбинации JK-триггер

инвертирует выход).

Этот

триггер имеет два информационных входа: J

– вход установки в единицу (аналог входа set)

и K – вход установки в ноль (аналог входа

reset) и один выход – Q.

Условное обозначение и таблица переходов JK-триггера изображены на рисунке. (в данном случае изображен асинхронный триггер, у синхронного есть также вход С)

JK-триггер называют “универсальным”, т.к. из него можно получить любой другой триггер.

Если не подавать на входы запрещенную комбинацию, то он работает как RS-триггер. Если на вход J подавать входной сигнал, а на вход K инвертированный входной сигнал, то получим D-триггер. И, наконец, если объединить входы J и K и подавать на них входной сигнал, то получим T-триггер.

Триггер со счетным входом (Т–триггер)

Основной особенностью Т-триггера является то, что при поступлении на его вход очередного импульса триггер изменяет свое состояние на противоположное. Существуют две структуры Т–триггеров: однотактная и двухтактная. Однотактные схемы в настоящее время практически не используются из-за их недостаточной надежности.

На рис. 8.7 представлена логическая схема Т-триггера со счетным входом, построенная на элементной базе “И-ИЛИ-НЕ”. Как видно из схемы, выходы триггера Q связаны со входами обратными связями.

Рис. 8.7. Логическая схема двухтактного Т- триггера

Двухтактная схема используется для того, чтобы с помощью обратной связи создать механизм запоминания предыдущего состояния триггера на время переходного процесса при установке триггера первой ступени в противоположное состояние.

УГО Т-триггера показано на рис. 8.9. Как видно из временной диаграммы (рис.8.8), при поступлении очередного импульса на счетный вход триггера его состояние меняется на противо-положное. При этом между моментами срабатывания триггеров первой и второй ступеней имеется временная задержка, равная длительности синхроимпульса. Частота импульсов, поступающих на вход триггера, делится на два, т.е. сам триггер срабатывает в 2 раза реже.

Рис. 8.8. Временная диаграмма работы Т-триггера

Рис. 8.9. УГО Т- триггера

8.9. УГО Т- триггера

Таблица 8.2

| Сt | Q1t+0,5 | Qt+1 |

| Q1t | Qt | |

| ┐Qt | ┐Qt |

В табл. 8.2 представлена таблица переходов триггера со счетным входом. В ней символ “ ┐” обозначает инверсию сигнала Q.

Универсальный D-триггер (триггер-задержка)

Его особенность в том, что он имеет один информационный вход (название D от Delay). Триггер запоминает (задерживает) информацию, которая поступает по одному информационному каналу. Триггер также называется универсальным, так как на его основе можно построить все другие типы триггеров. Существуют две структуры D-триггера: однотактная и двухтактная.

8.3.1. Однотактный D-триггер

На рис. 8.10 показано УГО однотактного D –триггера. На рис.8.11 представлена логическая схема D -триггера, построенная на ЛЭ типа “ И-НЕ”. Особенность этой схемы состоит в том, что имеется только один информационный вход D.

Особенность этой схемы состоит в том, что имеется только один информационный вход D.

Рис. 8. 10. УГО однотактного D-триггера

Рис. 8.11. Логическая схема однотактного D-триггера

Таблица 8.3

В табл. 8.3 дана таблица переходов однотактного D-триггера.

Из этой таблицы видно, что при С =1 на выходе триггера устанавливается состояние, равное значению входа D.

Двухтактный D-триггер

На рис. 8.12 представлена логическая схема двухтактного D -триггера, построенного на элементной базе “И-НЕ”. УГО двухтактного D –триггера представлено на рис. 8.13. Эта схема отличается от двухтактного R-S -триггера тем, что у нее только один информационный вход D.

Рис. 8.12. Логическая схема двухтактного D-триггера

Рис. 8.13. УГО двухтактного D-триггера

Рис.8.14. Т-триггер на основе двухтактного D-триггера

На основе двухтактного D-триггера можно построить Т-триггер, при этом роль счетного входа выполняет вход С (рис. 8.14).

8.14).

Универсальный JK-триггер

Эта схема называется универсальной потому, что на ее основе можно построить все основные типы триггеров. JK-триггер имеет только двухтактную структуру (рис.8.15). УГО JK –триггера изображено на рис.8.16.

Рис. 8.15. Логическая схема JK –триггера

Рис. 8.16. УГО JK –триггера

Рис. 8.17. Временная диаграмма работы JK –триггера

На рис. 8.15 представлена логическая схема JK –триггера, которая представляет собой двухступенчатую структуру с обратными связями. Так как схема собрана на ЛЭ “И-НЕ”, то в таблице переходов (табл. 8.4) работа триггера рассматривается в условиях положительной логики. Вход J является входом установки в состояние “1” , вход K – входом установки в “0”.

Триггер первой ступени срабатывает по положительному фронту синхроимпульса, а триггер второй ступени управляется инвертированным синхроимпульсом, т. е. срабатывает по отрицательному фронту синхроимпульса через 0.5 такта.

е. срабатывает по отрицательному фронту синхроимпульса через 0.5 такта.

Рассмотрим работу триггера, используя временную диаграмму (рис.8.17). В первом такте синхроимпульс С:=0, оба триггера находятся в нулевом состоянии. Во втором такте C:=1,K:=0, J: =1 и положительным фронтом синхроимпульса уста-

навливается триггер Q’:=1, а затем через 0,5 такта по заднему фронту это состояние передается во второй триггер Q: =1.

Таблица 8.4

| Ct | J | K | Qt+0,5 | Qt+1 |

| x | x | Qt’ | Qt | |

| Qt’ | Qt | |||

| ┐Qt’ | ┐Qt |

В третьем и четвертом тактах С:=1, J:=1, K:=1 и в соответствии с таблицей истинности дважды устанавливаются в противоположное состояние оба триггера. В третьем такте Q’:=0 и Q:=0, а в четвертом такте Q’:=1 и Q:=1. В пятом такте J:=0 , K:=1 и оба триггера устанавливаются в нуль. Наконец, в последнем такте С:=1, J;=1, K:=1 состояние обоих триггеров снова изменяется на противоположное Q’:=1, Q: =1.

В третьем такте Q’:=0 и Q:=0, а в четвертом такте Q’:=1 и Q:=1. В пятом такте J:=0 , K:=1 и оба триггера устанавливаются в нуль. Наконец, в последнем такте С:=1, J;=1, K:=1 состояние обоих триггеров снова изменяется на противоположное Q’:=1, Q: =1.

Счетчики

Счетчик – многоразрядный ФУ, предназначенный для подсчета количества импульсов, поступающих на его вход. Схемы счетчиков разнообразны, и их можно классифицировать по нескольким признакам:

1) в зависимости от системы счисления, в которой ведется подсчет числа импульсов, на: а) двоичные; б) двоично-десятичные;

2) по способу организации переноса между разрядами счетчика: а) с последовательным переносом, б) параллельным переносом, в) групповым переносом;

3) в зависимости от арифметической операции, выполняемой счетчиком: а) суммирующие, б) вычитающие, в) реверсивные;

4) по способу управления: а) асинхронные, б) синхронные.

10. 3.1 Счетчик с последовательным переносом

3.1 Счетчик с последовательным переносом

Рис.10.6. Двоичный суммирующий счетчик с последовательным переносом асинхронного типа.

На рис.10.6 и 10.7 приведены схема и УГО двоичного суммирующего счетчика с последовательным переносом асинхронного типа.

Рис.10.7. УГО счетчика

Ниже показана МОДИС- модель этого счетчика и временная диаграмма работы счетчика (рис.10.8).

Составим МОДИС- модель этого счетчика.

Описание переменных

‘ЗАВИСИМ’ С4 [1:K], Р [1: 2];

‘ИНЕЗАВ’ Р0, ГШ;

Описание схемы

С4 [1] ’:=‘ ‘ЕСЛИ’ ГШ ‘ТО’ 0

‘ИНЕСЛИ’ Р0 ‘ТО’ IC4 [1]

‘ИНАЧЕ’ C4 [1];

Р1 ‘:=‘ C4 [1] * P0

С4 [1:K] ‘:=‘ ‘ЕСЛИ’ ГШ ‘ТО’ 0

‘ИНЕСЛИ’ Р0 ‘ТО’ C4 [1:K]+1

“ИНАЧЕ’ C4 [1:K];

Рис. 10.8. Временная диаграмма работы счетчика

Каждый разряд счетчика делит частоту поступающих на его вход импульсов на 2. У асинхронного счетчика моменты срабатывания

отдельных разрядов счетчика определяются реальными задержками в схемах формирования переноса.

τp – время формирования переноса в одном разряде.

Быстродействие счетчика определяется временем пробега переноса по всем разрядам.

Трег= n * τp – время регистрации – интервал времени от момента поступления на вход счетчика очередного импульса до момента, когда новое значение установится во всех разрядах счетчика.

n –количество разрядов в счетчике.

10.3.2. Счетчик с параллельным переносом

Как следует из рис. 10.9. счетчик является синхронным, так как срабатывание всех триггеров происходит практически одновременно при поступлении на его вход сигнала Р0 . Схемы формирования переносов строятся по следующим формулам:

Р1 ‘:=‘ Р0 * Q1;

Р2 ‘:=‘ P1 * Q2 = P0 * Q1 * Q2;

…Pк ‘:=’ P0 * Q1 * Q2 * … * Qk-1; Трег≈ τp.

Счетчики с параллельным переносом обладают наибольшим быстродействием, причем Трег теоретически не зависит от количества разрядов. Однако на практике такие счетчики строятся не более, чем на 8 разрядов.

Рис. 10.9. Счетчик с параллельным переносом

10.9. Счетчик с параллельным переносом

Исследование работы триггеров — КиберПедия

Лабораторная работа № 1

Исследование работы триггеров

Цель работы:Изучить устройство и принцип действия триггеров (сменное устройство УС-14).

Асинхронный RS-триггер

RS-триггер – это триггер с раздельной установкой состояния логического нуля и единицы. Он имеет два информационных входа R и S. Его обозначение на функциональной схеме показано на рис. 1.

Рис. 1. RS-триггер с инверсными входами на элементах И-НЕ и его временная диаграмма.

Состояния триггера под воздействием определенной комбинации входных сигналов приведены в таблице 1.

Таблица 1. Состояния RS-триггера.

| Входы | Выходы | ||

| `S | `R | Qn+1 | `Qn+1 |

| Х | Х | ||

| Qn | `Qn |

При подаче на вход комбинации сигналов `S=0, `R=1 (входы инверсные) на выходе получим Qn+1=1. Такой режим называют режимом записи логической единицы. При подаче входных сигналов `S=1, `R=0 на выходе – Qn+1=0 (режим записи логического нуля или режим сброса). При `S=`R=1 состояние триггера не изменяется – режимом хранения информации. При `S=`R=0 состояние триггера будет неопределенным, так как во время действия информационных сигналов логические уровни на выходах триггера одинаковы (Qn+1=`Qn+1=1), а после окончания их действия триггер может равновероятно принять любое из двух устойчивых состояний. Поэтому такая комбинация `S=`R=0 является запрещенной.

Такой режим называют режимом записи логической единицы. При подаче входных сигналов `S=1, `R=0 на выходе – Qn+1=0 (режим записи логического нуля или режим сброса). При `S=`R=1 состояние триггера не изменяется – режимом хранения информации. При `S=`R=0 состояние триггера будет неопределенным, так как во время действия информационных сигналов логические уровни на выходах триггера одинаковы (Qn+1=`Qn+1=1), а после окончания их действия триггер может равновероятно принять любое из двух устойчивых состояний. Поэтому такая комбинация `S=`R=0 является запрещенной.

Синхронный RS-триггер

Для синхронных триггеров изменение сигналов на информационных входах не достаточно для изменения состояния триггера. Необходим дополнительный командный импульс, который подают на специальный синхронизирующий (тактирующий вход). В зависимости от исполнения синхронные триггеры управляются либо по уровню напряжения тактового импульса (триггеры – защелки), либо по его фронту или срезу. Управление по уровню напряжения называют статическим, а по перепаду (фронту или срезу) импульса – динамическим.

Управление по уровню напряжения называют статическим, а по перепаду (фронту или срезу) импульса – динамическим.

Синхронные триггеры по уровню срабатывают в момент, когда напряжение тактового импульса достигает порогового уровня. Сигналы на выходах при этом принимают значения, которые определены функциональным видом триггера и сочетанием сигналов на информационных входах. Специфика этих триггеров такова, что пока длится тактовый импульс, смена сигналов на информационных входах приводит к новым переключениям выходов. С окончанием тактового импульса такой триггер сохраняет (защелкивает) свое выходное состояние. Другими словами, наличие тактового импульса обеспечивает триггеру асинхронный режим работы, отсутствие – режим хранения. Схема простейшего синхронного RS-триггера и его условное обозначение показаны на рис. 2.

Рис. 2. Синхронный RS-триггер.

Триггер на элементах И-НЕ имеет прямые статические входы, поэтому управляющим сигналом является уровень логической единицы. Если на вход С подать сигнал логической единицы С=1, то работа триггера аналогична работе простейшего асинхронного RS-триггера. При С=0 входы S и R не оказывают влияния на состояние триггера. Комбинация S=R=C=1 является запрещенной. Таблица 2 – состояния синхронного RS-триггера.

Если на вход С подать сигнал логической единицы С=1, то работа триггера аналогична работе простейшего асинхронного RS-триггера. При С=0 входы S и R не оказывают влияния на состояние триггера. Комбинация S=R=C=1 является запрещенной. Таблица 2 – состояния синхронного RS-триггера.

Таблица 2. Состояния синхронного RS-триггера.

| Входы | Выходы | |||

| S | R | C | Qn+1 | `Qn+1 |

| любое | любое | Qn | `Qn | |

| X | X |

D – триггер

D-триггером называют синхронный триггер, имеющий два входа: вход данных D и вход синхронизации С. D-триггер переключается по сигналу на С-входе, в состояние соответствующее уровню на D-входе. Условное обозначение D-триггера и его реализация на синхронном RS-триггере показаны на рис. 3.

D-триггер переключается по сигналу на С-входе, в состояние соответствующее уровню на D-входе. Условное обозначение D-триггера и его реализация на синхронном RS-триггере показаны на рис. 3.

Рис. 3. D – триггер.

Изменения на D-входе при С=0 не влияют на состояние выхода Q, триггер заперт по С-входу и находится в режиме хранения. Фронт С-сигнала вызывает переключение триггера в то состояние, которое было к этому моменту на входе D. При С=1, любое изменение D-входа вызывает изменение выхода Q. По спаду синхросигнала – на выходе фиксируется состояние, которое было на D-входе непосредственно перед этим моментом. Следующее изменение Q будет возможно только по фронту следующего синхроимпульса.

Чтобы процесс фиксации состояния D-входа проходил без сбоев, т.е. был однозначно предсказуемым, переходной процесс в схеме защелки, вызванный срезом С-сигнала, не должен накладываться на переходной процесс, вызванный переключением D-входа. Это значит, что всякие изменения состояния D-входа должны прекратиться за некоторое время до среза С-сигнала, называемое временем подготовки (setup time), и могут снова начинаться после среза С-сигнала не ранее чем через время выдержки (удержания) (hold time).

Необходимость введения и нормирования интервалов подготовки и выдержки характерна для всех функциональных узлов, имеющих вход синхронизации. Кроме того, для любого синхронного узла, существует минимально допустимая длительность синхроимпульса, обеспечивающая отсутствие сбоев из-за наложения переходных процессов от фронта и среза этого импульса.

Если требуется задержка записанной информации более чем на один такт, применяют DV-триггер, отличающийся от D-триггера наличием дополнительного информационного входа V. Когда V=1, триггер работает как D-триггер. При V=0 триггер закрыт, т.е. при любых комбинациях сигналов на входах D и C в ячейке памяти хранится информация, записанная в предыдущем такте.

Комбинированные D-триггеры имеют дополнительные входы асинхронной установки S и R. Как устройства запоминания двоичной информации D- и DV-триггеры применяются при построении регистров, счетчиков и других узлов цифровой техники.

JK-триггеры

JK-триггеры подразделяются на универсальные и комбинированные.

Универсальный JK-триггер имеет два информационных входа J и K. Вход J выполняет роль входа S в RS-триггере, а вход K – роль входа R, т.е. по входу J триггер устанавливается в состояние Q=1, а по входу K – в состояние Q=0.

JK-триггер отличается от RS-триггера прежде всего тем, что в нем устранена неопределенность, которая возникает в RS-триггере при определенной комбинации входных сигналов.

Комбинированный JK-триггер отличается от универсального наличием дополнительных асинхронных входов S и R для предварительной установки триггера в определенное состояние (логической 1 или 0). Универсальность JK-триггера состоит в том, что он может выполнять функции RS-, T-, и D-триггеров.

Простейший JK-триггер можно получить из синхронного RS-триггера, если ввести дополнительные обратные связи с выводов триггера на входы, которые позволяют устранить неопределенные состояния (рисунок 4).

Рис. 4. JK – триггер.

Две буквы Т (рис. 4б) указывают на наличие двух ступеней. Вход С, реагирующий не на уровень потенциала, а на его отрицательный перепад, выделен специальным значком. Вход, реагирующий именно на перепад, называют динамическим.

При J=K=0, не зависимо от синхросигнала С (рис. 4а), триггер находится в режиме хранения. При J=1, К=0 синхросигналом может быть открыт лишь элемент 1 и только при условии, что перед поступлением С-сигнала на выходе триггера был 0 (Q=0). Тогда по спаду синхросигнала триггер переключится в «1». Если же триггер до синхросигнала был в «1», то он так и останется в «1». Таким образом, J-вход выполняет функции синхронизированного S-входа. В силу симметрии схемы легко показать, что K-вход выполняет функции синхронизированного R-входа, переводя триггер в «0». Таким образом, при разных уровнях на J- и К-входах JK-триггер ведет себя как синхронный RS-триггер.

Существенно отличным от RS-триггера является поведение JK-триггера при J=K=1. Для RS-триггера такое состояние входов запрещено. При любом состоянии триггера сигналы обратной связи открывают для С-сигнала именно тот входной элемент И, пройдя через который, С-сигнал переведет триггер в противоположное состояние. Таким образом, при J=K=1 по спаду каждого С-сигнала JK-триггер меняет состояние своих выходов на противоположное. Это так называемый счетный режим, или Т-режим работы триггера (от toggle—кувыркаться).

Состояния JK-триггера приведены в табл. 3. Спад синхроимпульса показан в таблице стрелкой вниз. Это означает, что JK-триггер переключается не уровнем сигнала, а перепадом уровня (в данном случае по заднему фронту).

Таблица 3. Состояние JK-триггера.

| Режим | С | Jn | Kn | Qn+1 |

| Хранение | любое | Qn | ||

| любое | любое | |||

| Сброс | ¯ | |||

| Установка | ¯ | |||

| Инверсия предыдущего состояния | ¯ | `Qn |

Т-триггер

Т-триггер или счетный триггер имеет один информационный вход Т.

Каждый импульс на этом входе переводит его в новое состояние.

Т-триггер можно построить на базе D-триггера (рис. 5).

Рис. 5. Т-триггер.

Из D-триггеров для этого годятся только те, которые имеют динамическое управление по тактовому входу. Если на входе D поставить дополнительный двухвходовый элемент И и инверсный выход триггера `Q соединить с одним из входов элемента И, а на второй вход подать сигнал E, то получим Т-триггер с дополнительным разрешением по входу (рис. 5).

Если входы JK-триггера J, K и C объединить, то получим Т-триггер, который переключается каждым входным импульсом.

Т-триггеры используются как делители частоты на 2 или счетчики по модулю 2.

Т-триггеры в виде самостоятельных изделий не выпускаются.

Триггер Шмитта

Триггеры Шмитта используют в качестве пороговых устройств и формирователей прямоугольных импульсов из сигналов произвольной формы, в том числе и синусоидальных. Он обладает двумя устойчивыми состояниями, смена которых происходит скачком под воздействием входных сигналов. Характерная особенность триггера Шмитта – различие в пороговых уровнях входных сигналов, при которых происходит его переключение. Это свойство называется гистерезисом. Участок характеристики между обоими пороговыми значениями – верхним Uпор.в. и нижним Uпор.н. – определяет область гистерезиса, а разность пороговых уровней DUпор=Uпор.в–Uпор.н – ее ширину. Ширина области гистерезиса характеризует чувствительность триггера Шмитта к переключающим сигналам: чем она уже, тем чувствительность выше. На рисунке 6 изображено графическое обозначение триггера Шмита и его передаточная характеристика.

Uвых

Вход Выход U1

U0

Uпор.н Uпор.в Uвх

Рис. 6. Триггер Шмита и его передаточная характеристика.

При входном сигнале низкого уровня выходное напряжение близко к нулю. Когда по мере роста входное напряжение достигнет нижнего порога Uпор.н, состояние триггера не изменится. Только когда входной сигнал сравняется с верхним пороговым напряжением Uпор.в, выходное напряжение скачком возрастет до уровня U1вых»Uп. Дальнейшее повышение входного напряжения не изменяет выходного. Уменьшение входного напряжения вызывает обратное переключение только тогда, когда входной сигнал понизится до Uпор.н. В этот момент выходное напряжение скачком уменьшится до нулевого значения.

Порядок выполнения работы

1. Ознакомиться с устройством, принципом действия триггеров, изучить их основные характеристики, условные графические обозначение.

2. Установить кассету со сменным устройством УС-14 в разъем на передней панели стенда и закрепить ее винтами, расположенными с левой и правой стороны кассеты.

На лицевой панели БУК нажать кнопку «Сеть».

Нажать кнопку «Питание V +5».

Если светодиод под надписью « Питание V +5» не светится, отжать кнопку и через 2-3 минуты нажать повторно, если после этого светодиод не светится, то необходимо повернуть винты, крепящие кассету, по часовой стрелке на 0,5-2 оборота.

Если светодиоды не светятся, то выключить стенд и обратиться к преподавателю.

3. Исследовать работу D-триггера (D4).

3.1. Кнопками h2..h5 ПК подать комбинации сигналов `S, D, C, `R на входы D-триггера. Учесть, что сигнал со входа D передается на выходы триггера при поступлении положительного перепада импульса на входе С (изменение от низкого к высокому, т.е. отжать и нажать h4). Состояние выходов – на табло Q25, Q26 в двоичном коде (кнопка 10/2 нажата).

3.2. Заполнить таблицу 4 переключений D-триггера (Х – любое состояние). Построить временную диаграмму работы триггера.

Таблица 4. Результаты эксперимента.

| Режим работы | Входы | Выходы | ||||

| `S | `R | D | C | Q | `Q | |

| Асинхронная установка | Х | Х | ||||

| Асинхронный сброс | Х | Х | ||||

| Неопределенность | Х | Х | ||||

| Загрузка «1» | | |||||

| Загрузка «0» | |

4. Исследовать работу JK-триггера (D2).

4.1. Кнопками H9..h22 ПК подать комбинации сигналов `S, K, J, `R на входы JK-триггера. На вход синхронизации С сигнал поступает с ПСИ (подавать 1 импульс, кнопка “ПУСК” служит для подачи импульса, кнопку “УСТАН. 0” следует нажимать перед подачей следующего импульса). Состояние выходов – на табло Q27, Q28.

4.2. Заполнить таблицу 5 переключений JK-триггера. Построить временную диаграмму работы триггера.

Таблица 5. Результаты эксперимента.

| Режим работы | Входы | Выходы | |||||

| `S | `R | J | K | `C | Qn+1 | `Qn+1 | |

| Асинхронная установка | Х | Х | Х | ||||

| Асинхронный сброс | Х | Х | Х | ||||

| Неопределенность | Х | Х | Х | ||||

| Установка «1» | |||||||

| Сброс «0» | |||||||

| Переключение | |||||||

| Хранение (без изменений) |

5. Построить Т-триггер на основе на JK-триггера и D-триггера.

5.1. Необходимые соединения выполнять перемычками вставляемые в разъемы XS (например, XS1-XS5 и XS3-XS7). Режим работы входов задавать кнопками.

5.2. Привести схему соединений.

5.3. Проверить работу триггера.

6. Построить D-триггер на основе на JK-триггера (например, соединив XS2-XS6).

6.1. Привести схему соединений.

6.2. Проверить работу триггера.

Примечание. Коммутация выходов КПИ.

КПИ1 – КПИ8 коммутация на «вх.1» (контроль V~).

На КВУ нажать

На «контроль V~» нажать «вх.1».

На программаторе СИ установить номер КПИ: КПИ1 – , КПИ2 – , КПИ3 – и т.д. и нажать «ПУСК». Номер КПИ отображается на левом индикаторе, при этом на первом и пятом слева индикаторах светиться запятая.

Осциллограф или вольтметр подсоединить к «выход V~».

Содержание отчета

1. Цель работы.

2. Схемы включения триггеров.

3. Таблицы состояний триггеров.

4. Временные диаграммы работы триггеров.

5. Выводы по работе.

5. Контрольные вопросы

1. Что называется триггером?

2. Как классифицируются триггеры по способу записи информации и по функциям?

3. Как работают триггеры Шмитта?

4. Чем отличаются D- и DV-триггеры?

5. Почему JK-триггеры называются универсальными?

6. Почему Т-триггеров нет в интегральном исполнении?

Лабораторная работа № 2

Исследование работы дешифраторов

с индикаторами в интегральном исполнении

Цель работы:Изучить устройство и принцип действия дешифраторов

(сменное устройство УС-16).

Дешифратор

Дешифратором(ДШ) называется устройство, служащее для преобразования кода числа на входе (или комбинации входных сигналов) в сигнал на определенном выходе. Другими словами, дешифратор представляет собой устройство, формирующих управляющий сигнал (например, высокого уровня) на одном из выходов, в то время как на остальных выходах сигналы отсутствуют (низкий уровень). Дешифраторы выпускаются в интегральном исполнении.

ДШ используют, когда нужно обратиться к цифровым устройствам, адрес (номер устройства) которых представлен двоичным кодом. Он также позволяет определить, в каком состоянии находится регистр, ОЗУ, счетчик и т.д.

Полный дешифратор — дешифратор, имеющий столько выходов m, сколько различных комбинаций может иметь n-разрядное двоичное число на его входах, т. е. m=2n. При m<2nдешифратор называется неполным или частичным.

Дешифраторы подразделяют по способу организации дешифрации слова на одноступенчатые (линейные) и многоступенчатые (прямоугольные, пирамидальные).

Условное изображение ДШ с инверсными выходами показано на рис. 1,а.

А0, А1, А2,…, Аn-1 – адресные входы, где индекс буквы А – показатель степени 2. Иногда эти входы просто нумеруют в соответствии с весами двоичных разрядов: 1, 2, 4, 8, 16,…, 2n-1.

Выходы дешифратора имеют нумерацию, совпадающую с десятичным представлением двоичного числа от 0 до n-1. Если, например, слово на входе имеет код 101 (табл. 1), то активный сигнал будет только на пятом выходе дешифратора, т. е. 22+01+20=5.

Е (enable) – разрешающий вход. На рис. 1,а вход Е инверсный. При Е=0 разрешается работа ДШ. Активный уровень “0” будет только на одном выходе, номер которого соответствует поданному на вход двоичному числу, а на всех остальных “1”. При Е=1 на всех выходах устанавливаются неактивные уровни “1” независимо от поданных сигналов на адресные входы.

Схема линейного дешифратора на три входа, у которого число выходов m=23=8приведено на рис.1,б. Число элементов одноступенчатого дешифратора определяется числом выходов.

Рис. 1. Дешифратор 3х8 с инверсными выходами.

Для схемной реализации каждого выхода дешифратора достаточно иметь один логический элемент И-НЕ (И) с числом входов, равным числу входов дешифратора. Каждый выход дешифратора принимает значение, равное логическому нулю, только при одном определенном наборе входных переменных A0…An(см. табл. 1).

Таблица 1. Состояния дешифратора

| Входы | Выходы | Функция | |||||||||

| A2 | A1 | A0 | Q0 | Q1 | Q2 | Q3, | Q4 | Q5 | Q6 | Q7 | |

| `Q0=`A2`A1`A0 | |||||||||||

| `Q1=`A2`A1A0 | |||||||||||

| `Q2=`A2A1`A0 | |||||||||||

| `Q3=`A2A1A0 | |||||||||||

| `Q4=A2`A1`A0 | |||||||||||

| `Q5=A2`A1A0 | |||||||||||

| `Q6=A2A1`A0 | |||||||||||

| `Q7=A2A1A0 |

Если длина дешифрируемого двоичного слова больше возможного числа входов элементов И, используют многоступенчатое (каскадное) построение дешифратора (рис. 2). Такие дешифраторы называются многоступенчатыми. К ним относятся пирамидальные и прямоугольные (матричные). В двухступенчатом дешифраторе каждый выход образован каскадным включением двухвходовых элементов И. Задержки распространения сигналов в таком дешифраторе больше, чем в дешифраторе, показанном на рис. 1. Таким образом, выбор той или иной схемы дешифратора определяется в основном длиной дешифрируемого слова и количеством входов элемента И.

В прямоугольном (матричном) дешифраторе (рис. 3) дешифрируемое слово разбивается на несколько подслов. Подслова дешифрируются на отдельных линейных дешифраторах, выходы которых подключают на вход следующей ступени дешифратора.

Рис. 2. Схема пирамидального дешифратора. Рис. 3. Схема матричного дешифратора.

Пример. Построить дешифратор на 8 входов и 256 выходов. Для этого можно использовать микросхемы типа ИД3 серии 133, 155, 533, 1533 и др. Для увеличения разрядности дешифратора используем входы разрешения Е, рис. 4. Если на обоих входах разрешения E уровни логического 0, то на том из выходов, номер которого соответствует значению двоичного входного кода, будет уровень логического 0, на остальных выходах – логическая 1. Если хотя бы на одном из входов разрешения уровень логической 1, то независимо от состояний входов на всех выходах ДШ формируется 1.

Старшие разряды используется в данном примере для выбора дешифраторов младших разрядов. Код дешифрируемого числа разделен на две части по 4 разряда (младшие X3 X2 X1 X0, старшие X7 X6 X5 X4). Код, определяемый комбинацией старших разрядов, обусловливает выбор одного из шестнадцати дешифраторов DС0-DС15. Например, если на вход поступает код X7X6X5X4X3X2X1X0=11110010, то старшие четыре разряда, поступая на входы DСy, приводят к появлению сигнала логического нуля на 15-м выходе DСy, так как 1111(2) =15(10), следовательно, разрешается работа DС15. Младшие разряды, которые одновременно поступают на входы DС0…DС15, приводят к появлению активного уровня на втором выходе DС15, так как 0010(2) = 2(10). Результат определяется как сумма 11110000(2) = 240(10) и 0010(2)=2(10), т.е. 11110010(2) =242(10). Остальные выходы всех дешифраторов находятся при этом в состоянии логической единицы.

На рис. 5а, таким способом построен ДШ 4х32 на четырех микросхем К555ИД7 3х8. Каждая микросхема имеет по три разрешающих входа (два инверсных и один прямой). Работа ДШ осуществляется лишь тогда, когда одновременно на инверсных входах «0», а на прямом «1».

В микросхему К555ИД4 (рис. 5б) входят два ДШ 2х4 с общими адресными входами А1 и А0. Каждый ДШ имеет два разрешающих входа. У верхнего по схеме ДШ два инверсных входа EQ1 и EQ2, у нижнего – один прямой – EP1, и один инверсный – EP2. Это позволяет объединить EQ1 и EP1. Подавая на эту пару третий разряд адреса А2 можно построить ДШ 3х8.

Рис. 5. Использование разрешающих входов микросхем дешифраторов.

а) – разрешающие входы использованы для построения второй ступени каскадного ДШ;

б) – построение ДШ 3х8 на микросхеме содержащих два дешифратора 2х4.

Пример построения дешифратора адреса внешнего устройства. Микропроцессорное устройство управления имеет 8 разрядную шину адреса. Диапазон адресов управляемых устройств A8H – AFH.

Запишем начальный и конечный адрес устройства в двоичном коде:

| A7 | A6 | A5 | A4 | A3 | A2 | A1 | A0 | ||

| Анач | A8H | ||||||||

| Aкон | AFH |

Пять старших разрядов адреса одинаковые для всех устройств. Для построения воспользуемся микросхемой К155ИД7. Неизменяемую часть адреса подадим на разрешающие входы E1, E2, E3 (рис. 6), что обеспечит работу дешифратора только при попадании в заданный диапазон адресов.

Рис. 6. Дешифратор адресов A8H – AFH.

Индикаторные устройства

Светодиодные индикаторы

Индикаторные устройства служат для визуальной индикации состояния электронных устройств или цифровой информации, преобразуемой электронными устройствами. Широкое используются светодиодные, вакуумные, люминесцентные и жидкокристаллические индикаторы.

Шкальные индикаторы представляют собой линейку светодиодов, катоды или аноды которых соединены вместе. Такие индикаторы могут использоваться для индикации уровня сигналов. Выпускаются специальные микросхемы для управления шкальными индикаторами, выходные усилители которых выполнены с открытым эмиттером или коллектором и встроенными токоограничивающими цепями. Если к выходам микросхемы подключить шкальный индикатор, то положение на нем светящейся точки будет определяться двоичным кодом на адресных входах дешифратора. Вход Е(рис. 7) может использоваться для управления яркостью свечения индикатора, для этого необходимо подать на него импульсный сигнал.

Рис. 7. Дешифратор3х8. Рис. 8. Управление семисегментным индикатором.

Семисегментные индикаторы позволяют визуально регистрировать числа как в десятичной, так и в 8- и 16-ричной системах счисления. На рис. 8 показаны микросхемы преобразователей двоично-десятичного кода в код для управления семисегментными цифровыми индикаторами. Вход BI (Blanking Input) служит для управления яркостью индикатора.

Семисегментные светодиодные и жидкокристаллические индикаторы работают при тех же напряжениях, что и микросхемы, имеют малый ток потребления. Индикация осуществляется семью сегментами, как показано на рис. 9, подачей управляющего напряжения на отдельные сегменты, что вызывает его свечение (светодиодный индикатор).

Рис. 9. Схема индикации семисегментного светодиодного индикатора АЛС324Б.

Матричные индикаторы

Матричные индикаторы позволяют отображать символы. На рис. 10 показана структура полного матричного индикатора формата 5х7 типа АЛС340А и его условное графическое изображение (УГО). СА – аноды столбцов, RC – катоды строк, РА – анод точки. При подачи логической 1, например, на вход СА1 и логического 0 на вход RC1 «загорится» верхний левый светодиод. Для индикации символа необходимо последовательно «зажигать» светодиоды (образующие этот символ). При определенной частоте, за счет инертности глаза человека, мигание отдельных элементов символов (светодиодов) не будет заметно.

Рис. 10. Структура матричного индикатора АЛС340А а) и его УГО б).

Порядок выполнения работы

1. Ознакомиться с устройством, принципом действия дешифраторов и индикаторных устройств, изучить их основные характеристики, условные графические обозначение (УГО).

2. Установить кассету со сменным устройством УС-16 в разъем на передней панели стенда и закрепить ее винтами, расположенными с левой и правой стороны кассеты.

На лицевой панели БУК нажать кнопку «Сеть».

Нажать кнопку «Питание V +5».

Если светодиод под надписью «Питание V +5» не светится, отжать кнопку и через 2-3 минуты нажать повторно, если после этого светодиод не светится, то необходимо повернуть винты, крепящие кассету, по часовой стрелке на 0,5-2 оборота.

Если светодиоды не светятся, то выключить стенд и обратиться к преподавателю.

3. Исследовать работу дешифраторов D9, D10 (рис. 11) и полупроводниковых индикаторов HG-1, HG2.

3.1. Установить счетчики D7, D8 в «0»: на входы установки R0 подать сигнал высокого уровня (нажать и отжать h26).

3.2. Разрешить работу индикаторов: НG1 – нажать Н15, HG2 – Н10.

3.3. Исследовать работу сегментов индикатора HG1 с помощью клавиш Н1-Н7. Нажимая на кнопки по очереди гасить сегменты индикатора НG1. На схеме индикации против каждого сегмента проставить номера управляющей кнопки.

3.4. Исследовать работу дешифраторов и индикаторов при различном состоянии счетчиков. Для этого на вход С1 счетчика D8 подать n импульсов, предварительно набранных на ПСИ, последовательно нажимая клавиши «Установ 0» и «Пуск». Состояние счетчиков индицируются на левом цифровом табло Q27 и Q28 в десятичном коде.

3.5. По полученным результатам заполнить таблицу истинности работы дешифратора (табл. 2), построить временные диаграммы: состояние на выходе счетчика – состояние сегментов индикатора (0 – не светится, 1 – светится).

Таблица 2. Результаты эксперимента.

| Входы D10 | Выходы D10 | ||||||||||||||

| 10-е | А | В | С | D | E | F | G | ||||||||

Содержание отчета

1. Цель работы.

2. Исследуемая схема с описанием работы.

3. Таблица истинности и временные диаграммы работы дешифратора (индикатора).

4. Выводы по работе.

5. Контрольные вопросы

1. Определение, классификация, принцип работы дешифраторов.

2. Привести схему линейного, многоступенчатого дешифратора.

3. Отличие многоступенчатого прямоугольного дешифратора от пирамидального?

4. Составить схему двухступенчатого дешифратора.

5. Объяснить работу семисегментного и матричного индикатора.

6. Построить схему дешифратора 5х32 на двух микросхемы типа ИД3 и одном элементе И-НЕ или элементе НЕ.

Лабораторная работа № 3

Порядок выполнения работы

1. Ознакомиться с устройством, принципом действия преобразователей кодов.

2. Установить кассету со сменным устройством УС-18 в разъем на передней панели стенда и закрепить ее винтами, расположенными с левой и правой стороны кассеты.

На лицевой панели БУК нажать кнопку «Сеть».

Нажать кнопку «Питание V +5».

Если светодиод под надписью « Питание V +5» не светится, отжать кнопку и через 2-3 минуты нажать повторно, если после этого светодиод не светится, то необходимо повернуть винты, крепящие кассету, по часовой стрелке на 0,5-2 оборота.

Если светодиоды не светятся, то выключить стенд и обратиться к преподавателю.

3. Исследование работы преобразователя двоично-десятичного кода в двоичный (DD2):

3.1. Кнопками Н3…Н7 ПК подается двоично-десятичный код с весом 10-5-4-2-1 соответственно. Сигнал на разрешающий вход P подается кнопкой Н1 ПК (активный уровень входа – низкий, поэтому микросхема DD2 работает при отжатой кнопке Н1).

3.2. Выходной двоичный код индицируется на индикаторах Q27…Q31.

| Q25 | Q26 | Q27 | Q28 | Q29 | Q30 | Q31 | Q32 | |

3.3. По результатам исследования преобразователя двоично-десятичного кода в двоичный заполнить табл. 4.

Таблица 4. Результаты эксперимента.

| Десятичное число | Двойчно-десятичный код | Двоичный код | |||||||||

| ВХОДЫ | ВЫХОДЫ | ||||||||||

| P | Е | D | C | B | A | Y5, Q27 | Y4, Q28 | Y3, Q29 | Y2, Q30 | Y1, Q31 | |

JK-триггеры

Информатика JK-триггеры

просмотров – 577

JK-триггер (от англ. jump и keep), отличается от рассмотренного RS-триггера тем, что появление на обоих информационных входах (J и K) логических единиц (для прямых входов) приводит к изменению состояния триггера. Такая комбинация сигналов для JK-триггера не является запрещенной.

В остальном JK-триггер подобен RS-триггеру, причем роль входа S играет вход J, а роль входа R – вход К. JK-триггеры реализуются в виде в виде двухтактных триггеров (т. е. JK-триггеры являются синхронными).

На рис. 3 приведено условное графическое обозначение двухступенчатого JK-триггера.

Рис. 3. JK-триггер

Полная таблица истинности JK-триггера аналогична таблице истинности RS-триггера, но не имеет неопределенных состояний (рис. 4). Данная таблица справедлива при активизации входа синхронизации.

Рис. 4. Таблица истинности JK-триггера

Для динамических триггеров характерно блокирование информационных входов в тот момент, когда полученная информация передается на выход.

Для примера рассмотрим микросхему К555ТВ9 (рис. 5), которая представляет собой два JK-триггера с динамическим управлением по входу синхронизации, имеющие инверсные входы асинхронной установки R и S.

Рис. 5. ИМС К555ТВ9

При подаче логического 0 на вход S и логической 1 на вход R триггер устанавливается в единичное состояние (Q = 1). При подаче на вход S логической 1, а на вход R логического 0 триггер устанавливается в нулевое состояние (Q = 0). При S = R = 1 триггер работает как синхронный JK-триггер, причем срабатывает он при изменении сигнала на входе синхронизации С от 1 к 0.

JK-триггер является универсальным триггером. Универсальность JK-триггера заключается в возможности реализации на его основе RS, T и D-триггеров. Преобразование JK-триггера в RS, T, D-триггеры показано на рис. 6. Подача уровня логической единицы “1” осуществляется либо подключением резистора (порядка 1кОм), соединенного с +5 В, либо к выходу свободного элемента И-НЕ, один вход которого подключается к корпусу.

Рис. 6. Реализация на основе JK других типов триггеров: а) асинхронный RS-триггер, б) асинхронный Т-триггер, в) синхронный Т-триггер, г) D-триггер

Читайте также

Каскадирование дешифраторов Дешифраторы, имеющие входы разрешения дешифрации, можно соединять для увеличения числа комбинаций. Например, из ИД4, сдвоенного дешифратора 2ґ4, введением дополнительных связей можно получить дешифратор 3ґ8 (рис. 47, а). Объединением двух… [читать подробенее]

Синтезировать реверсивный десятиразрядный регистр сдвига на одну позицию. Использовать триггеры типа D. При сдвиге вправо и влево в крайний разряд загружать единицу. Реализовать схему в пакете Electronics WorkBench. 3) Используя микросхему ТМ2 разработать реверсивный… [читать подробенее]

Прежде чем начать изучение jk триггера, вспомним принципы работы RS-триггера. Напомню, что в этом триггере есть запрещённые комбинации входных сигналов. Одновременная подача единичных сигналов на входы R и S запрещены. Очень хотелось бы избавиться от этой неприятной… [читать подробенее]

T-триггеры Т-триггер – это счетный триггер. У Т-триггера имеется только один вход. После поступления на этот вход импульса, состояние Т-триггера меняется на прямо противоположное. Счётным он называется потому, что он как бы подсчитывает количество импульсов,… [читать подробенее]

В RS-триггерах для записи логического нуля и логической единицы требуются разные входы, что не всегда удобно. При записи и хранении данных один бит может принимать значение, как нуля, так и единицы. Для его передачи достаточно одного провода. Как мы уже видели ранее, сигналы… [читать подробенее]

Типовые корпуса микросхем Рис. 2.25 – Типовые корпуса микросхем: а — планарный с двусторонним расположением выводов; б — типа DIP, в — пленарный с четырехсторонним расположением выводов Условия применения микросхем, их функциональные и энергетические… [читать подробенее]

Предварительно рассмотрим принципиальную схему так называемого Т-триггера (toggle — переключатель), выполняющего лишь одну функцию: он может делить частоту тактовой, последовательности, подаваемой на вход С в 2 раза. Принципиальная схема Т-триггера, содержащего два… [читать подробенее]

На рисунке 2.27,а показана принципиальная схема RS-триггера, которая содержит защелку (транзисторы VT1 и VT2), а также два раздельных статических входа управления (транзисторы VT3 и VT4). Эти входы управления называются R (reset — сброс) и S (set — установка). Иногда входы R и S называют… [читать подробенее]

На рис. 2.32,а показана схема простейшего JK-триггера. От RST-триггера (рис. 2.29, а) он отличается двумя обратными связями, которые устраняют неопределенность в таблице состояний. Назначение входов J и К такое же, как и входов R и S (сброс и установка). Буквы J и К были выбраны в свое… [читать подробенее]

Наиболее часто в цифровых интегральных микросхемах, а также в импульсных устройствах применяют триггеры с единственным входом данных D (data), так называемые D-триггеры. Одна из причин их появления была в том, что число выводов у корпусов микросхем ранних разработок не… [читать подробенее]

Вьетнамки

JK – Javatpoint

Триггер SR или триггер Set-Reset имеет множество преимуществ. Но у него есть следующие проблемы с переключением:

- Когда входы Set ‘S’ и Reset ‘R’ установлены на 0, этого условия всегда избегают.

- Когда вход Set или Reset меняет свое состояние, когда вход разрешения равен 1, происходит неправильное действие фиксации.

JK Flip Flop устраняет эти два недостатка SR Flip Flop.

Триггер JK – один из наиболее часто используемых в цифровых схемах.Триггер JK – это универсальный триггер с двумя входами «J» и «K». В SR-триггере «S» и «R» являются сокращенными сокращенными буквами для Set и Reset, а J и K – нет. J и K сами по себе являются автономными буквами, которые выбраны, чтобы отличать дизайн шлепанцев от других типов.

Триггер JK работает так же, как триггер SR. В шлепанцах JK вместо S и R используются триггеры J и K. Единственная разница между триггером JK и триггером SR заключается в том, что когда оба входа триггера SR установлены на 1, схема выдает недопустимые состояния как выходы, но в случае триггера JK недопустимые состояния отсутствуют, даже если оба Вьетнамки «J» и «K» установлены на 1.

JK Flip Flop – это стробируемый SR-триггер, имеющий добавленную схему входа тактовой частоты. Недопустимое или недопустимое условие выхода возникает, когда оба входа установлены на 1, и предотвращается добавлением входной схемы синхронизации. Итак, триггер JK имеет четыре возможных входных комбинации, то есть 1, 0, «без изменений» и «переключение». Обозначение триггера JK такое же, как у SR Bistable Latch , за исключением добавления тактового входа.

Блок-схема:

Принципиальная схема:

В триггере SR оба входа S и R заменены двумя входами J и K.Это означает, что вход J и K соответствует S и R соответственно.

Два логических элемента И с 2 входами заменены двумя логическими элементами И-НЕ с 3 входами. Третий вход каждого элемента подключен к выходам Q и Q ‘. Перекрестная связь триггера SR позволяет использовать предыдущее недопустимое условие (S = «1», R = «1») для выполнения «переключающего действия», поскольку два входа теперь заблокированы.

Если схема «установлена», вход J прерывается из положения «0» Q ‘через нижний логический элемент И-НЕ.Если схема “СБРОС”, ввод K прерывается с 0 позиций Q через верхний логический элемент И-НЕ. Поскольку Q и Q ‘всегда разные, мы можем использовать их для управления вводом. Когда оба входа «J» и «K» установлены в 1, JK переключает триггер в соответствии с заданной таблицей истинности.

Таблица истинности:

Когда оба входа триггера JK установлены на 1 и вход синхронизации также является импульсным «High», то из состояния SET в состояние RESET происходит переключение схемы. Триггер JK работает как триггер T-типа, когда оба его входа установлены на 1.

Триггер JK – это улучшенный триггер SR с тактовой частотой. Но он все еще страдает от проблемы “гонки” . Эта проблема возникает, когда состояние выхода Q изменяется до того, как синхронизирующий импульс тактового входа успевает пройти «Выкл» . Чтобы избежать этого периода, мы должны использовать короткие сроки плюс период (T).

Designing JK FlipFlop

Введение

Триггер JK назван в честь Джека Килби, инженера-электрика, который изобрел микросхему.Триггер JK называется универсальным программируемым триггером, потому что, используя его входы J, K Preset и Clear, можно имитировать работу любого другого триггера.

JK-триггер – это модификация SR-триггера без запрещенного состояния. В этом случае вход J аналогичен входу SET триггера SR, а вход K аналогичен входу RESET триггера SR. Символ триггера JK показан ниже.

Логическая схема триггера JK

Логическая схема триггера JK показана на рисунке ниже.Как было сказано ранее, триггер JK – это модифицированная версия триггера SR. Логическая схема состоит из трех входных ворот И-НЕ, заменяющих два входных элемента И-НЕ в триггере SR, а входы заменены на J и K из S и R.

Конструкция триггера JK такова, что три входа на один вентиль И-НЕ – это J, тактовый сигнал вместе с сигналом обратной связи от Q ‘и три входа для другого И-НЕ – это K, тактовый сигнал вместе с сигналом обратной связи от Q. Такая компоновка устраняет неопределенное состояние в триггере SR.

Таблица истинности

Вернуться к началу

Операция

Случай 1: когда оба входа J и K имеют НИЗКОЕ значение, тогда Q возвращает свое предыдущее значение состояния, т.е. он содержит предыдущие данные.

Когда мы применяем тактовый импульс к триггеру J K и вход J низкий, тогда, независимо от других вентилей И-НЕ, выход логического элемента И-1 становится ВЫСОКИМ. Таким же образом, если на входе K низкий уровень, то на выходе логического элемента И-2 также высокий уровень.Таким образом, выход остается в том же состоянии, то есть без изменений в состоянии триггера.

Случай 2: Когда J – НИЗКИЙ, а K – ВЫСОКИЙ, тогда триггер будет в состоянии сброса, то есть Q = 0, Q ‘= 1.

Когда мы подаем тактовый импульс к триггеру JK и входы: J низкий, а K высокий, выход логического элемента И-НЕ, подключенный к входу J, становится равным 1. Тогда Q становится 0. Это снова сбросит триггер в его предыдущее состояние. Таким образом, триггер будет в состоянии СБРОС.

Случай 3: Когда J – ВЫСОКОЕ, а K – НИЗКОЕ, тогда триггер будет в установленном состоянии, т.е. Q = 1, Q ‘= 0

Когда мы применяем тактовый импульс к триггеру JK и входы J – высокий уровень, а K – низкий, выход логического элемента И-НЕ, подключенного к входу K, становится равным 1. Тогда Q ‘становится равным 0. Это установит триггер на вход высокого тактового сигнала. Таким образом, триггер будет в состоянии SET.

Случай 4: Когда оба входа J и K имеют ВЫСОКИЙ уровень, то триггер находится в состоянии переключения.Это означает, что вывод будет дополнять предыдущее состояние.

Таблица истинности

Таблица истинности JK-триггера показана ниже.

Вернуться к началу

Гонка вокруг состояния JK-триггера

Для высоких входов JK-триггера только нижние вентили NAND запускаются выходами, которые дополняют друг друга, то есть Q и Q ’. Таким образом, пока высокие входы подключены к триггеру, в любой момент один вентиль включен, а другой – отключен.Если верхний вентиль находится в отключенном состоянии, он переводит триггер в состояние SET, позже, когда нижний вентиль включен, он переводит триггер в состояние RESET, что вызывает переключение выхода. Это вызовет состояние Race around в JK триггере.

Шаги по предотвращению состояния гонки

- Мы можем избежать условия гонки вокруг, установив время включения меньше, чем задержка распространения триггера. Это может быть достигнуто срабатыванием по фронту.

- Путем переключения триггера в течение одного периода времени.Эта концепция представлена в триггере Master Slave JK.

В начало

Главный-подчиненный JK-триггер

Мастер-подчиненный JK-триггер – это «синхронное» устройство, которое позволяет передавать данные в соответствии с синхронизацией тактового сигнала. Триггер «ведущий-ведомый» состоит из двух синхронизированных триггеров, соединенных последовательно, которые изолируют вход от выхода, отсюда и терминология «ведущий-ведомый». Помимо устранения проблемы “гонки вокруг” в обычных триггерах JK, триггеры JK “ведущий-ведомый” могут также имитировать функции триггера SR, синхронизированного триггера, D-триггера и Toggle-триггера.Выходы Q и Q ’ведомого триггера подаются обратно на главный триггер, в то время как выходы главного триггера подключаются как один из входов к ведомому триггеру.

Когда на входе тактовой частоты высокий уровень, ведущий активен, а ведомый неактивен. В зависимости от входов, выход главного триггера устанавливается или сбрасывается, а выход подчиненного триггера не изменяется и поэтому остается в предыдущем состоянии. Когда ведомый триггер становится активным при низком входном тактовом сигнале, выходы ведомого триггера изменяются.Когда часы высоки, выход ведущего триггера удерживается, так как ведомое устройство неактивно в течение этого периода. При низком тактовом сигнале выходной сигнал главного триггера виден подчиненному триггеру и передается на выход. Выход ведомого триггера является конечным выходом триггера ведущий-ведомый. Окончательный выход доступен в конце тактового импульса.

Конструкция

Триггер JK ведущего ведомого представляет собой каскадную комбинацию двух триггеров SR с обратной связью с выхода ведомого на вход ведущего.Схема триггера ведущий – ведомый показана ниже

Положительные тактовые импульсы подаются на ведущий триггер, и они инвертируются перед подачей на ведомый, т.е. ведущий триггер активен во время положительного перехода, пока ведомый триггер активен. во время отрицательного перехода. Во время положительного фронта тактового сигнала данные со входов J и K передаются на главный триггер и удерживаются там до появления отрицательного фронта перехода тактового сигнала. Затем данные или информация передаются ведомому триггеру, здесь собираются выходные данные.

Символьное представление JK-триггера ведущий-ведомый с двумя JK-триггерами показано ниже.

Таблица истинности JK триггера ведущий – ведомый вместе с предустановленными и очищенными входами показана ниже.

Когда на входе тактовой частоты низкий уровень, и два входа главного триггера, то есть входы J и K, не будут иметь никакого эффекта на выходе триггера Master Slave.

Когда на входе тактовый сигнал высокий

- Если J низкий, а K низкий: нет изменений в состоянии.

- Если J низкий, а K высокий: триггер Master Slave будет в состоянии сброса.

- Если J высокий, а K низкий: триггер Master Slave будет в установленном состоянии.

- Если J высокий, а K высокий: состояние переключения.

Временная диаграмма

Ширина входного импульса может быть меньше или больше задержки распространения триггера, это не влияет на состояние выхода. Но значение входов J и K в случае положительного фронта тактового сигнала будет влиять на состояние выхода триггера «ведущий – ведомый» при условии, что время установки и удержания не нарушается.

В начало

Приложения

Триггеры JK – одни из наиболее широко используемых триггеров в цифровой электронике. Это из-за их универсальной программируемой функции.

Некоторые из приложений JK-триггера включают

• Регистры сдвига

• Делители частоты

• Коммутационные приложения

• Параллельная передача данных

• Последовательная передача данных

• Двоичный счетчик

• Детектор последовательности

Одно из приложений JK flip флоп переключается.Это объясняется ниже.

Переключение JK-триггера