column%20address%20strobe — с немецкого на русский

дифференциальный манометр

дифманометр

Манометр для измерения разности двух давлений.

Примечание

Дифманометр с верхним пределом измерения не более 40000 Па (4000 кгс/м2) называется микроманометром.

[ГОСТ 8.271-77]

дифференциальный манометр

–

[Лугинский Я. Н. и др. Англо-русский словарь по электротехнике и электроэнергетике. 2-е издание – М.: РУССО, 1995 – 616 с.]

EN

differential-pressure gage

(engineering) Apparatus to measure pressure differences between two points in a system; it can be a pressured liquid column balanced by a pressured liquid reservoir, a formed metallic pressure element with opposing force, or an electrical-electronic gage (such as strain, thermal-conductivity, or ionization).

[ http://www.answers.com/topic/differential-pressure-gage#ixzz1gzzibWaQ]

Манометры дифференциальные сильфонные показывающие типа ДСП-160 нашли широкое применение на территории СНГ. Принцип их действия основан на деформации двух автономных сильфонных блоков, находящихся под воздействием «плюсового» и «минусового» давления. Эти деформации преобразовываются в перемещение указательной стрелки прибора. Перемещение стрелки осуществляется до установления равновесия между «плюсовым» сильфоном, с одной стороны, и «минусовым» и цилиндрической пружиной – с другой.

Рис. 2.23

Дифференциальный сильфонный манометр:

а – схема привода стрелки;

б – блок первичного преобразования;

1 – «плюсовый» сильфон;

2 – «минусовый» сильфон;

3 – шток;

4 – рычаг;

5 – торсионный вывод;

7 – компенсатор;

8 – плоскостный клапан;

9 – основание;

10 и 11 – крышки;

12 – подводящий штуцер;

13 – манжета;

14 – дросселирующий канал;

15 – клапан;

16 – рычажная система;

17 – трибко-секторный механизм;

18 – стрелка;

19 – регулировочный винт;

20 – натяжная пружина;

21 – пробка;

22 – уплотнительное резиновое кольцо

«Плюсовый» 1 и «минусовый» 2 сильфоны (рис. Рис. 2.23, б) соединены между собой штоком 3, функционально связанным с рычагом 4, который, в свою очередь, неподвижно закреплен на оси торсионного вывода 5. К концу штока на выходе «минусового» сильфона присоединена цилиндрическая пружина 6, закрепленная нижним основанием на компенсаторе 7 и работающая на растяжение. Каждому номинальному перепаду давления соответствует определенная пружина.

Рис. 2.23, б) соединены между собой штоком 3, функционально связанным с рычагом 4, который, в свою очередь, неподвижно закреплен на оси торсионного вывода 5. К концу штока на выходе «минусового» сильфона присоединена цилиндрическая пружина 6, закрепленная нижним основанием на компенсаторе 7 и работающая на растяжение. Каждому номинальному перепаду давления соответствует определенная пружина.

«Плюсовый» сильфон состоит из двух частей. Его первая часть (компенсатор 7, состоящий из трех дополнительных гофр и плоскостных клапанов 8) предназначена для уменьшения температурной погрешности прибора из-за изменения объема жидкости-наполнителя, обусловленного варьированием температуры окружающего воздуха. При изменении температуры окружающей среды и соответственно рабочей жидкости ее увеличивающийся объем перетекает через плоскостный клапан во внутреннюю полость сильфонов. Вторая часть «плюсового» сильфона рабочая и идентична по конструкции «минусовому» сильфону.

«Плюсовый» и «минусовый» сильфоны присоединены к основанию 9, на котором установлены крышки 10 и 11, образующие вместе с сильфонами «плюсовую» и «минусовую» камеры с соответствующими подводящими штуцерами 12 давления р + и р

Внутренние объемы сильфонов, так же как и внутренняя полость основания 9, заполняются: жидкостью ПМС-5 для обычного и коррозионно-стойкого исполнений; составом ПЭФ-703110 – в кислородном варианте; дистиллированной водой – в варианте для пищевой промышленности и жидкостью ПМС-20 – для газового исполнения.

В конструкциях дифманометров, предназначенных для измерения давления газа, на шток одета манжета 13, движение среды организовано через дросселирующий канал 14. Регулированием размера проходного канала с помощью клапана 15 обеспечивается степень демпфирования измеряемого параметра.

Дифманометр работает следующим образом. Среды «плюсового» и «минусового» давления поступают через подводящие штуцеры в «плюсовую» и «минусовую» камеры соответственно. «Плюсовое» давление в большей степени воздействует на сильфон 1, сжимая его. Это приводит к перетоку находящейся внутри жидкости в «минусовый» сильфон, который растягивается и разжимает цилиндрическую пружину. Такая динамика происходит до уравновешивания сил взаимодействия между «плюсовым» сильфоном и парой – «минусовый» сильфон – цилиндрическая пружина. Мерой деформации сильфонов и их упругого взаимодействия служит перемещение штока, которое передается на рычаг и соответственно на ось торсионного вывода. На этой оси (рис. 2.23,а) закреплена рычажная система 16, обеспечивающая передачу вращения оси торсионного вывода к трибко-секторному механизму 17 и стрелке 18.

Регулировочным винтом 19 с помощью натяжной пружины 20 производится корректировка нулевой точки прибора.

Пробки 21 предназначены для продувки импульсных линий, промывки измерительных полостей сильфонного блока, слива рабочей среды, заполнения измерительных полостей разделительной жидкостью при вводе прибора в работу.

При односторонней перегрузке одной из камер происходит сжатие сильфона и перемещение штока. Клапан в виде уплотнительного резинового кольца 22 садится в гнездо основания, перекрывает переток жидкости из внутренней полости сильфона, и таким образом предотвращается его необратимая деформация. При непродолжительных перегрузках разность «плюсового» и «минусового» давления на сильфонный блок может достигать 25 МПа, а в отдельных типах приборов не превышать 32 МПа.

Рис. 2.24

Показывающий дифференциальный манометр на основе мембранной коробки:

1 – мембранная коробка;

2 – держатель «плюсового» давления;

3 – держатель «минусового» давления;

4 – корпус;

5 – передаточный механизм;

6 – стрелка;

7 – цифербла

Достаточно широкое распространение получили

«Минусовое» давление через подводящий штуцер держателя 3 подается внутрь герметичного корпуса 4 прибора и воздействует на мембранную коробку снаружи, создавая противодействие перемещению ее подвижного центра. Таким образом «плюсовое» и «минусовое» давления уравновешивают друг друга, а перемещение подвижного центра мембранной коробки свидетельствует о величине разностного – дифференциального давления. Этот сдвиг через передаточный механизм передается на указательную стрелку 6, которая на шкале циферблата 7 показывает измеряемое дифференциальное давление.

Этот сдвиг через передаточный механизм передается на указательную стрелку 6, которая на шкале циферблата 7 показывает измеряемое дифференциальное давление.

Диапазон измеряемого давления определяется свойствами мембран и ограничивается, как правило, в пределах от 0 до 0,4…40 кПа. При этом класс точности может составлять 1,5; 1,0; 0,6; 0,4, а в некоторых приборах 0,25.

Обязательная конструктивная герметичность корпуса определяет высокую защищенность от внешних воздействий и определяется в основном уровнем IP66.

В качестве материала для чувствительных элементов приборов используется бериллиевая и другие бронзы, а также нержавеющая сталь, для штуцеров, передаточных механизмов – медные сплавы, коррозионно-стойкие сплавы, включая нержавеющую сталь.

Приборы могут изготавливаться в корпусах малых (63 мм), средних (100 мм), и больших (160 мм) диаметров.

Мембранные показывающие дифференциальные манометры, как и приборы с мембранными коробками, используются для измерения малых значений дифференциального давления. Отличительная особенность – устойчивая работа при высоком статическом давлении.

Отличительная особенность – устойчивая работа при высоком статическом давлении.

Рис. 2.25

Мембранные показывающие дифференциальные манометры с вертикальной мембраной:

1 – «плюсовая» камера;

2 – «минусовая» камера;

3 – чувствительная гофрированная мембрана;

4 – передающий шток;

5 – передаточный механизм;

6 – предохранительный клапан

Дифманометр с вертикальной мембраной (Рис. 2.25) состоит из «плюсовой» 1 и «минусовой» 2 рабочих камер, разделенных чувствительной гофрированной мембраной 3. Под воздействием давления мембрана деформируется, в результате чего перемещается ее центр вместе с закрепленным на нем передающим штоком 4. Линейное смещение штока в передаточном механизме 5 преобразуется в осевое вращение трибки, и соответственно указательной стрелки, отсчитывающей на шкале прибора измеряемое давление.

Для сохранения работоспособности чувствительной гофрированной мембраны при превышении максимального допустимого статического давления предусмотрен открывающийся предохранительный клапан 6.

Рис. 2.26

Мембранный показывающий дифференциальный манометр с горизонтальной мембраной:

1 – «плюсовая» камера;

2 – «минусовая» камера;

3 – входной блок;

4 – чувствительная гофрированная мембрана;

5 – толкатель;

6 – сектор;

7 – трибка;

8 – стрелка;

9 – циферблат;

10 – разделительный сильфон

Дифманометр с горизонтальной чувствительной мембраной показан на рис. 2.26. Входной блок 3 состоит из двух частей, между которыми устанавливается гофрированная мембрана 4. В ее центре закреплен толкатель 5, передающий перемещение от мембраны, через сектор 6, трибку 7 к стрелке 8. В этом передаточном звене линейное перемещение толкателя преобразуется в осевое вращение стрелки 8, отслеживающей на шкале циферблата 9 измеряемое давление.

Конструкция входного блока предусматривает возможность промывки или продувки «плюсовой» и «минусовой» камер и обеспечивает применение таких приборов для работы даже в условиях загрязненных рабочих сред.

Рис. 2.27

Мембранный двухкамерный показывающий дифманометр:

1 – «плюсовая» камера;

2 – «минусовая» камера;

3 – передающий шток;

4 – сектор;

5 – трибка;

6 – коромысло

Двухкамерная система измерения дифференциального давления применена в конструкции прибора, показанного на рис. 2.27. Измеряемые потоки среды направляются в «плюсовую» 1 и «минусовую» 2 рабочие камеры, основными функциональными элементами которых являются автономные чувствительные мембраны. Преобладание одного давления над другим приводит к линейному перемещению передающего штока 3, которое через коромысло 6 передается соответственно на сектор 4, трибку 5 и систему стрелочной индикации измеряемого параметра.

Преобладание одного давления над другим приводит к линейному перемещению передающего штока 3, которое через коромысло 6 передается соответственно на сектор 4, трибку 5 и систему стрелочной индикации измеряемого параметра.

Дифманометры с двухкамерной системой измерения используются для измерения малых дифференциальных давлений при высоких статических нагрузках, вязких сред и сред с твердыми вкраплениями.

Рис. 2.28.

Дифманометр с магнитным преобразователем:

1 – поворотный магнит;

2 – стрелка;

3 – корпус;

4 – магнитный поршень;

5 – фторопластовый сальник;

6 – рабочий канал;

7 – пробка;

8 – диапазонная пружина;

9 – блок электроконтактов

Принципиально иной показывающий дифманометр изображен на рис. 2.28. Поворотный магнит 1, на торце которого установлена стрелка 2, размещен в корпусе 3, выполненном из немагнитного металла. Магнитный поршень, уплотненный фторопластовым сальником 5, может передвигаться в рабочем канале 6. Магнитный поршень 4 со стороны «минусового» давления подпирает пробка 7, в свою очередь поджимаемая диапазонной пружиной 8.

Магнитный поршень 4 со стороны «минусового» давления подпирает пробка 7, в свою очередь поджимаемая диапазонной пружиной 8.

Среда «плюсового» давления через соответствующий подводящий штуцер воздействует на магнитный поршень и сдвигает его вместе с пробкой 7 по каналу 6 до уравновешивания такого смещения противодействующими силами – «минусовым» давлением и диапазонной пружиной. Движение магнитного поршня приводит к осевому вращению поворотного магнита и соответственно указательной стрелки. Такой сдвиг пропорционален перемещению стрелки. Полное согласование достигается подбором упругих характеристик диапазонной пружины.

В дифманометре с магнитным преобразователем предусмотрен блок 9, замыкающий и размыкающий соответствующие контакты при прохождении вблизи его магнитного поршня.

Приборы с магнитным преобразователем устойчивы к воздействию статического давления (до 10 МПа). Они обеспечивают относительно невысокую погрешность (примерно 2 %) в диапазоне функционирования до 0,4 Мпа и используются для измерения давления воздуха, газов, различных жидкостей.

[ http://jumas.ru/index.php?area=1&p=static&page=razdel_2_3_2]

Показывающий дифференциальный манометр на основе трубчатой пружины

1 и 2 – держатели;

3 и 4 – трубчатые пружины;

5 и 8 – трибки;

6 – стрелка «плюсового» давления;

7 и 9 – шкалы избыточного давления;

10 – стрелка «минусового» давления

В приборах такого типа на автономных держателях 1 и 2, соединенных вместе, установлены трубчатые пружины. Каждый держатель вместе с трубчатым чувствительным элементом образовывают автономные измерительные каналы. Среда «плюсового» давления поступает через входной штуцер держателя 2 в трубку 4, деформирует ее овал, в результате чего перемещается наконечник трубки и это перемещение через соответствующий зубчатый сектор передается на трибку 5. Эта трибка соответственно приводит к отклонению указательной стрелки 6, которая показывает на шкале 7 значение «плюсового» избыточного давления.

«Минусовое» давление посредством держателя 1, трубчатой пружины 3, трибки 8 приводит к перемещению циферблата 9, объединенного со стрелкой 10, которая на шкале 7 отслеживает значение измеряемого параметра.

Дифференциальные манометры (далее – дифманометры), как отмечалось в п.1.3, являются названием отнесенным в нашей стране к показывающим приборам. (Устройства, обеспечивающие электрический выходной сигнал, пропорциональный измеряемому дифференциальному давлению имеют название измерительных преобразователей разности давлений). Хотя отдельные производители, а также некоторые специалисты-эксплуатанционщики измерительные преобразователи разности давлений также называют дифманометрами.

Дифманометры нашли основное применение в технологических процессах для измерения, контроля, регистрации и регулирования следующих параметров:

· расхода различных жидких, газообразных и парообразных сред по перепаду давления на разного рода сужающих устройствах (стандартных диафрагмах, соплах, включая сопла Вентури) и дополнительно вводимых в поток гидро- и аэродинамических сопротивлениях, например на преобразователях типа Annubar или на нестандартных гидро- и аэродинамических препятствиях;

· перепада – разности давления, вакуумметрических, избыточных, в двух точках технологического цикла, включая потери на фильтрах систем вентиляции и кондиционирования воздуха;

· уровня жидких сред по величине гидростатического столба.

Согласно ГОСТ 18140–84/23/, предельные номинальные перепады давления дифманометров-расходомеров, верхние пределы или сумма абсолютных значений верхних пределов измерений дифманометров-перепадомеров должны приниматься из следующего ряда:

10; 16; 25; 40; 63; 100; 160; 250; 400; 630 Па;

1; 1,6; 2,5; 4; 6,3; 10; 16; 25; 40; 63; 100; 160; 250; 400; 630 кПа;

1; 1,6; 2,5; 4; 6,3 МПа.

У дифманометров-расходомеров верхние пределы измерений выбираются из ряда, определяемого выражением:

А = а × 10n, (2.7)

где а – одно из чисел следующего ряда: 1; 1,25; 1,6; 2,0; 2,5; 3,2; 4; 5; 6,3; 8; n – целое (положительное или отрицательное) число или нуль.

Верхние пределы измерений или сумма абсолютных значений верхних пределов измерений дифманометров-уровнемеров следует выбирать и ряда:

0,25; 0,4; 0,63; 1,0; 1,6; 2,5; 4,0; 6,3; 10; 16; 25; 40; 63; 100 и 160 метров.

Одной из важных характеристик дифманометров является предельно допустимое рабочее избыточное давление, т. е. избыточное давление, которое могут выдержать рабочие каналы без необратимой деформации чувствительных элементов. Такое значение параметра принимается из следующего ряда:

е. избыточное давление, которое могут выдержать рабочие каналы без необратимой деформации чувствительных элементов. Такое значение параметра принимается из следующего ряда:

25; 40; 63; 100; 160; 250; 400 и 630 кПа;

1; 1,6; 2,5; 4; 6,3; 10; 16; 25; 32; 40 и 63 МПа.

Нижние пределы измерений дифманометров-расходо-меров из-за неустойчивости работы стандартных сужающих устройств при малых Числах Рейнольдса измеряемого потока не должны превышать 30 % шкалы прибора. У преобразователей Annubar этот предел не превышает 10 % при сохранении объявленного класса точности (1,0).

Классы точности дифманометров принимаются из ряда: 0,25; 0,5; 1,0; 1,5.

Дифманометры должны иметь линейную шкалу при измерении уровня или перепада, линейную или квадратичную – при измерении расхода.

Дифманометры могут иметь условные обозначения, предложенные в методике п.1.4. Указываются модель прибора, причем на первом месте в обозначении фиксируется измеряемый параметр – тип измерителя (дифманометр), затем – принцип измерения и функция, предельный номинальный перепад, избыточное рабочее давление, класс точности. Например, дифманометр сильфонный показывающий в корпусе диаметром 160 мм, на предельный номинальный перепад давления 630 кПа, с рабочим избыточным давлением 32 МПа, класса точности 1,5 обозначается как

ДСП 160 (0…630 кПа)-32 МПа-1,5.

После этого допускается указывать дополнительные обозначения, например исполнение по «IP», измеряемой среде, присоединительным линиям и т. д.

Специфика измерения дифференциального давления обусловливает наличие в дифманометрах устройств продувки импульсных линий без необходимости демонтажа прибора или его узлов.

При испытаниях, а также в нормальных условиях отечественные дифманометры, согласно требований производителя, должны обеспечивать заданные метрологические характеристики после выдержки не менее 6-ти часов при температуре окружающей среды:

20 ± 2 или 23 ± 2 оС – для приборов классов точности 0,5; 0,6 и 1;

20 ± 5 или 23 ± 5 оС – для приборов класса точности 1,5.

Современные конструкции из-за снижения металлоемкости и совершенствования преобразователей позволяют сокращать время температурной адаптации у некоторых моделей до нескольких десятков минут.

Конкретная температура приведена в ТУ на измеритель и должна регистрироваться в техническом описании или паспорте на прибор.

Дифманометры, не защищенные от одностороннего воздействия, должны выдерживать перегрузку со стороны среды «плюсового» давления, превышающую предельные номинальные перепады на 10…50 %. «Плюсовым», в противовес «минусовому», называют большее из двух давлений среды, поступающей на вход дифференциального манометра.

Конструкции, у которых предусмотрены односторонние перегрузки, должны выдерживать десятикратные, стократные или двухсот пятидесятикратные односторонние перегрузки/23/.

Показывающие дифференциальные манометры на основе трубчатой пружины находят широкое применение для визуализации расхода различных сред, гидродинамических потерь в системах теплового отопления.

Дифференциальное давление, т. е. разность давлений р отсчитывается стрелкой на шкале циферблата.

Дифманометры такого типа, исходя из особенностей трубчатых пружин, обеспечивают работоспособность в промышленных условиях в диапазоне от 0 до 100 МПа.

[ http://jumas.ru/index.php?area=1&p=static&page=razdel2_2_4]

Тематики

Синонимы

EN

DE

FR

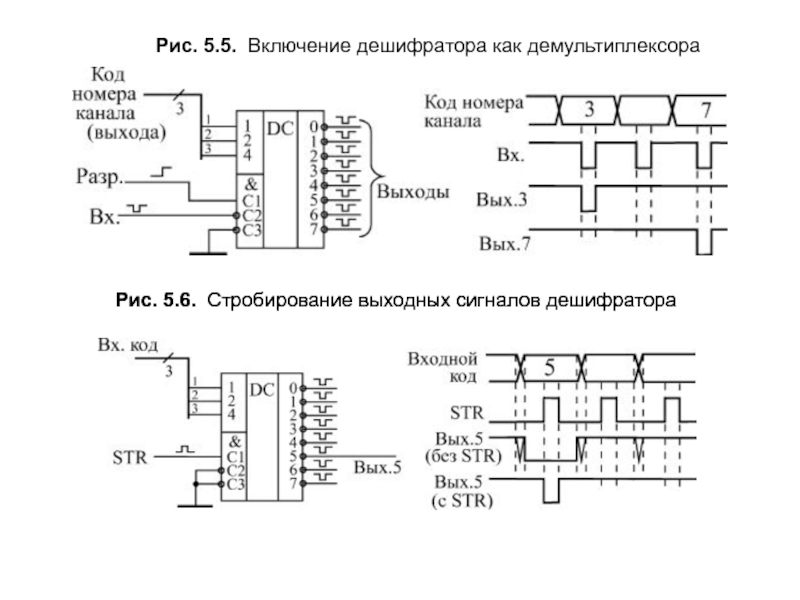

Лекции стр13.”Цифровая схемотехника”

Лекции стр13.”Цифровая схемотехника”Мультиплексор

Правила синтеза устройств на мультиплексоре

ДемультиплексорМультиплексор – это комбинационное логическое устройство, предназначенное для управляемой передачи данных от нескольких источников информации в один выходной канал.

Мультиплексор – цифровые позиционные переключатели, т.е. мультиплексор назначение коммутировать на одну выходную линию сигналы от различных выходных источников, следовательно мультиплексор имеет 3 группы входов :

1)информационные,

2)адресные – двоичный код, на котором определяется какой из информационных входов подключен к выходу;

3) стробирующие (разрешающие)

При разрядности адреса n, число информационных входов 2n.

Функционирование мультиплексора отражено в таблице истинности :

c |

А1 |

А0 |

Q |

|

1 |

х |

х |

0 |

1 |

0 |

0 |

0 |

D0 |

0 |

0 |

0 |

1 |

D1 |

1 |

0 |

1 |

0 |

D2 |

2 |

0 |

1 |

1 |

D3 |

3 |

При подаче на стробирующий вход активного логического сигнала (лог.1) , выходной сигнал постоянен и не зависит от входных сигналов.

ФАЛ:

MS: Q = D0A1A0cV D1A1A0cV D2A1A0cV D3A1A0cV

Можно составить логическую схему 2 порядка:

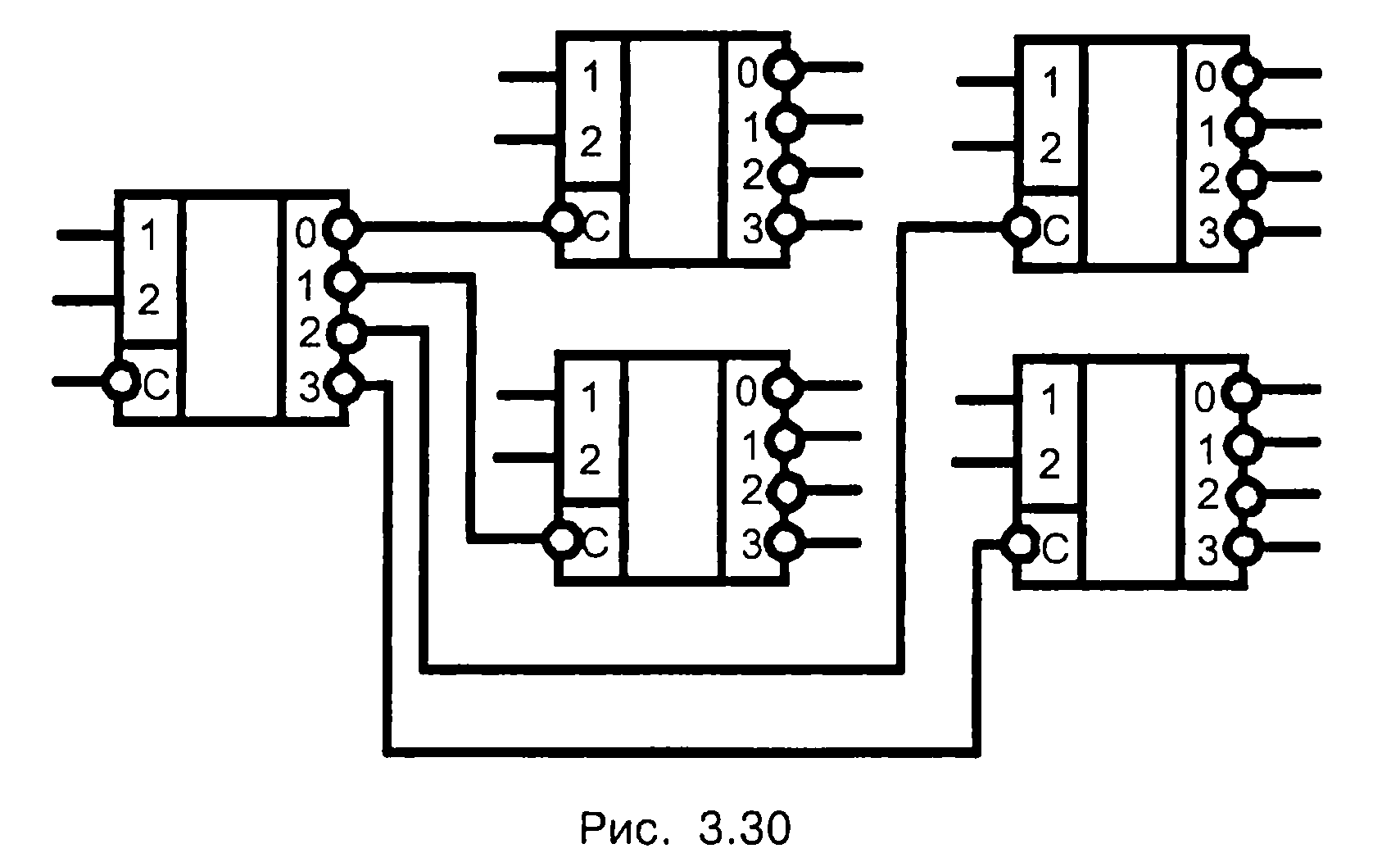

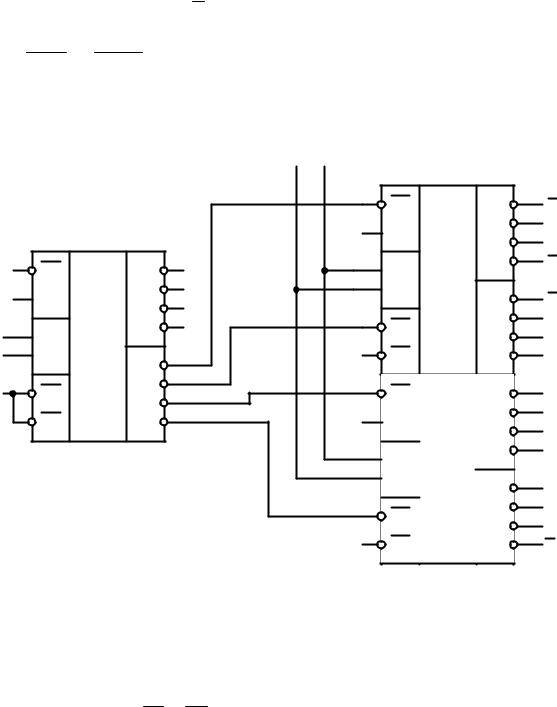

Число информационных входов в реально выпускаемых ИМС МS не превышает 16.

Если необходимо иметь большее число входов, то из имеющихся ИМС строят структуру мультимплексорного дерева.

Дано адресное слово 0110 МS I уровня входом D2, что соответствует младшим разрядам адресного слова 10, подключается к входам MS II уровня, т.е. будут поданы х2,х6, х10, х14.

МS II уровня выберет по старшим разрядам адресное слово 01 сигнал на D1, т.е. х6.Использование мультиплексора для синтеза комбинационных устройств.

Мультиплексор может быть использован для синтеза любого логического устройства. При этом может быть достигнуто значительное снижение числа используемых в схеме элементов.

Правила синтеза устройств на мультиплексоре

- Построить карту Карно выходной функции ( по переменным функциям)

- Выбрать порядок мультиплексора, который будет использоваться в схеме.

- Построить маскирующую матрицу, которая соответствует порядку выбранного мультиплексора.

- Наложить маскирующую матрицу на карту Карно.

- Минимизировать функцию в каждой области маскирующей матрицы отдельно.

- Результат минимизации записывается по тем переменным, которые не подаются на адресные входы мультиплексора.

- По результатам минимизации строится схема, которая может содержать и логический элемент.

Подробнее рассмотрим на примерах:

- Функция трех переменных на мультиплексоре третьего порядка

Функция трех переменных на мультиплексоре второго порядка.Функция четырех переменных на мультиплексоре второго порядка.

Демультиплексор – комбинационное логическое устройство, предназначенное для управляемой передачи данных от одного источника информации на несколько выходных каналов.

В общем случае:

Демультиплексор имеет один информационный вход, n адресных входов, 2n выхода и вход разрешения:

Таблица истинности

E |

А1 |

А0 |

y0 |

y1 |

y2 |

y3 |

1 |

x |

x |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

D |

0 |

0 |

0 |

0 |

0 |

1 |

0 |

D |

0 |

0 |

0 |

1 |

0 |

0 |

0 |

D |

0 |

0 |

1 |

1 |

0 |

0 |

0 |

D |

Используются технологии uCozПри подаче на информационный вход D=1 DMS>DC

ФАЛ: y0=DA1A0E

y1= DA1A0E

y2=DA1A0E

y3=DA1A0E

исходя из выше сказанного , можно построить логическую схему:Вернутся к содержанию…

Мультиплексоры и демультиплексоры: определение, назначение, устройство

Что такое мультиплексор?Мультиплексором — называют комбинационное устройство, обеспечивающее передачу в желаемом порядке цифровой информации, поступающей по нескольким входам на один выход. Мультиплексоры обозначают через MUX (от англ. multiplexor), а также через MS (от англ. multiplex or selector).

Васильев Дмитрий Петрович

Профессор электротехники СПбГПУ

Задать вопрос

Схематически мультиплексор можно изобразить в виде коммутатора, обеспечивающего подключение одного из нескольких входов (их называют информационными) к одному выходу устройства. Кроме информационных входов в мультиплексоре имеются адресные входы и, как правило, разрешающие (стробирующие).

Сигналы на адресных входах определяют, какой конкретно информационный канал подключен к выходу. Если между числом информационных входов n и числом адресных входов m действует соотношение n = 2m, то такой мультиплексор называют полным. Если n< 2m, то мультиплексор называют неполным.

Абрамян Евгений Павлович

Доцент кафедры электротехники СПбГПУ

Разрешающие входы используют для расширения функциональных возможностей мультиплексора. Они используются для наращивания разрядности мультиплексора, синхронизации его работы с работой других узлов. Сигналы на разрешающих входах могут разрешать, а могут и запрещать подключение определенного входа к выходу, т. е. могут блокировать действие всего устройства.

Функционирование двухвходового мультиплексора

Рассмотрим функционирование двухвходового мультиплексора (2 →1), который условно изображен в виде коммутатора, а состояние его входов Х1Х2 и выхода Y приведено в таблице (рис. 3.41).

Исходя из таблицы, можно записать следующее уравнение:

Y = X1A + X2A

На рис. 3.42 показаны реализация такого устройства и его условное графическое обозначение.

Основой данной схемы являются две схемы совпадения на элементах И, которые при логическом уровне «1» на одном из своих входов повторяют на выходе то, что есть на другом входе.

Если необходимо расширить число входов, то используют каскадное включение мультиплексоров. В качестве примера рассмотрим мультиплексор с четырьмя входами (4 → 1), построенный на основе мультиплексоров (2 → 1).

Схема и таблица состояний такого мультиплексора приведены на рис.3.43.

Мультиплексоры являются универсальными логическими устройствами, на основе которых создают различные комбинационные и последовательностные схемы. Мультиплексоры могут использоваться в делителях частоты, триггерных устройствах, сдвигающих устройствах и др.

Абрамян Евгений Павлович

Доцент кафедры электротехники СПбГПУ

Задать вопрос

Мультиплексоры часто используют для преобразования параллельного двоичного кода в последовательный. Для такого преобразования достаточно подать на информационные входы мультиплексора параллельный двоичный код, а сигналы на адресные входы подавать в такой последовательности, чтобы к выходу поочередно подключались входы, начиная с первого и кончая последним.

Мультиплексор как устройство сдвига

Рассмотрим пример использования мультиплексоров для реализации так называемого комбинационного устройства сдвига, обеспечивающего сдвиг двоичного, числа по разрядам. Принцип функционирования данного устройства понятен из схемы устройства и таблицы состояний его входов и выходов (рис. 3.44).

В обозначении мультиплексоров используют две русские буквы КП, например, промышленностью выпускаются такие мультиплексоры, как К155КП1, К531КШ8, К561КПЗ, К555КП17 и др.

Орлов Анатолий Владимирович

Начальник службы РЗиА Новгородских электрических сетей

Демультиплексором называют устройство, в котором сигналы с одного информационного входа, поступают в желаемой последовательности по нескольким выходам в зависимости от кода на адресных шинах. Таким образом, демультиплексор в функциональном отношении противоположен мультиплексору. Демультиплексоры обозначают через DMX или DMS.Если соотношение между числом выходов n и числом адресных входов m определяется равенством n= 2m, то такой демультиплексор называется полным, при n< 2m демультиплексор является неполным.

Функционирование демультиплексора с двумя выходами

Рассмотрим функционирование демультиплексора с двумя выходами, который условно изображен в виде коммутатора, а состояние его входов и выходов приведено в таблице (рис. 3.45).

Из этой таблицы следует: Y1=X·А Y2 = X·А т. е. реализовать такое устройство можно так, как показано на рис. 3.46.

Для наращивания числа выходов демультиплексора используют каскадное включение демультиплексоров. В качестве примера (рис. 3.47) рассмотрим построение демультиплексоров с 16 выходами (1 → 16) на основе демультиплексоров с 4 выходами (1 → 4).

При наличии на адресных шинах А0 и А1 нулей информационный вход X подключен к верхнему выходу DМХ0 и в зависимости от состояния адресных шин А2 и А3 он может быть подключен к одному из выходов DMX1. Так, при А2 = А3 = 0 вход X подключен к Y0. При А0 = 1 и А1 = 0 вход X подключен к DMX2, в зависимости от состояния А2 и А3 вход соединяется с одним из выходов Y4 − Y7 и т.д.

Функции демультиплексоров

Функции демультиплексоров сходны с функциями дешифраторов. Дешифратор можно рассматривать как демультиплексор, у которого информационный вход поддерживает напряжение выходов в активном состоянии, а адресные входы выполняют роль входов дешифратора.

Поэтому в обозначении как дешифраторов, так и демультиплексоров используются одинаковые буквы — ИД. Выпускают дешифраторы (демультиплексоры) К155ИДЗ, К531ИД7 и др.

При использовании КМОП-технологии можно построить двунаправленные ключи, которые обладают возможностью пропускать ток в обоих направлениях и передавать не только цифровые, но и аналоговые сигналы. Благодаря этому можно строить мультиплексоры-демультиплек-соры, которые могут использоваться либо как мультиплексоры, либо как демультиплексоры.

Мультиплексоры-демультиплексоры обозначаются через MX. Среди выпускаемых мультиплексоров-демультиплексоров можно выделить такие, как К564КП1, К590КП1. Мультиплексоры-демультиплексоры входят в состав серий К176, К561, К591, К1564.

Условное графическое обозначение и принцип действия

Мультиплексор это управляемый кодом электронный коммутатор, который соединяет один из своих m информационных входов с выходом (рис. 3.2). Десятичный номер соединяемого входа есть эквивалент двойного хода на n адресных входах.

Информационные и адресные входы мультиплексора находятся в

следующем соотношении:

m = 2n .

Кроме информационных и адресных входов, некоторые мультиплекаторы имеют еще разрешающий (стробирующий) вход Е

с активным лог. “0”, то есть при мультиплексора разрешено.

E = 0

функционирование

Рис. 3.2. Условное графическое обозначение мультиплексора

Условное графическое обозначение мультиплексора,

имеющего восемь информационных

D0 …D 7 , три адресных

A 0 …A 2

входов, разрешающий вход Е, прямой Y и инверсный Y выход, приведено рис. 3.2. В основном поле мультиплексора указано обозначение выполняемой функции – MUX. Следует заметить, что

адресные входы

A 0 …A 2

обеспечивают выбор (селекцию) данных, то

есть мультиплексоры способны выбирать (селектировать) определенный канал. Поэтому их иногда называют селекторами. Используется и двойное название мультиплексор-селектор, для обозначения которого ГОСТом предусмотрен символ MS.

Мультиплексор, представленный на рис. 3.2, реализует логическую функцию:

y = E(D0 A 2 A1A 0 + D1A 2 A1A 0 0 + D2 A 2 A1A 0 + D3 A 2 A1A 0 0 + D4 A 2 A1A 0 +

+ D5 A 2 A1A 0 0 + D6 A 2 A1A 0 + D7 A 2 A1A 0 )

и функционирует согласно табл. 3.1.

Таблица 3.1

Входы | Выходы | ||||

E | A2 | A1 | A0 | y | y |

0 | 0 | 0 | 0 | D0 | D0 |

0 | 0 | 0 | 1 | D1 | D1 |

0 | 0 | 1 | 0 | D2 | D2 |

0 | 0 | 1 | 1 | D3 | D3 |

0 | 1 | 0 | 0 | D4 | D4 |

0 | 1 | 0 | 1 | D5 | D5 |

0 | 1 | 1 | 0 | D6 | D6 |

0 | 1 | 1 | 1 | D7 | D7 |

1 | x | x | x | 0 | 1 |

Если на стробирующем входе лог. “0” ( E = 0 ), то

управляющие входы

A 0 …A 2

выбирают в соответствии с двоичным

кодом, поданным на эти входы, канал и соединяют его с выходами

Y и Y .

Логический сигнал, соответствующий выбранному каналу,

проходит на выход Y в прямом виде ( Di ), а на выход Y в

инверсном ( Di ). Если

E = 1, то независимо от сигналов на адресных

входах на прямом входе устанавливается сигнал лог. “0”, а на инверсном лог. “1”.

Мультиплексоры выполнены в виде отдельных ИМС, различаются числом информационных и адресных входов, отсутствием или наличием входа разрешение, а также видом выхода (стандартный и с тремя состояниями) и видом передачи информации с инверсией и без инверсии. Некоторые мультиплексоры имеют два выхода как инверсный, так и прямой.

ИМС мультиплексоров ТТЛ и КМОП имеют существенные структурные и функциональные отличия, поэтому рассмотрим их раздельно.

Материал взят из книги Цифровые интегральные микросхемы (Асмолов Г.И.)

2.1.Регенераторы. Параметры регенераторов. Определение длины регенерационного участка.

Рисунок 2.1. Принцип регенерации цифрового сигнала

Пороговое напряжение может подаваться извне или вырабатываться в схеме РУ. При поступлении импульса на выходе РУ появляется управляющий сигнал, а в случае 0 (.пробела) состояние РУ не изменяется. Формирующее устройство (ФУ) обеспечивает формирование по сигналам РУ импульсов с принятыми для конкретной системы стандартными параметрами. В приведенной выше схеме, характерной для современных регенераторов, регистрация входящего сигнала и принятие решения о его значении осуществляются по каждому символу в отдельности (возможно принятие решений по всей кодовой комбинации или по циклу, так называемый «прием в целом»), что значительно упрощает реализацию схемы регенератора. Однако при этом требуется введение устройства тактовой синхронизации (УТС), которое должно обеспечить принятие решений на определенных временных интервалах. Эти интервалы выбираются в пределах участков тактового интервала, на которых принимаемый импульс имеет минимальные искажения, так как выбор момента регистрации в менее искаженной части импульса гарантирует верность принятия решения РУ.

Верность принимаемых РУ решений зависит, в первую очередь, от способа обнаружения двоичного сигнала и качества работы УТС. При безошибочной работе РУ каждому входному импульсу соответствует выходной, а каждому «пробелу» на входе – «.пробел» на выходе. Однако из-за присутствия на входе РУ различных помех, несовершенства устройства тактовой синхронизации и других причин в процессе регенерации возможны ошибки, выражающиеся в преобразовании 1 на входе регенератора в 0 на выходе и наоборот входного 0 в выходную 1.

Построение регенераторов.

Регенераторы современных ЦСП классифицируются по методу регистрации импульсов, виду тактовой синхронизации, методам получения колебания тактовой частоты и использования синхросигнала в процессе регенерации импульсов. По методам регистрации импульсов различают регенераторы с однократным и многократным стробированием импульса цифрового сигнала. Практическое применение, благодаря достаточной простоте реализации узлов регистрации нашли регенераторы с однократным стробированием, в которых на протяжении одного символа цифрового сигнала берется один отсчет и с помощью РУ устанавливается наличие 1 или 0 на входе регенератора. По видам синхронизации различают регенераторы с внешней и внутренней синхронизацией.

При использовании внешней синхронизации цифровой сигнал в оконечном оборудовании линейного тракта объединяют с синхросигналом, получаемым от специальных УТС. При внешней синхронизации возможна также передача сигналов тактовой синхронизации по отдельному тракту. Оба способа внешней синхронизации требуют значительного усложнения оборудования системы и неэкономичны. Передача синхросигнала по отдельному тракту связана с необходимостью выравнивания группового времени распространения для информационных и синхротрактов. Совместная передача цифрового и синхросигналов кроме усложнения оборудования передачи приводит к усложнению схем регенераторов из-за необходимости осуществления процессов выделения тактовой частоты, подавления на входе регенератора составляющих цифрового сигнала, близких к тактовой частоте, объединения на выходе регенератора цифрового сигнала и сигнала тактовой синхронизации. Исходя из этого, на практике чаще всего используются регенераторы с внутренней синхронизацией, в которых тактовая синхронизирующая частота выделяется из цифрового сигнала. В зависимости от способа получения тактовой частоты регенераторы с внутренней синхронизацией подразделяются на регенераторы с пассивной и активной фильтрацией тактовой частоты. При активной фильтрации для формирования колебания тактовой частоты используются генераторы с фазовой автоподстройкой либо генераторы, синхронизируемые входящим цифровым сигналом. При пассивной фильтрации для выделения колебания тактовой частоты используются избирательные цепи типа, резонансных контуров, многоконтурных схем, фильтров.

Типовая структура УТС регенератора с внутренней синхронизацией и пассивной фильтрацией тактовой частоты представлена на (рисунке 2.2).

Рисунок 2.2. Структурная схема УТС

Устройство нелинейного преобразования (НП) входного сигнала позволяет получить в спектре преобразованного сигнала составляющую с частотой, равной тактовой fт, которая может быть выделена устройством фильтрации тактовой частоты (ФТЧ) и направлена в формирователь стробирующих импульсов (ФСИ). Формирователь стробирующих импульсов формирует импульсы с частотой следования, равной выделенной fт, определяющей промежутки времени стробирования для РУ и управляющей работой формирующего устройства (ФУ). При активной фильтрации структура УТС несколько видоизменяется (рисунок 2.3). Ток тактовой частоты с выхода ФТЧ поступает на ФД. на второй вход, которого подается тактовый сигнал от местного генератора тактовой частоты ГТЧ. Фазовый детектор вырабатывает управляющее напряжение Uy, пропорциональное разности фаз сигналов на входах ФД, которое поступает на вход цепи фазовой автоподстройки частоты ФАПЧ. Изменение параметров цепи ФАПЧ приводит к изменению частоты сигнала ГТЧ, при этом меняется разность фаз сигналов на входах ФД и напряжение Uy. Процесс продолжается до тех пор, пока частоты сигналов ГТЧ и ФТЧ не выравниваются, при этом Uy =0.

Рисунок 2.3. Структурная схема УТС

В регенераторах с внутренней синхронизацией синхросигнал может быть получен как из входной импульсной последовательности регенератора, так и из выходного сигнала регенератора. В первом случае регенератор носит название регенератора прямого действия (рисунок 2.4, а), во втором обратного действия (рисунок 2.4, б).

Рисунок 2.4. Варианты построения регенераторов однополярных цифровых сигналов.

В связи с тем, что устойчивость регенератора обратного действия ниже устойчивости регенератора прямого действия из-за наличия контура обратной связи, на практике чаще используют регенераторы прямого действия. Известны три способа использования сигналов тактовой синхронизации в процессе регенерации импульсов цифрового сигнала: перемножение регенерируемого сигнала с сигналом синхронизации с помощью схем логического умножения; сложение регенерируемого сигнала с сигналом синхронизации; перемножение сигналов с последующим сложением полученного результата с сигналом синхронизации или линейным сигналом. Наибольшее распространение получили регенераторы с РУ, осуществляющими перемножение регенерируемого сигнала с сигналом тактовой синхронизации. В таких регенераторах РУ осуществляет стробирование сигнала на его входе в моменты времени, определяемые УТС, в этом случае схема регистрации позволяет полностью восстановить временные интервалы между символами цифрового сигнала, так как они полностью определены моментами появления стробирующих импульсов на выходах УТС. Длительность стробирующего импульса обычно во много раз меньше длительности регистрируемого символа цифрового сигнала. В высокоскоростных ЦСП выработка стробирующих импульсов в регенераторах сильно затруднена, так как их длительность оказывается значительно меньше длительности очень коротких элементарных символов цифрового сигнала. В данном случае применяют регистрацию с частичным восстановлением временных соотношений цифрового сигнала. При этом в РУ осуществляется сложение входящего цифрового сигнала с сигналом тактовой частоты, вырабатываемым УТС. В дальнейшем из напряжения суммарного сигнала вычитается пороговое напряжение, что позволяет определить значение регенерируемого символа. В некоторых случаях возможно применение комбинации двух рассмотренных выше методов.

Рассмотренные выше структуры регенераторов предназначены для восстановления однополярных цифровых сигналов. Для восстановления формы двухполярных сигналов регенератором должно быть предусмотрено два канала регенерации – отдельно для положительных и отрицательных импульсов. Разделение импульсов в соответствии с полярностью наиболее просто реализуется с помощью дифференциальных трансформаторов.

Структурная схема линейного регенератора и временные диаграммы его работы представлены на рисунке 2.5. Ослабленный и искаженный в процессе прохождения по кабельной паре цифровой сигнал через симметрирующий трансформатор Tpi поступает на вход линейного корректора ЛК, в состав которого входят регулируемая искусственная линия РИЛ, корректирующий усилитель КУ, устройство автоматической регулировки уровня АРУ и устройство разделения импульсов по полярности УР.

Усилитель КУ корректирует форму импульсов цифрового сигнала при максимальном затухании предшествующего регенерационного участка таким образом, что на выходе усилителя импульсы имеют колоколообразную форму, амплитуду 2,4 В при ширине на уровне половины амплитуд, равной длительности тактового интервала. Затухание РИЛ устанавливается системой АРУ так, чтобы при изменении затухания кабельной цепи амплитуда импульсов на выходе ЛК сохранялась неизменной.

Скорректированный биполярный цифровой сигнал преобразуется устройством разделения на однополярные последовательности положительных и инвертированных отрицательных импульсов. Эти последовательности поступают на входы решающих устройств РУ1 и РУ2, где происходит опознавание кодовых символов. Восстановление импульсов по форме, длительности и временному положению происходит в формирователе выходных импульсов ФВИ. Регенерированные импульсы с ФВИ объединяются в симметрирующем трансформаторе Тр2 и поступают на вход следующего регенерационного участка. Управление работой РУ1 и РУ2

осуществляется двумя последовательностями прямоугольных импульсов,

обеспечивающих тактовую синхронизацию и восстановление временных интервалов.

а)

б)

Рис. 2.5. Структурная схема (а) и временные диаграммы работы (б) РЛ.

Временное положение фронта импульсов первой последовательности (в точке 1) определяет моменты опознавания кодовых символов и положение фронта регенерированных импульсов, срезом этих же импульсов формируется срез регенерированных импульсов. Импульсы второй последовательности (в точке 2), полученные за счет задержки по отношению к импульсам первой последовательности, запирают входы РУ, чем обеспечивается работа регенератора в режиме стробирования. Длительность стробирования равна интервалу времени между фронтом импульсов первой и срезом импульсов второй последовательности Дг.

Формирование синхросигналов осуществляется устройством тактовой синхронизации УТС, выполненным по классической схеме выделения тактовой частоты.

После выпрямления и ограничения снизу (в усилителе-ограничителе УО) импульсы поступают на контур ударного возбуждения К. С выхода контура квазигармонический сигнал с тактовой частотой через фазовращатель ФВ поступает на формирователь синхропоследовательностей ФСП, формирующий из квазигармонического сигнала последовательность прямоугольных импульсов с тем же периодом.

Параметры регенератора.

Основным параметром регенератора является коэффициент ошибок Кош, определяемый как отношение числа ошибочно регенерированных символов N/ош к общему числу символовN0:

Koш = NOщ/N0.

В каждой конкретной системе передачи для номинальной длины регенерационного участка задается минимально допустимое значение Кош.

В некоторых случаях в качестве основного параметра используется значение помехоустойчивости. Под помехоустойчивостью регенератора понимают то минимальное значение защищенности А з min, на входе регенератора, при которой обеспечивается заданный Кош. Помехоустойчивость оценивается с учетом ухудшающих работу регенератора факторов—неточности коррекции, нестабильности тактовой частоты, наличия зоны неопределенного решения РУ.

Для оценки качества коррекции импульсов УК регенератора и возможности достоверной регистрации импульса цифрового сигнала используются так называемые глаз-диаграммы.

Рисунок 2.6 Глаз-диаграмма идеального троичного сигнала.

Глаз-диаграмма— это график или картинка на экране осциллографа, состоящая из системы наложенных друг на друга всех возможных вариантов цифрового сигнала в интервале времени, равном двум тактовым интервалам.

На рисунке 2.6 представлен вариант глаз-диаграммы.Точка Р графически фиксирует опознавание импульса в центре тактового интервала на уровне,равном половине его амплитуды. Разность ДС/р между уровнями регистрируемого импульса и соседнего, создающего максимальную по величине межсимвольную помеху, называется раскрывом глаз-диаграммы. Чем больше раскрыв, тем больше допустимый уровень аддитивной помехи, при которой будет принято правильное решение. Следовательно, увеличение раскрыва снижает коэффициент ошибок регенератора, а его уменьшение приводит к росту Кош- Отметим, что раскрыв уменьшается при смещении момента регистрации от центра импульса (точка Р смещается влево или вправо).

Расчет длины регенерационного участка.

Существуют следующие типы станций для выпускаемой аппаратуры ЦСП: оконечные пункты (ОП), обслуживаемые регенерационные пункты (ОРП), необслуживаемые регенерационные пункты (НРП).

Расстояние между ОП – ОРП или ОРП – ОРП называется секцией дистанционного питания и задается в паспортных данных системы передачи. При размещении ОРП следует руководствоваться следующими соображениями:

-расстояние ОРП – ОРП не должно превышать максимальной длины секции дистанционного питания;

-ОРП может располагаться только в населенных пунктах.

Расстояние ОП – НРП, НРП – НРП или ОРП – НРП называется длиной регенерационного участка.

Номинальная длина регенерационного участка lнру для t°=20°C задается в технических данных аппаратуры.

Длина регенерационного участка при температуре грунта отличной от t=20°С может быть определена:

где Аном.РУ, Аmin.РУ, Аmin.РУ – номинальное, максимальное и минимальное затухание регенерационного участка по кабелю, согласно техническим данным системы.

α tmax – километрическое затухание кабеля на расчетной частоте fp цифровых систем передачи при максимальной температуре грунта по трассе линии.

Километрическое затухание кабеля при заданной максимальной температуре определяется:

(2.4)

где αt0 – километрическое затухание кабеля при температуре t0°= +20°, αα – температурный коэффициент затухания кабеля. Приводится в электрических характеристиках кабеля. ( чаще αα=4*10-3 1/град)

Расчет количества регенерационных участков внутри секции дистанционного питания можно осуществить по формуле:

(2.5)

где Lсек – длина секции дистанционного питания в км;

lном.РУ. – номинальная длина РУ в км;

Е(х) – функция целой части.

Укороченные или удлиненные участки не должны превышать длин lмин.РУ и lмакс.РУ определенных ранее. При невозможности выполнения этого условия допускается увеличить на один число НРП и организовать два укороченных регенерационных участка, при этом их следует располагать перед ОРП или ОП.

Ответы на вопрос “29.Преобразователи кодов. Мультиплексоры.”

~Мультиплексоры ~ ~Основные положения~ Назначение мультиплексоров (от англ. ~MULTIPLEX~ – многократный) -коммутировать в желаемом порядке информацию, поступающую с нескольких входных спин на одну выходную. С помощью мультиплексора осуществляется временное разделение информации, поступающей по разным каналам. Мультиплексор можно уподобить бесконтактному многопозиционному переключателю.

Мультиплексоры обладают двумя группами входов и одним, реже

двумя взаимодополняющими выходами. Одни входы информационные, а другие служат для управления. К ним относятся адресные и разрешающие (стробирующие) входы, Если мультиплексор имеет Ї адресных входом, то число информационных входов будет 2ї, Набор сигналов на адресных входах определяет конкретный информационный вход, который будет соединен с выходным выводом.

Разрешающий (стробирующий) вход управляет одновременно всеми

информационными входами независимо от состояния адресных входов. Запрещающий сигнал на этом входе блокирует действие всего устройства. Наличие разрешающего входа расширяет функциональные возможности мультиплексора, позволяя синхронизировать его работу с работой других узлов. Разрешающий вход употребляется также для наращивания разрядности мультиплексоров.

~7-2. схемотехннческие решения.~

На ~Рис. 7-1~ показаны принципиальные схемы двух простейших

мультиплексоров – селекторов вида “две линии к одной” (2 : 1). Вариант ‘с’ обеспечивает коммутацию информационных цепей с помощью механических устройств (переключателей, реле и т.п.) без вмешательства в управля- емые цепи. Переключатель S играет роль адресного устройства, положение контактов которого определяет, какие входные сигналы, X° или X•, будут поступать на выход добавлением логических элементов И можно увеличить число входных информационных шин.

R1 U• ----T---¬

-----T------- X¤------+ & ¦ 1 ¦

¦ ---- R2 A--T----------+ ¦ ¦F¤=AX¤°aX

¦ ¦ ----T---¬ ¦ +---+ +-------

¦-+-+ & ¦ 1 ¦ X--+----------+ & ¦ ¦

X¤—-+-+-+ ¦ ¦F=BaX°bAX ¦ —-¬ —+ ¦ ¦ ¦ ¦ +—+ +——– L-+ 1 ¦–a L—+—- б) ¦ ¦-+ & ¦ ¦ L—- —-T—¬ X—-+-+-+ ¦ ¦ a—-+ & ¦ 1 ¦ ¦ ¦ L—+—- X¤—-+ ¦ ¦F=aX¤°AX ¦ ¦B +—+ +——– ¦ L- + S а) A—-+ & ¦ ¦ L— ¦ X—-+ ¦ ¦ A L-¬ L—+—- с) -+- ~ Рис 7-1.~ Мультиплексор-селектор вида 2:1 а) управляемый контактами; б), с) управляемый сигналом.

В варианте 'б' для переключения входных цепей используется один

внешний сигнал. Когда а=1, F=X¤; при A=0 F=X•. Добавлением второго логического элемента И-ИЛИ (либо И-ИЛИ-НЕ, показан на ~Рис.7-1~ ‘б’) мо- жно получить распределитель сигналов, который часто применяется на практике, здесь при A=1 F¤=X¤, F=X; при A=0 F¤=X, F=X¤.

~Таблица 7-1.~ Эти же принципы положены в ——————T———–¬ основу построения и более сложных ¦ ¦ ¦ схем мультиплексоров. ~ Рис. 7-2~ +—–T—–T—–+ Выход F ¦ отражает логическую структуру ¦ V ¦ A ¦ B ¦ ¦ реального мультиплексора “четыре +—–+—–+—–+———–+ линии к одной” (4:1) – половину ¦ 0 ¦ 0 ¦ 0 ¦ D0 ¦ микросхемы ТТЛ К155КП2. Она содержит ¦ 0 ¦ 0 ¦ 1 ¦ D1 ¦ четыре информационных входа D0-D3, ¦ 0 ¦ 1 ¦ 0 ¦ D2 ¦ два адресных входа A и B и разреша- ¦ 0 ¦ 1 ¦ 1 ¦ D3 ¦ ющий вход V. Вход А принадлежит ¦ 1 ¦ X ¦ X ¦ 0 ¦ младшему разряду, В – старшему. Когда L—–+—–+—–+———— разрешающий вход находится под высоким потенциалом ‘1’ один из входов логических элементов И будет под низким и, следовательно, на их выходах также будут нулевые уровни независимо от состояния остальных входов. Выходной сигнал в этом случае также будет F=0.

Схема управления выполнена ----¬

так, что при разрешающем сигнале на A –T+ 1 ¦-¬ входе V любые комбинации сигналов на ¦L—- ¦ адресных входах, А и В создают ¦—-¬ ¦ условия, при которых на входах ( а B -T++ 1 ¦¬¦ значит, и на выходах) трех логических ¦¦L—-¦¦ —-¬ элементов И существуют потенциалы D0-++—–++–+ & +–¬ низкого уровня, неактивные для ¦¦ ¦+–+ ¦ ¦ элемента ИЛИ. Состояние четвертого ¦¦ ¦¦–+ ¦ ¦ элемента И определяется сигналом на ¦¦ ¦¦–+ ¦ ¦ информационном входе, тот же сигнал ¦¦ ¦¦¦ L—- ¦—-¬ будет и на выходе мультиплексора. ¦¦ ¦¦¦ —-¬ L+ 1 +–F Двоичные числа (00; 01; 10 и 11), D1-++—–+++-+ & +—+ ¦ характеризующие сигналы на входах В ¦¦ L++-+ ¦ –+ ¦ и А, эквивалентны индексу задейство- ¦¦——++-+ ¦ ¦-+ ¦ ванного информационного входа (D0; ¦¦ ¦¦-+ ¦ ¦¦L—- D1; D2; D3), Так, например, двоичное ¦¦ ¦¦ L—- ¦¦ число 10 на адресных входах обеспечит ¦¦ ¦¦ —-¬ ¦¦ селекцию шины D2. Это следует и из D2-++——++-+ & +–¦ таблицы истинности рассматриваемого ¦¦ L+-+ ¦ ¦ мультиплексора (~Табл. 7-1~), и из ¦+——-+-+ ¦ ¦ формулы ¦¦ ¦-+ ¦ ¦ ¦¦ ¦ L—- ¦ F=v(baD0°bAD1°AbD2°ABD3). ¦¦ ¦ —-¬ ¦ D3-++——-+-+ & +— В мультиплексорах ТТЛ входные ¦L——-+-+ ¦ информационные сигналы проходят через L——–+-+ ¦ несколько логических элементов. По- ¦-+ ¦ этому такие приборы могут обрабаты- —-¬ ¦ L—- вать только импульсные сигналы, логи- V—–+ 1 ¦– ческие уровни которых находятся в L—- пределах, допустимых для устройств ТТЛ ~Рис 7-2.~ Логическая структура мультиплексора вида 4:1 (1/2 К155КП2). ~7-3. Способы наращивания~ У мультиплексоров, выпускаемых в виде самостоятельных изделий число информационных входов не превышает шестнадцати. Большее число входов обеспечивается путем наращивания. Наращивание можно выполнять двумя способами: объединением нескольких мультиплексоров в пирамидальную (древовидную) систему либо последовательным соединением разрешающих входов и внешних логических элементов. На практике применяют оба метода.

Пирамидальные мультиплексоры строятся по ступенчатому

принципу, причем обычно применяются две, реже-три и более ступени, Пирамидальный характер схемы состоит в том, Что каждая ступень, начиная с первой, имеет больше входов, чем последующая. Младшие разряды кода адреса подаются на адресные входы первой ступени, а ступеням более высокого ранга соответствуют старшие разряды адресного кода. DD1 —-T—-¬ На ~Рис. 7-4~ показан вариант X—+X¤ ¦MUX ¦ мультиплексора 32:1 на основе —+X ¦ ¦ приборов 8:1 и 4:1. Чередование —+X ¦ ¦ сигналов в последовательности от —+X ¦ ¦Y 000 до 111 на адресных входах С, В, —+X ¦ F +-¬ А микросхем DD1-DD4 одновременно —+X¶ ¦ ¦ ¦ коммутирует входы X-X§ на шину —+X§ ¦ ¦ ¦ Y, входы X-X¤ на шину X§—+X ¦ ¦ ¦ Y¤;X¤¶-X на шину Y и X-X¤ на +—+ ¦ ¦ DD5 шину Y. Адресу СВA=100, например, -T—+ A ¦ ¦ ¦ —-T—-¬ соответствует поступление сигналов -+T–+ B ¦ ¦ L—-+X¤ ¦MUX ¦ с X на Y; X¤ на Y¤; с X на Y -++T-+ C ¦ ¦ Y¤—+X ¦ ¦ и с X на Y. ¦¦¦ L—+—– Y—+X ¦ F +- ¦¦¦—- . —–+X ¦ ¦ В свою очередь, мультипле- ¦¦+—- . ¦ +—+ ¦ ксирование шин Y-Y происходит при ¦++—- . ¦ D–+ A ¦ ¦ смене сигналов на адресных входах … ¦ E–+ B ¦ ¦ высших разрядов Е D (микросхема DD4 L-¬ L—+—– DD5) от 00 до 11. Если требуется, —-T—-¬ ¦ чтобы выход системы был связан со X—+X¤ ¦MUX ¦ ¦ входом X, то должно быть ED=10 —+X ¦ ¦ ¦ ( код шины Y ). Следовательно, —+X ¦ ¦ ¦ информационному входу X принадлежит —+X ¦ ¦Y¦ адрес EDCBA=10100. —+X ¦ F +— —+X¶ ¦ ¦ Общее число информационных —+X§ ¦ ¦ входов при однотипных мультипле- X¤—+X ¦ ¦ ксорах младшего ранга равно произведе- +—+ ¦ нию числа входов отдельных мультипле- L++–+ A ¦ ¦ ксоров и числа самих мультиплексоров: L+–+ B ¦ ¦ Nвх.общ = Nвх.х*Ї. Для очень больших L–+ C ¦ ¦ Nвх.общ понадобится третий ряд L—+—– мультиплексоров. Порядок их ~Рис 7-4.~ Пирамидальный мульти- подключения не требует пояснений. плексор 32:1. Общее число входов определяется по той же формуле.

Недостатками пирамидального наращивание следует считать

повышенный расход микросхем, а также сравнительно невысокое быстроде- йствие из-засуммирования задержек при последовательном прохождении сигналов по ступеням пирамиды.

По функциональным возможностям мультиплексоры являются очень

гибкими устройствами и помимо прямого назначения могут выполнять и другие функции.

Мультиплексоры, в частности, используются для преобразования

параллельного двоичного кода в последовательный, если управляющие сигналы на адресных входах мультиплексора. циклически менять в двоичной последовательности 00; 01; 10; 11 и т. д. (эта операция легко выполняется с помощью двоичного счетчика), то на выходе устройства будут появляться один за другим сигналы, существующие на информационных входах, в порядке номеров этих входов. Разрядность преобразуемого слова определяется числом информационных входов Если при этом время от времени чередовать сигналы на разрешающем входе, информация на выходе будет характеризоваться псевдослучайной последовательностью

~ 7-5. Мультиплексоры как универсальные

~ логические элементы

Еще одно интересное свойство мультиплексоров - работа в качес-

тве универсального логического “элемента, реализующего любую логическую функцию содержащую до Ї+1 переменной, где Ї – число адресных входов мультиплексора. Применение этого свойства особенно оправданно, когда число переменных достаточно велико, 4-5 и более. Один мультиплексор в этом случае может заменить несколько корпусов с логическими элементами вида И, ИЛИ, НЕ и пр. Синтез таких схем довольно прост и осуществляется на основе словесного описания функции или по таблице истинности.

Использование мультиплексора в качестве универсального логи-

ческого элемента основано на общем свойстве логических функций незави- симо от числа аргументов всегда равняться логической единице или нулю:

Если на адресные входы мультиплексора ----T---T---¬

подавать входные переменные, зная, какой ¦ X¤¦ X¦ Y ¦ выходной уровень должен отвечать каждому +—+—+—+ сочетанию этих сигналов, то, предварительно ¦ 0 ¦ 0 ¦ 0 ¦ установив на информационных входах потенциалы ¦ 0 ¦ 1 ¦ 1 ¦ нуля и единицы согласно программе, получим ¦ 1 ¦ 0 ¦ 1 ¦ устройство, реализующее требуемую функцию. На ¦ 1 ¦ 1 ¦ 0 ¦ простом примере функции “исключающее ИЛИ” L—+—+—- покажем, как с помощью мультиплексора 4:1, ~Таблица 5-21.~ описанного в начале главы (см. ~ Рис. 7-2~), можно реализовать любую двоичную функцию двух переменных.

Как следует из таблицы истинности для функции "исключающее ИЛИ"

(см~ Табл.5-21~),сочетаниям XX¤=00 и XX¤=11 отвечает значение логичес- кого 0, а двум другим XX¤=10 и XX¤ – логической 1. Для выполнения этих условий достаточно подключить к адресным входам мультиплексора А и В шины сигналов X¤ и X соответственно, на информационные входы D0 и D3 подать потенцнал логического 0, а на D1 и D2 -логической 1. Разре- шающий вход при этом должен быть в состоянии логического 0. Если число аргументов равно Ї+1, то мультиплексор следует включать несколько иначе. Допустим, что на основе того же мультиплексора (по ~Рис. 7-2~) требуется составить схему, реализующую функцию трех переменных, задан- ную ~Таблицей истинности 7-2~ .

—–T—-T—–T—–T————¬ ¦ X ¦ X¤ ¦ X ¦ F ¦ Примечание ¦ +—-+—-+—–+—–+TTTTTTTTTTTT+ —-T—–¬ ¦ ¦ ¦ …¦… ++++++++++++++ 0 –¦ V ¦ MUX ¦ ¦ 0 ¦ 0 ¦ .0 ¦ 1. ¦ ¦ 1 –+D0 ¦ ¦ ¦ 0 ¦ 0 ¦ .1 ¦ 1. ¦ F = 1 ¦ X–+D1 ¦ ¦ F ¦ ¦ ¦ …¦… +TTTTTTTTTTTT+ 0 –+D2 ¦ +— ¦ ¦ ¦ …¦… ++++++++++++++ x–+D3 ¦ ¦ ¦ 0 ¦ 1 ¦ .0 ¦ 0. ¦ ¦ +—+ ¦ ¦ 0 ¦ 1 ¦ .1 ¦ 1. ¦ F = X ¦ X¤–+ A ¦ ¦ ¦ ¦ ¦ …¦… +TTTTTTTTTTTT+ X–+ B ¦ ¦ ¦ ¦ ¦ …¦… ++++++++++++++ L—+—— ¦ 1 ¦ 0 ¦ .0 ¦ 0. ¦ ¦ ~Рис 7-5.~ Схемная реализация ¦ 1 ¦ 0 ¦ .1 ¦ 0. ¦ F = 0 ¦ функции, представленной ¦ ¦ ¦ …¦… +TTTTTTTTTTTT+ Табл 7-2. ¦ ¦ ¦ …¦… ++++++++++++++ ¦ 1 ¦ 1 ¦ .0 ¦ 1. ¦ ¦ ¦ 1 ¦ 1 ¦ .1 ¦ 0. ¦ F = x ¦ ¦ ¦ ¦ …¦… +TTTTTTTTTTTT+ L—-+—-+—–+—–+++++++++++++- ~Таблица 7-2.~

Расчленим мысленно таблицу истинности на группы по две строки в

каждой;в каждой группе X и X¤ неизменны, X(аргумент младшего разряда) имеет два состояния, а выходкой сигнал F может иметь одно из четырех значений: F=1; F=0; F=X и F=x. Если переменные сигналы X и X¤ под- ключить к адресным входам мультиплексора A и B, а на информационные входы D0 -D3 подать согласно таблице истинности постоянные потенциалы 1, 0 и переменные сигналы X, то такая схема (~Рис. 7-5~) будет удовле- творять заданным условиям.

Описанный метод проектирова-

ния годится также для составления ¦ ¦ ¦ ¦ —-T—–¬ схем и с большим числом переменных. –+–+–+–+-+D0 ¦ MUX ¦ На ~Рис 7-6~ показана матрица информа- –+–+–+–+-+D1 ¦ ¦ ционных и адресных шин при четырех –+–+–+–+-+D2 ¦ ¦ входных переменных. Конкретные точки –+–+–+–+-+D3 ¦ ¦F соединений шин определяются по задан- –+–+–+–+-+D4 ¦ +– ной таблице истинности. –+–+–+–+-+D5 ¦ ¦ –+–+–+–+-+D6 ¦ ¦ ~7-5. Мультиплексоры ТТЛ~ –+–+–+–+-+D7 ¦ ¦ +—+ ¦ Мультиплексоры ТТЛ, выполнен- —-+ A ¦ ¦ ные в виде самостоятельных микросхем, —-+ B ¦ ¦ строятся по образцу схемы, показанной —-+ C ¦ ¦ на ~Рис. 7-2~, и различаются главным L—+—— образом числом информационных и адрес- ных входов, наличием или отсутствием ~Рис 7-6.~ Матрица информационных разрешающего входа, а также характе- и адресных шин для четырех ром выходных сигналов (относительно переменных. входных информационных), которые могут быть прямыми, инверсными или парными.

---- / / ----

Пересчетные устройства и устройства измерения временных промежутков

Схемы совпадений

Функция схемы совпадений состоит в генерации на ее выходе сигнала, если время появления сигналов на ее входах меньше некоторого предварительно установленного времени , которое называется разрешающим временем схемы совпадения. Входов в схеме совпадений может быть 2 (двойная схема совпадений) и больше.

Рис. 1. Входные и выходные импульсы схемы “и”. |

Рассмотрим двойную схему совпадений так называемого перекрывающего типа. Такая схема совпадений практически то же самое, что схема “и” цифровой электроники. Схемы совпадения такого типа обычно используются в микросекундной области. Это так называемые медленные схемы совпадений (slow coincidence). На вход такой схемы поступают сформированные прямоугольные (медленные логические) импульсы. Иногда импульсы, поступающие на вход дополнительно регулируются (меняется их длительность). Эти импульсы поступают на схему “и”. Выходной импульс со схемы “и” формируется и поступает на выход. Импульсы на выходе возникают, если временное рассогласование между двумя импульсами меньше, чем t1 + t2, где t1 и t2 – длительности импульсов на входе “и”.

Рис. 2. Кривая самосовпадений – сплошная линия и кривая совпадений – штриховая линия. |

Если на оба входа схемы совпадений подать сигналы от одного источника и в один из каналов ввести задержку td, то интенсивность на выходе N в зависимости от задержки будет иметь П-образную форму (сплошная кривая на рис. 2). Это так называемая кривая самосовпадений (e = t1 + t2 – электрическое разрешающее время). Однако если подать на входы схемы совпадений сигналы от двух источников и проделать ту же операцию (снять кривую совпадений), картина может заметно измениться (штриховая кривая на рис. 2). Она может быть заметно асимметричной. Это связано с временными неопределенностями временных привязок в каналах. Чем они больше, тем кривая совпадений сильнее размывается. Часть событий (серые области на рис. 2) при измерениях с, так выбранным, разрешающим временем будут утеряны (эффективность системы регистрации <100%). Можно ввести понятие физического разрешающего времени

Различие между этими величинами характеризует временное “размытие” в каналах.

Для характеристики временных свойств систем часто используют другую

характеристику – полная ширина на половине высоты (FWHM) временного

распределения.

Для того чтобы эффективность схемы совпадения была 100%,

задержки в каналах должны быть одинаковыми. Кроме того, длительности входных

импульсов в каждом из каналов должны быть не меньше максимальной временной

неопределенности в данном канале. Если длительности входных импульсов слишком

велики, неоправданно увеличивается вклад случайных совпадений, частота которых

для двойной схемы совпадений определяется соотношением

| Nсл = 2N1N2e, | (2) |

где N1 и N2 – загрузки в каналах. Подбор оптимальных задержек и длительностей импульсов методом проб и ошибок утомительно, и экспериментаторы нередко избегают этого, устанавливая длительность входных импульсов на основании своих оценок временных неопределенностей в каналах. Между тем, задачу оптимизации разрешающего времени для двойной схемы совпадений можно существенно упростить, используя вместо схемы совпадений время-амплитудный конвертор с одноканальным анализатором.

Входов у схемы совпадений может быть больше двух. Часть из входов может быть задействовано на антисовпадения. Кроме рассмотренной выше схемы совпадений перекрывающего типа, в быстрых схемах совпадений используют более сложные схемы формирования сигналов.

Произошла ошибка при настройке пользовательского файла cookie

Этот сайт использует файлы cookie для повышения производительности. Если ваш браузер не принимает файлы cookie, вы не можете просматривать этот сайт.

Настройка вашего браузера для приема файлов cookie

Существует множество причин, по которым cookie не может быть установлен правильно. Ниже приведены наиболее частые причины:

- В вашем браузере отключены файлы cookie. Вам необходимо сбросить настройки своего браузера, чтобы он принимал файлы cookie, или чтобы спросить вас, хотите ли вы принимать файлы cookie.

- Ваш браузер спрашивает вас, хотите ли вы принимать файлы cookie, и вы отказались. Чтобы принять файлы cookie с этого сайта, используйте кнопку «Назад» и примите файлы cookie.

- Ваш браузер не поддерживает файлы cookie. Если вы подозреваете это, попробуйте другой браузер.

- Дата на вашем компьютере в прошлом. Если часы вашего компьютера показывают дату до 1 января 1970 г., браузер автоматически забудет файл cookie. Чтобы исправить это, установите правильное время и дату на своем компьютере.

- Вы установили приложение, которое отслеживает или блокирует установку файлов cookie. Вы должны отключить приложение при входе в систему или проконсультироваться с системным администратором.

Почему этому сайту требуются файлы cookie?

Этот сайт использует файлы cookie для повышения производительности, запоминая, что вы вошли в систему, когда переходите со страницы на страницу. Чтобы предоставить доступ без файлов cookie потребует, чтобы сайт создавал новый сеанс для каждой посещаемой страницы, что замедляет работу системы до неприемлемого уровня.

Что сохраняется в файле cookie?

Этот сайт не хранит ничего, кроме автоматически сгенерированного идентификатора сеанса в cookie; никакая другая информация не фиксируется.

Как правило, в файлах cookie может храниться только информация, которую вы предоставляете, или выбор, который вы делаете при посещении веб-сайта. Например, сайт не может определить ваше имя электронной почты, пока вы не введете его. Разрешение веб-сайту создавать файлы cookie не дает этому или любому другому сайту доступа к остальной части вашего компьютера, и только сайт, который создал файл cookie, может его прочитать.

AND / OR / NAND / NOR Gate

| Библиотека: | Gates | ||||||||||||

| Введено: | 2.0 Бета 1 | ||||||||||||

| Внешний вид: |

| ||||||||||||

Поведение

Каждый логический элемент AND, OR, NAND и NOT вычисляет соответствующий функция входов и вывести результат на выходе.

По умолчанию любые неподключенные входы игнорируются.

– это если к входу действительно ничего не прикреплено,

даже не провод.

Таким образом, вы можете вставить вентиль с 5 входами, но присоединить только два входа,

и он будет работать как вентиль с 2 входами;

это избавляет вас от необходимости беспокоиться о настройке

количество входов каждый раз, когда вы создаете ворота.

(Если все входы не подключены, на выходе будет значение ошибки X .)

Однако некоторые пользователи предпочитают, чтобы Logisim настаивал на подключении всех входов.

поскольку это то, что соответствует реальным воротам.Вы можете включить это поведение, перейдя в пункт меню Проект> Параметры…,

выбрав вкладку Simulation, и

выбор Ошибка для неопределенных входов

для Выходной сигнал, если не определен.

Таблица истинности с двумя входами для ворот следующая. (Буква X представляет значение ошибки, а буква Z представляет плавающее значение.)

Короче говоря, эти компоненты работают должным образом, пока все входы равны 0 или 1.Если вход не равен ни 0, ни 1 (он плавающий или это значение ошибки) тогда компонент рассматривает его как 0 и 1: Если бы результат был одинаковым в обоих направлениях (например, когда логический элемент И имеет один вход, который определенно равен 0 и сомнительный второй вход), это будет выходное значение; но если результат меняется в зависимости от того, 0 или 1, вывод – это значение ошибки.

Многобитовые версии каждого логического элемента будут выполнять свои однобитовые побитовое преобразование на его входах.

Штифты (при условии, что компонент направлен на восток)

- Западный край (входы, разрядность в соответствии с атрибутом Data Bits)

Входы в компонент. Их будет столько, сколько указывается в атрибуте Number of Inputs.

Обратите внимание, что если вы используете фасонные ворота, западная сторона OR и NOR ворота будут изогнутыми. Тем не менее, входные контакты выстроены в линию. Logisim нарисую короткие отрезки, иллюстрирующие это; и если вы промахнетесь мимо заглушки, она будет молча предположить, что вы не хотели его промахнуть.В “принтере” view “, эти заглушки не будут отображаться, если они не подключены к провода.

- Восточный край (вывод, разрядность в соответствии с атрибутом Data Bits)

Выход ворот, значение которого вычисляется на основе текущего входы, как описано выше.

Атрибуты

Когда компонент выбран или добавлен,

цифры от ‘0’ до ‘9’ изменяют его атрибут Number of Inputs

,

Alt-0 – Alt-9 изменяет его атрибут Data Bits

,

а клавиши со стрелками изменяют его атрибут Facing

.

- Облицовка

- Направление компонента (его выход относительно его входов).

- Биты данных

- Разрядность входов и выходов компонента.

- Размер ворот

- Определяет, рисовать ли более широкую или более узкую версию

составная часть. Это не влияет на количество входов, которое указано.

по атрибуту Number of Inputs. Однако, если выбраны фасонные ворота,

тогда ворота будут нарисованы с

крыльями

для размещения дополнительных входов за пределами того, что форма естественным образом приспосабливает. - Количество входов

- Определяет, сколько контактов должно быть для компонента на его западе. боковая сторона.

- Выходное значение

- Указывает, как ложные и истинные результаты должны переводиться в выходные значения.

По умолчанию ложь обозначается низким напряжением (0), а истина – высоким напряжением (1),

но одно или другое можно заменить на значение с высоким сопротивлением (

, плавающее,

). вместо. Это позволяет проводить проводные или проводные соединения, как показано ниже: Слева атрибут выходного значения буферов имеет плавающее значение / 1, а резистор стремится к 0, придание проводного поведения; справа атрибут выходного значения буферов равен 0 / плавающий, а резистор тянет до 1, давая проводные и поведенческие. - Этикетка

- Текст внутри метки, связанной с воротами.

- Шрифт этикетки

- Шрифт для визуализации метки.

- Отрицательный x

- Если

да

, вход инвертируется перед подачей в ворота. Входы подсчитываются сверху вниз, если ориентация обращена на восток или запад, и они считаются слева направо, если ориентация обращена на север или юг.

Поведение Poke Tool

Нет.

Поведение текстового инструмента

Позволяет редактировать метку, связанную с воротами.

Вернуться к Ссылка на библиотеку

Логический вентиль– обзор

VIII.B Массивы вентилей

Массив вентилей – это логические вентили, которые предварительно размещены в матричной форме на кристалле, как показано на рис. 20. Фактически, несвязанные компоненты логических вентилей, которые называемые ячейки (эти ячейки следует отличать от ячеек в библиотеке ячеек, которая будет описана позже), предварительно заложены вместо логических вентилей.Соединив компоненты в ячейке соответствующим образом, мы можем реализовать один из нескольких различных типов логических вентилей. Ячейка матрицы затвора КМОП, в качестве примера, показана на рис. 21, где пара полевых МОП-транзисторов и пара полевых МОП-транзисторов расположены слева и справа, соответственно, без соединений между ними. Логический элемент И-НЕ, показанный на фиг. 22a, может быть реализован путем соединения компонентов, показанных на фиг. 21, двумя металлическими слоями, как показано на фиг. 22b. Эти два металлических слоя формируются путем формирования первого металлического слоя, показанного на рис.22c, изоляционный слой (не показан), а затем второй металлический слой, показанный на (d).

РИСУНОК 20. Матрица ворот.

РИСУНОК 21. Ячейка вентильной матрицы CMOS (любезно предоставлена Fujitsu Ltd.).

РИСУНОК 22. Пример схемы подключения ячейки на рис. 21 (любезно предоставлено Fujitsu Ltd.)

После того, как разработчики завершат логический дизайн, логические сети реализуются путем соответствующего соединения компонентов в ячейке для формирования логических вентилей. а затем соответствующим образом подключив логические вентили.Таким образом, была получена схема всей микросхемы. В этом случае проектирование электронной схемы и компоновка, которые требуются при полностью индивидуальном проектировании, по существу пропускаются.

Матрицы ворот имеют следующие преимущества. Скорость улучшена по сравнению с PLA. Только 2 или 3 маски для соединений и контактных окон должны быть изготовлены на заказ вместо всех двух десятков масок, необходимых для полностью индивидуального дизайна. Кроме того, с помощью САПР необходимо эффективно выполнять только компоновку соединений и распределение ворот, что значительно сокращает время компоновки.Таким образом, конструкция с вентильными матрицами является очень недорогой и быстрой по сравнению с полностью индивидуализированной конструкцией. Широко используются вентильные матрицы CMOS. Когда новая технология обработки должна быть внедрена в матрицу вентилей, нам необходимо обновить компоновку несвязанных компонентов только одной ячейки, что позволит нам быстро и недорого внедрить новую технологию.

С другой стороны, вентильные матрицы имеют следующие недостатки, такие как большой размер микросхемы, много неиспользуемых ячеек (ограниченных доступным количеством контактных площадок) и неравномерные задержки на вентилях.Микросхема больше, чем микросхема, разработанная с помощью подхода к проектированию библиотеки ячеек, который будет описан ниже, потому что каждый логический вентиль не обязательно является самым компактным, и все логические вентили не расположены компактно. Поскольку готовые компоненты одинакового размера используются во всех ячейках, каждая электронная схема в ячейке не настроена на потребности каждого конкретного логического элемента. Например, даже если затвор имеет длинное выходное соединение, размер схемы транзистора не может быть увеличен для увеличения задержки смещения.Таким образом, скорость приносится в жертву, а логические элементы на разных сайтах имеют разные задержки. Кроме того, программа САПР может не обеспечивать хорошую маршрутизацию, несмотря на важность маршрутизации с помощью САПР для сокращения времени и затрат на проектирование. Когда межсетевые соединения между воротами перегружены в некоторых областях, новые межсоединения необходимо обходить, используя длинные межсоединения и, таким образом, увеличивая задержку.

В отличие от программируемых пользователем вентильных матриц, которые будут описаны ниже, вентильные матрицы здесь называются вентильными матрицами, программируемыми по маске.

Digital Logic – learn.sparkfun.com

Добавлено в избранное Любимый 32Комбинационная логика

Комбинационные схемы состоят из пяти основных логических элементов:

- И вентиль – выход равен 1, если ОБЕИХ входов 1

- вентиль ИЛИ – выход равен 1, если по крайней мере один вход равен 1

- вентиль XOR – выход равен 1, если ТОЛЬКО один вход равен 1

- вентиль И-НЕ – выход равен 1, если по крайней мере один вход 0

- вентиль ИЛИ-НЕ – выход равен 1, если ОБЕИХ входов 0

В цифровой логике есть шестой элемент, инвертор (иногда называемый вентилем НЕ).Инверторы на самом деле не ворота, поскольку они не принимают никаких решений. Выход инвертора равен 1, если вход равен 0, и наоборот.

Несколько замечаний по поводу изображения выше:

- Обычно название ворот – , а не ; Предполагается, что символа достаточно для идентификации.

- Обозначение клемм типа A-B-Q является стандартным, хотя в логических схемах они обычно не используются для сигналов, которые не являются входами или выходами для системы в целом.

- Два устройства ввода являются стандартными, но иногда вы можете встретить устройства с более чем двумя входами. Однако у них будет только один выход.

Цифровые логические схемы обычно представлены с использованием этих шести символов; входы слева, а выходы справа. Хотя входы могут быть соединены вместе, выходы никогда не должны соединяться друг с другом, только с другими входами. Однако один выход может быть подключен к нескольким входам.

Таблицы истинности

Описания выше подходят для описания функциональности отдельных блоков, но есть более полезный инструмент: таблица истинности.Таблицы истинности – это простые графики, которые объясняют выход схемы с точки зрения возможных входов для этой схемы. Вот таблицы истинности, описывающие шесть основных элементов:

Таблицы истинности могут быть расширены до произвольного масштаба, с таким количеством входов и выходов, с которым вы можете справиться, прежде чем ваш мозг растает. Вот как выглядит схема с четырьмя входами и таблица истинности:

Записанная логическая логика

Конечно, полезно иметь возможность записать в простом математическом формате уравнение, представляющее логическую операцию.Для этого существуют математические символы для уникальных операций: И, ИЛИ, XOR и NOT.

- A AND B следует записывать как AB (или иногда A • B)

- A OR B следует записать как A + B

- A XOR B следует записать как A ⊕ B

- НЕ А следует писать как А ‘или А

Вы заметите, что в этом списке отсутствуют два элемента: NAND и NOR. Обычно они просто дополняются соответствующим представлением:

- NAND B записывается как (AB) ‘, (A • B)’ или (AB)

- A NOR B записывается как (A + B) ‘или (A + B)

← Предыдущая страница

Введение Имитатор логических вентилей

| Academo.org

Простой бесплатный онлайн-симулятор логических вентилей. Изучите поведение логических элементов AND, OR, NOT, NAND, NOR и XOR. Выберите ворота из раскрывающегося списка и нажмите «Добавить узел», чтобы добавить дополнительные ворота. Перетащите полые круги к сплошным кругам, чтобы установить соединения. Щелкните соединения правой кнопкой мыши, чтобы удалить их. См. Ниже более подробные инструкции.

Инженерное дело Электроника логика

Приведенная выше демонстрация позволяет вам создавать последовательности логических вентилей, чтобы увидеть, как они ведут себя при подключении к различным входам и выходам.Изначально, вам предоставляется простой вход включения / выключения и выход. Чтобы соединить их, щелкните и перетащите из полого круга в правой части переключатель включения / выключения и отпустите кнопку мыши, когда вы окажетесь над сплошным кружком в левой части блока «вывода».