Транзистор МП39 — DataSheet

Перейти к содержимому

Цоколевка транзисторов МП38, МП39, МП40

| Параметр | Обозначение | Маркировка | Условия | Значение | Ед. изм. |

| Аналог | МП39 | SFT306 | |||

| МП39Б | АС540 | ||||

| Структура | — | — | p-n-p | мВт | |

| Максимально допустимая постоянная рассеиваемая мощность коллектора | PK max,P*K, τ max,P** | МП39 | — | 150 | |

| МП39Б | — | 150 | |||

| Граничная частота коэффициента передачи тока транзистора для схемы с общим эмиттером | fгр, f*h31б, f**h31э, f***max | МП39 | — | ≥0. 5* 5* | МГц |

| МП39Б | — | ≥0.5* | |||

| Пробивное напряжение коллектор-база при заданном обратном токе коллектора и разомкнутой цепи эмиттера | UКБО проб., U*КЭR проб., U**КЭО проб. | МП39 | 10к | 15* | В |

| МП39Б | 10к | 15* | |||

| Пробивное напряжение эмиттер-база при заданном обратном токе эмиттера и разомкнутой цепи коллектора | UЭБО проб., | МП39 | — | 5 | В |

| МП39Б | — | 5 | |||

| Максимально допустимый постоянный ток коллектора | IK max, I*К , и max | МП39 | — | 20(150*) | мА |

| МП39Б | — | 20(150*) | |||

| Обратный ток коллектора — ток через коллекторный переход при заданном обратном напряжении коллектор-база и разомкнутом выводе эмиттера | IКБО, I*КЭR, I**КЭO | МП39 | 5 В | ≤15 | мкА |

| МП39Б | ≤15 | ||||

| Статический коэффициент передачи тока транзистора в режиме малого сигнала для схем с общим эмиттером | h21э, h*21Э | МП39 | 5 В; 1 мА | ≥12 | |

| МП39Б | 5 В; 1 мА | 20…60 | |||

| Емкость коллекторного перехода | cк, с*12э | МП39 | — | ≤50 | пФ |

| МП39Б | — | ≤50 | |||

| Сопротивление насыщения между коллектором и эмиттером | rКЭ нас, r*БЭ нас | МП39 | — | — | Ом |

| МП39Б | — | — | |||

| Коэффициент шума транзистора | Кш, r*b, Pвых | МП39 | — | — | Дб, Ом, Вт |

| МП39Б | 1 кГц | ≤12 | |||

| Постоянная времени цепи обратной связи на высокой частоте | τк, t*рас, t**выкл, t***пк(нс) | МП39 | — | — | пс |

| МП39Б | — | — |

Описание значений со звездочками(*,**,***) смотрите в таблице параметров биполярных транзисторов.

Если вы нашли ошибку, пожалуйста, выделите фрагмент текста и нажмите Ctrl+Enter.

МП39, МП39Б, МП40, МП40А, МП41, МП41А

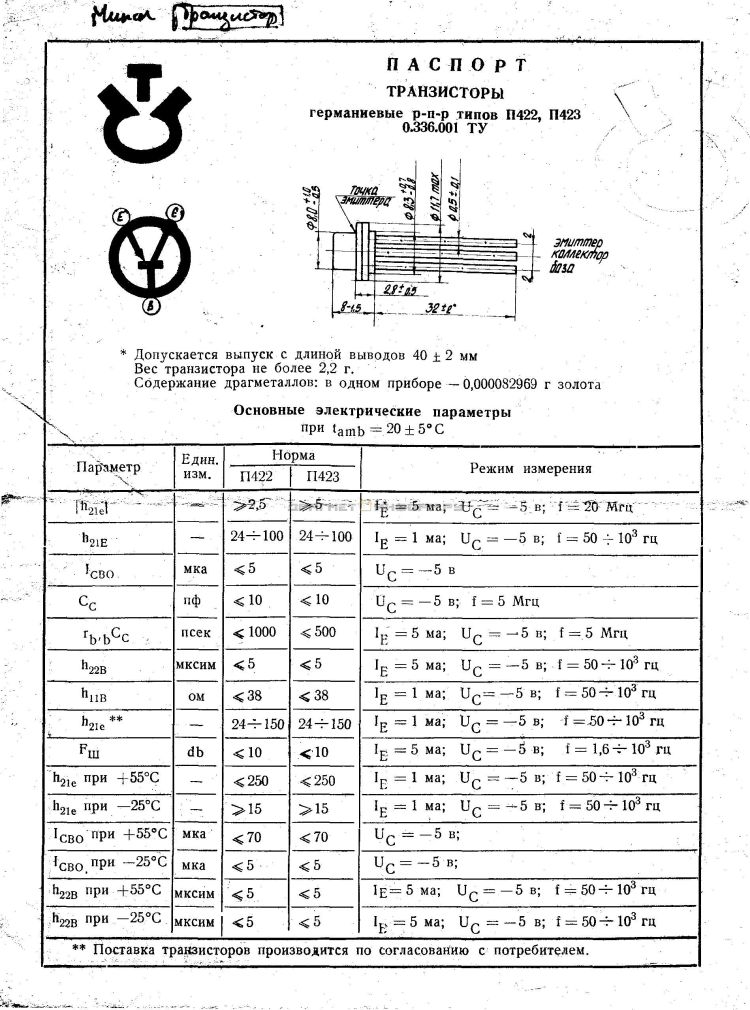

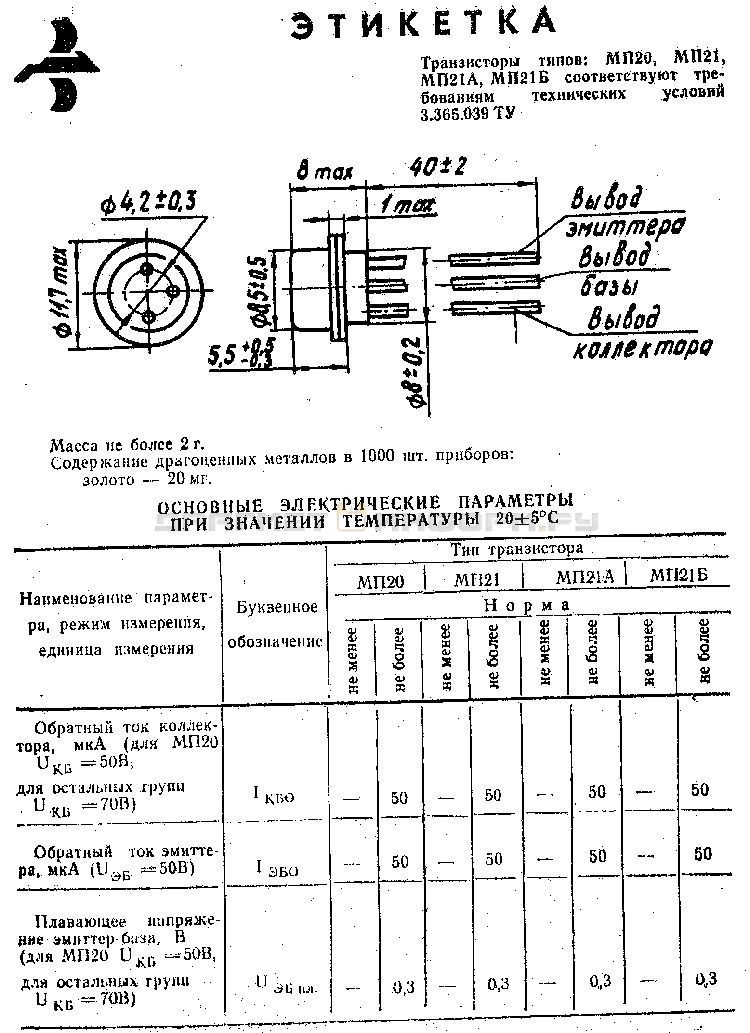

Транзисторы МП39, МП39Б, МП40, МП40А, МП41, МП41А германиевые сплавные p-n-p усилительные низкочастотные с ненормированным (МП39, МП40, МП40А, МП41, МП41А и нормированным (МП39Б) коэффициентом шума на частоте 1 кГц. Предназначены для усиления сигналов низкой частоты. Выпускаются в металлостеклянном корпусе с гибкими выводами. Масса транзистора не более 2 гр. Чертёж транзистора МП39, МП39Б, МП40, МП40А, МП41, МП41А Электрические параметры.

Предельные эксплуатационные данные МП39, МП39Б, МП40, МП40А, МП41, МП41А.

| |||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

Mouser Electronics – Скоро вернусь.

..

..- 本网站暂时不可用。如需即时帮助,请联系您当地的分支机构。

- 本網站暫時無法使用,請與當地分公司聯絡尋求即時支援。

- Tato stránka je dočasně nedostupná. Pro okamžitou pomoc se prosím obraťte na svou místní pobočku.

- Le site est temporairement indisponible. Свяжитесь с местным агентством Veuillez для оказания немедленной помощи.

- Die Seite ist momentan nicht verfügbar. Bitte wenden Sie sich für sofortige Unterstützung an Ihre Regionale Niederlassung.

- Momentaneamente il site non è disponibile. Contatta la sede locale для немедленного получения помощи.

- El site estátempormente не подлежит оплате. Póngase en contacto con la officina local para recibir ayuda inmediata.

- Este sitio estátempormente fuera de servicio. Póngase en contacto con su concesionario local para recibir asistencia inmediata.

| Область | Телефон | Факс | Электронная почта |

|---|---|---|---|

| Америка | |||

| США (всемирная штаб-квартира) | 1 (800) 346-6873 | 1 (817) 804-3888 | sales@mouser. com com |

| Мексика | +52 33 3612 7301 | +52 33 3612 7356 | мексиканские продажи@mouser.com |

| Азия/Тихий океан | |||

| Гонконг, Китай | +852 3756-4700 | +852 3756-4701 | Гонконг@mouser.com |

| Шанхай, Китай | +86 (21) 6360-6111 | +86 (21) 6360-0189 | шанхай@mouser. com com |

| Сингапур | +65 6788-9233 | +65 6542-6916 | сингапур@mouser.com |

| Индия | +91 80 41148091/92 | +91 80 41148093 | Индия@mouser.com |

| Тайвань | +886 (02) 2799-2096 | +886 (02) 2799-2095 | Тайвань@mouser. com com |

| Таиланд | +66 2694 2310 | +66 2694 2276 | таиланд@mouser.com |

| Европа | |||

| Германия (Европейская штаб-квартира) | +49 (0) 8952 04621 10 | +49 (0) 8952 04621 20 | [email protected] |

| Великобритания | +44 (0) 1494-467490 | +44 (0) 1494-467499 | uk@mouser. com com |

| Чешская Республика | +420 517070880 | +420 517070881 | [email protected] |

| Франция | +33 5 55 85 79 96 | +33 5 55 85 79 97 | [email protected] |

| Израиль | +972 9 7783020 | +972 9 7458885 | israelsales@mouser. com com |

| Италия | +39 02 575 065 71 | +39 02 575 164 78 | Италия@mouser.com |

| Испания | +34 936455263 | +34 936455264 | испания@mouser.com |

| Нидерланды | +31 402 6476 57 | +31 402 6476 58 | Нидерланды@mouser. com com |

| Швеция | +46 8 590 88 715 | +46 8 590 88 746 | Швеция@mouser.com |

Патент США на схему опорного напряжения. Патент (Патент № 7,301,321, выдан 27 ноября 2007 г.)

ПРЕДПОСЫЛКИ ИЗОБРЕТЕНИЯ

Более конкретно, настоящее изобретение относится к схеме опорного напряжения КМОП-транзистора.

2. Описание предшествующего уровня техники

РИС. 1 представляет собой кривую соответствующих параметров технологии производства полупроводников. Напряжение питания уменьшается из-за уменьшения толщины оксида. Пороговое напряжение (В TH ) МОП-транзистора, однако, масштабируется не так сильно, как напряжение питания (V DD ). Следовательно, в случае, когда запас по напряжению ограничен, все аналоговые схемы сталкиваются с проблемой сохранения присущих им характеристик при низком рабочем напряжении V DD .

РИС. 2 представляет собой принципиальную схему традиционной цепи опорного напряжения. Транзисторы PMOS MP 21 и MP 22 со смещением в подпороговой области используются для успешного получения большего запаса напряжения, так что схема может работать при более низком рабочем напряжении V ДД . Обычная схема опорного напряжения включает токовое зеркало с PMOS-транзисторами MP 24 ˜MP 26 , PMOS-транзисторами MP 21 ˜MP 23 , операционный усилитель 202 и резисторы R 2 1 2 R2 2 22 . Для удобства иллюстрации указаны узловые напряжения V 21 и V 22 . Затем принцип работы и недостатки традиционной схемы опорного напряжения проиллюстрированы со ссылкой на фиг. 2.

Как видно из узловых напряжений V 21 и V 22 на фиг. 2, с использованием механизма обратной связи, образованного операционным усилителем 201 и транзисторами PMOS MP 24 , MP 25 , узловое напряжение V 21 равно узловому напряжению V 22 . Следовательно, при простом анализе схемы ток I 21 , протекающий через резистор R 21 , выводится следующим образом.

Следовательно, при простом анализе схемы ток I 21 , протекающий через резистор R 21 , выводится следующим образом.

я 21 = ( В SG21 -V SG22 )/ R 21 (1)

arein, 21. 21023232323232323232323232323232323232323232323232323232323232323232323232323232323232323232323232323232323232323232323232323232323232323232323231. тока зеркала, а выходное опорное напряжение V BG получают следующим образом.

V BG = V SG23 +R 22 /R 21 *( /R 21 *( /R 21 *( /R 21 .0285 SG22 ) (2)

Поскольку транзисторы PMOS МП 21 , МП 22 смещены в подпороговой области в соотношении площадей 1 : K, используя тот факт, что токовые характеристики транзисторов PMOS, поэтому их можно анализировать как анализ биполярных транзисторов, опорное напряжение V BG далее выражается как

VBG=VSG23+R22R21·n·VT·ln(K)(3)

, где n – параметр процесса, и V T – тепловое напряжение. Как видно из формулы (3), обычная схема опорного напряжения формирует независимое от температуры опорное напряжение V BG с использованием комбинации напряжения с отрицательным температурным коэффициентом V SG23 и напряжения с положительным температурным коэффициентом V T .

Как видно из формулы (3), обычная схема опорного напряжения формирует независимое от температуры опорное напряжение V BG с использованием комбинации напряжения с отрицательным температурным коэффициентом V SG23 и напряжения с положительным температурным коэффициентом V T .

Наряду с изменениями в архитектуре схемы, для обеспечения возможности работы PMOS-транзисторов МП 21 , МП 22 в подпороговой области, резистор R 21 , используемый в традиционной схеме опорного напряжения, имеет большее значение сопротивления, а токовые зеркала М 24 ˜M 26 может работать в подпороговой области. Кроме того, обычная схема опорного напряжения выдает опорное напряжение V BG , где напряжение V SG23 с отрицательным температурным коэффициентом связано с отрицательным температурным коэффициентом. Так как температурный коэффициент тока, протекающего через PMOS-транзистор МП 23 , пропорционален абсолютной температуре, то дополнительно два входных напряжения (т. е. узловые напряжения В 21 , V 22 ) операционного усилителя 201 очень малы, поэтому операционный усилитель 201 не может работать в области низкого усиления. В настоящем изобретении используются резисторы R 31 и R 32 на ФИГ. 3, чтобы увеличить входное синфазное напряжение операционного усилителя, что позволит операционному усилителю 311 работать в области более высокого усиления.

е. узловые напряжения В 21 , V 22 ) операционного усилителя 201 очень малы, поэтому операционный усилитель 201 не может работать в области низкого усиления. В настоящем изобретении используются резисторы R 31 и R 32 на ФИГ. 3, чтобы увеличить входное синфазное напряжение операционного усилителя, что позволит операционному усилителю 311 работать в области более высокого усиления.

СУЩНОСТЬ ИЗОБРЕТЕНИЯ

Соответственно, целью настоящего изобретения является создание схемы опорного напряжения, которая обеспечивает стабильное опорное напряжение с малой температурной зависимостью при работе при низком рабочем напряжении.

Для достижения вышеуказанных и других целей настоящее изобретение предлагает схему опорного напряжения. Генератор тока с положительным температурным коэффициентом используется для генерации тока с положительным температурным коэффициентом. Генератор тока с отрицательным температурным коэффициентом используется для генерации тока с отрицательным температурным коэффициентом. Ток с положительным температурным коэффициентом и ток с отрицательным температурным коэффициентом протекают через первый резистор для генерирования независимого от температуры тока, так что стабильное опорное напряжение выводится из первого резистора. Генератор тока с положительным температурным коэффициентом включает в себя второй резистор, первый PMOS-транзистор, второй PMOS-транзистор, токовое зеркало с положительным температурным коэффициентом, первый операционный усилитель, третий резистор, четвертый резистор, пятый резистор и шестой резистор. Первый PMOS-транзистор и второй PMOS-транзистор смещены в области слабой инверсии, и, таким образом, второй резистор, включенный последовательно между затворами двух транзисторов, генерирует ток с положительным температурным коэффициентом, используя токовую характеристику первого и второго PMOS-транзисторов.

Генератор тока с отрицательным температурным коэффициентом используется для генерации тока с отрицательным температурным коэффициентом. Ток с положительным температурным коэффициентом и ток с отрицательным температурным коэффициентом протекают через первый резистор для генерирования независимого от температуры тока, так что стабильное опорное напряжение выводится из первого резистора. Генератор тока с положительным температурным коэффициентом включает в себя второй резистор, первый PMOS-транзистор, второй PMOS-транзистор, токовое зеркало с положительным температурным коэффициентом, первый операционный усилитель, третий резистор, четвертый резистор, пятый резистор и шестой резистор. Первый PMOS-транзистор и второй PMOS-транзистор смещены в области слабой инверсии, и, таким образом, второй резистор, включенный последовательно между затворами двух транзисторов, генерирует ток с положительным температурным коэффициентом, используя токовую характеристику первого и второго PMOS-транзисторов. аналогичен транзистору с биполярным переходом. Токовое зеркало с положительным температурным коэффициентом использует механизм отрицательной обратной связи, образованный первым операционным усилителем, для создания тока смещения, необходимого для первого PMOS-транзистора и второго PMOS-транзистора. А третий резистор и четвертый резистор обеспечивают другой путь тока к земле, чтобы гарантировать, что токовое зеркало с положительным температурным коэффициентом сохраняется в области сильной инверсии. Два входных напряжения первого операционного усилителя поднимаются до синфазного входного диапазона первого операционного усилителя за счет падения напряжения на пятом резисторе и шестом резисторе.

аналогичен транзистору с биполярным переходом. Токовое зеркало с положительным температурным коэффициентом использует механизм отрицательной обратной связи, образованный первым операционным усилителем, для создания тока смещения, необходимого для первого PMOS-транзистора и второго PMOS-транзистора. А третий резистор и четвертый резистор обеспечивают другой путь тока к земле, чтобы гарантировать, что токовое зеркало с положительным температурным коэффициентом сохраняется в области сильной инверсии. Два входных напряжения первого операционного усилителя поднимаются до синфазного входного диапазона первого операционного усилителя за счет падения напряжения на пятом резисторе и шестом резисторе.

Генератор тока с отрицательным температурным коэффициентом включает в себя токовое зеркало с отрицательным температурным коэффициентом, второй операционный усилитель, седьмой резистор, третий PMOS-транзистор и независимый от температуры источник тока. Независимый от температуры источник тока подает ток смещения на третий PMOS-транзистор, так что напряжение затвор-исток третьего PMOS-транзистора представляет собой напряжение, связанное только с отрицательным температурным коэффициентом. Ток с отрицательным температурным коэффициентом генерируется в ответ на падение напряжения с отрицательным температурным коэффициентом (напряжение затвор-исток третьего PMOS-транзистора) на седьмом резисторе из-за свойства виртуального короткого замыкания на двух входах второго операционного усилителя.

Ток с отрицательным температурным коэффициентом генерируется в ответ на падение напряжения с отрицательным температурным коэффициентом (напряжение затвор-исток третьего PMOS-транзистора) на седьмом резисторе из-за свойства виртуального короткого замыкания на двух входах второго операционного усилителя.

Таким образом, в схеме опорного напряжения по настоящему изобретению ток с положительным температурным коэффициентом и ток с отрицательным температурным коэффициентом объединяются для формирования тока с низкой температурной зависимостью. Ток с малой температурной зависимостью протекает через первый резистор, создавая стабильное опорное напряжение. По сравнению с традиционной архитектурой, за счет изменения способа связи второго резистора генератор тока с положительным температурным коэффициентом заставляет схему работать при низком напряжении, а также экономится стоимость площади компоновки схемы.

Чтобы сделать вышеупомянутые и другие цели, особенности и преимущества настоящего изобретения более понятными, предпочтительные варианты осуществления, сопровождаемые чертежами, подробно описаны ниже.

Следует понимать, что как предшествующее общее описание, так и последующее подробное описание являются иллюстративными и предназначены для дальнейшего пояснения заявленного изобретения.

КРАТКОЕ ОПИСАНИЕ ЧЕРТЕЖЕЙРИС. 1 представляет собой кривую соответствующих параметров технологии производства полупроводников.

РИС. 2 представляет собой принципиальную схему традиционной цепи опорного напряжения.

РИС. 3 представляет собой принципиальную схему схемы опорного напряжения согласно варианту осуществления настоящего изобретения.

РИС. 4-РИС. 8 являются кривыми схемных характеристик цепи опорного напряжения согласно настоящему варианту осуществления.

ОПИСАНИЕ ВАРИАНТОВ ВОПЛОЩЕНИЯ

РИС. 3 показана схема опорного напряжения согласно варианту осуществления настоящего изобретения. Цепь опорного напряжения содержит генератор тока с положительным температурным коэффициентом 9. 0221 301 , генератор тока с отрицательным температурным коэффициентом 302 и резистор R 37 . Генератор 301 положительного температурного коэффициента используется для генерирования тока I PTC с положительным температурным коэффициентом, а генератор тока 302 с отрицательным температурным коэффициентом используется для генерирования тока I NTC с отрицательным температурным коэффициентом. Затем в R 9 втекают два тока I PTC и I NTC .0221 37 для формирования независимого от температуры тока I TC . Ток I TC протекает через резистор R 37 для формирования стабильного опорного напряжения V BG с малой температурной зависимостью.

0221 301 , генератор тока с отрицательным температурным коэффициентом 302 и резистор R 37 . Генератор 301 положительного температурного коэффициента используется для генерирования тока I PTC с положительным температурным коэффициентом, а генератор тока 302 с отрицательным температурным коэффициентом используется для генерирования тока I NTC с отрицательным температурным коэффициентом. Затем в R 9 втекают два тока I PTC и I NTC .0221 37 для формирования независимого от температуры тока I TC . Ток I TC протекает через резистор R 37 для формирования стабильного опорного напряжения V BG с малой температурной зависимостью.

Генератор тока с положительным температурным коэффициентом 301 состоит из операционного усилителя 311 , токового зеркала с положительным температурным коэффициентом 304 с транзисторами PMOS MP 31 ˜MP 34 MP, 9 транзисторами PMOS0221 35 , МП 36 и резисторы R 31 ˜R 34 . Два входа операционного усилителя 311 соединены с узлами Va и Vb соответственно, а его выход электрически соединен с затворами PMOS-транзисторов MP 31 ˜MP 34 . PMOS-транзистор МП 31 имеет исток, подключенный к рабочему напряжению V DD , сток, подключенный к резистору R 31 , и затвор, подключенный к выходу операционного усилителя 9.0221 311 . PMOS-транзистор MP 32 имеет исток, подключенный к рабочему напряжению V DD , сток, подключенный к резистору R 32 , и затвор, подключенный к выходу операционного усилителя 311 . PMOS-транзистор MP 33 имеет исток, подключенный к рабочему напряжению V DD , сток, подключенный к резистору R 35 , и затвор, подключенный к выходу операционного усилителя 311 . Транзистор PMOS МП 34 имеет исток, подключенный к рабочему напряжению V DD , сток, подключенный к резистору R 37 , и затвор, подключенный к выходу операционного усилителя 311 .

Два входа операционного усилителя 311 соединены с узлами Va и Vb соответственно, а его выход электрически соединен с затворами PMOS-транзисторов MP 31 ˜MP 34 . PMOS-транзистор МП 31 имеет исток, подключенный к рабочему напряжению V DD , сток, подключенный к резистору R 31 , и затвор, подключенный к выходу операционного усилителя 9.0221 311 . PMOS-транзистор MP 32 имеет исток, подключенный к рабочему напряжению V DD , сток, подключенный к резистору R 32 , и затвор, подключенный к выходу операционного усилителя 311 . PMOS-транзистор MP 33 имеет исток, подключенный к рабочему напряжению V DD , сток, подключенный к резистору R 35 , и затвор, подключенный к выходу операционного усилителя 311 . Транзистор PMOS МП 34 имеет исток, подключенный к рабочему напряжению V DD , сток, подключенный к резистору R 37 , и затвор, подключенный к выходу операционного усилителя 311 . Резистор R 31 включен последовательно между стоками ПМОП-транзисторов МП 31 , МП 35 , а резистор R 32 включен последовательно между стоками ПМОП-транзисторов МП 32 , МП 36 . Два резистора R 31 и R 32 соединены с заземляющим концом соответственно двумя другими резисторами R 33 и R 34 . Два конца резистора R 35 соответственно подключены к затворам PMOS транзисторов МП 35 , МП 36 . Для удобства иллюстрации здесь указаны узловые напряжения Va и Vb.

Резистор R 31 включен последовательно между стоками ПМОП-транзисторов МП 31 , МП 35 , а резистор R 32 включен последовательно между стоками ПМОП-транзисторов МП 32 , МП 36 . Два резистора R 31 и R 32 соединены с заземляющим концом соответственно двумя другими резисторами R 33 и R 34 . Два конца резистора R 35 соответственно подключены к затворам PMOS транзисторов МП 35 , МП 36 . Для удобства иллюстрации здесь указаны узловые напряжения Va и Vb.

Генератор тока с положительным коэффициентом 301 делает узловое напряжение Va равным узловому напряжению Vb с помощью механизма обратной связи, сформированного операционным усилителем 311 и транзисторы PMOS MP 31 , MP 32 . Таким образом, падение напряжения ΔV SG на резисторе R 35 получается и выражается следующим образом.

Таким образом, падение напряжения ΔV SG на резисторе R 35 получается и выражается следующим образом.

Δ В SG = V SG35 – V SG36 (4)

. Соответствующий I 9023 3 3102 3 310 2 3102 3 3102 3 3102 3 3102 3 3102. 3102 3 3102. 310 2 3102. 3102.10 210 2 3.

Я 31=( В SG35 =V SG36 )/ R 35 (5)

36 настоящего варианта осуществления работают в подпороговой области с соотношением площадей 1:К. Ввиду того, что токовая характеристика двух транзисторов МП 35 , МП 36 аналогична характеристике биполярного транзистора, напряжения В SG35 и V SG36 выражаются следующими формулами:

VSG35≈VTH+n·VT·ln(ID35(W/L)35·IDO)(6) ·VT·ln(ID36(W/L)36·IDO)(7)

где, V TH – пороговое напряжение; n и I DO – параметры процесса; V T – тепловое напряжение; I D — ток стока, протекающий через МОП-транзистор; (Ш/Д) 35 представляет собой отношение ширины к длине PMOS-транзистора MP 35 ; и (Ш/Д) 36 представляет собой отношение ширины к длине PMOS-транзистора MP 36 . По формулам (4)~(7) ток I 31 , протекающий через резистор R 35 , определяется следующим образом.

По формулам (4)~(7) ток I 31 , протекающий через резистор R 35 , определяется следующим образом.

I31=1R35·n·VT·ln(K)(8)

Поскольку тепловое напряжение V T является положительным температурным коэффициентом, ток I PTC формируется путем повторения тока I 31 – ток с положительным температурным коэффициентом. Другими словами, токовое зеркало 9 с положительным температурным коэффициентом0221 304 генерирует ток с положительным температурным коэффициентом I PTC .

Чтобы предотвратить работу токового зеркала с положительным температурным коэффициентом 304 в подпороговой области, генератор тока с положительным температурным коэффициентом 301 использует резисторы R 33 и R 34 для формирования другого пути тока для текущее зеркало с положительным температурным коэффициентом 304 , так что текущее зеркало с положительным температурным коэффициентом 304 удерживается в области сильной инверсии ветвящимися токами I 32 и I 33 . Кроме того, два входа операционного усилителя 311 соответственно соединены с PMOS-транзисторами MP 35 , MP 36 резисторами R 31 , R 32 . Падения напряжения на резисторах R 31 , R 32 способствуют повышению двух входных напряжений (т.е. узловых напряжений Va и Vb) операционного усилителя 9.0221 311 , так что операционный усилитель 311 работает в области высокого усиления и не ограничивается входным синфазным диапазоном операционного усилителя 311 .

Кроме того, два входа операционного усилителя 311 соответственно соединены с PMOS-транзисторами MP 35 , MP 36 резисторами R 31 , R 32 . Падения напряжения на резисторах R 31 , R 32 способствуют повышению двух входных напряжений (т.е. узловых напряжений Va и Vb) операционного усилителя 9.0221 311 , так что операционный усилитель 311 работает в области высокого усиления и не ограничивается входным синфазным диапазоном операционного усилителя 311 .

В схеме опорного напряжения согласно настоящему варианту осуществления генератор 302 тока с отрицательным температурным коэффициентом содержит операционный усилитель 312 , квазинезависимый от температуры источник 313 тока, токовое зеркало 9 с отрицательным температурным коэффициентом0221 305 с PMOS транзисторами MP 37 , MP 38 , PMOS транзистором MP 39 и резистором R 36 ._%D0%BF40_%D0%BF41.jpg) Два входных конца операционного усилителя 312 соединены с землей соответственно включенным диодом PMOS-транзистором MP 39 и резистором R 36 , а его выходной конец подключен к затворам PMOS-транзисторов MP. 37 , МП 38 . Квазитемпературно-независимый источник тока 313 включен последовательно между рабочим напряжением V DD и транзистором PMOS MP 39 . Затвор и сток PMOS-транзистора MP 39 соединены с заземляющим концом, а его исток подключен к квазитемпературно-независимому источнику тока 313 . Связь токового зеркала с отрицательным температурным коэффициентом 305 описана следующим образом. Транзистор PMOS MP 37 имеет источник, подключенный к рабочему напряжению В DD , затвор подключен к выходу операционного усилителя 312 , а сток подключен к резистору R 37 .

Два входных конца операционного усилителя 312 соединены с землей соответственно включенным диодом PMOS-транзистором MP 39 и резистором R 36 , а его выходной конец подключен к затворам PMOS-транзисторов MP. 37 , МП 38 . Квазитемпературно-независимый источник тока 313 включен последовательно между рабочим напряжением V DD и транзистором PMOS MP 39 . Затвор и сток PMOS-транзистора MP 39 соединены с заземляющим концом, а его исток подключен к квазитемпературно-независимому источнику тока 313 . Связь токового зеркала с отрицательным температурным коэффициентом 305 описана следующим образом. Транзистор PMOS MP 37 имеет источник, подключенный к рабочему напряжению В DD , затвор подключен к выходу операционного усилителя 312 , а сток подключен к резистору R 37 . PMOS-транзистор MP 38 имеет исток, подключенный к рабочему напряжению V DD , затвор, подключенный к выходу операционного усилителя 312 , и сток, подключенный к резистору R 36 .

PMOS-транзистор MP 38 имеет исток, подключенный к рабочему напряжению V DD , затвор, подключенный к выходу операционного усилителя 312 , и сток, подключенный к резистору R 36 .

Чтобы обеспечить ток с отрицательным температурным коэффициентом, генератор тока с отрицательным температурным коэффициентом 302 использует квазинезависимый от температуры источник тока 313 для обеспечения тока смещения для PMOS-транзистора MP 39 , чтобы генерировать напряжение V SG39 , связанное с отрицательным температурным коэффициентом. Используя свойство виртуального короткого замыкания на двух входах операционного усилителя 312 , в ответ на напряжение V SG39 генерируется ток I 34 с силой тока V SG39 /R 36 . падение на резистор R 36 . Затем ток I 34 воспроизводится зеркалом 305 тока с отрицательным температурным коэффициентом, так что генератор 302 тока с отрицательным температурным коэффициентом генерирует ток I NTC с отрицательным температурным коэффициентом.

Чтобы сделать схему опорного напряжения варианта осуществления более понятной, на фиг. 4~РИС. 8 показывают характеристики схемы настоящего варианта осуществления, которые соответственно проиллюстрированы ниже. ИНЖИР. 4 видно, что при рабочем напряжении V DD составляет 1 В, в настоящем варианте осуществления при изменении температуры от -40°C до 125°C отклонение опорного напряжения ΔV BG выходного опорного напряжения V BG составляет 2,73 мВ (т.е. 16,55 частей на миллион/°С). ИНЖИР. 5 показано соотношение между током положительного температурного коэффициента I PTC и током отрицательного температурного коэффициента I NTC при рабочем напряжении V DD , равном 1 В, и отклонении опорного напряжения ΔV BG составляет 2,73 мВ в варианте осуществления. ИНЖИР. 6 показывает, что при нормальной работе схема опорного напряжения варианта осуществления допускает минимальное рабочее напряжение V DD около 600 мВ. Изменения опорного напряжения (VDD=0,6 В~1,5 В) в зависимости от напряжения питания и температуры представлены на фиг. 7, отклонение эталонного напряжения ΔV BG в результате различных рабочих напряжений V DD составляет 8,91 мВ в худшем случае. Наконец, фиг. 8 показаны изменения опорного напряжения V BG в схеме опорного напряжения варианта осуществления, при изменении параметров процесса, т.е. при разных угловых моделях (FF, TT, SF, FS, SS). В настоящем изобретении учитывалось изменение процесса.

Изменения опорного напряжения (VDD=0,6 В~1,5 В) в зависимости от напряжения питания и температуры представлены на фиг. 7, отклонение эталонного напряжения ΔV BG в результате различных рабочих напряжений V DD составляет 8,91 мВ в худшем случае. Наконец, фиг. 8 показаны изменения опорного напряжения V BG в схеме опорного напряжения варианта осуществления, при изменении параметров процесса, т.е. при разных угловых моделях (FF, TT, SF, FS, SS). В настоящем изобретении учитывалось изменение процесса.

Подводя итог, можно сказать, что вариант осуществления настоящего изобретения использует генератор положительного температурного коэффициента и генератор отрицательного температурного коэффициента для создания стабильного опорного напряжения с низкой температурной зависимостью. По сравнению с традиционной архитектурой, настоящее изобретение использует схемную архитектуру, в которой соединительный провод резисторов может быть изменен, чтобы позволить схеме работать при более низком рабочем напряжении, и, таким образом, площадь компоновки схемы и ограничение операционного усилителя, вызванное схема сокращена и обойдена.