Первая микросхема 🙂 / Хабр

Очень рад в подробностях рассказать о своей первой интегральной схеме и поделиться перипетиями этого проекта, которым занимался на протяжении прошлого года. Надеюсь, мой успех вдохновит других и поможет начать революцию в производстве домашних микросхем. Когда я приступил к этому проекту, то понятия не имел, во что ввязался, но в итоге узнал больше, чем когда-либо думал, о физике, химии, оптике, электронике и многих других областях.

Кроме того, мои усилия сопровождались лишь самыми положительными отзывами и поддержкой со всего мира. Искренне благодарен всем, кто мне помогал, давал советы и вдохновлял на этот проект. Особенно моим удивительным родителям, которые не только всегда поддерживают и поощряют меня как только могут, но и предоставили рабочее место и смирились с затратами на электроэнергию… Спасибо!

Без дальнейших церемоний представляю первую интегральную схему (ИС), изготовленную литографическим способом в домашних (гаражных) условиях — PMOS-чип двойного дифференциального усилителя Z1.

Я говорю «изготовленную литографическим способом», потому что Джери Эллсуорт изготовила первые транзисторы и логические вентили (с соединениями, тщательно проложенными вручную проводящей эпоксидной смолой) и показала миру, что это возможно. Вдохновленный её работой, я представляю интегральные схемы, созданные масштабируемым, стандартным фотолитографическим процессом. Излишне говорить, что это логический шаг вперёд по сравнению с моим предыдущей работой, где я воспроизвёл полевой транзистор Джери.

Я разработал усилитель Z1, когда искал простой чип для тестирования и настройки своего процесса. Макет сделан в Magic VLSI для процесса PMOS с четырьмя масками (активная/легированная область, подзатворный оксид, контактное окно и верхний металлический слой). У PMOS есть преимущество перед NMOS, если учесть ионные примеси из-за изготовления в гараже. Маски разработаны с соотношением сторон 16:9 для упрощения проекции.

Макет Magic VLSI

Генерация маски

Активная область

Затвор

Контакт

Металл

Размер затвора приблизительно 175 мкм, хотя на чипе для проверки выполнены элементы размером до 2 мкм. Каждая секция усилителя (центральная и правая) содержит три транзистора (два для дифференциальной пары с общим резистором в эмиттерах и один в качестве источника тока/нагрузочного резистора), что означает в общей сложности шесть транзисторов на ИС. В левой части резисторы, конденсаторы, диоды и другие тестовые элементы, чтобы изучить характеристики техпроцесса. Каждый узел дифференциальных пар выходит отдельным штифтом на выводной рамке, поэтому его можно изучать, а при необходимости добавить внешнее смещение.

Каждая секция усилителя (центральная и правая) содержит три транзистора (два для дифференциальной пары с общим резистором в эмиттерах и один в качестве источника тока/нагрузочного резистора), что означает в общей сложности шесть транзисторов на ИС. В левой части резисторы, конденсаторы, диоды и другие тестовые элементы, чтобы изучить характеристики техпроцесса. Каждый узел дифференциальных пар выходит отдельным штифтом на выводной рамке, поэтому его можно изучать, а при необходимости добавить внешнее смещение.

Процесс изготовления состоит из 66 отдельных шагов и занимает примерно 12 часов. Выход достигает 80% для больших элементов, но сильно зависит от количества выпитого кофе в конкретный день. Я также записал видео на YouTube о теории производства микросхем и отдельно об изготовлении МОП-транзисторов.

Пластина N-типа 50 мм

Пластина N-типа 50 мм

Сначала с пластины снимается нативная окись быстрым погружением в разбавленный фтороводород с последующей интенсивной обработкой травильной смесью «пиранья» (смесь серной кислоты и перекиси водорода), смесью RCA 1 (вода, аммиак, перекись водорода), смесью RCA 2 (вода, соляная кислота, перекись водорода) и повторным погружением во фтороводород.

Защитный окисел термически выращивается в водяном паре окружающего воздуха (влажное оксидирование) до толщины 5000−8000 Å.

Влажное термическое оксидирование

Влажное термическое оксидирование

Трубчатая печь

Оксидированная пластина

Оксидированная пластина готова к формированию рисунка на активной/легированной (Р-типа) области. Фоторезист AZ4210 наносится на вращающуюся примерно на 3000 оборотах в минуту подолжку, формируя плёнку толщиной около 3,5 мкм, которая аккуратно подсушивается при 90°С на электроплитке.

Процесс литографии детально

Маску активной зоны обрабатывает мой фотолитографический степпер Mark IV в ультрафиолете с шагом 365 нм — и структура отрабатывается в растворе гидроксида калия.

Структура резиста

30-минутная подсушка

Травление активной зоны

После этого структура резиста плотно затвердела и применяется несколько других трюков, чтобы обеспечить хорошее сцепление и химическую стойкость во время следующего вытравливания во фтороводороде, который переносит эту структуру на слой подзатворного оксида и открывает окна к голому кремнию для легирования. Эти регионы позже станут истоком и стоком транзистора.

Частицы замыкают затвор

Легированные кристаллы с вытравленными затворами

После этого производится легирование, то есть введение примесей из твёрдого или жидкого источника. В качестве твёрдого источника применяется диск нитрида бора, размещённый поблизости (менее 2 мм) от пластины в трубчатой печи. Как вариант, можно приготовить жидкостный источник из фосфорной или борной кислоты в воде или растворителе — и провести легирование по стандартному процессу преднанесения/погружения во фтороводород/диффундирования/удаления глазури.

Как вариант, можно приготовить жидкостный источник из фосфорной или борной кислоты в воде или растворителе — и провести легирование по стандартному процессу преднанесения/погружения во фтороводород/диффундирования/удаления глазури.

Вышеупомянутые шаги формирования рисунка затем повторяются дважды для подзатворного оксида и контактного слоя. Подзатворный оксид должен быть гораздо тоньше (менее ~750 Å), чем защитный оксид, поэтому зоны между стоком/истоком вытравливаются — и там выращивается более тонкий оксид. Затем, поскольку вся пластина оксидировалась на шаге легирования, нужно вытравить контактные окна, чтобы установить контакт металлического слоя с легированными зонами истока/стока.

Теперь все транзисторы сформированы и готовы к межсоединениям с выходом на выводную рамку. Защитный слой алюминия (400−500 нм) распыляется или термически напыляется на пластину. Альтернативой был бы метод взрывной литографии (lift-off process), когда сначала формируется фоторезист, а затем осаждается металл.

Напылённый металл

Напылённый металл

Затем на слое металла формируется рисунок методом фотолитографии и происходит травление в горячей фосфорной кислоте, чтобы завершить изготовление интегральной схемы. Заключительные шаги перед тестированием — это визуальный осмотр и высокотемпературный отжиг алюминия для формирования омических переходов.

Микросхема теперь готова для упаковки и тестирования.

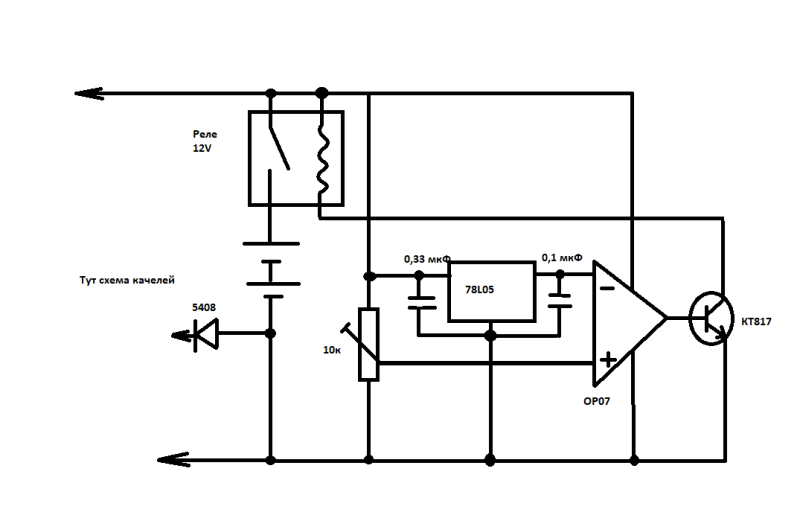

У меня нет установки микросварки (принимаю пожертвования!), поэтому сейчас процесс тестирования ограничен прощупыванием пластины острым пинцетом или использованием платы flip-chip (трудно выровнять) c подключением к характериографу. Дифференциальный усилитель также эмпирически тестируется в цепи для проверки работоспособности.

Кривая IV

Кривая IV

Кривая FET Ids/Vds от с предыдущего устройства NMOS

Конечно, эти кривые далеки от идеальных (в том числе из-за излишнего сопротивления контактов и других подобных факторов), но я ожидаю улучшения характеристик, если раздобуду установку микросварки.

Микросхема STR54041 – ШИМ-контроллер для ипульсных блоков питания со встроенным силовым ключом

Внешний вид и назначение выводов str54041:

| Назначение выводов | №выв. | |

| Общий | 1 | |

| Вход обратной связи | 2 | |

| Коллектор ключевого транзистора | 3 | |

| Эмиттер ключевого транзистора | 4 | |

| Входной сигнал усилителя ошибки | 5 | |

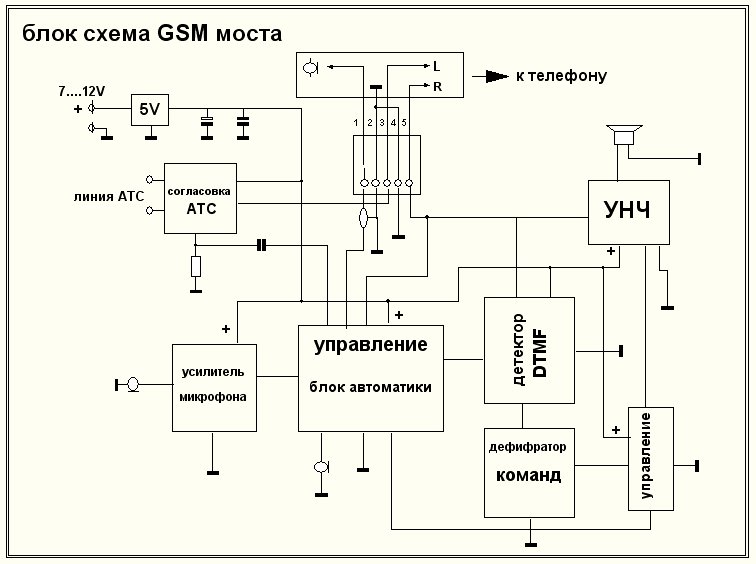

Рис. 2. Структурная схема микросхемы str54041

Типовые схемы блоков питания на микросхеме STR54041

Принцип работы блока питания на микросхеме STR54041

Принцип работы микросхемы str54041 рассмотрим на примере импульсного блока питания телевизора Sony KV-V2155K (шасси: ВЕ-2А).

Рис. 5.Принципиальная схема импульсного блока питания телевизора Sony KV-V2155K.

Блок питания формирует стабилизированные вторичные напряжения +120 В, +21 В, +8 В, +5 В для питания узлов телевизора в рабочем и дежурном режимах.

Блок построен на основе ШИМ-контроллера со встроенным силовым ключом ic STR58041. Микросхема включает в себя источник опорного напряжения, усилитель сигнала ошибки, усилитель тока и силовой ключ.

Схема работает следующим образом. Выпрямленное и отфильтрованное сетевое напряжение поступает на 5 вывод Т601. Благодаря смещению R607, R611 силовой ключ начинает открываться и через обмотку 5-7 Т601 течет ток.

Напряжение ПОС с обмотки 11-13 Т601 прикладывается к базе ключа (2 вывод IC601) и ускоряет процесс перехода его в состояние насыщения. Рост тока через обмотку 5-7 Т601 прекращается, полярность напряжений на обмотках изменяется на противоположную, теперь уже к базе силового ключа будет приложен отрицательный потенциал обмотки положительной обратной связи (ПОС) 11-13 Т601, что приведет к его переходу в состояние отсечки. Далее процесс открытия и закрытия силового ключа повторяется. Таким образом постоянное напряжение преобразуется в импульсную последовательность частотой в десятки кГц. Накопление энергии в Т601 происходит, когда силовой ключ открывается, а передача энергии в нагрузку — в момент закрытого состояния ключа.

Далее процесс открытия и закрытия силового ключа повторяется. Таким образом постоянное напряжение преобразуется в импульсную последовательность частотой в десятки кГц. Накопление энергии в Т601 происходит, когда силовой ключ открывается, а передача энергии в нагрузку — в момент закрытого состояния ключа.

Стабилизация вторичных выходных напряжений осуществляется следующим образом. На обмотке 13-15 Т601 формируется напряжение, величина которого пропорциональна выходным напряжения блока питания. Оно выпрямляется (D607, С618) и поступает на 1 вывод IC601 для формирования опорного напряжения. Часть выпрямленного напряжения поступает на 5 вывод IC601 (вход усилителя ошибки). Сигнал с выхода усилителя ошибки через усилитель тока поступает на базу силового ключа, изменяет его рабочую точку и тем самым изменяет время открытого и закрытого состояния ключа, что приводит к стабилизации выходных напряжений.

На элементах R609, R615, Q601 выполнена защита силового ключа от перегрузки. При значении тока через ключ, близком к максимальному, падение напряжения на R609 открывает Q601 и низким уровнем силовой ключ запирается.

С целью уменьшения влияния помех на работу узлов телевизора частота работы преобразователя синхронизируется сигналом из блока строчной развертки.

Трансформатор Т604 является элементом гальванической развязки. Сигнал синхронизации подается непосредственно на базу силового ключа (2 вывод IC601).

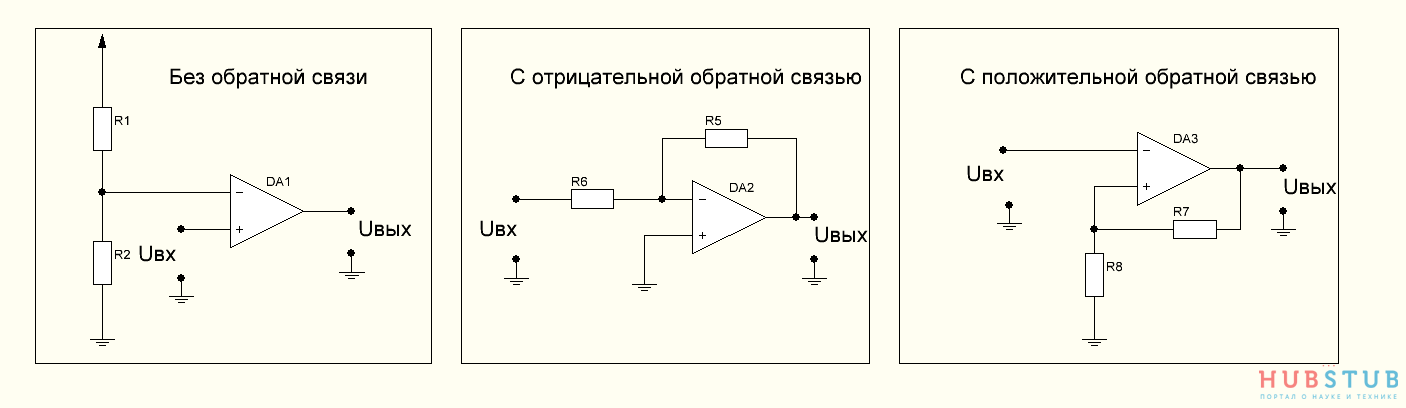

Интегральная микросхема – презентация онлайн

1. Интегральная микросхема

Два изобретения середины ХХ века значительноувеличили скорость технологического (и, как следствие,

общественного) прогресса. Сделанный в 1948 году

транзистор открыл дорогу твердотельной электронике. А

спустя десять лет появился микрочип, интегральная

схема, ставшая предшественником микропроцессора,

который оказал гигантское влияние на всю современную

цивилизацию.

• В 1958 году изобретатель Роберт Нойс (Robert

Noyce) из Fairchild Semiconductor, позже ставший

одним из основателей Intel, создал первую

кремниевую планарную интегральную схему.

Практически одновременно с Нойсом, но

независимо от него, к похожему техническому

решению пришел Джек Килби из Texas

Instruments.

В основе микросхемы

лежало другое

ключевое

изобретение —

транзистор,

созданный в 1947

году в Bell Labs.

3. Изобретение микросхем началось с изучения свойств тонких оксидных плёнок, проявляющихся в эффекте плохой электропроводимости

при небольших электрическихнапряжениях

Транзистор- радиоэлектронный

компонент из полупроводникового

материала обычно с тремя выводами,

позволяющий входным сигналам управлять

током в электрической цепи. В русскоязычной

литературе

и документации до 1970-х гг.

применялись обозначения «Т»,

«ПП» (полупроводниковый

прибор) или «ПТ»

(полупроводниковый триод).

4. первый транзистор – маленький элемент схемы, действующий подобно миниатюрному выключателю и тем самым позволяющий реализовывать

алгоритмы обработкиинформации.

После изобретения

микросхемы отпала

необходимость

соединять компоненты

электрической схемы

вручную, а

транзисторы стали

постепенно

уменьшаться в

размерах.

5. Классификация транзисторов

Германиевые

Кремниевые

Арсенид-галлиевые

• Биполярные

– n-p-n структуры, «обратной проводимости».

– p-n-p структуры, «прямой проводимости»

• Полевые

– с p-n переходом

– с изолированным затвором

• Однопереходные

• Криогенные транзисторы

Пятьдесят лет назад, в сентябре 1958 года, Джек Килби

продемонстрировал руководству Texas Instruments первый рабочий

экземпляр интегральной схемы – на небольшом кристалле

полупроводника инженеру удалось разместить несколько

компонентов электронной схемы, таких как транзисторы, резисторы,

конденсаторы и пр. Килби использовал в качестве

полупроводникового материала кристалл германия, который сегодня

не столь популярен, как кремний.

7. Джек Килби

( Jack St. Clair Kilby,8 ноябра 1923,Джефферсонсити -20 июня 2005 ,Даллас) — американскийучёный. Лауреат Нобелевской премии по

физике в 2000году за своё

изобретение интегральной схемы в 1958 году в

период работы в Texas Instruments (TI). Также

он — изобретатель карманного калькулятора и

термопринтера (1967).

Таким образом, достижение Джека Килби

заключается в практической реализации идей

его английского коллеги, Джеффри Даммера,

однако значение этого шага столь велико, что в

2000 году Килби становится лауреатом

Нобелевской премии, именно за его разработки

конца 50-хх годов.

Следующим значительным этапом развития интегральных микросхем стала

демонстрация Робертом Нойсом (компания Fairchild Semiconductor) интегральной

схемы на основе кремния.

Роберт Нортон Нойс

(Robert Norton Noyce;

12 декабря 1927 — 3 июня 1990) —

американский инженер,

один из изобретателей

интегральной схемы (1959),

один из основателей

Fairchild Semiconductor (1957),

основатель, совместно с

Г.

Муром, корпорации Intel (1968).

Муром, корпорации Intel (1968).Интегральная (микро)схема

(ИС, ИМС, м/сх, англ. integrated circuit, IC,

microcircuit), чип, микрочип (англ. microchip, silicon chip, chip — тонкая

пластинка — первоначально термин относился к пластинке кристалла

микросхемы) — микроэлектронное устройство — электронная

схема произвольной сложности (кристалл), изготовленная

на полупроводниковой подложке (пластине или плёнке)

и помещённая в неразборный корпус, или без такового, в случае

вхождения в состав микросборки.

На сегодняшний день большая часть микросхем изготавливается в корпусах

для поверхностного монтажа. Кристалл в микроэлектронике —

размещённая на полупроводниковой пластине или плёнке электронная

схемапроизвольной сложности.

В процессе сборки упаковывается в

корпус и в результате образует готовое изделие — микросхему

Кристалл СБИС

10. Как работает микрочип

11. Транзисторы соединяют друг с другом в разной последовательности для того, чтобы реализовать разные логические операции: И, ИЛИ,

Транзисторы соединяют друг с другом в разнойпоследовательности для того,

чтобы реализовать разные

логические операции:

И, ИЛИ, НЕ, Исключающее ИЛИ

схема устройства,

которое

складывает два

двузначных

числа: AB + CD =

XYZ

12.

Технологический процесс

Технологический процесс При изготовлении микросхем используется метод фотолитографии

В качестве характеристики технологического процесса производства

микросхем указывают минимальные контролируемые размеры

топологии фотоповторителя

В 1970-х годах минимальный контролируемый размер составлял 28 мкм в 1980-х был уменьшен до 0,5-2 мкм. Экспер.образцы 0,18 мкм.

В 1990-х годах экспериментальные методы стали внедряться в

производство и быстро совершенствоваться. В начале 1990-х

процессоры (например, ранние Pentium и Pentium Pro) изготавливали

по технологии 0,5-0,6 мкм (500—600 нм). Потом их уровень поднялся до

250—350 нм. Следующие процессоры (Pentium 2, K6-2+, Athlon) уже

делали по технологии 180 нм.

В конце 1990-х фирма Texas Instruments создала новую

ультрафиолетовую технологию с минимальным контролируемым

размером около 80 нм. Но достичь её в массовом производстве не

удавалось вплоть до недавнего времени. По состоянию на 2009 год

технологии удалось обеспечить уровень производства вплоть до 90 нм.

• Новые процессоры

• (сперва это был Core 2 Duo) делают по новой УФ-технологии 45 нм.

Есть и другие микросхемы, давно достигшие и превысившие данный

уровень (в частности, видеопроцессоры и флеш-память

фирмы Samsung — 40 нм). Тем не менее дальнейшее развитие

технологии вызывает всё больше трудностей. Обещания фирмы Intel

по переходу на уровень 30 нм уже к 2006 году так и не сбылись.

• По состоянию на 2009 год альянс ведущих разработчиков и

производителей микросхем работает над тех. процессом 32 нм.

• В 2010-м в розничной продаже уже появились процессоры,

разработанные по 32-х нм тех. процессу.

Контроль качества

• Для контроля качества интегральных микросхем широко применяют

так называемые тестовые структуры.

14. Корпуса микросхем

Микросхемы выпускаются в двухконструктивных вариантах — корпусном и

бескорпусном.

Корпус микросхемы — это несущая система и

часть конструкции, предназначенная для

защиты от внешних воздействий и

для электрического соединения с внешними

цепями посредством выводов.

Корпуса

Корпусастандартизованы для упрощения технологии

изготовления готовых изделий.

Бескорпусная микросхема — это

полупроводниковый кристалл,

предназначенный для монтажа в гибридную

микросхему или микросборку

(возможен непосредственны

монтажна печатную плату).

15. Специфические названия микросхем

• Фирма Intel первой изготовила микросхему, которая выполнялафункции микропроцессора Intel 4004. На базе усовершенствованных

микропроцессоров 8088 и 8086 фирма IBM выпустила свои

известные персональные компьютеры).

• Микропроцессор формирует ядро вычислительной машины,

дополнительные функции, типа связи с периферией выполнялись с

помощью специально разработанных наборов микросхем (чипсет).

Для первых ЭВМ число микросхем в наборах исчислялось десятками и

сотнями, в современных системах это набор из одной-двух-трёх

микросхем. В последнее время наблюдаются тенденции постепенного

переноса функций чипсета (контроллер памяти) в процессор.

• Законодательство России предоставляет правовую охрану топологиям

интегральных микросхем.

16. Интересные факты:

• В мае 2011 фирмой Altera была выпущена, по 28 нм техпроцессу,самая большая в мире микросхема, состоящая из 3,9 млрд

транзисторов.

• Так выглядит микрочип — стандартное приспособление для

измерения уровня активности генов. Яркость свечения каждой из

ячеек соответствует уровню активности одного конкретного гена

• Разработка интегральной схемы с широким

использованием устройств функциональной

микроэлектроники позволяет вплотную

приблизиться к «идеальной конструкции»

гибридных устройства.

17. Материалы:

•http://theoryandpractice.ru•http://ru.wikipedia.org

•http://elementy.ru

•http://chernykh.net

•http://www.3dnews.ru

Что такое микросхемы. Как они работают, с чего изготовляются, какая главная их задача

Википедия гласит, что микросхема – это материальное воплощение электрической схемы, которое выполняет определенную функцию. Эта формулировка также подходит к чипам – маленьких плоских кусочков, на поверхности которых, собственно происходит весь процесс.

Микросхемы обрабатывают информацию, которая выражена двоичным кодом (бинарным кодом) единицами и нулями. Они работают на основе транзисторов – радиоэлектронных полупроводниковых элементов, которые управляют входным током. В одной микросхеме помещается до миллиарда транзисторов, что дает нам огромные вычислительные мощности. Сегодня, на микросхемах построены современные компьютеры, смартфоны и вся умная электроника.

Как работает микросхема

Так как микросхемы является основой всех гаджетов, что нас окружают, следовательно, технология достаточно массовая. В ее основе лежит специальный материал – монокристаллический кремний, на нем и формируется инженерами микросхемы с электронных элементов: конденсаторов, резисторов и транзисторов.

во избежании неприятностей, микросхемам нужен диэлектрик, который служит для изоляции транзисторов друг от друга и металлические проводники для соединения. Иными словами говоря, транзистор превращает входной ток и передает информацию в виде 01001 110 000111 010101… и тому подобное.

Как изготовляют монокристаллический кремний

В современных микросхемах на одном кристалле кремния расположены миллиарда транзисторов, поэтому их размещением занимается компьютер, а не человек.

Кристаллы для микросхем выращивают специальным способом, к сплаву кремния кладут небольшой кусочек самого кремния, и медленно его вращают, пока не начнет застывать. Из этого следует цилиндр монокристаллического кремния, который нарезают на несколько пластин. К кремнию добавляют атомы различных элементов, формируя ключевой элемент транзистора – p-n-переход. Пленка из оксида кремния изолирует транзисторы, а металлические развязки соединяют их между собой.

Быстрая и правильная обработка информации – главная задача микросхем

Выше говорилось, что микросхемы выполняют вычислительные функции. Они обрабатывают двоичный код, трансформируя его в электрический сигнал и наоборот. С микросхем созданы различные устройства – от датчиков движения к средствам машинного зрения и разумных бытовых приборов.

Что такое закон Мура?

Основатель корпорации Intel Гордон Мур вычислил, что количество транзисторов на монокристалле удваивается каждые два года. Это происходит благодаря уменьшению самих транзисторов, однако у этого процесса есть предел, который рано или поздно придется пересечь, что есть проблемой, так как неизвестно как это сделать.

Производство центральных процессоров, внутри наших устройств, имеет ограничения. Дело в том, что общая вычислительная мощность возрастает, если распределять задачи между ядрами процессора. Логичное решение – создание многоядерных процессоров – позволило сделать рывок в микроэлектронике 10 лет назад, когда Intel представила двухъядерный процессор Core Duo.

Впрочем, этот же закон вводит ограничения на рост производительности от этой многоядерности.

Угрозу видят в том, что на фоне стремительного роста технологий микросхем предыдущие технологии будут слишком быстро и «искусственно-принудительно» устаревать. Через токсичные материалы, которые используют в производстве современных компьютеров, чрезмерный моральный износ без разумного регулирования имеет вредное воздействие на окружающую среду и может привести к катастрофе.

Мировая микроэлектроника, следуя закону Мура, до сих пор всегда опровергала опасения инженеров, что вот-вот упремся в непреодолимые физические ограничения, после которых отрасль или застрянет навсегда, или должна будет перейти на принципиально новые материалы и технологии.

Принципы построения, функционирования и диагностики микросхем семейства DP104, применяемых в источниках питания мониторов Samsung

В очень многих моделях мониторов Samsung, а также в мониторах других торговых марок, выпускаемых по OEM соглашениям с Samsung, применяются микросхемы семейства DP104, к которому относятся DP304, DP704, DP308 и другие. Любой специалист, сколько-нибудь серьезно занимающийся ремонтом мониторов, сталкивался с этими микросхемами. И, наверняка, у него появлялась масса вопросов, типа: «Что это такое и как это работает?», «Каким образом это можно проверить?» и «Где это можно приобрести?». Постараемся дать ответы на большую часть подобных вопросов и, постараемся, наконец-то, разобраться со всеми нюансами работы и диагностики данных микросхем.

Микросхема DP104, как впрочем, и другие «DP-шки», относятся к микросхемам класса SPS (Samsung Power Switch) – силовые ключи от Samsung. Микросхемы данного класса объединяют в себе две функции:

1. Функцию мощного ключа.

2. Функцию управляющей микросхемы.

Управляющий модуль, входящий в состав SPS, обеспечивает функционирование ключа в режиме широтно-импульсной модуляции – ШИМ (PWM), а также обеспечивает силовой ключ различными защитами. Внешний вид и блок-схема силового ключа типа SPS, представлены на рис.1, а описание контактов приводится в табл.1.

Рис.1 Блок-схема и внешний вид микросхемы DP 104Таблица 1. Назначение контактов DP 104

|

№ |

Обознач. |

Функция |

|

1 |

DRAIN |

Сток внутреннего FET транзистора. Этот контакт подключается к первичной обмотке импульсного трансформатора. |

|

2 |

GND |

Общий. Контакт для подключения к «земле». Внутри этот контакт соединен со стоком FET транзистора. |

|

3 |

VCC |

Вход питающего напряжения. Этот контакт также используется и как вход для сигнала защиты от превышения напряжения (OVP). |

|

4 |

VFB |

Вход сигнала обратной связи, который используется для стабилизации выходных напряжений источника питания. Через этот контакт также осуществляется и защита от короткого замыкания в нагрузке (OCP). |

|

5 |

SYNC |

Вход сигнала синхронизации, который осуществляет подстройку рабочей частоты микросхемы под параметры строчной развертки. Контакт также используется для обеспечения функции «мягкого» старта. |

Функциональная схема SPS-ключа и минимально-необходимые для его работы внешние компоненты изображены на рис.2.

Рис.2 Типовой источник питания на базе DP104Рассмотрим принципы запуска и функционирования микросхемы.

Цепь запуска

Микросхемы SPS спроектированы таким образом, чтобы запускаться при малых пусковых токах, величиной около 0.1 мА. В составе SPS имеется схема UVLO (Under Voltage Lock Out – отключение при понижении входного напряжения), гарантирующая, что питающее напряжение равно величине, полностью делающей микросхему работоспособной. Схема UVLO защищает микросхему от работы при низком питающем напряжении.

Рис.3 Схема запуска и схема UVLO микросхемы DP 104

Схемы запуска и UVLO представлены на рис.3. Схема UVLO начинает функционировать, когда на контакте 3 напряжение достигает величины 15В (рис.4). Величина тока, потребляемого микросхемой в момент запуска, составляет всего 0.1 мА – это позволяет минимизировать потери мощности. Однако после запуска микросхемы, величина потребляемого тока резко возрастает.

Рис.4 Гистерезис запуска и выключения микросхемы DP104

Схема UVLO отключает микросхему в момент, когда питающее напряжение падает ниже 9В, т.е. процесс включения/выключения представляет собой гистерезис величиной 6В. Этот гистерезис предотвращает беспорядочные включения и выключения микросхемы во время подачи напряжения, т.к. в течение почти 40 мс после ее запуска наблюдаются колебания питающего напряжения (рис.5). И если в течение этого времени микросхема SPS выключится, то для ее перезапуска придется полностью отключить питающее напряжение.

Рис.5 В момент включения на линии питания наблюдаются колебания в течение 40 мс

Внутренний стабилитрон Vz обеспечивает ограничение величины питающего напряжения на уровне 32В. Это предотвращает разрушение микросхемы под воздействием высоковольтного напряжения. Если напряжение питания становится выше 32В, стабилитрон открывается и весь входной ток течет через него. В результате, напряжение на входе «+» компаратора «Сброс при включении питания» становится ниже 6.5В, и компаратор на своем выходе формирует сигнал блокировки микросхемы. Компаратор «Сброс при включении питания» никак не связан со схемой UVLO и не питается опорным напряжением Vref.

После того как микросхема запустится, ее внутренний источник опорного напряжения начинает формировать напряжение Vref величиной 5В, которое используется для питания цепей управления. Величина напряжения Vref не зависит от температурных колебаний кристалла микросхемы и не зависит от колебаний питающего напряжения. Работа источника опорного напряжения разрешается сигналом от схемы UVLO. Напряжение Vref предназначено для формирования различных внутренних напряжений смещения, а также для управления логикой схемы контроля опорных напряжений. Опорное напряжение никак не используется схемой UVLO и компаратором «Сброс при включении питания».

Рис.6 Пусковая цепь блоков питания мониторов Samsung SynMaster 550B/750S

Процесс запуска DP104 рассмотрим на примере блока питания мониторов Samsung SyncMaster 550B и 750S. Пусковая цепь этих блоков питания приведена на рис.6, а их запуск происходит следующим образом:

1) Если переключатель SW601 находится в разомкнутом состоянии (монитор выключен), то к катоду диода D606 приложено напряжение менее 5В. Это напряжение создается делителем, состоящим из резисторов R609, R610 и R605.

2) Когда переключатель SW601 переводится в состояние «включено», пусковой ток начинает протекать через резисторы R609, R610, обеспечивая медленный заряд конденсатора С609. Напряжение конденсатора является напряжением Vcc, прикладываемым к конт.3 микросхемы DP104.

3) В момент, когда конденсатор зарядится до 15В, схема UVLO запустит преобразователь, и в дополнительной обмотке импульсного трансформатора T601 появятся импульсы, которые выпрямляются диодом D606 и сглаживаются конденсатором C609. В результате на конденсаторе C609, а значит и на конт.3 DP104 создается напряжение величиной 18-19В, которое и является нормальным питающим напряжением.

Процесс запуска DP104 поясняют осциллограммы основных сигналов на рис.7.

Рис.7 Алгоритм процесса запуска микросхемы DP104

Цепь «мягкого» старта

«Мягкий» старт подразумевает плавное нарастание длительности импульсов, открывающих силовой ключ. В результате ток через ключ и все выходные напряжения не сразу становятся максимальными, начинают монотонно нарастать. Такой плавный запуск позволяет предотвращать появление повышенного выходного тока блока питания, а, значит, и снижать вероятность отказа элементов источника питания в момент включения. Поэтому можно говорить, что наличие схемы «мягкого» старта является обязательным атрибутом современного импульсного преобразователя напряжения.

При рассмотрении принципа «мягкого» старта DP104 обратимся к части схемы источника питания монитора Samsung SyncMaster 550B, представленной на рис.8.

Рис.8 Схема “мягкого старта” микросхемы DP104 в составе монитора Samsung SyncMaster 550B

Когда микросхема включена и нормально функционирует, в средней точке диодов (аноды D1, D2 и D3) устанавливается напряжение 3.15В. Это напряжение можно получить простым вычислением по формуле 1 для эквивалентной цепи, изображенной на рис.9 (сопротивлением открытого диода пренебрегаем).

Рис.9 Эквивалентная схема внутреннего делителяИсточником тока 0.9мА обеспечивается заряд конденсатора C610 до напряжения 3.15В, что приводит к установке этого потенциала на конт.4. При этом на входе компаратора ШИМ-логики напряжение будет соответствовать величине 0.9В (вычисляется по формуле 2). Напряжения 3.15В на входе микросхемы и 0.9В на входе внутреннего компаратора, соответствуют максимальной длительности управляющих импульсов, т.е. соответствуют максимальному току преобразователя.

Цепь «мягкого» старта подключается к конт.5 и состоит, главным образом, из конденсатора C611. Кроме того, в состав цепи входит еще и внутренний диод D3. Заряд конденсатора C611 будет происходить значительно медленнее, чем заряд конденсатора C610, что обусловлено разностью в номиналах их емкостей (C611=1мкФ, С610=47нФ). В момент запуска микросхемы DP104 оба конденсатора разряжены, и начинают заряжаться источником тока 0.9 мА. В результате часть тока ответвляется на зарядку конденсатора С611, что, естественно, приводит к уменьшению тока, заряжающего С610.

В момент заряда С611 потенциал средней точки диодов D1, D2 и D3 уменьшается – этот потенциал составляет уже не 3.15В, а равен величине напряжения на С611 плюс 0.7В (падение напряжения на D3). В результате, и на «минусовом» входе компаратора ШИМ-логики потенциал также будет ниже 0.9В, что приведет к уменьшению длительности рабочего цикла управляющих импульсов. Постепенно, по мере заряда C611, потенциал в средней точке диодов растет; растет напряжение на входе компаратора и увеличивается длительность управляющих импульсов.

Когда конденсатор С611 зарядится до величины 3.15В, диод D3 закроется, и напряжение на С610 сразу же достигает максимального значения 3.15В. Напряжение на входе компаратора также становится максимальным – 0.9В, длительность управляющих импульсов растет, и ток преобразователя увеличивается. Далее регулировка этого тока осуществляется только лишь за счет обратной связи, напряжение которой прикладывается к конт.4.

Конденсатор же C611 заряжается до 5В за счет внутреннего резистора Rc. Конденсатор мягкого старта C611 разряжается, когда схема UVLO отключает DP104. Это позволяет повторить процесс «мягкого» старта при повторном перезапуске.

Диаграммы, поясняющие суть работы схемы «мягкого» старта, представлены на рис.10.

Рис.10 Алгоритм работы схемы “мягкого старта” в DP104

Цепь синхронизации

Так как микросхема DP104 разработана специально для применения в мониторах, она должна иметь возможность синхронизироваться со строчной разверткой. Наличие функции синхронизации является отличительной особенностью импульсных регуляторов, применяемых в мониторах, от регуляторов общего назначения.

Синхронизация позволяет сделать так, чтобы шумовые помехи на изображении, вызванные переключением мощного транзистора источника питания, возникали во время обратного хода луча по строке. В результате, эти помехи оказываются невидимыми. Для такой синхронизации источника питания используется импульс обратного хода, вырабатываемый в выходном каскаде строчной развертки.

Рис.11 Схема синхронизации DP104 с блоком строчной развертки

Рассмотрим функционирование цепи синхронизации по рис.11. Внешний сигнал синхронизации подается на конт.5 микросхемы DP104. Этот сигнал не должен быть меньше чем -0.6В, что обеспечивается резистором R614 и диодом D607. Напряжение сигнала синхронизации на рис.11 обозначено, как Vrs. После того, как «мягкий» старт завершится, на конденсаторе C611 создается напряжение величиной 5В. В момент, когда импульс синхронизации активизируется, напряжение Vrs «накладывается» на 5В конденсатора С611, в результате чего на конт.5 появляется импульс амплитудой более 7В. Внутренний компаратор синхронизации сравнивает это напряжение с опорным напряжением 7.2В и формирует на своем выходе сигнал Vcomp, который изменяет частоту переключения триггера задающего генератора. В отсутствии сигнала синхронизации задающий генератор работает с частотой собственных колебаний.

Рис. 12 Сигналы контрольных точек цепи синхронизацииФорма сигналов в контрольных точках цепи синхронизации DP104 приведены на рис.12 и по ним можно сделать следующие замечания:

1) Сигнал AFC (автоматическая подстройка частоты) снимаемый с выходного каскада строчной развертки прикладывается к разделительному трансформатору T602. Импульс ЭДС, наводимый во вторичной обмоткеТ602, создает ток через дифференциальную цепь, состоящую из C612 и R614. Отрицательная часть продифференцированного сигнала «срезается» диодом D607, в результате остается только часть отрицательного выброса величиной около 0.6-0.7В (падение напряжения на открытом диоде). Таким образом получается сигнал Vrs амплитудой около 3В.

2) Полученный сигнал Vrs прикладывается к нижней по рисунку обкладке конденсатора С611, напряжение на котором составляет 5В. Напряжение сигнала Vrs суммируется с постоянным напряжением 5В, и результирующий сигнал с амплитудой около 8В прикладывается к конт.5 микросхемы DP104.

3) В момент, когда импульс на конт.5 достигнет величины 7В или выше, внутренний компаратор перестроит частоту генератора под параметры входного сигнала.

Цепь обратной связи

Модуль обратной связи SPS DP104 выполняет две основные функции:

– регулировка напряжения Vfb;

– обеспечение функции «задержка отключения».

Импульсный трансформатор состоит из первичной и вторичной части. В то время как во вторичной части находятся лишь вторичные обмотки, в первичной части трансформатора имеются и первичная обмотка и третичные обмотки. Третичные обмотки бывают двух типов, в соответствии с выполняемыми ими функциями:

– третичная обмотка для создания питающего напряжения Vcc микросхемы DP104;

– третичная обмотка для формирования напряжения обратной связи Vfb.

Естественно, что в данном разделе мы рассматривать обмотку обратной связи.

Регулировка и стабилизация выходных напряжений источника питания осуществляется модуляцией ширины импульсов, управляющих затвором FET транзистора. Ширина этих импульсов определяется путем сравнения напряжения Vfb, подаваемого на конт.4 микросхемы, с напряжением, которое формируется на резисторе токового датчика – Rsense . Наличие встроенного токового датчика (резистора Rsense) и узкополосного фильтра позволяет снизить количество внешних элементов микросхем семейства SPS.

Функционирование цепи обратной поясняет схема на рис.13.

Рис.13 Цепь обратной связи микросхемы DP104

Напряжение обратной связи Vfb при нормальном функционировании блока питания должно находиться в диапазоне от 0В до 3.15В. Напряжение обратной связи Vfb, равное 3.15В, соответствует максимальному значению тока FET-транзистора, а уменьшение напряжения Vfb приводит к уменьшению этого тока (рис.14). Величина Vfb определяется напряжением на конденсаторе C610, который заряжается источниками тока 0.9мА и 4мкА, входящими в состав DP104. Разряд конденсатора C610 обеспечивается внешним транзистором Q602. Источник тока 0.9мА обеспечивает заряд C610 в момент запуска микросхемы (см. раздел «мягкий» старт), а источник тока 4мкА поддерживает заряд конденсатора уже после того, как диод D1 закроется.

Рис.14 Уменьшение напряжения обратной связи FB приводит к уменьшению тока FET транзистора

Напряжение Voff используется для блокировки работы микросхемы SPS при отсутствии нагрузки.

Основные элементы цепи обратной связи представлены на рис.15. Рассмотрим функционирование этого каскада.

1) Для формирования напряжения обратной связи используется третичная обмотка, в которой при работе DP104 наводятся импульсы, выпрямляемые диодом D614 и сглаживаемые конденсатором C630. Это напряжение открывает стабилитрон ZD601, в результате чего создается ток Iz, величина которого прямопропорциональна величине всех выходных напряжений источника питания. Этим током открывается Q602, в результате чего начинает изменяться потенциал конт.4 микросхемы DP104.

2) Если нагрузка вторичной цепи уменьшается, то это ведет к увеличению напряжения Vout. Часть энергии передается в третичную обмотку обратной связи, что в итоге приводит к увеличению тока Iz. Транзистор Q602открывается и через его коллектор начинает протекать ток внутреннего диода D2. В результате, потенциал средней точки диодов уменьшается, т.е. уменьшаетcя и ток диода D1. Напряжение на «-» входе компаратора падает, что ведет к уменьшению длительности управляющих импульсов FET-транзистора, т.е. ведет к уменьшению тока через первичную обмотку импульсного трансформатора. Как следствие, все вторичные выходные напряжения уменьшаются, т.е. обеспечивается их стабилизация.

3) При уменьшении же вторичного напряженияVout все процессы происходят в обратном порядке, т.е.: ток Iz уменьшается – транзистор Q602 призакрывается – ток коллектора Q602 уменьшается – уменьшается ток диода D2 – потенциал средней точки диодов и ток диода D1 возрастают – возрастает напряжение на «-» входе компаратора – длительность управляющих импульсов возрастает – ток первичной обмотки растет – выходные напряжения увеличиваются, т.е. стабилизируются.

4) Рассмотренный выше процесс стабилизации осуществляется импульсным методом, т.е. происходит периодически, но в очень короткие моменты времени, когда к катоду ZD601 прикладывается напряжение 6.8 – 6.9В (в этот момент времени начинает протекать ток Iz). Напряжение 6.8 – 6.9 В получается за счет суммирования двух напряжений: напряжения перехода база-эмиттер транзистора Q602 (Vbe=0.6-0.7В) и порогового напряжения стабилитрона ZD601 (6.2 В).

Рис.15 Типовое построение и основные элементы цепи обратной связи микросхемы DP104

Токовая защита

Токовая защита, она же защита от коротких замыканий (OCP – Over Current Protection), обеспечивает отключение микросхемы SPS в случае обнаружения слишком большого тока в выходных цепях источника питания. Токовая защита организована через контакт обратной связи (конт.4). Сигнал обратной связи является нормальным, когда его величина меньше 3.15В, но больше 0В. Если сопротивление на выходе источника питания падает, или в цепи обратной связи возникает какая-либо другая проблема, должна начать свое функционирование цепь «задержка отключения», образованная компаратором токовой защиты, конденсатором C610 и источником тока 4мкА. Цепь «задержка отключения» изменяет режим заряда конденсатора обратной связи C610. Напомним, что этот конденсатор заряжается внутренними источниками тока микросхемы, а разряжается внешним транзистором Q602, который открывается током цепи обратной связи. При возникновении короткого замыкания в нагрузке, все выходные напряжения а, значит, и напряжение обратной связи уменьшаются практически до нуля. Уменьшение сигнала обратной связи приводит к прекращению тока Iz и закрыванию транзистора Q602. И вот в момент, когда разряд конденсатора C610 прекратится из-за полного закрывания транзистора Q602, цепь «задержка отключения» начинает заряд конденсатора до более высокого потенциала. Поясним принцип функционирования цепи токовой защиты, используя рис.16.

Рис.16 Цепь токовой защиты микросхемы DP104

1) Если уровень напряжения обратной связи на конт.4 больше 0В, но в то же самое время не превышает 3.15В, заряд конденсатора C610 осуществляется источником тока 0.9 мА через диод D2. При этом форма зарядного тока С610 представляет собой кривую (Т1 на рис.17).

2) Когда потенциал на конденсаторе С610 достигнет уровня 3.15В и превысит его, диод D2 закрывается, и заряд конденсатора будет осуществляться источником тока 4мкА. Форма зарядного тока С610 на этом этапе становится практически прямолинейной (T2 на рис.17). В это время через транзистор FET протекают максимальные токи.

3) Когда напряжение на конденсаторе С610 достигнет величины порядка 7.5 – 8В, компаратор OCP переключится и сформирует сигнал отключения.

4) Микросхема DP104 блокируется и для ее повторного запуска необходимо обеспечить перезапуск питающего напряжения, т.е. микросхему необходимо выключить и снова включить. Эта функция обеспечивается цепью «Сброс при включении питания». После того как срабатывает блокировка, конденсатор C610 заряжается до потенциала VCC источником тока 4мкА и именно напряжение устанавливается на конт.4 до тех пор, пока микросхема не перезапустится.

Рис.17 Функционирование токовой защиты DP104

Защита от превышения напряжений

Схема защиты от превышения напряжений (OVP – Over Voltage Protection) обеспечивает защиту вторичной части блока питания в том случае, если величина выходных напряжений становится недопустимо большой. Защита от превышения организована через контакт питающего напряжения микросхемы SPS (конт.3). Если в цепи обратной связи возникнет какая-либо неисправность, например, сигнал обратной связи будет оборван, выходные напряжения начнут очень быстро увеличиваться, т.к. микросхемой будет обеспечиваться режим максимальных токов, что в итоге может привести к очень серьезным последствиям. Задача схемы OVP заключается в том, чтобы в этом случае определить аварийный режим работы и отключить микросхему SPS.

Рис.18 Цепь питания DP104

На рис.18 показана цепь питания микросхемы DP104, и из этого рисунка видно, что после запуска микросхема питается от третичной обмотки импульсного трансформатора. Импульсы этой обмотки выпрямляются диодом D606 и

сглаживаются конденсатором C609. Полученное, таким образом, напряжение подается на конт.3 микросхемы DP104.

Если все функционирует правильно, то на конт.3 создается потенциал порядка 18 – 20В. Однако как только в цепи обратной связи возникают проблемы, напряжение на C609 начинает нарастать очень и очень быстро, т.к. в этом случае импульсы в третичной обмотке изменяют свою амплитуду мгновенно.

Напряжение конт.3 сравнивается внутренним компаратором OVP с опорным напряжением 25В. Поэтому, как только на конт.3 напряжение превысит величину 25В, компаратор формирует блокирующий сигнал, обеспечивающий отключение микросхемы. Защита от превышения напряжения является триггерной, т.е. после ее срабатывания микросхема блокируется, и перезапустить ее можно только путем выключения. Если быть более точным, то схема OVP «освобождается», когда напряжение на конт.3 падает до уровня 6.5В. Повторный запуск микросхемы DP104 после срабатывания OVP, обеспечивается цепью «Сброс при включении питания».

Термическая защита

Термическая защита (TSD) предотвращает повреждение микросхемы SPS в случае перегрева ее корпуса. Если температура кристалла микросхемы достигает 150°С, или становится выше, схема TSD активизирует триггер отключения. Повторный запуск микросхемы DP104 после срабатывания термической защиты обеспечивается цепью «Сброс при включении питания», т.е. только после отключения питания

Схема гашения переднего края импульса

Схема гашения переднего импульса (LEB – Leading Edge Blanking) позволяет предотвратить переключение FET-транзистора во время прохождения нежелательного импульса тока, который возникает в момент включения FET. Все дело в том что, как только FET-транзистор открывается, ЭДС во всех обмотках импульсного трансформатора меняет свое направление, в результате чего через вторичные выпрямительные диоды в течение некоторого (очень короткого) периода времени начинает протекать обратный ток (ток обратного восстановления диодов). Этот паразитный ток наводит во всех обмотках, в том числе и в первичной обмотке, ЭДС, вызывающую появление достаточно мощного, хотя и короткого, импульса тока через FET-транзистор. Формированию этого импульса способствует еще и наличие эквивалентной емкости перехода сток-исток полевого транзистора.

Рис.19 Схема гашения переднего импульса – LEB

Возникающий импульс тока формирует на внутреннем резисторе Rsense импульс напряжения, который способен вызвать срабатывание компаратора, и, как следствие, может оборвать импульс, открывающий транзистор FET. Таким образом, необходимо этот переходной процесс подавить и предотвратить отключение FET. В случае, когда управляющая микросхема и транзистор разделены, подавление нежелательного импульса тока осуществляется применением RC-фильтра, устанавливаемого между токовым датчиком и микросхемой. В данном же варианте, такое подавление обеспечивается схемой LEB, которая блокирует цепь обратной связи на время прохождения нежелательного импульса тока. Схема LEB является более точной, по сравнению с RC-фильтром, т.к. схемой LEB анализируется форма напряжения на затворе FET. За счет эффекта Миллера форма напряжения затвора очень точно показывает момент окончания импульса тока.

Реализация схемы LEB демонстрируется на рис.19, а принцип ее функционирования поясняет временная диаграмма на рис.20.

Рис. 20 Принцип работы схемы LEB

Диагностирование микросхем SPS

Так как практически все микросхемы семейства SPS имеют одинаковую функциональную схему и одинаковое назначение контактов, предлагаемая ниже методика тестирования подходит в равной степени для всех микросхем этого типа.

Диагностирование микросхем опирается на хорошее знание принципов функционирования SPS и знание их внутренней архитектуры. Именно поэтому, мы сначала в таких подробностях рассмотрели структуру DP104 и функционирование ее отдельных узлов. Это будет ключом к пониманию методов диагностики микросхем SPS, и позволит грамотно походить к вопросам использования аналогов, а также к вопросам возможной доработки схем при установке аналогов с несколько отличающимися параметрами.

Для диагностирования микросхем семейства SPS нам понадобится следующее оборудование:

– осциллограф;

– тестер для измерения сопротивления и напряжения;

– лабораторный источник питания с возможностью регулировки выходных напряжений (лучше иметь два источника, т.к. это позволит провести наиболее полную функциональную проверку).

Мы предлагаем четыре типа диагностических проверок микросхем SPS:

1. Простая проверка на «пробой» силового ключа.

2. Простая функциональная проверка.

3. Расширенная функциональная проверка.

4. Полная функциональная проверка.

Начнем рассмотрение этих проверок в порядке их усложнения.

Проверка на «пробой» силового ключа

Для этой процедуры достаточно иметь под руками самой простой мультиметр. Суть проверки заключается в «прозвонке» перехода сток-исток внутреннего FET-транзистора. Практически во всех случаях отказ микросхем сопровождается пробоем этого транзистора, поэтому данный метод является наиболее быстрым и эффективным, а самое главное, дает почти 100%-ый результат достоверности.

Итак, для проверки микросхемы измеряем сопротивление между конт.1 и конт.2. При этом к конт.1 прикладывается «плюс» измерительного прибора, а к конт.2 – «минус». Если это сопротивление очень большое (десятки МОм), то микросхему можно считать исправной. Если же это сопротивление составляет единицы-десятки Ом, то с уверенностью можно говорить о неисправности микросхемы и необходимости ее замены.

Данную проверку можно проводить, не выпаивая микросхему из печатной платы – это практически не влияет на достоверность результата, поэтому рассмотренный метод вполне подходит под определение «экспресс-анализа» (однако всегда стоит учитывать наличие внешних элементов, способных «коротить» переход сток-исток FET-транзистора).

Этой проверки достаточно в подавляющем большинстве случаев, однако, при очень сложных ситуациях, а также при попытках установить аналогичную микросхему, может потребоваться более детальный анализ.

Простая функциональная проверка

Для проведения этой проверки потребуются все те приборы, которые мы упоминали выше. Суть проверки заключается в том, что на микросхему SPS, которую не выпаивают из схемы, подают питающее напряжение от лабораторного источника питания. Естественно, что при такой проверке монитор нельзя включать в питающую сеть, т.е. проверка проводится в режиме, абсолютно безопасном для силовых каскадов.

Рассмотрим последовательность действий по порядку:

1) От лабораторного источника подаем напряжение на конт.3 микросхемы SPS. Начинаем это напряжение плавно увеличивать.

2) Когда питающее напряжение достигнет величины 15В, микросхема SPS запускается, и на конт.1 «проскакивают» импульсы (в течение очень короткого периода времени). Наличие импульсов контролируем с помощью осциллографа. Но стоит обратить внимание на тот факт, что сток транзистора в этом эксперименте не запитан, а поэтому импульсы имеют очень маленькую амплитуду (милливольты) и контролировать их можно, лишь установив очень высокую чувствительность осциллографа.

3) Кроме того, после запуска микросхемы на конт.5 устанавливается напряжение около +5В, а на конт.4 – устанавливается напряжение почти равное напряжению питания.

4) С помощью лабораторного источника начинаем увеличивать питающее напряжение на конт.3. При этом на конт.4 напряжение также пропорционально растет, а напряжение на конт.5 остается без изменений.

5) Далее начинаем уменьшать выходное напряжение лабораторного источника питания. При этом на конт.4 напряжение также пропорционально уменьшается, а напряжение на конт.5 все также остается без изменений. Однако в момент, когда напряжение на конт.3 уменьшится до 9В, микросхема SPS отключится, т.е. напряжения на конт.4 и на конт.5 пропадут (установятся в 0В).

Именно такое поведение микросхемы, как это было только что описано, можно считать нормальным. При любых отклонениях от приведенного алгоритма необходимо провести углубленную диагностику, как самой микросхемы, так и элементов блока питания.

Расширенная функциональная проверка

Целью этой проверки является попытка ввести микросхему SPS в режим постоянной генерации. Как мы видели в предыдущем тесте, в момент запуска микросхемы на ее конт.1 «проскакивают» импульсы, но тут же пропадают. Это связано с тем, что срабатывает защита от короткого замыкания в нагрузке. Для того чтобы избежать срабатывания этой защиты необходимо изменить потенциал на конт.4 (контакт обратной связи). С этой целью впаиваем резистор, желательно переменный, номиналом 5-10 кОм между конт.4 и «землей» (рис.21).

Рис.21 Переменный резистор впаивается между конт.4 DP104 и “землей”

При подаче питающего напряжения величиной 15В на конт.3, микросхема SPS запускается, и на конт.1 можно наблюдать регулярные импульсы. Но, опять же, обращаем внимание на то, что амплитуда этих импульсов очень мала.

Подкручивание переменного резистора практически не дает каких–либо изменений. Лишь только когда номинал этого резистора будет выкручен почти в 0 Ом, генерация прекращается.

Отсутствие генерации на конт.1 при выполнении этого теста требует замены микросхемы, а также проведения внимательнейшей проверки других компонентов блока питания.

Полная функциональная проверка

Целью проверки является запуск микросхемы и проверка всех ее внутренних функций. Для данного теста потребуется еще один источник питания, который лучше всего подключить к выпрямительному конденсатору (рис.22). В остальном же, все делаем так, как и в предыдущем тесте.

Рис.22 Лабораторный стенд для полного функционального тестирования DP104

Далее действуем в следующем порядке:

1) Включаем лабораторный источник №1, который создает смещение на первичной обмотке импульсного трансформатора блока питания. На выходе этого источника устанавливаем напряжение 6В – 9В.

2) Включаем второй лабораторный источник, которым запитывается микросхема SPS. На выходе источника устанавливаем напряжение 15В и выше. Микросхема запускается, и на конт.1 появляются импульсы, размахом 9В – 15В, которые контролируем осциллографом. Блок питания начинает функционировать, правда не в номинальном режиме, но некоторые выходные напряжения могут достичь соответствующих значений (например, может щелкнуть реле петли размагничивания).

3) Подкручивая переменный резистор, начинаем контролировать изменение длительности импульсов на конт.1.

Внимание! Эту проверку не стоит проводить в течение слишком большого периода времени, т.к. микросхема SPS начинает сильно разогреваться, что в принципе, может привести к ее отказу.

Данная проверка дает полное представление о работоспособности микросхемы, но самое главное преимущество данного теста – это возможность проверить на только (и не столько микросхему), сколько весь источник питания. При выполнении данной проверки можно контролировать наличие импульсов во всех обмотках силового трансформатора, контролировать исправность вторичных выпрямительных диодов и отсутствие коротких замыканий в нагрузке. Хотя, конечно же, необходимо делать скидку на то, что это, все-таки, «ненормальный» режим работы блока питания.

Аналоги и взаимозаменяемость

Как мы уже отмечали в самом начале статьи, семейство SPS представлено множеством микросхем. Наиболее часто применяемыми микросхемами являются: DP104, DP704 и DP904. Но кроме них можно встретиться еще и с такими силовыми ключами, как DP306, DP308, DP108, DP708, DP706. Кроме того, аналоги этих микросхем выпускаются фирмой Fairchild Semiconductor, из которых наиболее известными и доступными являются KA2S0880 и KA2S0680, но кроме них существуют и другие типы микросхем этого семейства, например, КА5S0765C-TU и FS6S0765RCH. Эти микросхемы имеют абсолютно такую же внутреннюю архитектуру и точно такое же расположение контактов, а отличаются они лишь своими параметрами: величиной максимального тока, уровнем срабатывания защит, максимальной длительностью рабочего цикла и некоторым другими характеристиками. Поэтому все эти микросхемы можно считать взаимозаменяемыми, но иногда такие замены требуют некоторых доработок, что связано именно с различием характеристик.

Все различия представителей этого большого класса можно компенсировать изменением параметров цепи обратной связи, которая подключается к конт.4 микросхемы. В случае, когда при установке аналогичной микросхемы блок питания перестает нормально функционировать, необходимо изменить параметры либо резистора R608, либо стабилитрона ZD601 (рис.23). Чаще всего практикующие специалисты проводят замену резистора R608, что считается более простым решением. Так, например, при замене микросхемы DP704 на микросхему DP104 номинал этого резистора увеличивают (обычно с 220 Ом до 1.2 кОм). Но, в принципе, точно такого же результата можно добиться и увеличением порогового напряжения стабилитрона ZD601 (только подобрать нужный порог срабатывания оказывается сложнее, чем подобрать резистор).

Рис.23 Элементы, которые необходимо корректировать при подборе аналогов микросхемы DP104

Кроме того, схему можно доработать с помощью резистора Rдоп, устанавливаемого между конт.4 и «землей». Проще всего установить в качестве этого резистора переменный резистор номиналом до 15 кОм – это позволит упростить процесс настройки источника питания.

В случае, когда сигнал обратной связи в блоке питания формируется с помощью оптрона, а не с помощью третичной обмотки, доработать схему проще всего двумя способами: изменением номинала резистора R606 или изменением номинала резисторов R653 и R654 (рис.24).

Рис.24 “Доработка” схемы при использовании аналогов DP104 при условии, что сигнал обратной связи формируется на дополнительной обмотке импульсного трансформатора

Хочется надеяться, что после такого подробного анализа микросхем семейства DP, проблемы, связанные с возможной доработкой схем источников питания, будут решаться без особых сложностей.

Некоторые практические результаты взаимозаменяемости микросхем SPS представлены в табл.2.

Таблица 2. Аналоги микросхемы DP104 и необходимые доработки схемы при их применении

|

Микросхема |

Замена |

|

DP704C |

Заменяется на DP104C, но требуется увеличение номинала R608 до 1.2кОм. Если резистор не заменить, то в дежурном режиме начинает щелкать реле Degauss. |

|

DP704C |

Замена на KA2S0680 с одновременным увеличением номинала R608 до 1.2кОм. |

|

DP904 |

Замена на DP104 без доработок прошла успешно. |

|

DP104 |

Замена на KA2S0680 с одновременным увеличением номинала R608 до 1.2кОм. |

|

КА5S0765C-TU |

Замена на DP104 без доработок, возможно, что корректна и обратная замена. |

|

DP104 |

Замена на FS6S0765RCH без доработок. |

Рассказ о микросхемах SPS будет неполным, если не рассмотреть их практическое применение. Именно для этого мы приводим два варианта блоков питания с микросхемами SPS семейства DP.

На одной из схем сигнал обратной связи формируется третичной обмоткой импульсного трансформатора, а на второй схеме – сигнал обратной связи формируется из выходного напряжения и передается на микросхему DP через оптопару. Надеемся, что теперь представленные схемы не требуют пояснений.

LinkSwitch — микросхемы для построения обратноходовых преобразователей малой мощности – Компоненты и технологии

Долгое время не занятая импульсниками ниша наконец-то занята сетевыми изолированными источниками питания малой мощности 2-4 Вт. LinkSwitch — так назвали новую серию микросхем для построения обратноходовых преобразователей малой мощности. На их основе можно строить изолированные источники питания для применения в проводных и беспроводных телефонах, проигрывателях CD, MP3, игрушках, в бытовой аппартуре в качестве питания дежурного режима, в зарядных устройствах и везде, где требуется отобрать от сети небольшую мощность.

Давайте поближе познакомимся с одной из микросхем этого семейства — LNK501. Это изделие содержит в себе силовой ключ — 700-вольтовый транзистор POWER MOSFET, компаратор ограничения тока, схему отключения при перегреве, схему мягкого запуска, усилитель ошибки, генератор, ШИМ-компаратор. Упакована LNK501 в 7-ножечные корпуса стандартного размера: DIP-8B (вариант Р) и SMD-8B (вариант G), у которых отсутствует одна ножка (рис. 1).

Микросхема позволяет строить недорогие преобразователи из очень малого количества компонентов, причем плата преобразователя по размерам получается меньше, чем трансформатор соответствующей мощности на 50 Гц. И намного легче. Встроенные системы мягкого запуска, авторестарта, защиты от перегрузки и перегрева уменьшают число навесных компонентов, удешевляя схему, упрощая монтаж и увеличивая надежность системы. Рабочая частота микросхемы — 42 кГц. При такой частоте упрощается фильтрация электромагнитных помех на входе и выходе. Кроме того, изолирующий трансформатор совсем маленький по сравнению с 50-герцовым.

С помощью LNK501 можно строить преобразователи не только на фиксированное входное напряжение, но и универсальные (85–265 В), что немаловажно для сельской местности. К особенностям этой микросхемы можно отнести такой интересный факт, как эксплуатация без обратной связи со стороны низкого напряжения. То есть, когда не нужна высокая стабильность выходного напряжения, можно упростить схему, воспользовавшись встроенной обратной связью. Нестабильность выхода увеличивается при этом до ±10%. Если же нужна большая стабильность, в схему придется ввести оптопару.

Для работы с этими микросхемами подбираются трансформаторы стандартной конструкции, наиболее подходящие для работы в таких условиях.

Микросхема соответствует стандартам EсоSmart, Energy Star, Blue Angel и рекомендациям ЕС. При отсутствии нагрузки и напряжении в сети 265 В она потребляет менее 300 мВт. Микросхема не нуждается во внешнем токовом сенсоре для контроля тока.

Назначение выводов

D (сток) — вывод соединен со стоком мощного MOSFET-транзистора, по нему подводится питание ко всей схеме управления (рис. 2). Вывод имеет соединение с внутренней схемой ограничения тока.

С (управление) — вход усилителя ошибки, схемы обратной связи по току (регулировка рабочего цикла) и управление схемой ограничения тока. Встроенный параллельный регулятор подключен к внутреннему источнику тока в нормальном состоянии. Вход также используется для подключения сглаживающего конденсатора и конденсатора компенсации и авторестарта.

S (исток) является выходом мощного ключа для подключения нагрузки и выводом схемы управления первичной обмоткой.

Описание работы

Включение питания

Типовая схема включения без контроля вторичной цепи показана на рис. 1. В течение процесса подачи напряжения конденсатор С1, включенный между выводами С и S, заряжается сквозным током от входа D через внутренний источник тока. Когда напряжение на выводе С достигает значения 5,6 В относительно вывода S, ток прекращается, внутренняя управляющая схема активизируется и внутренний высоковольтный транзистор MOSFET начинает коммутировать первичную обмотку. В этот момент заряд на С1 используется для питания управляющих цепей микросхемы.

Поддержание заданного тока

Форма выходного напряжения повторяет наклон кривой напряжения, приложенного к первичной обмотке трансформатора. Ток IС на выводе С нарастает. Когда значение IС сравняется с IDCT, внутренняя схема ограничивает нарастание IС по достижению порога ILIM (рис. 2). Внутренняя схема обеспечивает V-образную форму IС для поддержания нормального питания во время просадок напряжения.

Поддержание заданного напряжения

Когда IС превышает значение IDCS (рис. 3), уменьшается скважность импульсов. Так как значение IС зависит от напряжения питания, рабочий цикл ограничивается в зависимости от пикового тока, устанавливаемого внутренней цепочкой управления ключом (та самая микросхема LinkSwitch).

В зависимости от положения рабочей точки на графиках рис. 3 микросхема работает либо в режиме поддержания напряжения, либо поддержания тока. При минимуме входного напряжения (в случае использования микросхемы в блоке питания с универсальным входом) этот переход происходит приблизительно при 30% скважности. Когда скважность будет менее 4%, уменьшается частота переключений, чтобы снизить потребление энергии. Резистор R1 (рис. 4) с самого начала выбирается в зависимости от значения IС приблизительно равным IDCT, когда VOUT принимает желаемые значения при минимуме входного напряжения. Окончательный выбор R1 производится, когда будет закончена разработка схемы.

Режим авторестарта

При возникновении каких-либо отклонений в работе, например, короткое замыкание или обрыв нагрузки, прекращается ток на выводе С. Конденсатор С1 разряжается до 4,7 В. При этом активируется схема авторестарта, которая закрывает транзистор MOSFET и переводит управляющую схему в режим низкого потребления мощности. В режиме авторестарта микросхема периодически запускается, но переходит в нормальный режим только после устранения неисправности. Приведенная на рис. 6 характеристика описывает все состояния микросхемы, включенной без обратной связи со стороны низкого напряжения через оптопару.

На регулировку выходного напряжения влияет напряжение на конденсаторе С2, которое, в свою очередь, зависит от ЭДС самоиндукции первичной обмотки трансформатора. Резистор R2 и конденсатор С2 образуют фильтр, на котором выделяется напряжение ошибки.

Если возникает необходимость более жесткого допуска выходного напряжения, необходимо завести обратную связь со стороны низкого напряжения через оптопару. Такая обратная связь обеспечивает микросхемам LinkSwitch лучшие характеристики. На рис. 5 показана типовая схема включения с оптроном обратной связи.

На стороне первичной обмотки добавлены элементы R3, C3 и транзистор оптрона. Светодиод оптрона включен на стороне вторичной обмотки вместе с элементами R5, R4, VR1. Глядя на схему, нетрудно понять, как работает эта обратная связь. Резистор R4 задает рабочий ток VR1. Резистор R5 ограничивает сквозной ток через светодиод оптрона и VR1. Как только напряжение на стороне вторичной обмотки превышает порог открытия светодиода и стабилитрона, засвеченный фототранзистор открывается и шунтирует резистор R3, увеличивая напряжение на конденсаторе C2.

Изменение напряжения на конденсаторе С2 вызывает уменьшение скважности импульсов, подаваемых на мощный ключ, и, как следствие, уменьшение напряжения на стороне вторичной обмотки. Выходная характеристика микросхемы показана на рис. 6.

За более подробной информацией обращайтесь на сайт

www.powerint.com.

Микросхема для блока питания LNK626, и ремонт блока питания

Одним прекрасным летним утром я обнаружил полное отсутствие наличия интернета. Дальнейшие проверки показали во-первых отсутствие свечения каких бы то ни было светодиодов на роутере, а во-вторых — отсутствие какого бы то ни было напряжения на выходе блока питания. Блок питания этот я уже однажды ремонтировал — издох выходной конденсатор. Но на этот раз всё оказалось серьёзнее. Благо был запасной БП…Вскрытие показало, что у главной и единственной микросхемы сорвало крышу, и из неё вышел волшебный дым. А все мы знаем, что микросхемы работают на волшебном дыме, который туда закачивают на заводе, и если дым вышел — всё, микросхему придется менять, потому что закачать в неё этот дым в домашних условиях нет совершенно никакой возможности, не говоря уже о том, что его и не купить-то нигде, прямо заговор производителей!

Кроме ШИМ-контроллера (хотя это в данном случае не совсем корректное название, кстати, вот даташит на него) издохли и оба входных конденсатора, на 400В и 4.7 и 10мкФ, благо я их тоже купил, ну и предохранительный резистор.

Теперь о предмете обзора. Вот они красавицы:

Как видим это распай, что с моей точки зрения хорошо, ножки залужены красиво, и ничто не предвещает беды. Но я решил перестраховаться и проверить их все. Для этого я запаял панельку

Ну и поочередно проверил все 10 микросхем, и все 10 оказались рабочими. Панельку решил оставить

Это лишнее

Это готовый БП.

Шо могу сказать? Я доволен. Про наличие в наших радиолавках я даже не пытался узнать, потому что в чипе-дипе одна микруха стоит почти баксик, и это без доставки, а значит если вдруг свершится чудо и в одной из локальных радиолавок будет эта микруха — то будет уже по полтора-два бакса, что как видим соизмеримо с десятком микрух из Китая. И когда оно нужно в одном экземпляре и реальную цену не знаешь — то и фиг бы с ним, а когда видел сколько оно стоит на али — от местных цен становится не очень хорошо. И да, я понимаю что сравнивать новое в магазине и распай из Китая — некорректно. Зато выгодно 😉 А оставшиеся микрухи, я уверен, пригодятся. Микрухи могу смело рекомендовать к приобретению, и продавец, вероятно, тоже неплохой.

Как работают интегральные схемы?

Как работают интегральные схемы? – Объясни это Рекламное объявлениеКриса Вудфорда. Последнее изменение: 30 января 2020 г.

Вы когда-нибудь слышали о компьютере 1940-х годов? называется ENIAC? Он был примерно такой же длины и веса, как три-четыре двухэтажных автобуса. содержал 18 000 гудящих электронных переключателей, известных как вакуумные лампы. Несмотря на свои гигантские размеры, это были тысячи в разы менее мощный, чем современный ноутбук – машина примерно в 100 раз меньше.

Если история вычислительной техники звучит как волшебный трюк – выжать все больше и больше мощности во все меньшее и меньшее пространство – это так! Что сделало это возможно было изобретение интегрированного схема (IC) в 1958 году. Это изящный способ втиснуть сотни, тысячи, миллионы или даже миллиарды электронных компонентов на крошечные кремниевые чипы нет больше ногтя. Давайте подробнее рассмотрим микросхемы и то, как они работают!

Фото: Интегральная схема снаружи. Он поставляется в удобной форме, называемой двухрядным корпусом (DIP), который состоит из черного пластика или керамический внешний корпус с металлическими штырями по бокам для подключения к электронной плате большего размера (коричневая деталь, которую вы видите на заднем плане).Фактическая схема, которая выполняет эту работу, представляет собой крошечный чип, встроенный в DIP; вы можете увидеть, как он подключен к внешним контактам DIP на следующей фотографии.

Что такое интегральная схема?

Фото: Интегральная схема изнутри. Если бы вы могли снять крышку с типичного микрочипа, такого как тот, что на верхнем фото (а это не очень легко – поверьте, я пробовал!), Вы бы нашли внутри именно это. Интегральная схема – это крошечный квадрат в центре.От него выходят соединения к клеммам (металлические штыри или ножки) по краю. Когда вы подключаете что-либо к одной из этих клемм, вы фактически подключаетесь к самой цепи. Вы можете увидеть рисунок электронных компонентов на поверхности самого чипа. Фото любезно предоставлено Исследовательским центром NASA Glenn Research Center (NASA-GRC).

Откройте телевизор или радио, и вы увидите, что оно построено вокруг печатная плата (PCB) : немного похоже на электрическую карту улиц с маленький электронный компоненты (например, резисторы и конденсаторы) на месте здания и печатные медные соединения связывая их вместе как миниатюрные металлические улочки.Печатные платы хороши в небольших таких приборов, но если вы попытаетесь использовать ту же технику для построить сложную электронную машину, например компьютер, вы быстро врезался в препятствие. Даже самому простому компьютеру нужно восемь электронных переключает на хранение одного байта (символа) информации. Итак, если вы хотите построить компьютер с достаточным объемом памяти для хранения этого абзаца, вы смотрите примерно 750 символов, умноженных на 8 или около 6000 переключателей – за один абзац! Если вы любите переключатели, как в ENIAC – электронные лампы размером взрослый палец – скоро вы получите колоссально большой, энергоемкая машина, которой нужно собственное мини-электричество завод, чтобы он работал.

Когда в 1947 году три американских физика изобрели транзисторы, несколько улучшилось. Транзисторы были размером с электронные лампы и реле. (электромагнитные переключатели, которые начали заменять электронные лампы в середина 1940-х годов), потребляли гораздо меньше энергии и были гораздо более надежными. Но все еще оставалась проблема соединить все эти транзисторы вместе в сложных схемах. Даже после того, как были изобретены транзисторы, компьютеры по-прежнему представляли собой спутанную массу проводов.

Фото: Интегральные схемы вставляются в печатные платы (ПП), как зеленая, которую вы видите здесь.Обратите внимание на тонкие дорожки, соединяющие «ножки» (клеммы) двух разных микросхем. Другие дорожки связывают ИС с обычными электронными компонентами, такими как резисторы и конденсаторы. Вы можете думать о дорожках как о «улицах», прокладывающих пути между «зданиями», где делаются полезные вещи (сами компоненты). Также существует миниатюрная версия печатной платы внутри интегральной схемы: дорожки создаются в микроскопической форме на поверхности кремниевой пластины.

Интегральные схемы все изменили.Основная идея заключалась в том, чтобы взять полная схема со всеми ее многочисленными компонентами и связями между их, и воссоздать все это в микроскопически крошечной форме на поверхности кусок кремния. Это была удивительно умная идея, и она реализована возможно всевозможные «микроэлектронные» гаджеты, которые мы сейчас принимаем за предоставлено, от цифровых часов и карманные калькуляторы на Луну ракеты и ракеты со встроенной спутниковой навигацией.

Закон Мура

Интегральные схемы произвели революцию в электронике и вычислительной технике в 1960-х и 1970-х годах.Первый, инженеры помещали десятки компонентов на микросхему в так называемой маломасштабной интеграции (SSI). Вскоре последовала Medium-Scale Integration (MSI) с сотнями компонентов в области такого же размера. Как и ожидалось, примерно в 1970 году крупномасштабная интеграция (БИС) принесла тысячи компонентов, очень крупномасштабная интеграция (СБИС). дали нам десятки тысяч и миллионы сверхбольших масштабов (ULSI) – и все на микросхемах не больше, чем они был раньше. В 1965 году Гордон Мур из компании Intel, ведущего производителя микросхем, заметил, что количество компонентов на микросхеме удваивалась примерно каждые один-два года. Закон Мура , как он известен, продолжает действовать с тех пор. В интервью The New York Times 50 лет спустя, в 2015 году, Мур выразил свое удивление по поводу того, что закон продолжает оставаться в силе: «Первоначальное предсказание заключалось в том, чтобы смотреть на 10 лет, что, по моему мнению, было большой натяжкой. на интегральной схеме до 60 000 – тысячекратная экстраполяция за 10 лет. Я подумал, что это было довольно дико. Тот факт, что нечто подобное происходит в течение 50 лет, поистине удивительно.«

Диаграмма: Закон Мура: количество транзисторов, упакованных в микрочипы, примерно удваивается каждый год или два за последние пять десятилетий – другими словами, оно растет экспоненциально. Если вы построите график количества транзисторов (ось y) в зависимости от года выпуска (ось x) для некоторых распространенных микрочипов за последние несколько десятилетий (желтые звезды), вы получите экспоненциальную кривую; вместо этого построив логарифм, вы получите прямую линию. Обратите внимание, что вертикальная ось (y) на этой диаграмме является логарифмической. и (из-за графического программного обеспечения OpenOffice, которое я использовал) горизонтальная ось (x) имеет лишь неопределенную линейную форму.Источник: построено с использованием данных Transistor Count, Wikipedia, сверено с данными из других источников.

Рекламные ссылкиКак изготавливаются интегральные схемы?

Фото: Интегральные схемы производятся в безупречно чистых условиях; Рабочие должны носить вот такие «костюмы для кроликов», чтобы они не загрязняли чипы, которые они производят. Это завод Intel по производству пластин в Чандлере, Аризона, США. Фото любезно предоставлено архивом Кэрол М. Хайсмит, Библиотека Конгресса, Отдел эстампов и фотографий.

Как сделать что-то вроде микросхемы памяти или процессора для компьютера? Все начинается с необработанного химического элемента, такого как кремний, который подвергается химической обработке или легированию для придания ему различных электрических свойств …

Легирование полупроводников

Если вы читали наши статьи о диодах и транзисторы, ты будешь знаком с идеей полупроводников . Традиционно люди думали о материалах, которые можно разделить на две аккуратные категории: которые позволяют электричеству течь через их довольно легко (проводники) и те, что нет (изоляторы).Металлы составляют большую часть проводников, а неметаллы, такие как пластик, дерево и стекло изоляторы. На самом деле все гораздо сложнее, особенно когда речь идет об определенных элементы в середине периодической таблицы (в группах 14 и 15), особенно кремний и германий. Обычно изоляторы, эти элементы могут быть заставить вести себя больше как проводники, если мы добавим небольшое количество примеси к ним в процессе, известном как легирование . Если вы добавите сурьму в кремний, вы получите немного больше электронов, чем он. обычно имеет – и способность проводить электричество.Кремний “легированный” таким образом называется n-типа . Добавляем бор вместо сурьмы и вы удаляете часть электронов кремния, оставляя после себя «дыры» которые работают как «отрицательные электроны», несущие положительный электрический ток в обратном порядке. Такой кремний называется p-type . Расположение областей кремния n-типа и p-типа рядом друг с другом создает переходы, в которых электроны ведут себя очень интересным образом – и это как мы создаем электронные компоненты на основе полупроводников, такие как диоды, транзисторы и воспоминания.

Внутри завода по производству микросхем

Фото: кремниевая пластина. Фото любезно предоставлено Исследовательским центром NASA Glenn Research Center (NASA-GRC).