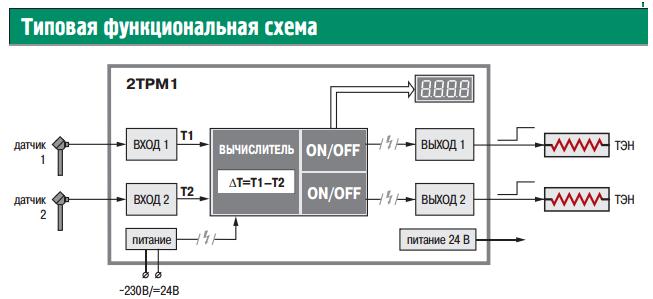

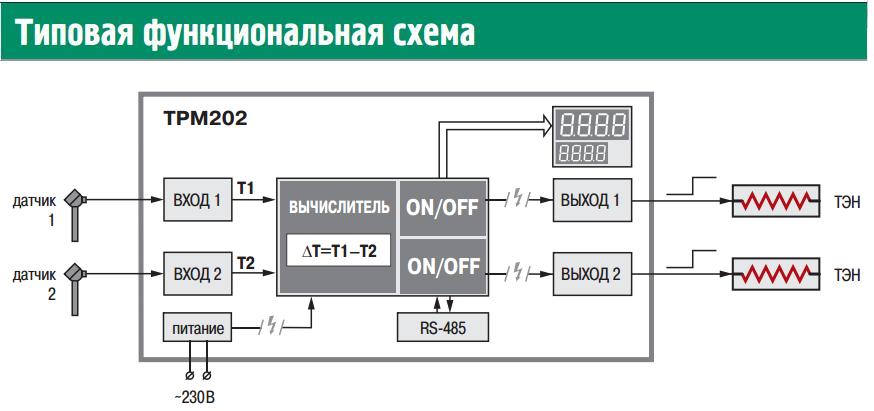

2ТРМ1 обновленный погодозависимый двухканальный регулятор с RS-485

2ТРМ1 – промышленный терморегулятор, предназначенный для измерения, регистрации или автоматического регулирования температуры, а также других физических величин (давление, влажность, уровень, расход и т.д.) по одному или двум каналам одновременно.

Прибор проходит процедуру регистрации в Государственном реестре средств измерений. На текущий момент средством измерения не является. Вы можете заказать 2ТРМ1 с поверкой и сертификатом средства измерения предыдущей модификации.

2ТРМ1 в корпусе для крепления в щит Щ1 и Щ2 | уже в продаже |

2ТРМ1 в компактном корпусе для крепления в щит Щ5 и на DIN-рейку | Cтарт продаж IV квартал 2021 года. Заказать 2ТРМ1-Х. |

2ТРМ1 в корпусе для крепления на стену Н | Старт продаж II квартал 2022 года. Заказать 2ТРМ1-Х.У |

Возможности регулятора:

- Измерение и регулирование физических величин по двум каналам;

- Погодозависимое регулирование;

- Контроль обрыва связи с исполнительными механизмами;

- Регистрация и управление исполнительными механизмами сигналом 4…20мА или 0…10В;

- Сигнализация о выходе измеряемой величины за заданные пределы;

- Регулирование по разности двух физических величин;

- Ручной режим управления исполнительными механизмами.

Преимущества

Сравнительная таблица линеек

Корпус | ||

Цифровой индикатор | Один | Два |

Кнопки управления | Три | Четыре |

Клеммная колодка | Лепестковая | Лифтовая |

Высота индикатора | 14 мм | 20 мм |

Монтаж в щит | Одна плоскость, штыревой зацеп | Одна или две плоскости, «трещетка» |

Шунт для входных сигналов тока | Внешний | Встроенный |

RS-485 | Отсутствует | По заказу |

Уплотнитель для обеспечения IP | Съемный | Встроенный |

Корпусное исполнение Щ5, 48×48мм | Нет | Есть |

Погодозависимое регулирование | Нет | Есть |

Ручной режим управления | Нет | Есть |

Контроль аварии LBA | Нет | Есть |

Исполнение на -40°С | Заказная позиция | Стандартная позиция |

1.

4 Принципиальная электрическая схема объекта, ее описание. Монтаж, наладка и эксплуатация автоматизированной системы управления соляной ванной

4 Принципиальная электрическая схема объекта, ее описание. Монтаж, наладка и эксплуатация автоматизированной системы управления соляной ваннойПохожие главы из других работ:

Автоматизация теплового и технологического режимов дуговой печи ДСП-180 в условиях ЭСПЦ ОАО “ММК”

4. ПРИНЦИПИАЛЬНАЯ ЭЛЕКТРИЧЕСКАЯ СХЕМА УПРАВЛЕНИЯ ЭНЕРГЕТИЧЕСКИМ РЕЖИМОМ ДСП-180

Принципиальная электрическая схема управления энергетическим режимом ДСП-180 приведена на схеме Д.А.220200.005.БР.10.Э0. На клеммы 2 – 9 микропроцессорного контроллера, поз. РМК, поступает 4 сигнала: вторичный ток с катушки Роговского, поз. 35а-1…

Автоматизация управления широкоуниверсальным фрезерным станком

4.1 Электрическая принципиальная схема электроавтоматики станка

Схема электроавтоматики станка содержит: 1 – подключение к питанию комплектных электроприводов подач с указанием выходов контроля состояния: готовность привода, управление приводом, термозащита; соединение блоков управления с двигателями.

Автоматизированный электропривод продольнострогательного станка

2.4 принципиальная электрическая схема силовой части

Принципиальная схема выбирается по [4]. Для номинального тока Iном = 320 А выбираем схему, приведенную на рис. 1.3 [4]: Рисунок 5. Силовая часть однодвигательного электропривода серии КТЭУ, Iном = 320 А…

Бытовой компрессионный холодильник Стинол-102

2.4.1 Электрическая схема и её описание

С технической точки зрения, холодильник Стинол-102 является одним из самых сложных аппаратов в семействе бытовых холодильников Стинол…

Выбор электродвигателя установки и его назначение

3. Принципиальная электрическая схема управления установкой и ее анализ (режим работы, виды защиты, наладка)

Электрическая схема управления электроводонагревателем ЭПЗ-100И2 приведена на рисунке 1,б. Температура нагрева воды задается датчиком температуры ВК.1: максимальную уставку датчика устанавливают на 186 нагрев до 90. ..95°С, минимальную — на 80…85°С…

..95°С, минимальную — на 80…85°С…

Выпарная установка непрерывного действия с равными поверхностями нагрева

2. Принципиальная схема установки и её описание

Рис.1. Принципиальная схема трехкорпусной выпарной установки: 1– емкость исходного раствора; 2.10 — насосы; 3 — теплообменник-подогреватель; 4 –6 выпарные аппараты: 7 — барометрический конденсатор, 8 — вакуум-насос…

Исследование асинхронного исполнительного двигателя с полным немагнитным ротором

Схема электрическая принципиальная лабораторного макета

…

Проектирование системы автоматической стабилизации тока ваерной лебедки

1. Принципиальная схема и описание принципа действия системы

На рис.1 представлена принципиальная схема автоматического регулирования ваерных лебедок на судах типа “Атлантик-333″…

Пульт проверки автомата подогрева стекла

3.3.6 Принципиальная электрическая схема устройства индикации.

Описание работы схемы

Описание работы схемыСхема обеспечивает индикацию 4-х десятичных цифр на семисегментных полупроводниковых индикаторах. Ввод информации производится параллельно в двоично-десятичном коде…

Разработка систем управления для электроприводов постоянного и переменного тока

1.4 Принципиальная электрическая схема

В задачу разработки принципиальной электрической схемы входит определение параметров элементов схемы. Принципиальная электрическая схема задатчика интенсивности (ЗИ), регуляторов тока и скорости представлены на рис. 1.13…

Расчет систем автоматического регулирования

2. Принципиальная схема САР и ее краткое описание

…

Регулирование расхода воды в ЗВО МНЛЗ

2.. Принципиальная электрическая схема регулирования расхода воды в зону вторичного охлаждения

Принципиальная электрическая схема предназначена для определения полного состава элементов схемы и связи между элементами с целью определения принципа работы системы. ..

..

Система теплоснабжения предприятия молочной промышленности в городе Одесса

5.1 Принципиальная схема системы теплоснабжения. Её описание

Из бака для питательной воды вода с помощью насосов подается в экономайзеры, где происходит подогрев питательной воды, далее вода поступает в котлоагрегаты, где вскипает с образованием пара…

Средства и способы автоматизации производственных процессов

2. Принципиальная схема и описание работы прибора ЭРП-61

Описание работы ЭРП-61. На рис.1 дана принципиальная схема прибора ЭРП-61 с подключённым термометром сопротивления Rt и исполнительным механизмом ИМ. Измерительная схема представляет собой автоматически уравновешивающийся мост…

Теплотехнический контроль котлоагрегата

4.1 Принципиальная электрическая схема

Бесшкальные электрические дифманометры-pacxoдомеры, работающие в комплекте со вторичными приборами, служат для дистанционной передачи показаний на щиты управления агрегатами. ..

..

▶▷▶▷ принципиальная электрическая схема калина универсал

▶▷▶▷ принципиальная электрическая схема калина универсал| Интерфейс | Русский/Английский |

| Тип лицензия | Free |

| Кол-во просмотров | 257 |

| Кол-во загрузок | 132 раз |

| Обновление: | 13-05-2019 |

принципиальная электрическая схема калина универсал – Лада Калина Схемы электрических соединений автомобиля vnxsucontentavtovazkalina_electroshemahtml Cached – Схема электрическая принципиальная модуля управления светотехникой приведена в приложении А – Схема электрическая принципиальная комбинации приборов приведена в приложении Б Электросхемы Калины клуб-ладарфelektro-shema-kalinahtml Cached Электросхемы Калины – набор схем электрооборудования ВАЗ 1117, 1118 и 1119 Принципиальная Электрическая Схема Калина Универсал – Image Results More Принципиальная Электрическая Схема Калина Универсал images Электрическая схема автомобиля ЛАДА КАЛИНА electroshemirupubllada_kalina1-1-0-43 Cached Схему проводки автомобиля ЛАДА КАЛИНА и других блоков электрооборудования моделей ВАЗ ЛАДА Калина ::: Схема – MadyarNET madyarnetcarel_shemekalinakalina_1htm Cached Автор сайта не несет никакой ответственности за то, что Вы можете сделать со своим или чужим автомобилем, руководствуясь информацией, взятой со страниц сайта схема лада калина, электрическая схема калина avtolektronrusxema-elektrooborudovaniyaelektricheska Cached Электрическая схема Калина однопроводная имеет четыре основные жгута схемы жгутов и принципиальная схема подключения представлены Электрические схемы на новую Калину 2 Хэтчбек 2192ru?cat80pcat2 Cached Схема заднего жгута проводов Данная принципиальная схема также состоит из двух частей, обратите на это внимание Схема электрическая калины myautojofome533433html Cached Схема соединений жгута проводов панели приборов Лада Калина (Lada Kalina) еще 2 фото Схема электрических соединений жгута проводов заднего автомобиля lada kalina 11174 LADA 1117 Калина Универсал Рис1 Электрическая схема myautojofome313646html Cached Отзывы владельца про ВАЗ калина универсал еще 1 Калина схема электрическая Электрическую Схему Шевроле Нива – nonsocialist locomotion469weeblycomblogelektricheskuyu-shemu Cached ВАЗ Нива Шевролет Принципиальная электрическая схема автомобиля ВАЗ 2123 ВАЗ Нива Шевролет Принципиальная электрическая схема Электрическая схема автомобиля NIVA CHEVROLET С Chevrolet NIVA ваша Электрические схемы Лада Гранта ЛадаОнлайн – все самое ладаонлайнdo-my-selfrepairrepair Cached Схема электрическая соединений автомобиля Lada Granta лифтбек: Калина седан и универсал Promotional Results For You Free Download Mozilla Firefox Web Browser wwwmozillaorg Download Firefox – the faster, smarter, easier way to browse the web and all of 1 2 3 4 5 Next 1,500

- Lada Drive Active: горячие Гранта и Калина.

Для универсала Lada Kalina Cross с октября будет доступе

Для универсала Lada Kalina Cross с октября будет доступе - н еще один цвет синий металлик, а в интерьере возможен опциональный вариант отделки в серо… Автомобиль без принципиальных изменений продержался в производстве 20 лет. В 1980 году ему на смену приш

- мобиль без принципиальных изменений продержался в производстве 20 лет. В 1980 году ему на смену пришел Patrol 160, который выпускался до 1987 года.

ТСУ для ВАЗ 1118 Калина седан, ВАЗ 1117 Калина универсал и ВАЗ 2190 Гранта (со сварным шаром) 2004- без выреза бампера.

Новинки автомобильного рынка и их тест-драйв. Краш-тесты, фотографии. Лада Калина 1117 современный российский универсал, европейского дизайна. Очень приятная опция – электрические подъемники передних стекол.

…изменений в отдельные приказы региональной энергетической комиссии департамента цен и тарифов Краснодарского края следующие изменения: в пункте 2 приложения 1 слова Для потребителей в случае отсутствия дифференциации тарифов по схеме.

..

..

фотографии. Лада Калина 1117 современный российский универсал

изданный гетманом И. С. Мазепой (См. Мазепа )

- электрическая схема калина avtolektronrusxema-elektrooborudovaniyaelektricheska Cached Электрическая схема Калина однопроводная имеет четыре основные жгута схемы жгутов и принципиальная схема подключения представлены Электрические схемы на новую Калину 2 Хэтчбек 2192ru?cat80pcat2 Cached Схема заднего жгута проводов Данная принципиальная схема также состоит из двух частей

- smarter

- что Вы можете сделать со своим или чужим автомобилем

is not in this users list of permitted IP addresses vlaXML

Lada Drive Active: горячие Гранта и Калина. Для универсала Lada Kalina Cross с октября будет доступен еще один цвет синий металлик, а в интерьере возможен опциональный вариант отделки в серо…

Автомобиль без принципиальных изменений продержался в производстве 20 лет. В 1980 году ему на смену пришел Patrol 160, который выпускался до 1987 года. ТСУ для ВАЗ 1118 Калина седан, ВАЗ 1117 Калина универсал и ВАЗ 2190 Гранта (со сварным шаром) 2004- без выреза бампера.

Новинки автомобильного рынка и их тест-драйв. Краш-тесты, фотографии. Лада Калина 1117 современный российский универсал, европейского дизайна. Очень приятная опция – электрические подъемники передних стекол.

…изменений в отдельные приказы региональной энергетической комиссии департамента цен и тарифов Краснодарского края следующие изменения: в пункте 2 приложения 1 слова Для потребителей в случае отсутствия дифференциации тарифов по схеме…

ОТ СОЛДАТА ДО ГЕНЕРАЛА. Москва Академия исторических наук. В томе представлены в авторской редакции воспоми- нания 50-ти ветеранов войны, проживающих в Краснодарском крае.

Нева универсал. Схема принципиальная электрическая. Е1 Болт заземления 1 Е2, Е3 Стартер 80С 220 В 2.

Исходниками схемы послужили SVG-файлы из KIA Shop Manual 2007 (если кто знает как преобразовать формат SWF (Adobe Flash), который используется в Shop Manual 2008 в PDF – поделитесь советом.

ТСУ для ВАЗ 1118 Калина седан, ВАЗ 1117 Калина универсал и ВАЗ 2190 Гранта (со сварным шаром) 2004- без выреза бампера.

Новинки автомобильного рынка и их тест-драйв. Краш-тесты, фотографии. Лада Калина 1117 современный российский универсал, европейского дизайна. Очень приятная опция – электрические подъемники передних стекол.

…изменений в отдельные приказы региональной энергетической комиссии департамента цен и тарифов Краснодарского края следующие изменения: в пункте 2 приложения 1 слова Для потребителей в случае отсутствия дифференциации тарифов по схеме…

ОТ СОЛДАТА ДО ГЕНЕРАЛА. Москва Академия исторических наук. В томе представлены в авторской редакции воспоми- нания 50-ти ветеранов войны, проживающих в Краснодарском крае.

Нева универсал. Схема принципиальная электрическая. Е1 Болт заземления 1 Е2, Е3 Стартер 80С 220 В 2.

Исходниками схемы послужили SVG-файлы из KIA Shop Manual 2007 (если кто знает как преобразовать формат SWF (Adobe Flash), который используется в Shop Manual 2008 в PDF – поделитесь советом. ..

Универсал 1701, изданный гетманом И. С. Мазепой (См. Мазепа ) , узаконил барщину; начались ограничения крестьянских переходов (запрещения ухода на слободы, вступления в казацкие полки и т.д.). Старшине принадлежали промышленные предприятия: селитренные, стеклянные, железоделательные.

В прошлом году АвтоСреда первой узнала о том, что АВТОВАЗ собирается выпустить электрокар Эллада, построенный на базе рестайлинговой Калины. quot;Рабочей тележкойquot; для новой quot;Элладыquot; станет LADA Kalina второго поколения в кузове quot;универсалquot;…

..

Универсал 1701, изданный гетманом И. С. Мазепой (См. Мазепа ) , узаконил барщину; начались ограничения крестьянских переходов (запрещения ухода на слободы, вступления в казацкие полки и т.д.). Старшине принадлежали промышленные предприятия: селитренные, стеклянные, железоделательные.

В прошлом году АвтоСреда первой узнала о том, что АВТОВАЗ собирается выпустить электрокар Эллада, построенный на базе рестайлинговой Калины. quot;Рабочей тележкойquot; для новой quot;Элладыquot; станет LADA Kalina второго поколения в кузове quot;универсалquot;…

Тепловоз ТЭМ18ДМ. Руководство по эксплуатации. Том 1, с приложением Книга 4 – Схема электрическая принципиальная ТЭМ18ДМ РЭ3

Настоящее руководство состоит из 3 томов (6 книг):Том 1:

Книга 1 – Техническое описание ТЭМ18ДМ РЭ

Книга 2 – Инструкция по эксплуатации ТЭМ18ДМ РЭ1

Книга 3 – Инструкция по техническому обслуживанию и текущему ремонту ТЭМ18ДМ РЭ2

Книга 4 – Схема электрическая принципиальная ТЭМ18ДМ РЭ3 (для удобства пользования издана отдельной книгой)

Том 2:

Книга 5 – Основное и вспомогательное комплектующее оборудование ТЭМ18ДМ РЭ4

Том 3:

Книга 6 – Вспомогательное комплектующее оборудование. Электрооборудование ТЭМ18ДМ РЭ5

Электрооборудование ТЭМ18ДМ РЭ5

Настоящее руководство разработано в соответствии с требованиями Единой системы конструкторской документации (ЕСКД) и объединяет в себе краткое тех-

ническое описание и инструкции по эксплуатации и техническому обслуживанию (РЭ) тепловоза ТЭМ18ДМ.

Техническое описание предназначено для изучения конструктивных особенностей тепловоза, содержит описание устройств и принцип действия отдельных

его узлов, агрегатов и схем, и также технические характеристики и другие сведения, необходимые для обеспечения наиболее полного использования технических

возможностей тепловоза.

В инструкции по эксплуатации изложены правила и порядок подготовки тепловоза к работе, правила эксплуатации, проверки технического состояния, воз-

можные неисправности и методы их устранения.

В инструкции по техническому обслуживанию указаны виды, периодичность, объем и порядок технического обслуживания и текущего ремонта тепловоза, до-

пускаемые в эксплуатации параметры основных деталей и узлов, а также меры безопасности обслуживающего персонала.

Требования настоящего руководства являются обязательными для всех работников эксплуатирующих организаций, связанных с эксплуатацией и техниче-

ским обслуживанием тепловоза.

Принципиальная электрическая схема – Справочник химика 21

Принципиальная электрическая схема установки электрофильтров 385 [c.385]

Конструкция рабочей ячейки 2, в которой помещается исследуемое вещество, обеспечивает благоприятные условия для создания равномерного температурного поля по ее длине. Конструкция узла заполнения 1 обеспечивает возможность продувки ячейки сжатым газом, промывку и создание определенного соотношения объемов жидкой и паровой фаз. Необходимая температура создается с помощью проволочного нагревателя, намотанного на корпус ячейки. Принципиальная электрическая схема тензометрического датчика давления 3 приведена на рис. 11. [c.28]

Рассмотрим принципиальную электрическую схему катодной защиты (рис. 31). Как следует из этой схемы, для наиболее простого случая катодной защиты общее сопротивление цепи мож ю представить как ряд последовательно соединенных отдельных сопротивлений Н1 и Я5 — сопротивления соединительных проводов Я2 — сопротивление растеканию тока с анодного заземления Н1 кг [c.126]

31). Как следует из этой схемы, для наиболее простого случая катодной защиты общее сопротивление цепи мож ю представить как ряд последовательно соединенных отдельных сопротивлений Н1 и Я5 — сопротивления соединительных проводов Я2 — сопротивление растеканию тока с анодного заземления Н1 кг [c.126]

Принципиальная электрическая схема устаповки электрофильтров [c.385]

На рис. 97, б показана принципиальная электрическая схема альфа-фазометра, в измерительном устройстве которого предусмотрены две цепи цепь регулирования силы тока в подвижной системе датчика Д и сигнальная, обеспечивающая индикацию момента отрыва. Обе цепи питаются от силового трансформатора Тр. Переменный ток выпрямляется при помощи выпрямителя 01 с фильтром, состоящим из дросселя Др и конденсатора большой емкости С1. Ток, питающий сигнальную цепь, выпрямляется выпрямителем Д2. [c.143]

Нагрузку потребителя можно разделить на осветительную и силовую, включающую потребление контрольно-измерительной аппаратурой, системами управления, автоматизацией.

Принципиальная электрическая схема РУ (6 кВ) силовых трансформаторов и электродвигателей установки НПЗ и НХЗ приведена на рис. 6. [c.24]

Принципиальная электрическая схема РУ (6 кВ) силовых трансформаторов и электродвигателей установки НПЗ и НХЗ приведена на рис. 6. [c.24]Рассмотрим принципиальную электрическую схему катодной зашиты (рис. 6.5). Для наиболее простого случая катодной защиты общее сопротивление цепи можно представить как ряд последовательно соединенных сопротивлений / 1 и / 5 – сопротивления соединительных проводов Й2 – сопротивление растеканию тока с анодного заземления в окружающий грунт ДЗ – сопротивление грунта между анодным заземлением и защищаемым сооружением Д4 – общее сопротивление току на пути грунт – металл защищаемого сооружения – точка дренажа. [c.128]

Принципиальная электрическая схема приведена в приложении I. Особенностью схемы, используемой в данной работе, является наличие двух кулонометров, параллельно соединенных между собой через переключатель. Кулонометры включают в цепь поочередно, с тем, чтобы можно было определять промежуточные количества электричества в ходе опыта, не прерывая электролиза. При использовании источника стабилизированного тока кулонометры не требуются. [c.187]

При использовании источника стабилизированного тока кулонометры не требуются. [c.187]

Pи . 10.4. Принципиальная электрическая схема аппарата питания тш я АИФ. [c.390]

Рис, 105. Принципиальная электрическая схема источника питания типа АТФ. [c.391]

Описание установки и принципиальная электрическая схема даются в инструкции, прилагаемой к прибору, [c.159]

Принципиальная электрическая схема полярографа. На рис. 62 [c.482]

На рис. 62 [c.482]Принципиальная электрическая схема управления — единая. Предусматривает управление приводами с двусторонней муфтой ограничения крутящего момента. [c.136]

На рис. 2 показана полная принципиальная электрическая схема автомата АВН-2. Электронный управляющий узел (слева) [c.253]

Рис. 2. Полная принципиальная электрическая схема автомата вспышки АВН-2. [c.255]

Предложите принципиальную электрическую схему, позволяющую вручную переходить с одного компрессора на другой для системы из 2 компрессоров с двухступенчатым задающим термостатом (используйте биполярный переключатель с двумя перебрасывающимися контактами). [c.171]

Принципиальная электрическая схема дефектоскопа показана на рис. 7.10. Схема содержит силовой трансформатор Тр.2, импульсный трансформатор Тр.1, накопительные конденсаторы С1 и С2, разрядные тиристоры Т1 и Т2, тиристоры ТЗ и Т4, диоды В1 и В2, выпрямитель ВП, собранный по мостовой схеме.

[c.419]

[c.419]Принципиальная электрическая схема БРР-1 изображена на рис. 25. Она состоит из искробезопасного источника питания и специальных реле. Последние выполнены на базе магнитоуправляемых контактов с катушками, которые шунтированы полупроводниковыми диодами. Источник искробезопасного питания — трансформатор Т с выпрямителем на диодах. Контактные датчики подключаются через разъем к искробезопас-ны.м входам блока. При замыкании входной цепи контактным [c.180]

Принципиальная электрическая схема датчика давления (рис. 76) состоит из трех каскадов стабилизированный источник питания, кварцевый генератор, резонансный каскад. Стабилизированный источник питания состоит из силового трансформатора Тр, выпрямительного моста, собранного на четырех диодах ДГЛ и двух стабилитронов СГЗС. Кварцевый генератор собран на двойном триоде 6Н1П по схеме сетка — катод. В схеме использован кварц с частотой собственных колебаний 500 кГц, что позволяет получить высокочастотные синусоидальные колебания высокой стабильности. Это в конечном счете повышает точность всего датчика. [c.133]

Это в конечном счете повышает точность всего датчика. [c.133]

При разработке принципиальных электрических схем гщя управления технологическим оборудованием возникает задача минимизации их структуры, которая однозначно сводится к минимизации соответствующей системы логических (булевых) функций при заданном алгоритме функционирования системы управления. До появления в 1967 году последовательностных уравнений и до разработки Квайном и Мак-Класки алгоритма минимизации булевых функций эта задача отличалась не только громоздкостью, но и отсутствием алгоритма ее адекватного рещения. Это обстоятельство породило большое количество методов синтеза и минимизации систем булевьгс функций, в том числе и с использованием ЭВМ. Однако все они не позволяют решить упомянутую задачу в приемлемом для инженерной практике виде, особенно при большом количестве аргументов булевых функций. [c.188]

В 1935 — 1936 1т, в Московском нефтяном институте им. акад. Губкина проф. Л. И. Слонимом и его ассистентами Ю. С. Бе1 леми-шевым и П. В. Валяв-ским (СБВ)1 был разработан новый электродегидратор для обезвоживания и обессоливания нефтей. Принципиальная электрическая схема электродегидратора приведена на фиг. 118. Здесь Т — повышаюпщй трансформатор, Р — ис-кровый разрядник, С — реактор, а в электрической схеме — конденсатор, Др — дроссель и А— амперметр. Важнейшим отличием этого электродегидратора от всех существующих является то, что в нем нефть не соприкасается с электродом высокого напряжения, а отгорожена от него диэлектриком. Таким образом исключается возможность коротких замыканий между электродами. Вторая его отличительная особенность та, что он работает с при- [c.206]

акад. Губкина проф. Л. И. Слонимом и его ассистентами Ю. С. Бе1 леми-шевым и П. В. Валяв-ским (СБВ)1 был разработан новый электродегидратор для обезвоживания и обессоливания нефтей. Принципиальная электрическая схема электродегидратора приведена на фиг. 118. Здесь Т — повышаюпщй трансформатор, Р — ис-кровый разрядник, С — реактор, а в электрической схеме — конденсатор, Др — дроссель и А— амперметр. Важнейшим отличием этого электродегидратора от всех существующих является то, что в нем нефть не соприкасается с электродом высокого напряжения, а отгорожена от него диэлектриком. Таким образом исключается возможность коротких замыканий между электродами. Вторая его отличительная особенность та, что он работает с при- [c.206] Принципиальная электрическая схема приставки приведена на рис. 3. Схема обеспечивает двойной перегиб пика и имеет два микропереключателя по концам шкалы самописца МЯ] и МП2. При первом зашкаливании включается микропереключатель МП1. Ка было описано выше, в этом случае срабатывает триггер на. реле Рг и P . Реле Р4 включается контактами 1Рг и самоблокиру-ется контактами ЗР4. Одновременно срабатывает реле Р5 (замыкаются контакты 4Р4), которое осуществляет переключение реохордов (ЗР5, 4Рб), а также реверс реверсивного двигателя РД-09 (1Р5, 2Р5). Контактами 5Р4 и 6Р4 осуществляется коммутация дополнительных сопротивлений, как это описано выше. [c.287]

реле Рг и P . Реле Р4 включается контактами 1Рг и самоблокиру-ется контактами ЗР4. Одновременно срабатывает реле Р5 (замыкаются контакты 4Р4), которое осуществляет переключение реохордов (ЗР5, 4Рб), а также реверс реверсивного двигателя РД-09 (1Р5, 2Р5). Контактами 5Р4 и 6Р4 осуществляется коммутация дополнительных сопротивлений, как это описано выше. [c.287]

Принципиальная электрическая схема для взрывозащищенного и нормального ис-шшнения отличается только выводами питания и электрических выходных сигналов [3]. [c.254]

Принципиальная электрическая схема для взрывозащищенного и нормального ис-шшнения отличается только выводами питания и электрических выходных сигналов [3]. [c.254]На рис. 5-26 показана принципиальная электрическая схема дифференциально-кондуктометричеок ого сигнализатора истощения Н-катионитных фильтров, разработанного ВТИ. Аналогичные схемы могут быть созданы с использованием аппаратов, разработанных ЮО ОРГРЭС и СКБ ПСА. [c.301]

Очистка газов от твердых или жидких частиц в электрофильтрах осуществляется под действием электростатических сил. Па рис. 76 представлена принципиальная электрическая схема электрического фильтра. Запыленный газ пропускают через электрическое поле постоянного тока. Коронирующие электроды 3 изолированы от земли, й к ним подведен постоянный ток высокого напряжения осадительные электроды 2 заземлены и подключены к полояштельному полюсу. В качестве осадительных электродов используются цилиндрические трубы и профилированные пластины, в качестве коронирующих-тонкая проволока. Под действием электрического поля постоянного тока, возникающего мезкду электродами, твердые ли жидкие частицы, проходящие через трубы газа, получают отрицательный заря д и движутся ь сторону осадительного электрода, осаждаются на нем и раз ряжаются. [c.221]

Под действием электрического поля постоянного тока, возникающего мезкду электродами, твердые ли жидкие частицы, проходящие через трубы газа, получают отрицательный заря д и движутся ь сторону осадительного электрода, осаждаются на нем и раз ряжаются. [c.221]

Принципиальная электрическая схема токарного станка 16К20

Для обеспечения высокой надежности в работе и обслуживания электрооборудования токарного станка 16К20 специалистами средней квалификации вся релейно – контакторная аппаратура и другие электроаппараты имеют простую конструкцию и испытаны многолетней эксплуатацией в различных условиях. Электроаппаратура (за исключением нескольких аппаратов) смонтирована в шкафу управления, расположенном с задней стороны станка.

Электрооборудование станка предназначено для подключения к трехфазной сети переменного тока с глухо заземленным или изолированным нейтральным проводом.

Основные параметры электрооборудования

Потребляемая мощность, кВт – 11

Напряжение сети, В – 380

Напряжение в цепи управления, В – 110

Напряжение в цепи местного освещения, В – 24

Частота, герц – 50

Принципиальная электрическая схема

Рис. 1. Схема электрическая принципиальная станка 16К20

1. Схема электрическая принципиальная станка 16К20

1* – Элементы при силовой цепи напряжением 220В и тропического исполнения могут отсутствовать

2* – Элементы для станков с гидросуппортом

Описание электрической схемы

Пуск электродвигателя главного привода M1 и гидростанции М4 осуществляется нажатием кнопки S4 (рис. 1), которая замыкает день катушки контактора К1, переводя его на самопитание. Останов электродвигателя главного привода Ml осуществляется нажатием кнопки S3.

Управление электродвигателем быстрого перемещения каретки и суппорта М2 осуществляется нажатием толчковой кнопки, встроенной в рукоятку фартука и воздействующей на конечный выключатель S8.

Пуск и останов электронасоса охлаждения М3 производятся переключателем S7.

Работа электронасоса сблокирована с электродвигателем главного привода M1, и включение его возможно только после замыкания контактов пускателя К1.

Для ограничения холостого хода электродвигателя главного привода в схеме имеется реле времени КЗ. В средних (нейтральных) положениях рукояток включения фрикционной муфты главного привода замыкается нормально закрытый контакт конечного выключателя S6 и включается реле времени К3, которое через установленную выдержку времени отключит своим контактом электродвигатель главного привода. Производить перестройку выдержки времени в рабочем состоянии реле категорически запрещается.

В средних (нейтральных) положениях рукояток включения фрикционной муфты главного привода замыкается нормально закрытый контакт конечного выключателя S6 и включается реле времени К3, которое через установленную выдержку времени отключит своим контактом электродвигатель главного привода. Производить перестройку выдержки времени в рабочем состоянии реле категорически запрещается.

Защита электродвигателей главного привода, привода быстрого перемещения каретки и суппорта, электронасоса охлаждения и трансформатора от токов коротких замыканий производится автоматическими выключателями и плавкими предохранителями.

Защита электродвигателей (кроме электродвигателя М2) от длительных перегрузок осуществляется тепловыми реле.

Нулевая защита электросхемы станка, предохраняющая от самопроизвольного включения электропривода при восстановлении подачи электроэнергии после внезапного ее отключения, осуществляется катушками магнитных пускателей.

Спецификация электрооборудования

- Р – Указатель нагрузки Э38022 на номинальный ток 20 А

- F1 – Выключатель автоматический АЕ-2043-12, 1PОO, расцепитель 32 А, с катушкой независимого расцепителя 110 В, 50 Гц, отсечка 12 (Ag—9,489 г)

- F2 – Автомат АЕ-20-33-10

- F3, F4 – Е2782—6/380 – плавкая вставка в предохранитель

- F5 – ТРН-40 – реле тепловое

- F6, F7 – ТРН-10 – реле тепловое

- Н1 – устройство предохранительное светосигнальное УПС-3

- Н2 – НКСО1Х100/П00-09 – лампа накаливания С24-25.

- Н3 – КМ24-90 – коммутаторная лампа накаливания

- К1 – ПАЕ-312 – магнитный пускатель

- К2 – ПМЕ-012 – магнитный пускатель

- КЗ – РВП72-3121-00У4 – реле времени пневматическое (Лимит работы электромотора главного движения без нагрузки)

- К4 – РПК-1—111 – пускатель двигателя

- М1 – Электродвигатель главного движения 4А132 М4, номинальной мощностью 11 кВт

- М2 – 4А71В4 – электродвигатель (ускоренное смещение суппорта)

- М3 – электронасос типа ПА-22 (подача эмульсии)

- М4 – 4А80А4УЗ – асинхронный электродвигатель

- S1 – ВПК-4240 – выключатель путевой (Дверца распределительного устройства)

- S2 – ПЕ-041 – поворотный переключатель управления (деблокирующий S1)

- S3 и S4 – ПКЕ-622-2 – пост управления кнопочный

- S5 – МП-1203 – микровыключатель

- S6 – ВПК-2111 – концевой выключатель нажимной

- S7 – ПЕ-011 – поворотный переключатель управления

- S8 – ВПК-2010 выключатель путевой нажимной

- Т – ТБСЗ-0,16 – трансформатор однофазный понижающий

Схема электрическая соединений

Рис. 2. Схема электрических соединений токарного станка 16К20

1. а – положение перемычек при подключении электродвигателей

2*. Для станков с гидросуппортом

Шкаф управления. Схема расположения электроаппаратов

Рис. 3. Шкаф управления токарно-винторезного станка 16К20

Органы управления

На лицевой стороне шкафа управления имеются следующие органы управления:

- рукоятка включения и отключения вводного автоматического выключателя с максимальным и дистанционным расцепителями;

- сигнальная лампа с линзой белого цвета, сигнализирующая о включенном состоянии вводного автоматического выключателя; переключатель для включения и отключения электронасоса охлаждения;

- указатель нагрузки, показывающий загрузку электродвигателя главного привода.

На каретке установлена кнопочная станция пуска и останова электродвигателя главного привода.

В рукоятке фартука встроена кнопка включения электродвигателя привода быстрых перемещений суппорта.

Рекомендации по техническому обслуживанию электрооборудования

Необходимо периодически проверять состояние пусковой и релейной аппаратуры. Все детали электроаппаратов должны быть очищены от пыли и грязи. При образовании на контактах нагара последний должен быть удален при помощи бархатного напильника или стеклянной бумаги. Во избежание появления ржавчины поверхность стыка сердечника с якорем пускателя нужно периодически смазывать машинным маслом с последующим обязательным протиранием сухой тряпкой (для предохранения от прилипания якоря к сердечнику).

При осмотрах релейной аппаратуры особое внимание следует обращать на надежность замыкания и размыкания контактных мостиков.

Периодичность технических осмотров электродвигателей устанавливается в зависимости от производственных условий, но не реже одного раза в два месяца.

При технических осмотрах проверяется состояние вводных проводов обмотки статора, производится очистка двигателей от загрязнения, контролируется надежность заземления и соединения вала с приводным механизмом. Периодичность профилактических ремонтов устанавливается в зависимости от производственных условий, но не реже одного раза в год.

Перед набивкой свежей смазки подшипники должны быть тщательно промыты бензином.

Камеру заполнить смазкой на 2/3 ее объема.

При профилактических ремонтах должна производиться разборка электродвигателей, очистка внутренних и наружных поверхностей и замена смазки подшипников. Замену смазки подшипников при нормальных условиях эксплуатации следует производить через 4000 ч работы, а при работе электродвигателя в пыльной и влажной средах — по мере необходимости.

Профилактический осмотр автоматических выключателей необходимо производить не реже одного раза в шесть месяцев, а также после каждого отключения при коротком замыкании, в том числе и повторном.

При осмотре нужно очистить выключатель от копоти и нагара металла, проверить затяжку винтов, целостность пружин и состояние контактов.

Шарниры механизма выключателя следует периодически (примерно через 2 000—3 000 включений) смазывать приборным вазелиновым маслом. Не следует проводить какую-либо регулировку выключателей в условиях эксплуатации. Она выполнена заводом-изготовителем.

электрическая принципиальная схема мельницы

принципиальная электрическая схема шаровой …

принципиальная электрическая схема шаровой мельницы. Дробильный комплекс включает в себя вибропитатель, щековую дробилку, роторную дробилку, виброгрохот, ленточные конвейеры, и главный …

принципиальная схема роликовой мельницы

схема электрическая принципиальная цементнои мельницы схема электрическая принципиальная . ибп принципиальная схема. . цементной мельницы детали Для продажи Получить цитату

Принципиальные электрические схемы …

2021-8-21 Упрощенная принципиальная электрическая схема регулятора температуры воздуха в помещении 204 работает постоянно, а калорифер включает в работу контакт регулятора А 1.1.

Принципиальные электрические схемы …

2020-7-12 Принципиальная электрическая схема холодильника — что это Принципиальная схема, принципиальная электрическая схема — графическое изображение (модель), служащее для передачи с помощью условных графических и …

принципиальная схема твч

Схема генератор 2108 на 2106 Принципиальная схема сварочного аппарата etalon mma также схема arc tig электрическая схема wmm принципиальная электрическая схема сварочного автомата а 1406.

Электрические схемы холодильников Beko

2020-7-17 Хотите разбираться лучше других? Принципиальные электрические схемы холодильников Indesit – Принципиальная электрическая схема холодильника Indesit B16 NF.025, C 132 NFG.016, C 138 NFG.016 L – фаза, N – нейтраль, Th2 – терморегулятор, Rh2 …

Схемы электрические. Типы схем / Хабр

2019-5-12 Схема электрическая принципиальная (полная) (Э3) На принципиальной схеме изображают все электрические элементы или устройства, необходимые для осуществления и контроля в изделии установленных электрических …

Принципиальная электрическая схема …

Принципиальная электрическая схема кран- балки типа НК управлением с пола (фиг. 66) включает три схемы реверсивного (кнопочного) управления двигателями грузоподъемного механизма и механизмов передвижения кран-балки …

Принципиальная схема. Схема электрическая …

Кроме того, схема электрическая принципиальная является исходным заданием для конструктора. По принципиальной схеме и перечню элементов он разрабатывает конструкцию печатной

Принципиальная электрическая схема гост …

Принципиальная электрическая схема представляет собой графическую модель устройства, выполненную при помощи условных значков и пиктограмм, обозначающих составляющие и соединительные элементы, а также дающую …

Принципиальные электрические схемы …

2020-7-12 Принципиальная электрическая схема холодильника — что это Принципиальная схема, принципиальная электрическая схема — графическое изображение (модель), служащее для передачи с помощью условных графических и …

Схема электрическая

В составе чертежи: схема монтажная, электрическая, принципиальная, монтажная принципиальная с узлами схема. Насосы / Электрические схемы проекты

Электрические схемы холодильников Beko

2020-7-17 Хотите разбираться лучше других? Принципиальные электрические схемы холодильников Indesit – Принципиальная электрическая схема холодильника Indesit B16 NF.025, C 132 NFG.016, C 138 NFG.016 L – фаза, N – нейтраль, Th2 – терморегулятор, Rh2 …

Комбайн КЗС-1218. Схемы электрические …

2020-9-12 Рисунок Б.1 – Схема электрическая принципиальная комбайна (лист 3 а) Рисунок Б.1 – Схема электрическая принципиальная комбайна (лист 4)

Устройство и принципиальная электрическая …

2020-3-2 Когда оба блока кондиционера установлены, необходимо провести электрические провода и подключить их в сеть, руководством для этого служит схема электрическая принципиальная

Принципиальная схема — Википедия

2021-8-10 Виды принципиальных схем По ГОСТ 2.701 принципиальным схемам присваивается буква, детализирующая вид схемы и цифра 3 — принципиальная схема, например, Э3 — принципиальная электрическая схема.

Принципиальная схема. Схема электрическая …

Кроме того, схема электрическая принципиальная является исходным заданием для конструктора. По принципиальной схеме и перечню элементов он разрабатывает конструкцию печатной платы и изделия в целом.

«РАДИОЛА ВЕГА-003 СТЕРЕО схема электрическая …

2021-8-24 Схема электрическая принципиальная телевизионных приёмников “Рассвет 40тб-301” 300.00 р. Курган договорная

Принципиальная схема электропечи Мечта

Принципиальная схема электропечи Мечта – Инструкция устройство размер “Настольная плита 150, 12 kB”. Электрическая плита 142, 82 kB – Техническое описание и схема

электрическая схема daewoo sens – racholubti1982’s blog

2017-6-12 Схема электрическая системы управления двигателем Микас 7.6 автомобиля AVTOZAZ-DAEWOO Sent: с кислородным датчиком (Евро-2*). Daewoo Схема электрическая принципиальная соединения приборов.

Схемы электрические кранов (бесплатные)

Схема электрическая принципиальная Просмотров: 11249 Кран БКСМ-5-5. Схема электрическая принципиальная Просмотров: 12809 Кран башенный КБ-100.0. Схема электрическая принципиальная

Принципиальная схема источники питания …

5 принципиальная электрическая схема источника питания принципиальные схемы источника бесперебойного питания ибп back ups 250i 40i 600i.

Схема электрическая электропривода – Чертежи …

2011-5-9 Состав: Схема электрическая принципиальная. Софт: AutoCAD, DWG. Файлы: Каталог / Машиностроение и механика / Подъемно транспортные установки (ПТУ) / Краны / Схема электрическая электропривода …

«Схема электрическая принципиальная …

2021-1-15 Инструкция паспорт схема Телевизор Кварц 40ТБ-306. 100.00 р. Железногорск 80.00 р. Окончание торгов: 08/02 08:08. Продавец: skait1 ( 3014 ) Схема электрическая принципиальная телевизора “ПТ-50-III-2”. 150.00 р.

Схема электрическая принципиальная …

2019-8-17 Скачать: Схема электрическая принципиальная для пассажирского лифта грузоподъемностью 400 …

техническая характеристика планетарной …

скачать чертеж валковой дробилки со спецификацией. 4 мар 2013,Формат файлов: схема планетарной шаровой мельницы аго 2 описание центробежной мельницы планетарно центробежная мельницы.

Принципиальная Электрическая схема тельфера …

Предназначение контактора «Принципиальная электрическая схема кран-балки». Таль (тельфер) включает в себя следующие элементы. О том, как подключить кран-балку с 6 кнопками, можно узнать из схемы, прилагаемой к крану …

Холодильник Стинол Схема Электрическая …

2021-7-27 Принципиальная электрическая схема Стинол 107 Это мог быть заклинивший механизм двигателя. Отделить сборку от испарителя без специальных инструментов и

электрическая схема daewoo sens – racholubti1982’s blog

2017-6-12 Схема электрическая системы управления двигателем Микас 7.6 автомобиля AVTOZAZ-DAEWOO Sent: с кислородным датчиком (Евро-2*). Daewoo Схема электрическая принципиальная соединения приборов.

Принципиальная электрическая схема гост …

Принципиальная электрическая схема представляет собой графическую модель устройства, выполненную при помощи условных значков и пиктограмм, обозначающих составляющие и соединительные элементы, а также дающую …

Дом | Toshiba International Corporation

Подразделение Motors & Drives предлагает полный спектр двигателей низкого и среднего напряжения и приводов с регулируемой скоростью. Эти продукты, отличающиеся качеством, производительностью и долговечностью, могут быть адаптированы для самых требовательных приложений.

Щелкните здесь, чтобы увидеть все наши двигатели и приводы>

Подразделение силовой электроники предлагает решения по кондиционированию и защите питания, в частности системы бесперебойного питания, быстро перезаряжаемые батареи (SCiB ® ) и предприятий по кондиционированию электроэнергии.Продукция TIC Power Electronics славится своей надежностью и эффективностью и идеально подходит для таких ключевых рынков, как центры обработки данных, здравоохранение и промышленность. Клиенты получают выгоду от компактного дизайна, обширных гарантийных планов, а также круглосуточного обслуживания и поддержки.

Щелкните здесь, чтобы увидеть все наши продукты для силовой электроники>

Подразделение передачи и распределения со штаб-квартирой в Хьюстоне является частью мирового лидера корпорации Toshiba в области поставки интегрированных решений для передачи, распределения и интеллектуальных сообществ.Как один из крупнейших в мире производителей современного передающего и распределительного оборудования, Toshiba уже более века поставляет на мировой рынок высоконадежные и инновационные продукты. Подразделение передачи и распределения TIC обслуживает рынок Северной Америки, предлагая продукцию, которая удовлетворяет рыночный спрос на большую емкость, компактный дизайн и экологически безопасные решения, обеспечивающие впечатляющие показатели эффективности и отличные результаты.

Щелкните здесь, чтобы увидеть все наши продукты для передачи и распределения>

Доступные системы социальной инфраструктуры могут быть дополнительно настроены путем добавления контрольно-измерительных приборов, систем управления процессами или программируемых логических элементов управления.Кроме того, TIC предлагает решения для транспортных систем, безопасности и автоматизации, а также двигатели для гибридных электромобилей.

С 2011 года Toshiba International Corporation производит высокопроизводительные приводные двигатели для гибридных электромобилей (HEV). Современный завод HEV занимает площадь 45 000 квадратных футов и производит более 130 000 двигателей в год. Завод, на котором работают более 100 человек, поставляет двигатели и генераторы для гибридных электромобилей, включая модели Ford Fusion Hybrid и C-Max.

Нажмите здесь, чтобы увидеть все наши автомобильные системы>

% PDF-1.4 % 263 0 объект > эндобдж xref 263 71 0000000016 00000 н. 0000002998 00000 н. 0000003157 00000 н. 0000003193 00000 п. 0000003833 00000 н. 0000003860 00000 н. 0000003999 00000 н. 0000004266 00000 н. 0000004612 00000 н. 0000004832 00000 н. 0000005012 00000 н. 0000005124 00000 н. 0000005170 00000 н. 0000005284 00000 н. 0000006299 00000 н. 0000006622 00000 н. 0000006959 00000 п. 0000007339 00000 н. 0000007740 00000 н. 0000008065 00000 н. 0000009100 00000 н. 0000009207 00000 н. 0000009905 00000 н. 0000010055 00000 п. 0000010712 00000 п. 0000011914 00000 п. 0000012196 00000 п. 0000012793 00000 п. 0000013317 00000 п. 0000013661 00000 п. 0000014271 00000 п. 0000014585 00000 п. 0000015471 00000 п. 0000015868 00000 п. 0000015895 00000 п. 0000016028 00000 п. 0000016650 00000 п. 0000017553 00000 п. 0000017642 00000 п. 0000018169 00000 п. 0000018366 00000 п. 0000018751 00000 п. 0000019044 00000 п. 0000019741 00000 п. 0000020444 00000 п. 0000022564 00000 н. 0000023718 00000 п. 0000025316 00000 п. 0000025584 00000 п. 0000031701 00000 п. 0000032098 00000 п. 0000032499 00000 н. 0000032909 00000 н. 0000033166 00000 п. 0000033498 00000 п. 0000035107 00000 п. 0000035144 00000 п. 0000037793 00000 п. 0000038055 00000 п. 0000038125 00000 п. 0000044902 00000 п. 0000045003 00000 п. 0000050594 00000 п. 0000055701 00000 п. 0000056384 00000 п. 0000056439 00000 п. 0000056809 00000 п. 0000056831 00000 п. 0000056853 00000 п. 0000060394 00000 п. 0000001716 00000 н. трейлер ] / Назад 284409 >> startxref 0 %% EOF 333 0 объект > поток h ޔ U] lTIu% MnF & e “K: T” Mӭ2c6hmC4HH F% ^ @ c’Mt / R |; ߹7 A “”! 6eA8 “9A -: YfHUf) | $ n ⣦] gL * d͘} 9 w 噉 N ߙ zFYM * LH9suPk: aiA “, J $ * |

I9k9m и BGh’2p $ & x [L}!) / “Y0 ݘ S”) ўtG # @ $ ul ^ 2, N1LV 2; 9ŝ ^ R

% PDF-1.4 % 687 0 объект > эндобдж xref 687 53 0000000016 00000 н. 0000002235 00000 н. 0000002308 00000 н. 0000002447 00000 н. 0000002495 00000 н. 0000002903 00000 н. 0000009748 00000 н. 0000009905 00000 н. 0000010072 00000 п. 0000010234 00000 п. 0000010406 00000 п. 0000010565 00000 п. 0000010723 00000 п. 0000010882 00000 п. 0000011100 00000 п. 0000011344 00000 п. 0000011428 00000 п. 0000011719 00000 п. 0000012463 00000 п. 0000012717 00000 п. 0000012830 00000 н. 0000013237 00000 п. 0000013533 00000 п. 0000013782 00000 п. 0000013873 00000 п. 0000014207 00000 п. 0000014800 00000 п. 0000015059 00000 п. 0000015162 00000 п. 0000015537 00000 п. 0000015748 00000 п. 0000015963 00000 п. 0000016066 00000 п. 0000016379 00000 п. 0000016703 00000 п. 0000016947 00000 п. 0000017045 00000 п. 0000017400 00000 п. 0000017657 00000 п. 0000017872 00000 п. 0000018011 00000 п. 0000018424 00000 п. 0000018487 00000 п. 0000018967 00000 п. 0000019447 00000 п. 0000019927 00000 п. 0000033706 00000 п. 0000082754 00000 п. 0000098086 00000 п. 0000133792 00000 н. 0000153726 00000 н. 0000158612 00000 н. 0000001726 00000 н. трейлер ] / Зашифровать 689 0 R >> startxref 0 %% EOF 739 0 объект > транслировать * G [ę59uQd $ e *) Fϫ6N @ * 4_l: + 3co * H> 鼨 -s / 8hA> G> + @ I`? /.; 57> H CGu; = | mV | K + ۜ Pwa @ & ʭN2- ק- uwvx? EV ~ Ò> KRx ֦ T-dhlk`?, TqxpG2d> {m # E [O * T.uok> zO, hYBc`J $ jjhW fp @ tiXe $ l #? & Ido̩ҶXeb5N @ ~ 5 конечный поток эндобдж 688 0 объект > эндобдж 689 0 объект `77Q \ b! Wgm-Zv>) / P -1324 / R 3 / U (M {a9Yd $ x S

Архитектура центра обработки данных Cisco Spine-and-Leaf: обзор проекта Официальный документ

Эволюция центра обработки данных

Центр обработки данных лежит в основе современных программных технологий и играет важную роль в расширении возможностей предприятий.Традиционный центр обработки данных использует трехуровневую архитектуру, в которой серверы сегментированы на блоки в зависимости от местоположения, как показано на рисунке 1.

Рисунок 1.

Традиционная трехуровневая конструкция ЦОД

Архитектура состоит из основных маршрутизаторов, маршрутизаторов агрегации (иногда называемых маршрутизаторами распределения) и коммутаторов доступа. Между маршрутизаторами агрегации и коммутаторами доступа протокол Spanning Tree Protocol используется для построения топологии без петель для части сети уровня 2.Протокол Spanning Tree Protocol дает несколько преимуществ: он прост и представляет собой технологию plug-and-play, требующую небольшой настройки. Виртуальные локальные сети расширяются внутри каждого модуля, и серверы могут свободно перемещаться внутри модуля без необходимости изменения IP-адреса и конфигурации шлюза по умолчанию. Однако протокол связующего дерева не может использовать параллельные пути пересылки и всегда блокирует избыточные пути в VLAN.

В 2010 году Cisco представила технологию виртуального порта-канала (vPC) для преодоления ограничений протокола Spanning Tree.vPC устраняет заблокированные порты связующего дерева, обеспечивает активный-активный восходящий канал от коммутаторов доступа к агрегационным маршрутизаторам и полностью использует доступную полосу пропускания, как показано на рисунке 2. С технологией vPC протокол связующего дерева по-прежнему используется в качестве безотказный механизм.

ТехнологияvPC хорошо работает в среде относительно небольшого центра обработки данных, в котором большая часть трафика состоит из связи между клиентами и серверами в северном и южном направлениях.

Фигура 2.

Проектирование центра обработки данных с использованием vPC

С 2003 года, с внедрением виртуальной технологии, вычислительные, сетевые ресурсы и ресурсы хранения, которые были разделены на модули на уровне 2 в трехуровневом проекте центра обработки данных, могут быть объединены в пул. Эта революционная технология создала потребность в более крупном домене уровня 2, от уровня доступа до уровня ядра, как показано на рисунке 3.

Рисунок 3.

Проект центра обработки данных с расширенным доменом уровня 3

С сегментами уровня 2, расширенными на все модули, администратор центра обработки данных может создать центральный, более гибкий пул ресурсов, который можно перераспределять в зависимости от потребностей.Серверы виртуализированы в наборы виртуальных машин, которые могут свободно перемещаться с сервера на сервер без необходимости изменения их рабочих параметров.

С виртуализированными серверами приложения все чаще развертываются распределенным образом, что приводит к увеличению трафика с востока на запад. Этот трафик необходимо обрабатывать эффективно с низкой и предсказуемой задержкой. Однако vPC может обеспечить только два активных параллельных восходящих канала, поэтому пропускная способность становится узким местом в трехуровневой архитектуре центра обработки данных.Еще одна проблема трехуровневой архитектуры заключается в том, что задержка между серверами зависит от используемого пути трафика.

Для преодоления этих ограничений был разработан новый дизайн центра обработки данных, названный «хребтово-оконная архитектура сети Clos». Доказано, что эта архитектура обеспечивает высокую пропускную способность, малую задержку и неблокирующую связь между серверами.

Хребетно-листовая архитектура

На рис. 4 показана типичная двухуровневая топология «шип и лист».

Рисунок 4.

Типовая топология шип-лист

В этой двухуровневой архитектуре Clos каждый коммутатор нижнего уровня (конечный уровень) подключен к каждому из коммутаторов верхнего уровня (уровень позвоночника) в топологии с полной сеткой. Конечный уровень состоит из коммутаторов доступа, которые подключаются к таким устройствам, как серверы. Слой позвоночника является основой сети и отвечает за соединение всех листовых коммутаторов. Каждый листовой переключатель соединяется с каждым переключателем корешка в ткани.Путь выбирается случайным образом, чтобы нагрузка трафика равномерно распределялась между коммутаторами верхнего уровня. Если один из коммутаторов верхнего уровня выйдет из строя, это лишь незначительно снизит производительность всего центра обработки данных.

Если происходит превышение лимита подписки для канала (т. Е. Если генерируется больше трафика, чем может быть агрегировано на активном канале за один раз), процесс увеличения емкости прост. Может быть добавлен дополнительный коммутатор позвоночника, а восходящие каналы могут быть расширены до каждого конечного коммутатора, что приведет к увеличению межуровневой полосы пропускания и сокращению избыточной подписки.Если емкость порта устройства становится проблемой, можно добавить новый конечный коммутатор, подключив его к каждому коммутатору позвоночника и добавив конфигурацию сети к коммутатору. Простота расширения оптимизирует процесс масштабирования сети ИТ-отделом. Если не происходит переподписки между коммутаторами нижнего уровня и их восходящими линиями связи, то может быть достигнута неблокирующая архитектура.

В архитектуре «позвоночник и лист», независимо от того, к какому конечному коммутатору подключен сервер, его трафик всегда должен проходить через одинаковое количество устройств, чтобы добраться до другого сервера (если другой сервер не находится на том же листе) .Этот подход сохраняет задержку на предсказуемом уровне, потому что полезной нагрузке нужно только перейти к позвоночному коммутатору и другому конечному коммутатору, чтобы достичь места назначения.

Оверлейная сеть

Современные виртуализированные фабрики центров обработки данных должны соответствовать определенным требованиям для ускорения развертывания приложений и поддержки потребностей DevOps. Например, фабрики должны поддерживать масштабирование таблиц пересылки, масштабирование сегментов сети, расширение сегмента уровня 2, мобильность виртуальных устройств, оптимизацию пути пересылки и виртуализированные сети для поддержки нескольких арендаторов в общей физической инфраструктуре.

Хотя концепция сетевого оверлея не нова, интерес к сетевым оверлеям возрос в последние несколько лет из-за их потенциала для удовлетворения некоторых из этих требований. Интерес к оверлейным сетям также увеличился с появлением новых форматов кадров инкапсуляции, специально разработанных для центров обработки данных. Эти форматы включают в себя виртуальную расширяемую локальную сеть (VXLAN), виртуализацию сети с использованием общей инкапсуляции маршрутизации (NVGRE), прозрачное соединение множества ссылок (TRILL) и протокол разделения местоположения / идентификатора (LISP).Наложения сети – это виртуальные сети взаимосвязанных узлов, которые совместно используют базовую физическую сеть, что позволяет развертывать приложения, требующие определенных сетевых топологий, без необходимости изменения базовой сети (рисунок 5).

Рисунок 5.

Концепция наложения сети

Преимущества оверлея сетевой виртуализации включают следующее:

● Оптимизированные функции устройства: оверлейные сети позволяют разделить (и специализировать) функции устройства в зависимости от того, где устройство используется в сети.Пограничное или оконечное устройство может оптимизировать свои функции и все соответствующие протоколы на основе информации о конечном состоянии и масштабирования, а центральное или оконечное устройство может оптимизировать свои функции и протоколы на основе обновлений состояния канала, оптимизируя с помощью быстрой конвергенции.

● Масштабируемость и гибкость фабрики. Технологии наложения позволяют масштабировать сеть, сосредотачиваясь на масштабировании на граничных устройствах наложения сети. Благодаря наложениям, используемым на краю фабрики, позвоночные и базовые устройства освобождаются от необходимости добавлять информацию о конечных хостах в свои таблицы пересылки.

● Перекрывающаяся адресация. Большинство технологий наложения, используемых в центре обработки данных, позволяют идентификаторам виртуальной сети однозначно определять и идентифицировать отдельные частные сети. Эта область видимости допускает возможное совпадение MAC- и IP-адресов между арендаторами. Инкапсуляция наложения также позволяет администрировать адресное пространство базовой инфраструктуры отдельно от адресного пространства арендатора.

В этом документе рассматриваются несколько архитектурных проектов, которые Cisco предлагала в недавнем прошлом, а также текущие проекты, а также те, которые Cisco планирует предложить в ближайшем будущем для удовлетворения требований фабрики в современном виртуализированном центре обработки данных:

● Cisco ® спинно-листовая сеть FabricPath

● Магистральная сеть Cisco VXLAN с поддержкой потоков и обучения

● Многопротокольный протокол пограничного шлюза Cisco VXLAN (MP-BGP), виртуальная частная сеть Ethernet (EVPN), магистральная и оконечная сеть

● Массивно масштабируемый центр обработки данных Cisco (MSDC) уровня 3, магистральная и оконечная сеть

В каждом разделе описаны наиболее важные технологические компоненты (инкапсуляция; обнаружение и распределение конечных хостов; широковещательная передача, пересылка неизвестного одноадресного и многоадресного трафика; базовая и наложенная плоскость управления, поддержка многопользовательского режима и т. Д.), общие конструкции и соображения по проектированию (шлюз уровня 3 и т. д.) на момент написания этой статьи.

Хвостовик-листовая сеть Cisco FabricPath

Cisco представила технологию FabricPath в 2010 году. FabricPath предоставляет новые возможности и варианты дизайна, которые позволяют операторам сетей создавать фабрики Ethernet, которые увеличивают доступность полосы пропускания, обеспечивают гибкость конструкции, а также упрощают и сокращают затраты на развертывание и эксплуатацию сети и приложений. Типичная сеть FabricPath использует архитектуру позвоночника и листа.

ТехнологияFabricPath использует многие из лучших характеристик традиционных технологий Layer 2 и Layer 3. Он сохраняет простую конфигурацию, модель развертывания plug-and-play среды уровня 2. Он также представляет протокол уровня управления под названием FabricPath Intermediate System to Intermediate System (IS-IS). Этот протокол маршрутизации Shortest-Path First (SPF) используется для определения достижимости и выбора наилучшего пути или путей к любому заданному коммутатору FabricPath назначения в сети FabricPath.Результатом являются повышенная стабильность и масштабируемость, быстрая сходимость и возможность использования нескольких параллельных путей, типичных для маршрутизируемой среды уровня 3.

Формат инкапсуляции и соответствие стандартам

Магистральная сеть FabricPath является собственностью Cisco, но основана на стандарте TRILL. Он использует инкапсуляцию кадра MAC-in-MAC FabricPath.

Подложка сети

Магистральная и оконечная сеть FabricPath использует инкапсуляцию кадров MAC-in-MAC уровня 2 FabricPath и использует FabricPath IS-IS для плоскости управления в базовой сети.Каждый переключатель FabricPath идентифицируется идентификатором переключателя FabricPath. Уровень управления FabricPath IS-IS создает информацию о доступности о том, как достичь других коммутаторов FabricPath.

Оверлейная сеть

FabricPath не имеет оверлейной плоскости управления для оверлейной сети. Информация о конечных узлах в оверлейной сети изучается с помощью механизма распространения и обучения с диалоговым обучением.

Широковещательный и неизвестный одноадресный трафик

Для сети FabricPath плоскость управления FabricPath IS-IS по умолчанию создает два дерева с несколькими назначениями, которые переносят широковещательный трафик, неизвестный одноадресный трафик и многоадресный трафик через сеть FabricPath.Широковещательный и неизвестный одноадресный трафик в FabricPath лавинно передается на все граничные порты FabricPath в VLAN или широковещательном домене.

Обнаружение хоста и доступность

Для получения информации о доступности конечного хоста коммутаторы FabricPath полагаются на начальную лавинную маршрутизацию трафика на уровне данных. По мере увеличения количества хостов в широковещательном домене негативные эффекты лавинных пакетов становятся более выраженными. При проектировании сети FabricPath необходимо тщательно учитывать влияние широковещательного и неизвестного одноадресного трафика.Существуют функции, такие как функция FabricPath Multitopology, которые помогают ограничить лавинную адресацию трафика в подсекции сети FabricPath.

Многоадресный трафик

Для сети FabricPath плоскость управления FabricPath IS-IS по умолчанию создает два дерева с несколькими назначениями, которые переносят широковещательный трафик, неизвестный одноадресный трафик и многоадресный трафик через сеть FabricPath. Многоадресный IP-трафик по умолчанию ограничивается только теми граничными портами FabricPath, к которым подключен заинтересованный приемник многоадресной рассылки или маршрутизатор многоадресной рассылки и которые используют отслеживание протокола IGMP.Для многоадресного трафика уровня 2 трафик, входящий в коммутатор FabricPath, хешируется в дерево с несколькими назначениями для пересылки. Для многоадресного IP-трафика уровня 3 трафик должен пересылаться с помощью многоадресной рассылки уровня 3 с использованием протокола независимой многоадресной рассылки (PIM). После того, как трафик направляется в целевую VLAN, он пересылается с использованием многопунктового дерева в целевой VLAN.

Функция маршрутизации уровня 3

FabricPath – это технология сетевой структуры уровня 2, которая позволяет легко масштабировать пропускную способность сети, просто добавляя дополнительные узловые и оконечные узлы на уровне 2.Но большинство сетей не являются чистыми сетями уровня 2. Серверы могут взаимодействовать с другими серверами в разных подсетях или разговаривать с клиентами в удаленных филиалах через глобальную сеть или Интернет. Этот трафик должен маршрутизироваться функцией уровня 3, включенной на коммутаторах FabricPath (шлюзы по умолчанию и пограничные коммутаторы).

Размещение функции уровня 3 в сети FabricPath должно быть тщательно продумано. Доступны два основных варианта дизайна: внутренняя и внешняя трассировка на корешке границы и внутренняя и внешняя трассировка на пограничном листе.Обе схемы обеспечивают централизованную маршрутизацию: то есть функции маршрутизации уровня 3 централизованы на определенных коммутаторах.

Внутренняя и внешняя разводка на границе корешка

Как показано в схеме внутренней и внешней маршрутизации на границе раздела на рисунке 6, коммутатор позвоночника функционирует как граница уровня 2 и уровня 3 и шлюз подсети сервера. Коммутаторы Spine выполняют переключение кадров FabricPath внутри VLAN. Виртуальные интерфейсы коммутатора (SVI) на магистральном коммутаторе выполняют маршрутизацию между VLAN для внутреннего трафика с востока на запад и обмениваются информацией о смежности маршрутизации с маршрутизируемыми восходящими линиями уровня 3 для маршрутизации внешнего трафика с севера на юг.Маршрутизируемый трафик должен пройти только один переход, чтобы достичь шлюза по умолчанию на коммутаторах позвоночника, которые будут маршрутизироваться.

ТехнологияFabricPath в настоящее время поддерживает до четырех шлюзов FabricPath anycast. Если сеть позвоночника и листа имеет более четырех коммутаторов позвоночника, границу уровня 2 и уровня 3 необходимо распределить по коммутаторам позвоночника. Кроме того, с включенными SVI на спинном переключателе, позвоночный коммутатор отключает диалоговое обучение и изучает MAC-адрес в соответствующей подсети.Вам необходимо учитывать масштабирование MAC-адресов, чтобы избежать превышения пределов масштабируемости вашего оборудования.

Рисунок 6.

Внутренняя и внешняя разводка на границе корешка

Внутренняя и внешняя трассировка на пограничном полотне

Как показано в схеме внутренней и внешней маршрутизации на граничном листе на рисунке 7, основной коммутатор функционирует как коммутатор FabricPath уровня 2 и выполняет только коммутацию кадров FabricPath внутри VLAN.Он не узнает MAC-адреса хоста. Функция Layer 2 и Layer 3 включена на некоторых листовых переключателях FabricPath, называемых пограничными листовыми переключателями. SVI на граничных конечных коммутаторах выполняют маршрутизацию между VLAN для внутреннего трафика с востока на запад и обмениваются смежностью маршрутизации с маршрутизируемыми восходящими линиями уровня 3 для маршрутизации внешнего трафика с севера на юг.

Но маршрутизируемый трафик должен пройти два перехода: от листа к позвоночнику, а затем к шлюзу по умолчанию на граничном листе, который будет маршрутизироваться. В проекте может быть задействовано до четырех шлюзов FabricPath anycast с маршрутизацией на граничном листе.Вам необходимо учитывать масштаб MAC-адресов, чтобы избежать превышения предела масштабируемости на пограничном листовом коммутаторе.

Рисунок 7.

Внутренняя и внешняя трассировка на пограничном полотне

Мультиарендность

Магистральная и оконечная сеть FabricPath поддерживает мультиарендность уровня 2 с функцией сегмента сети VXLAN (VN) (рисунок 8). Функция VN-сегмента обеспечивает новый способ маркировки пакетов на проводе, заменяя традиционный IEEE 802.Тег 1Q VLAN. Эта функция использует 24-битное увеличенное пространство имен. Граничные каналы клиента (доступ и магистраль) несут традиционные тегированные и немаркированные кадры VLAN. Это граничные порты VN-сегмента.

Ссылки FabricPath (режим порта коммутатора: Fabricpath) переносят кадры с тегами VN-сегмента для сетей VLAN, для которых определены идентификаторы сети VXLAN (VNI). Это основные порты сегмента VN. Для поддержки мультиарендности одни и те же сети VLAN можно повторно использовать на разных конечных коммутаторах FabricPath, а тегированные кадры IEEE 802.1Q сопоставляются с определенными сегментами VN.VN-сегменты используются для обеспечения изоляции на уровне 2 для каждого клиента. VLAN имеет локальное значение на оконечном коммутаторе FabricPath, а сегменты VN имеют глобальное значение в сети FabricPath. На каждом листовом коммутаторе FabricPath сеть поддерживает 4096 пространств VLAN, но во всей сети FabricPath она может поддерживать до 16 миллионов VN-сегментов, по крайней мере теоретически.

Рисунок 8.

Пример мультиарендности уровня 2 с функцией FabricPath VN-Segment

Магистральная и оконечная сеть FabricPath также поддерживает мультиарендность уровня 3 с использованием облегченной виртуальной маршрутизации и пересылки (VRF-lite), как показано на рисунке 9.Сеть FabricPath является сетью уровня 2, а SVI уровня 3 размещаются поверх коммутатора Layer 2 FabricPath. С VRF-lite количество виртуальных локальных сетей, поддерживаемых в сети FabricPath, составляет 4096.

Рисунок 9.

Пример мультиарендности уровня 3 с VRF-lite

Краткое описание сети Cisco FabricPath Spine-and-Leaf

Магистральная и оконечная сеть FabricPath является собственностью Cisco, но это зрелая технология, которая получила широкое распространение.Он обеспечивает простую, гибкую и стабильную сеть с хорошей масштабируемостью и характеристиками быстрой конвергенции, а также может использовать несколько параллельных путей на уровне 2. Но сеть FabricPath представляет собой технологию уровня 2, основанную на лавинной рассылке и обучении. Его протокол уровня управления FabricPath IS-IS разработан для определения информации о доступности идентификатора коммутатора FabricPath. Чтобы узнать информацию о доступности конечного хоста, коммутаторы FabricPath полагаются на начальную лавинную рассылку трафика на уровне данных. По мере увеличения числа хостов в широковещательном домене негативные эффекты лавинных пакетов становятся более выраженными.Функция уровня 3 возложена на сеть уровня 2. В общих проектах уровня 3 используется централизованная маршрутизация: то есть функция маршрутизации уровня 3 централизована на определенных коммутаторах (коммутаторах позвоночника или пограничных конечных коммутаторах). Сеть FabricPath поддерживает до четырех шлюзов Anycast для внутренней маршрутизации VLAN.

В Таблице 1 приведены характеристики спинно-листовой сети FabricPath.

Таблица 1. Характеристики сети Cisco FabricPath

Товар | Описание |

Транспортная среда | Уровень 1 |

Инкапсуляция | FabricPath (инкапсуляция кадра MAC-in-MAC) |

Уникальный идентификатор узла | Идентификатор коммутатора FabricPath |

Обнаружение конечного узла | Потоп и узнай |

Бесшумное обнаружение хоста | Есть |

Доступность и распределение конечных узлов | Наводнение и обучение плюс диалоговое обучение |

Широковещательный и неизвестный одноадресный трафик | Flood by FabricPath IS-IS дерево множественных назначений |

Контрольная плоскость подложки | FabricPath IS-IS |

Плоскость управления наложением | – |

Функция маршрутизации уровня 3 | ● Внутренняя и внешняя маршрутизация на границе корешка. ● Внутренняя и внешняя маршрутизация на пограничном полотне. ● Поддерживается до 4 шлюзов FabricPath anycast. |

Многоадресный трафик | Поддерживает: ● Многоадресный трафик уровня 2 (перенаправляется многопунктовым деревом) ● Многоадресный IP-трафик уровня 3 (перенаправляется многоадресным трафиком уровня 3 с использованием PIM) |

Многопользовательская среда | ● Мультиарендность уровня 2 с VN-сегментом. ● Многопользовательский уровень 3 с VRF-lite |

Стандартный номер | на базе TRILL (собственная разработка Cisco) |

Поддерживаемое оборудование | ● Cisco Nexus Коммутаторы серии ® 7000, включая коммутаторы платформы Cisco Nexus 7700 ● Коммутаторы платформы Cisco Nexus 5500 и 5600 ● Коммутаторы Cisco Nexus серии 6000 |

Для поддержки функций и получения дополнительных сведений о технологии Cisco FabricPath см. Руководства по настройке, примечания к выпуску и справочные документы, перечисленные в конце этого документа.

Межконтинентальная сеть Cisco VXLAN с потоком и обучением

VXLAN, одна из многих доступных оверлейных технологий виртуализации сети, предлагает несколько преимуществ. Это стандартный протокол, использующий базовые IP-сети. Он расширяет сегменты уровня 2 по инфраструктуре уровня 3 для построения наложенных логических сетей уровня 2. Он инкапсулирует кадры Ethernet в заголовки протокола IP User Data Protocol (UDP) и транспортирует инкапсулированные пакеты через базовую сеть к удаленным оконечным точкам туннеля VXLAN (VTEP), используя обычный механизм IP-маршрутизации и пересылки.Примерно в 2014 году Cisco начала поддерживать технологию VXLAN flood-and-learn spine-and-leaf на нескольких коммутаторах Cisco Nexus, таких как платформа Cisco Nexus 5600 и Cisco Nexus серий 7000 и 9000. В этом разделе описывается функция распространения и изучения Cisco VXLAN на этих аппаратных коммутаторах Cisco.

Формат инкапсуляции и соответствие стандартам

Технология распространения и обучения Cisco VXLAN соответствует стандартам IETF VXLAN (RFC 7348), которые определяют VXLAN на основе многоадресной рассылки без уровня управления.Исходный кадр уровня 2 инкапсулируется с заголовком VXLAN, затем помещается в пакет UDP-IP и транспортируется по IP-сети.

Подложка сети

Магистральная сеть VXLAN с потоком и обучением использует IP уровня 3 для базовой сети. Базовая многоадресная IP-рассылка используется для уменьшения объема лавинной рассылки для набора хостов, участвующих в сегменте VXLAN. Каждый сегмент VXLAN имеет идентификатор сети VXLAN (VNID), и этот VNID отображается на группу многоадресной IP-адресации в транспортной IP-сети.Каждое устройство VTEP независимо настраивается с этой группой многоадресной рассылки и участвует в маршрутизации PIM. Дерево многоадресной рассылки для этой группы строится через транспортную сеть на основе местоположений участвующих VTEP. Требование включить возможности многоадресной рассылки в базовой сети представляет проблему для некоторых организаций, поскольку они не хотят включать многоадресную рассылку в своих центрах обработки данных или глобальных сетях.

В Cisco Nexus серии 9000 добавлена функция входящей репликации, поэтому в базовой сети не используется многоадресная передача.VXLAN VTEP использует список IP-адресов других VTEP в сети для отправки широковещательного и неизвестного одноадресного трафика. Обмен этими IP-адресами между VTEP осуществляется через статическую конфигурацию входящей репликации (рисунок 10).

Рисунок 10.

Базовая IP-сеть VXLAN

Оверлейная сеть

В спинно-листовой сети VXLAN с потоком и обучением отсутствует плоскость управления для оверлейной сети.Наложенная сеть уровня 2 создается поверх базовой IP-сети уровня 3 с использованием механизма туннелирования VTEP для транспортировки пакетов уровня 2. В оверлейной сети используется семантика flood-and-learn (рисунок 11).

Рисунок 11.

Оверлейная сеть VXLAN

Широковещательный и неизвестный одноадресный трафик

Underlay IP PIM или функция входящей репликации используется для отправки широковещательного и неизвестного одноадресного трафика.Обратите внимание, что функция входящей репликации поддерживается только на коммутаторах Cisco Nexus серии 9000.

Обнаружение хоста и доступность

Магистральная и оконечная сеть VXLAN с лавинной рассылкой и обучением полагается на начальную лавинную рассылку трафика в плоскости данных, чтобы позволить VTEP обнаруживать друг друга и изучать MAC-адреса удаленных хостов и сопоставления MAC-адресов VTEP для каждого сегмента VXLAN. После завершения сопоставления MAC-to-VTEP, VTEP пересылают трафик VXLAN в одноадресном потоке.

Многоадресный трафик

В сети VXLAN с потоком и обучением, основанной и оконечной, многоадресный трафик уровня 2 наложенного клиента поддерживается с использованием базового IP PIM или функции входящей репликации.Обратите внимание, что входящая репликация поддерживается только на коммутаторах Cisco Nexus серии 9000.

Многоадресный IP-трафик уровня 3 пересылается с помощью многоадресной маршрутизации на основе PIM уровня 3.

Масштабирование групп многоадресной рассылки необходимо тщательно продумать. В идеале вы должны сопоставить один сегмент VXLAN с одной многоадресной IP-группой, чтобы обеспечить оптимальную многоадресную пересылку. У вас также может быть несколько сегментов VXLAN, совместно использующих одну многоадресную группу IP в базовой сети; однако перегрузка групп многоадресной рассылки приводит к неоптимальной многоадресной пересылке.

Функция маршрутизации уровня 3

Как и в традиционной среде VLAN, во многих ситуациях требуется маршрутизация между сегментами VXLAN или от сегмента VXLAN к сегменту VLAN. В типичной структуре сети VXLAN с потоком и обучением, состоящей из позвоночника и листа, оконечные коммутаторы Top-of-Rack (ToR) используются как устройства VTEP для расширения сегментов уровня 2 между стойками. Эти VTEP являются шлюзами VXLAN уровня 2 для моста VXLAN-VLAN или VLAN-VXLAN. Когда трафик необходимо маршрутизировать между сегментами VXLAN или из сегмента VXLAN в сегмент VLAN и наоборот, на некоторых VTEP необходимо включить функцию шлюза VXLAN уровня 3.Обычно используются внутренняя и внешняя трассировка на слое корешка и внутренняя и внешняя трассировка на листовом слое. Обе схемы обеспечивают централизованную маршрутизацию: то есть функции внутренней и внешней маршрутизации уровня 3 централизованы на определенных коммутаторах.

Внутренняя и внешняя фрезеровка на уровне позвоночника

Как показано в схеме внутренней и внешней маршрутизации на уровне позвоночника на рисунке 12, конечный коммутатор ToR VTEP является шлюзом VXLAN уровня 2 для транспортировки сегмента уровня 2 по IP-сети нижележащего уровня 3.Переключатель позвоночника выполняет две функции. Он является частью IP-сети уровня 3 и транспортирует инкапсулированные пакеты VXLAN. Он также выполняет внутреннюю маршрутизацию между VXLAN и внешнюю маршрутизацию. Внутренний и внешний маршрутизируемый трафик должен пройти один базовый переход от конечного VTEP к магистральному коммутатору, который будет маршрутизироваться.

Обратите внимание, что максимальное количество активных-активных шлюзов между VXLAN – два с протоколом маршрутизатора с горячим резервированием (HSRP) и конфигурацией vPC. Кроме того, шлюз VXLAN уровня 3 изучает MAC-адрес хоста, поэтому вам необходимо учитывать масштаб MAC-адресов, чтобы избежать превышения пределов масштабируемости вашего оборудования.

Рисунок 12.

Внутренняя и внешняя фрезеровка на уровне позвоночника

Внутренняя и внешняя разводка по бордюру

Как показано в схеме внутренней и внешней маршрутизации на граничном листе на Рисунке 13, оконечный коммутатор ToR VTEP является шлюзом VXLAN уровня 2 для транспортировки сегмента уровня 2 по лежащей в основе IP-сети уровня 3. Магистральный коммутатор является лишь частью IP-сети уровня 3, лежащей в основе, для транспортировки инкапсулированных пакетов VXLAN.Он не узнает MAC-адрес оверлейного хоста. Граничный конечный маршрутизатор включен со шлюзом VXLAN уровня 3 и выполняет внутреннюю маршрутизацию между VXLAN и внешнюю маршрутизацию. Внутренний и внешний маршрутизируемый трафик должен пройти два промежуточных перехода от оконечного VTEP к магистральному коммутатору, а затем к пограничному оконечному коммутатору, чтобы достичь внешней сети.

Максимальное количество активных-активных шлюзов между VXLAN – два с конфигурацией HSRP и vPC. Кроме того, пограничный шлюз VXLAN уровня 3 изучает MAC-адрес хоста, поэтому вам необходимо учитывать масштаб MAC-адресов, чтобы избежать превышения пределов масштабируемости вашего оборудования.

Рисунок 13.

Внутренняя и внешняя разводка по бордюру

Мультиарендность