3.3.Схемы с памятью

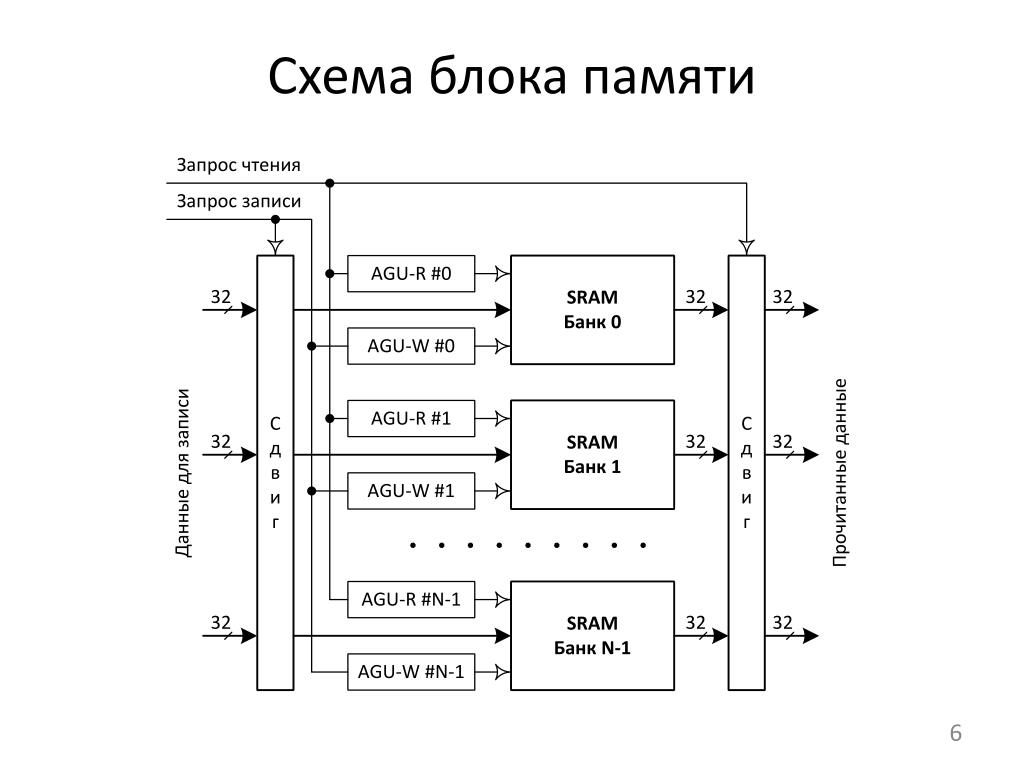

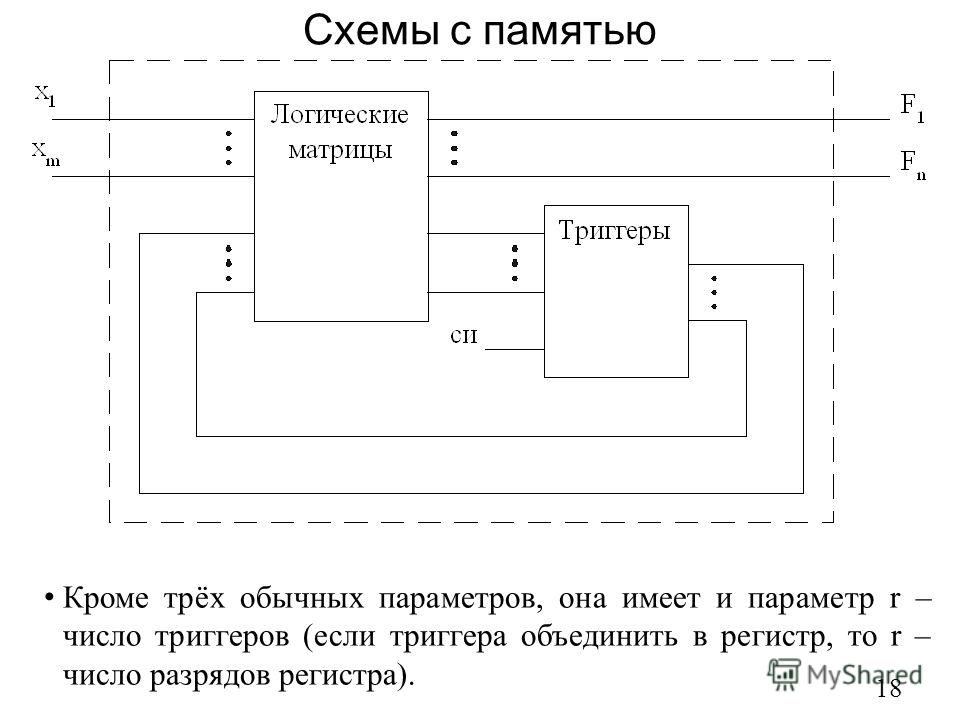

Более сложным преобразователем информации являются схемы с памятью. Наличие памяти в схеме позволяет запоминать промежуточные состояния обработки и учитывать их значения в дальнейших преобразованиях. Выходные сигналы Y=(y1,y2,…,ym) в схемах данного типа формируются не только по совокупности входных сигналов X = (х1,х2,…,хп), но и по совокупности состояний схем памяти Q = (q1,q2,…,qk)- При этом различают текущий дискретный момент времени t и последующий (t+1) момент времени (рис. 3.8).

Передача

значения Q между

моментами времени t

и (t+1) осуществляется

обычно с применением двухступенчатой

памяти и синхронизирующих импульсов

(СИ).

В качестве простейшего запоминающего элемента в современных ЭВМ используют триггеры. В связи с успехами микроэлектроники в схемах основных устройств ЭВМ (процессоров и оперативной памяти) перестали применяться в качестве запоминающихся элементов схемы, использующие остаточную намагниченность — ферритовые сердечники. Самая простейшая схема триггера может быть синтезирована по общим правилам (см. п. 2.4.4).

Пример 3.1. Построить автомат памяти — триггер, имеющий вход R (Reset — сброс), для установки элемента в «нулевое состояние» и вход S (Set — установка) — для установки элемента в «единичное» состояние. При отсутствии сигналов R=S=0 элемент должен сохранять свое состояние до тех пор, пока не будут получены новые сигналы на входе R или S.

Условия работы триггера могут быть показаны в виде таблицы переходов, представляющей собой модификацию таблицы истинности. Наиболее простой вид она имеет для автомата, описываемого системой уравнений автомата Мура.

Таблица

3. 5 Условия

работы триггера

5 Условия

работы триггера

Содержание

таблицы расшифровывается следующим

образом. Элемент памяти может сохранять

значение qt=0

или qt=1 в

зависимости от установки ранее

установленного состояния. При отсутствии

входных сигналов на входах R

и S

(R=0

и S=0)

значения qt+l в

первой строке таблицы в точности

повторяют значения qt. При

поступлении сигнала R=l

(сигнала установки «нуля») элемент

независимо от своего состояния

принимает значение, равное нулю, дt+1 =0.

Если же на вход S

поступает сигнал установки «единицы»

(S=1),

то q В схемах формирования

сигналов R

и S

должны быть предусмотрены блокировки,

исключающие их совпадения, S=R=1.

В схемах формирования

сигналов R

и S

должны быть предусмотрены блокировки,

исключающие их совпадения, S=R=1.

Для таблицы переходов (см. табл. 3.5) может быть построена диаграмма Вейча (табл. 3.6).

Таблица 3.6 Диаграмма Вейча для таблицы переходов триггера

В этой таблице знаком «~» отмечены запрещенные комбинации входных сигналов. Эти комбинации могут быть использованы для упрощения логических зависимостей. Логическая зависимость, описывающая работу элемента памяти, принимает вид:

(3.4)

Уравнение (3.4) получено путем эквивалентных преобразований. Добавление в него комбинаций, соответствующих запрещенным ситуациям и помеченных знаком «~», т.е.

позволяет еще более упростить уравнение триггера:

Для реализации полученной зависимости в базисе И — НЕ применим правило де Моргана и получим функцию

По

данной зависимости можно построить

схему элемента памяти — асинхронного

RS-триггера. В этой схеме следует только соединить

выход qt+1 со входом qt (рис. 3.9). Эта связь отмечена штриховой

линией.

В этой схеме следует только соединить

выход qt+1 со входом qt (рис. 3.9). Эта связь отмечена штриховой

линией.

RS-триггер нашел широкое распространение в схемах ЭВМ. Одиночные триггеры этого типа часто используются в различных блоках управления. В асинхронных RS-триггерах имеется один существенный недостаток, обусловленный самой логикой их построения (см. табл. 3.5), т.е. в них сигналы R и S должны быть разнесены во времени. Дополнение этого триггера комбинационными схемами синхронизации на входе и выходе позволяет получить триггеры с более сложной логикой работы: синхронные RS-, Т-, JK-, D-триггеры и целый ряд комбинированных RST-, JKRS-, DRS-триггеров [4].

Рис. 3.9. Схема асинхронного RS-триггера: а — схема;

б — обозначение на принципиальных электрических схемах;

в — временная диаграмма

Прописные буквы в названиях триггеров обозначают:

• R (Reset — сброс) — вход установки триггера в нулевое состояние, Q=0;

• S (Set — установка) — вход установки триггера в единичное состояние, Q=l;

• Т (Toggle —релаксатор) — счетный вход триггера;

• J (Jerk — внезапное включение) — вход установки JK-триггера в единичное состояние, Q=l;

• К (Kill — внезапное выключение) — Q=0;

• D (Delay — задержка) — вход установки триггера в единичное или нулевое состояние на время, равное одному такту;

• С

(Clock

— часы) — вход синхронизирующих тактовых

импульсов.

На рис. 3.10 показаны схемы синхронного однотактного (а) и двухтактного (б) RS-триггеров.

Рис. 3.10. Синхронные RS-триггеры

Двухкаскадная схема RS-триггера (см. рис. 3.10, б) нашла наиболее широкое применение для построения n-разрядных схем запоминания — всевозможных регистровых схем. Пунктирными линиями на схеме указаны дополнительные точки подключения сигналов установки и сброса.

На рис. 3.11 приведена схема Т-триггера или, иначе говоря, триггера со счетным входом. При значении Xt=0 триггер сохраняет свое ранее установленное состояние — режим хранения состояния, при Хt=1 триггер переходит в противоположное состояние. Таблица переходов (табл. 3.7) и диаграмма работы (см. рис. 3.11,

Рис. 3.11. Схема триггера со счетным входом: а — функциональная схема; б — условное обозначение; в — временная диаграмма

Таблица 3. 7 Таблица

переходов Т-триггера

7 Таблица

переходов Т-триггера

Используя таблицу переходов, можно получить логическую функцию, реализуемую Т-триггером:

(3.7)

Нетрудно видеть, что зависимость (3.7) очень похожа на функцию (3.2), выведенную для одноразрядного комбинационного полусумматора. На рис. 3.11, а показано, как двухтактный RS-триггер преобразуется в Т-триггер.

Наиболее сложным типом триггера является JK-триггер. Он, по существу, является объединением двухтактного RS- и Т-триггеров. Этому соответствует его таблица переходов (табл. 3.8).

Таблица 3.8 Таблица переходов JK-триггера

Если первые три строки таблицы переходов полностью повторяют соответствующие строки табл. 3.5, то последняя строка, с запрещенной комбинацией для RS-триггера, соответствует режиму переключения Т-триггера (см. табл. 3.7). Схема JK-триггера изображена на рис. 3.12.

Рис. 3.12. JK-триггер: а

— функциональная

схема; б

— условное

обозначение

3.12. JK-триггер: а

— функциональная

схема; б

— условное

обозначение

D-триггер обычно строится на основе двухтактного RS- или JK-триггера. Он предназначается для хранения состояния (1 или 0) на один период тактовых импульсов (с задержкой на 1 такт). Его переходы отражены в табл. 3.9. На рис. 3.13, а и б представлены варианты построения D-триггера, а на рис. 3.13, в — его условное обозначение.

Таблица 3.9 Таблица переходов D-триггера

Рис. 3.13. D-триггер: а — функциональная схема на основе RS-триггера; б — функциональная схема на основе JK-триггера; в — условное обозначение

Все перечисленные элементы памяти позволяют хранить одну единицу информации — бит или одну двоичную цифру.

При построении

ЭВМ широко используются функциональные

схемы, обеспечивающие операции

хранения и преобразования информации

над группами битов (машинными словами). Такие сложные схемы называются

узлами. К типовым узлам относят: регистры,

счетчики, сумматоры. Все они также

принадлежат к регулярным структурам,

состоящим из одинаковых параллельно

работающих одноразрядных схем.

Такие сложные схемы называются

узлами. К типовым узлам относят: регистры,

счетчики, сумматоры. Все они также

принадлежат к регулярным структурам,

состоящим из одинаковых параллельно

работающих одноразрядных схем.

Регистром называется узел, предназначенный для приема, временного хранения и выдачи машинного слова. Регистры могут также использоваться для некоторых операций преобразования данных: для сдвига кода числа (слова) на определенное число разрядов влево или вправо, для преобразования последовательного кода числа в параллельный и наоборот и т.д. Эти дополнительные функции регистров обеспечиваются путем усложнения схем хранения, выбора более сложных триггеров и подключения дополнительных логических схем на их входах и выходах.

Таким образом, регистры представляют собой совокупность триггеров, число которых соответствует числу разрядов в слове, и вспомогательных схем, обеспечивающих выполнение различных операций над словом.

На

рис. 3.14 показана функциональная схема

n-разрядного

регистра, построенного на RS-триггерах.

Информация в регистр записывается

под действием сигнала «Запись».

Предварительно перед установкой

кода на регистр обычно на все разряды

R

подается сигнал сброса. На рисунке

показано, что подключение к входам R

дополнительных инверторов позволяет

избежать этой предварительной операции.

Здесь на вход каждого разряда поступает

парафазный код двоичной цифры

3.14 показана функциональная схема

n-разрядного

регистра, построенного на RS-триггерах.

Информация в регистр записывается

под действием сигнала «Запись».

Предварительно перед установкой

кода на регистр обычно на все разряды

R

подается сигнал сброса. На рисунке

показано, что подключение к входам R

дополнительных инверторов позволяет

избежать этой предварительной операции.

Здесь на вход каждого разряда поступает

парафазный код двоичной цифры

На

рис. 3.15 изображена функциональная схема

того же регистра, дополненная логическими

элементами для преобразования хранящегося

на регистре кода. По сигналу «Прямой

код» с регистра считывается прямой код

хранящихся данных, а по сигналу «Обратный

код» — инверсное значение каждого

разряда слова. Если оба этих сигнала

поступают одновременно, то считывается

парафазный код хранящейся информации. Более сложная логика на входе и выходе

запоминающих элементов позволяет

строить сдвигающие регистры.

Более сложная логика на входе и выходе

запоминающих элементов позволяет

строить сдвигающие регистры.

Рис. 3.14. Схема регистра на RS-триггерах: а — функциональная схема; б — условное обозначение регистра

Рис. 3.15. Схема выдачи информации из регистра

Счетчик — это узел ЭВМ, позволяющий осуществлять подсчет поступающих на его вход сигналов и фиксацию результата в виде многоразрядного двоичного числа. Счетчик, состоящий из n-триггеров, позволяет подсчитывать до N сигналов, связанных зависимостью

п = Iog2N или N = 2n.

В ЭВМ счетчики

используются для подсчета импульсов,

сдвигов, формирования адресов и т.д.

Функционально различают суммирующие,

вычитающие, реверсивные счетчики. Они

также отличаются друг от друга логикой

работы дополнительных логических

элементов, подключаемых к триггерам.

В основу построения любого счетчика положено свойство Т-триггеров изменять свое состояние при подаче очередного сигнала на счетный вход Т. На рис. 3.16 показана схема трех разрядов суммирующего счетчика, построенного на Т-триггерах. Логика его работы представлена в табл. 3.10.

Таблица 3.10 Таблица переходов трехразрядного счетчика

Рис. 3.16. Организация счетчика на Т-триггерах: а — функциональная схема;

б — условное обозначение счетчика

Сумматор — это

узел ЭВМ, в котором суммируются коды

чисел. Как правило, любой сумматор

представляет собой комбинацию

одноразрядных сумматоров. Сумматоры

различают по принципам построения:

накапливающего типа и комбинационного

типа. Сумматоры накапливающего

типа строят

на сложных JKRS-триггерах,

дополняя их выходы достаточно

сложными

схемами формирования и распространения

переносов. Процесс сложения при этом

осуществляется поэтапно. Сначала на

триггерах сумматора фиксируется код

первого операнда, затем на счетные

коды разрядов подается код второго

операнда. По зависимостям (3.3) на каждом

триггере формируются одноразрядные

суммы и значения переносов между

разрядами. Учет возникающих переносов

задерживает формирование окончательного

результата суммы и может требовать

дополнительных тактов сложения.

Из-за этого многоразрядные схемы

сумматора накапливающего типа используются

достаточно редко.

Процесс сложения при этом

осуществляется поэтапно. Сначала на

триггерах сумматора фиксируется код

первого операнда, затем на счетные

коды разрядов подается код второго

операнда. По зависимостям (3.3) на каждом

триггере формируются одноразрядные

суммы и значения переносов между

разрядами. Учет возникающих переносов

задерживает формирование окончательного

результата суммы и может требовать

дополнительных тактов сложения.

Из-за этого многоразрядные схемы

сумматора накапливающего типа используются

достаточно редко.

Для построения сумматоров чаще применяют сумматоры комбинационного типа. Логика работы такого сумматора была представлена данными табл. 2.2. Обычно у комбинационного сумматора на входе и выходе имеются регистры для хранения и преобразования кодов операндов и результата (рис. 3.17).

Рис. 3.17. Упрощенная схема сумматора ЭВМ

Регистр Рг1

предназначается для хранения кода

первого операнда, регистр Рг2 — для

хранения кода второго операнда. Сумматор

по сигналам из устройства управления

настраивается на выполнение определенной

машинной операции, соответствующей

коду операции, находящемуся в коде

команды. Результат выполняемой операции

фиксируется в регистре РгЗ. При

необходимости этот результат может

использоваться для продолжения

вычислений. Для этого предусматривается

возможность перезаписи содержимого

регистра РгЗ на Рг1 в качестве значения

одного из операндов при выполнении

очередной операции.

Сумматор

по сигналам из устройства управления

настраивается на выполнение определенной

машинной операции, соответствующей

коду операции, находящемуся в коде

команды. Результат выполняемой операции

фиксируется в регистре РгЗ. При

необходимости этот результат может

использоваться для продолжения

вычислений. Для этого предусматривается

возможность перезаписи содержимого

регистра РгЗ на Рг1 в качестве значения

одного из операндов при выполнении

очередной операции.

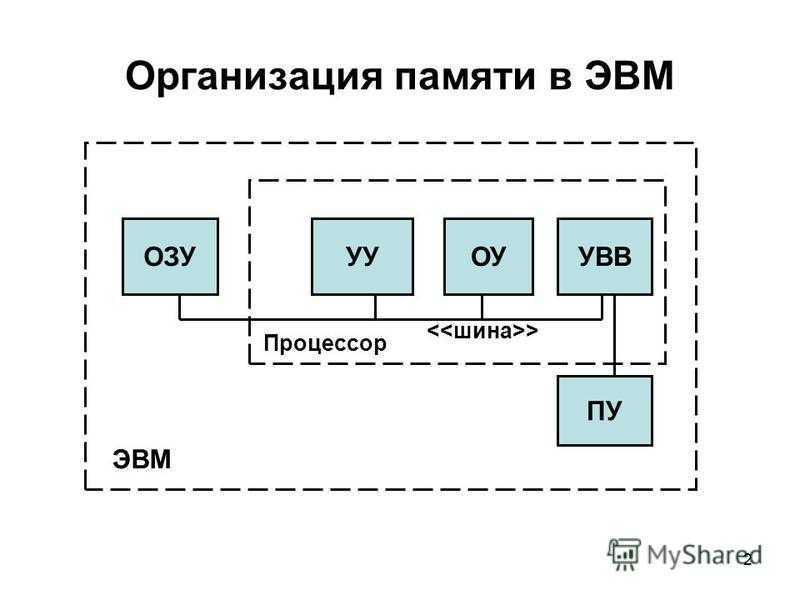

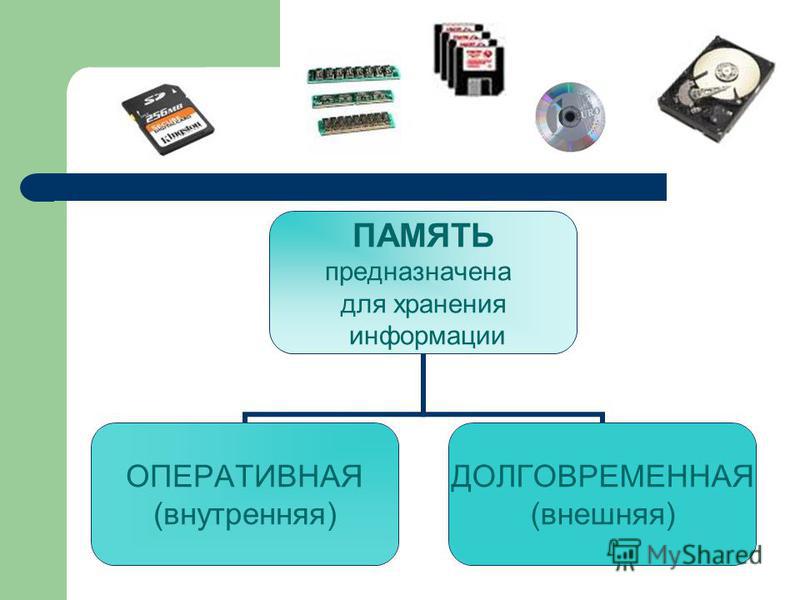

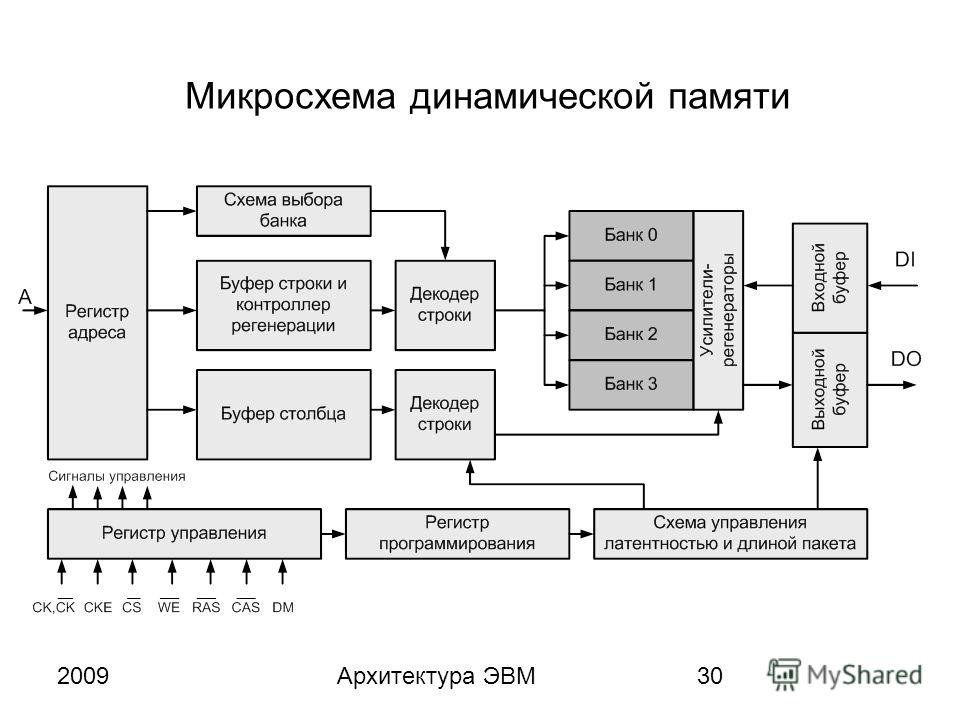

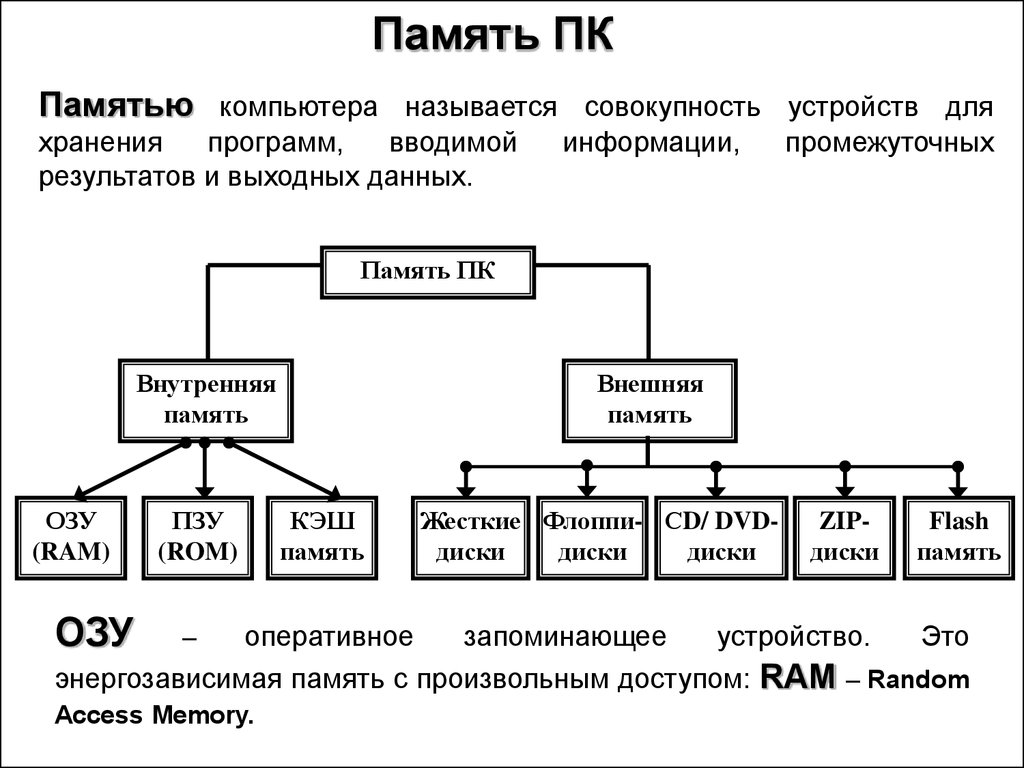

Оперативная память. Строение и устройство (RAM, ОЗУ) / Хабр

Оперативная память это важная часть любой компьютерной системы и сейчас я объясню, почему это так.

Оперативная память (RAM)

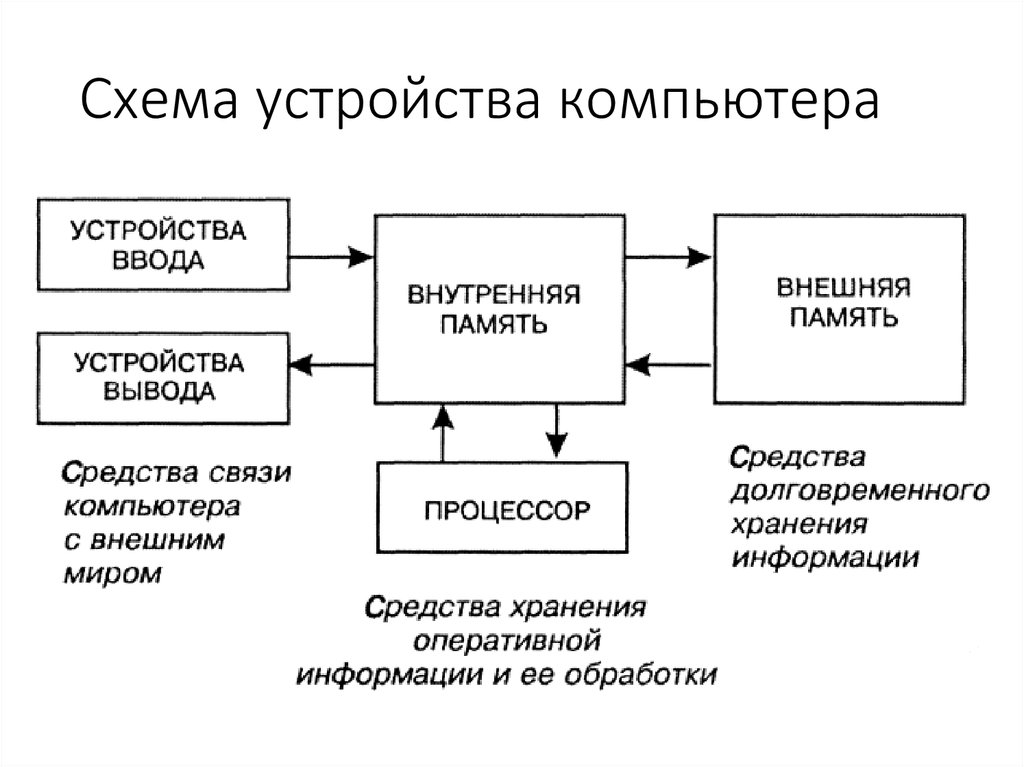

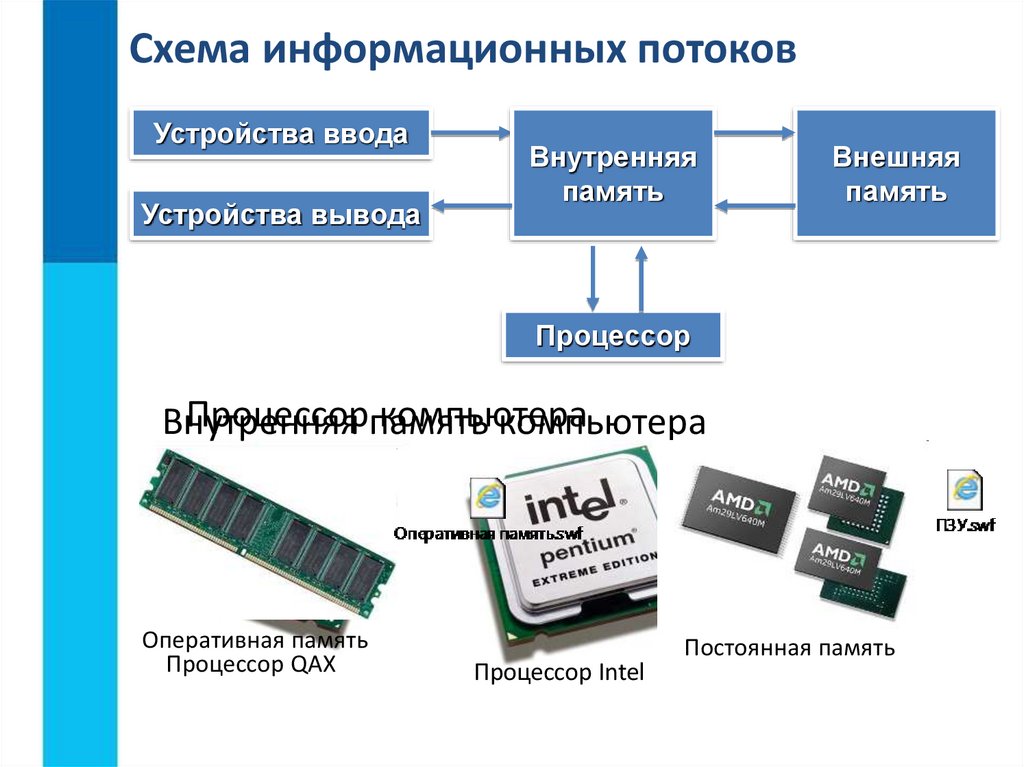

В процессе работы память выступает в качестве буфера между накопителем и процессором, то есть данные сперва считываются с жесткого диска (или другого накопителя) в оперативную память и уже затем обрабатываются центральным процессором.

Упрощённая схема работы памяти компьютера

Такая схема применяется, потому что процессор – очень быстрое устройство и ему требуется быстро получать доступ к нужным данным и командам, иначе он будет простаивать и производительность системы уменьшится, а так как жёсткий диск и SSD не могут обеспечить необходимую скорость, все нужные данные считываются и перемещаются в более быструю оперативную память и хранятся там, пока не понадобятся процессору для обработки.

Физически, оперативная память представляет собой набор микросхем припаянных к плате.

Микросхемы на планке памяти

Если посмотреть внутрь одной такой микросхемы, то можно увидеть что она состоит из множества, соединённых друг с другом слоёв, каждый слой состоит из огромного количества ячеек, образующие прямоугольные матрицы. Одна ячейка может содержать 1 бит информации, а состоит она из одного полевого транзистора и одного конденсатора.

Устройство ячейки в чипе

Выглядит эта конструкция довольно сложно и может различаться в зависимости от применённых технологий, так что для наглядности лучше представить ячейку в виде схемы.

Схематичное устройство ячейки динамической памяти

Так легче понять, что именно конденсатор хранит информацию, а транзистор выполняет роль электрического ключа, который либо удерживает заряд на конденсаторе, либо открывает для считывания. Когда конденсатор заряжен, можно получить логическую единицу, а когда разряжен, ноль.

Упрощённая схема массива ячеек, страница

Таких конденсаторов в чипе, очень много но считать заряд с одной конкретной ячейки нельзя, считывается вся страница целиком.

Чтобы сделать это необходимо на нужную нам горизонтальную линию которая называется строка, подать сигнал, который откроет транзисторы, после чего усилители расположенные на концах вертикальных линий считают заряды которые находились на конденсаторах.

Упрощённая схема массива ячеек (чтение)

Каждое такое считывание опустошает заряды на странице, из-за чего приходится её заново переписывать, для этого на строку так же подаётся открывающий транзистор заряд, а на столбцы подаётся более высокое напряжение, тем самым заряжая конденсаторы и записывая информацию.

Упрощённая схема массива ячеек (запись)

Задержки между этими операциями называют “Латенстностью” или в народе “Таймингами”, чем они меньше тем более быстрая будет вся система в целом

Помимо самих чипов памяти, на модуль распаиваются SMD-компоненты резисторы и конденсаторы обеспечивающие развязку сигнальных цепей и питание чипов, а также Микросхема SPD – это специальная микросхема, в которой хранятся данные о параметрах всего модуля (ёмкость, рабочее напряжение, тайминги, число банков и так далее). Это нужно чтобы во время запуска системы, BIOS на материнской плате выставил оптимальные настройки согласно информации, отображенной в микросхеме.

Это нужно чтобы во время запуска системы, BIOS на материнской плате выставил оптимальные настройки согласно информации, отображенной в микросхеме.

Компоненты плашки памяти, микросхема SPD

Так же существует несколько форм факторов модулей, модули для компьютеров называются DIMM, а для ноутбуков и компактных систем SO-DIMM, отличаются они размером и количеством контактов для подключения. Это двухрядные модули которые имеют два независимых ряда контактов по одному с каждой стороны.

DIMM и SO-DIMM

Например в старых модулях Simm контакты с двух сторон были замкнуты и они могли передать только 32 бита информации за такт, в то время как dimm могут передавать 64 бита.

DIMM и SIMM

Ко всему этому модули делятся на одноранговые, двухранговые и четырёхранговые. Ранг — это блок данных шириной 64 бита, который может быть набран разным количеством чипов память.Одноранговая память имеет ширину 64 бита, тогда как Двухранговая память имеет ширину 128 бит. Но, так как один канал памяти имеет ширину всего 64 бита, как и одноранговый модуль, контроллер памяти может одновременно обращаться только к одному рангу. В то время как двухранговый модуль может заниматься ответом на переданную ему команду, а другой ранг уже может подготавливать информацию для следующей команды, что незначительно увеличивает производительность.

В то время как двухранговый модуль может заниматься ответом на переданную ему команду, а другой ранг уже может подготавливать информацию для следующей команды, что незначительно увеличивает производительность.

Ранги оперативной памяти

Так же хочется отдельно сказать о памяти с коррекцией ошибок, ECC-памяти, так как эти модули имеют дополнительный банк памяти на каждые 8 микросхем. Дополнительные банки и логика в модуле служат для проверки и устранения ошибок.

ECC- память с коррекцией ошибок

Использование буферов и коррекции ошибок незначительно ухудшает производительность, но сильно повышает надёжность данных. Поэтому ECC память широко используется в серверах и рабочих станциях

Ширина данных у ECC

Ещё немного расскажу о типах памяти, так как в современных компьютерах используется синхронная динамическая память с произвольным доступом и удвоенной скоростью передачи данных DDR SDRAM 4-го поколения и скоро будет распространено пятое.

Синхронная динамическая память (DDR)

Память типа DDR пришла на смену памяти типа SDR. SDR SDRAM работает синхронно с контроллером. В ней внутренняя и внешняя шина данных работает на одной и той же частоте. При подаче сигнала на микросхему происходит синхронное считывание информации и передача её в выходной буфер. Передача каждого бита из буфера происходит с каждым тактом работы ядра памяти. В SDR памяти синхронизация обмена данными происходит по фронту тактового импульса.

SDR SDRAM работает синхронно с контроллером. В ней внутренняя и внешняя шина данных работает на одной и той же частоте. При подаче сигнала на микросхему происходит синхронное считывание информации и передача её в выходной буфер. Передача каждого бита из буфера происходит с каждым тактом работы ядра памяти. В SDR памяти синхронизация обмена данными происходит по фронту тактового импульса.

Синхронная динамическая память (SDR)

При подаче сигнала на микросхему происходит синхронное считывание информации и передача её в выходной буфер. Передача каждого бита из буфера происходит с каждым тактом работы ядра памяти. В SDR памяти синхронизация обмена данными происходит по фронту тактового импульса.

SDR (Схема)

После SDR, вышла DDR память, в ней обмен данными по внешней шине идет не только по фронту тактового импульса, но и по спаду, из-за чего на той же частоте можно передать вдвое больше информации, а чтобы воспользоваться этим увеличением, внутреннею шину расширили вдвое. То есть работая на тех же частотах что SDR, DDR память передаёт в 2 раза больше данных.

То есть работая на тех же частотах что SDR, DDR память передаёт в 2 раза больше данных.

SDR и DDR (Схема)

Следующие поколения памяти DDR не сильно отличаются, увеличивается только частота работы буферов ввода вывода, а также расширяется шина, связывающая ядро памяти с буферами, сам принцип работы не меняется, но даже так, каждое новое поколение получает таким способом существенное увеличение пропускной способности, без увеличения частоты работы самих ячеек памяти.

(Схема) DDR 2, DDR 3, DDR 4, DDR 5

Понятно, что с каждый новым поколением улучшается работа логики, техпроцесс и многое другое. Но сам принцип работы остаётся одним и для общего понимая этого достаточно.

Ниже оставлю видео версию статьи, может кому будет интересно посмотреть на 3D анимацию планок памяти. На этом у меня всё, всем пока.

Схемы памяти — справочник Digilent

Содержание

- Схемы памяти

- Бистабильная схема

- Важные идеи

Схемы памяти функционируют, сохраняя напряжение, присутствующее во входном сигнале, всякий раз, когда они запускаются управляющим сигналом. Они сохраняют это сохраненное напряжение до следующего утверждения управляющего (или триггерного) сигнала. Между утверждениями управляющего сигнала входной сигнал игнорируется, а выход приводится к последнему сохраненному напряжению. Схема памяти сохраняет уровень входного сигнала при каждом утверждении управляющего входа, выход будет изменяться сразу после утверждения управляющего сигнала (если входное значение противоположно сохраненному) или останется постоянным. «Память» происходит между утверждениями управляющего сигнала, потому что выход остается постоянным на последнем сохраненном значении, независимо от изменений входного сигнала.

Они сохраняют это сохраненное напряжение до следующего утверждения управляющего (или триггерного) сигнала. Между утверждениями управляющего сигнала входной сигнал игнорируется, а выход приводится к последнему сохраненному напряжению. Схема памяти сохраняет уровень входного сигнала при каждом утверждении управляющего входа, выход будет изменяться сразу после утверждения управляющего сигнала (если входное значение противоположно сохраненному) или останется постоянным. «Память» происходит между утверждениями управляющего сигнала, потому что выход остается постоянным на последнем сохраненном значении, независимо от изменений входного сигнала.

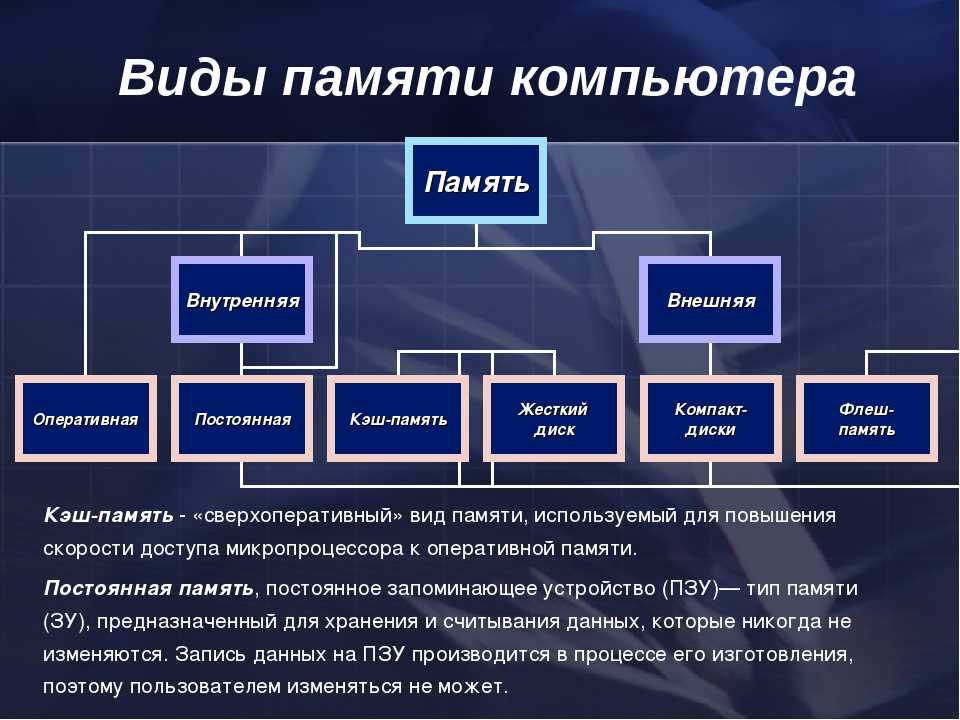

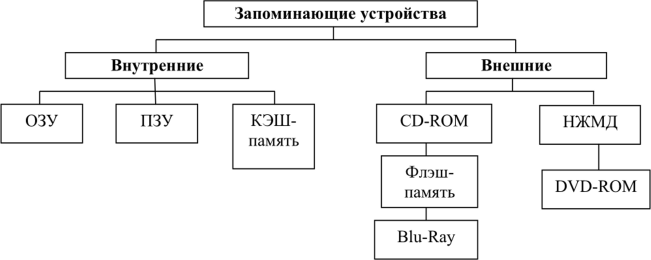

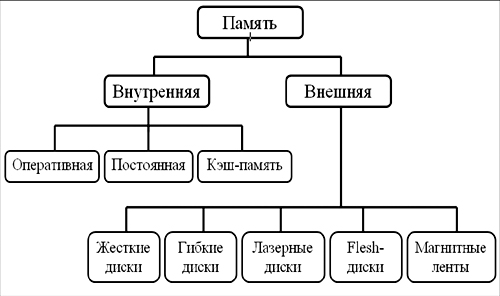

Сегодня используются два основных семейства схем памяти: динамическая память и статическая память. Ячейки динамической памяти используют небольшой конденсатор для хранения напряжения сигнала, и они используются в самых маленьких и дешевых схемах памяти. Поскольку напряжение на конденсаторе со временем снижается, ячейки динамической памяти необходимо периодически обновлять, иначе они потеряют свое сохраненное значение. Хотя это требование обновления приводит к значительным накладным расходам, ячейки динамической памяти очень малы, поэтому они стали наиболее широко используемыми из всех схем памяти. Большинство схем статической памяти сохраняют логические значения, используя два параллельных инвертора. Устройства статической памяти не нуждаются в обновлении, и они могут работать намного быстрее, чем динамические схемы. Но поскольку они требуют гораздо большей площади микросхемы, чем ячейки динамической памяти, они используются только там, где они больше всего нужны, например, в высокоскоростной памяти, или когда требуется лишь небольшой объем памяти. Схемы динамической памяти для компьютерных систем стали очень специализированными, и они будут рассмотрены в одной из следующих лабораторных работ. В этом разделе мы сосредоточимся на схемах памяти, которые используются для хранения информации о рабочем состоянии цифровой системы.

Хотя это требование обновления приводит к значительным накладным расходам, ячейки динамической памяти очень малы, поэтому они стали наиболее широко используемыми из всех схем памяти. Большинство схем статической памяти сохраняют логические значения, используя два параллельных инвертора. Устройства статической памяти не нуждаются в обновлении, и они могут работать намного быстрее, чем динамические схемы. Но поскольку они требуют гораздо большей площади микросхемы, чем ячейки динамической памяти, они используются только там, где они больше всего нужны, например, в высокоскоростной памяти, или когда требуется лишь небольшой объем памяти. Схемы динамической памяти для компьютерных систем стали очень специализированными, и они будут рассмотрены в одной из следующих лабораторных работ. В этом разделе мы сосредоточимся на схемах памяти, которые используются для хранения информации о рабочем состоянии цифровой системы.

Многие электронные устройства содержат цифровые системы, которые используют схемы памяти для определения своего рабочего состояния. На самом деле любое электронное устройство, которое может создать последовательность событий или отреагировать на нее, должно иметь память. Примеры таких устройств включают часы и таймеры, контроллеры бытовой техники, игровые устройства и вычислительные устройства. Если цифровая система содержит N устройств памяти, и каждое устройство памяти хранит «1» или «0», то рабочее состояние системы может быть определено N-битным двоичным числом. Кроме того, цифровая система с N запоминающими устройствами должна находиться в одном из 2N состояний, где каждое состояние однозначно идентифицируется двоичным числом, созданным из совокупного содержимого всех запоминающих устройств в системе.

На самом деле любое электронное устройство, которое может создать последовательность событий или отреагировать на нее, должно иметь память. Примеры таких устройств включают часы и таймеры, контроллеры бытовой техники, игровые устройства и вычислительные устройства. Если цифровая система содержит N устройств памяти, и каждое устройство памяти хранит «1» или «0», то рабочее состояние системы может быть определено N-битным двоичным числом. Кроме того, цифровая система с N запоминающими устройствами должна находиться в одном из 2N состояний, где каждое состояние однозначно идентифицируется двоичным числом, созданным из совокупного содержимого всех запоминающих устройств в системе.

В любой момент времени двоичное число, хранящееся во внутренней памяти устройства, определяет текущее состояние цифровой системы. Входные данные, которые поступают в цифровую систему, могут вызвать изменение состояния содержимого одного или нескольких запоминающих устройств (с «1» на «0» или наоборот), тем самым вызывая изменение состояния цифровой системы. Таким образом, изменение состояния цифровой системы или переход состояния происходит всякий раз, когда изменяется двоичное число, хранящееся во внутренней памяти. Именно посредством направленных переходов между состояниями цифровые системы могут создавать последовательности событий или реагировать на них. В следующей лабораторной работе будут представлены цифровые системы, которые могут сохранять и изменять состояния в соответствии с некоторым алгоритмом; эта лабораторная работа исследует схемы, которые можно использовать для формирования памяти.

Таким образом, изменение состояния цифровой системы или переход состояния происходит всякий раз, когда изменяется двоичное число, хранящееся во внутренней памяти. Именно посредством направленных переходов между состояниями цифровые системы могут создавать последовательности событий или реагировать на них. В следующей лабораторной работе будут представлены цифровые системы, которые могут сохранять и изменять состояния в соответствии с некоторым алгоритмом; эта лабораторная работа исследует схемы, которые можно использовать для формирования памяти.

Бистабильная схема

В цифровой инженерии мы имеем дело с двухуровневыми или бистабильными схемами памяти. Бистабильные схемы имеют два устойчивых рабочих состояния: состояние, когда на выходе есть логическая «1» (или Vdd), и состояние, когда на выходе есть «0» (или GND ). Когда бистабильная схема памяти находится в одном из двух стабильных состояний, требуется некоторое количество энергии, чтобы перевести ее из этого состояния в другое стабильное состояние. При переходе между состояниями выходной сигнал должен проходить через область, в которой он нестабилен. Схемы памяти спроектированы таким образом, что они не могут бесконечно оставаться в нестабильном состоянии; как только они входят в нестабильное состояние, они немедленно пытаются восстановить одно из двух стабильных состояний.

При переходе между состояниями выходной сигнал должен проходить через область, в которой он нестабилен. Схемы памяти спроектированы таким образом, что они не могут бесконечно оставаться в нестабильном состоянии; как только они входят в нестабильное состояние, они немедленно пытаются восстановить одно из двух стабильных состояний.

Рисунок 1 выше дает адекватную аналогию. Здесь шарик представляет значение, хранящееся в памяти, а «холм» представляет нестабильную область, которую необходимо пересечь, прежде чем схема памяти сможет перейти к сохранению противоположного значения. Обратите внимание, что в этой аналогии существует третье потенциальное стабильное состояние — с нужным количеством энергии можно было бы сбалансировать мяч прямо на вершине холма. Точно так же схемы памяти также имеют третье потенциально стабильное состояние, где-то между двумя стабильными состояниями. Когда схемы памяти переходят между двумя стабильными состояниями, важно убедиться, что в схему передается достаточно энергии, чтобы обеспечить пересечение нестабильной области.

Оба состояния «0» и «1» в бистабильной схеме легко поддерживаются после их достижения. Управляющий сигнал, который заставляет схему изменять состояния, должен передавать некоторое минимальное количество энергии, чтобы перевести схему в нестабильное состояние. Если вход, вызывающий переход из одного устойчивого состояния в другое, обеспечивает энергию, превышающую минимально необходимую, то переход происходит очень быстро. Если управляющий сигнал выдает меньше минимально необходимой энергии, то схема возвращается в исходное стабильное состояние. Но если на вход подается неправильное количество энергии — достаточное, чтобы начать переход, но недостаточное, чтобы быстро протолкнуть его через нестабильную область, — тогда схема может временно «застрять» в нестабильной области. Схемы памяти спроектированы таким образом, чтобы свести к минимуму эту возможность и уменьшить количество времени, в течение которого схема может оставаться в нестабильном состоянии, если она туда попадет (по аналогии, представьте себе остроконечную вершину в нестабильной области с очень высокой скоростью). Крутые склоны). Если запоминающее устройство застревает в нестабильном состоянии слишком долго, его выходной сигнал может колебаться или оставаться на полпути между «0» и «1», что приводит к непреднамеренному и часто непредсказуемому поведению цифровой системы. Устройство памяти, застрявшее в нестабильной области, называется метастабильным, а все устройства памяти страдают от возможности перехода в метастабильное состояние (подробнее о метастабильности будет сказано позже).

Крутые склоны). Если запоминающее устройство застревает в нестабильном состоянии слишком долго, его выходной сигнал может колебаться или оставаться на полпути между «0» и «1», что приводит к непреднамеренному и часто непредсказуемому поведению цифровой системы. Устройство памяти, застрявшее в нестабильной области, называется метастабильным, а все устройства памяти страдают от возможности перехода в метастабильное состояние (подробнее о метастабильности будет сказано позже).

Схема со статической памятью требует обратной связи, а любая схема с обратной связью имеет память (до сих пор мы имели дело только с комбинационными схемами с прямой связью без памяти). Любая логическая схема может иметь обратную связь, если выходной сигнал просто «подается обратно» и подключается к входу. Большинство цепей обратной связи не будут демонстрировать полезного поведения — они будут либо моностабильными (т. е. застрявшими в выходном состоянии «1» или «0»), либо будут бесконечно колебаться. Некоторые схемы обратной связи будут бистабильными и управляемыми, и эти схемы являются кандидатами на роль простых схем памяти. Простые схемы обратной связи показаны на рис. 2 ниже, и они помечены как управляемые/неуправляемые и бистабильные/небистабильные.

Простые схемы обратной связи показаны на рис. 2 ниже, и они помечены как управляемые/неуправляемые и бистабильные/небистабильные.

Важные идеи

Любое электронное устройство, которое может создавать или реагировать на последовательность событий, должно иметь память.

Изменение состояния цифровой системы или переход состояния происходит всякий раз, когда изменяется двоичное число, хранящееся во внутренней памяти. Именно посредством направленных переходов из одного состояния в другое цифровые системы могут создавать последовательности событий или реагировать на них.

Бистабильные схемы имеют два стабильных рабочих состояния: состояние, когда на выходе есть логическая «1» (или Vdd), и состояние, когда на выходе есть «0» (или 9).0028 ЗЕМЛЯ ). Когда бистабильная схема памяти находится в одном из двух стабильных состояний, требуется некоторое количество энергии, чтобы перевести ее из этого состояния в другое стабильное состояние.

При переходе между состояниями выходной сигнал должен проходить через область, в которой он нестабилен. Схемы памяти устроены так, что они не могут оставаться в нестабильном состоянии бесконечно — как только они входят в нестабильное состояние, они немедленно пытаются восстановить одно из двух стабильных состояний.

Любая логическая схема может иметь обратную связь, если выходной сигнал просто «подается обратно» и подключается к входу.

учиться, основы, схемы, схемы памяти

Интегральные схемы памяти – NetSource Technology

Интегральные схемы памяти (ИС) лежат в основе практически всей современной электроники, позволяя системам эффективно хранить данные для краткосрочного или долгосрочного хранения. В NetSource Technology, Inc. мы помогаем компаниям определить и приобрести именно те микросхемы памяти, которые им нужны для их приложений. Являясь одним из ведущих в мире независимых дистрибьюторов электронных компонентов, NetSource предлагает комплексные услуги по закупкам и цепочке поставок производителям по всему миру.

С 1997 года NetSource сотрудничает с OEM-производителями и контрактными производителями, чтобы обнаруживать даже самые малоизвестные электронные компоненты, включая устаревшие, отслужившие свой срок и высокораспределенные I/C. Мы используем обширную глобальную сеть для поиска необходимых компонентов, независимо от их ниши. Мы также поддерживаем обширный ассортимент новых компонентов от ведущих поставщиков электроники, что позволяет нам быстро выполнять заказы на новые и востребованные ИС.

Ищете ли вы совершенно новую технологию или компонент, производство которого было прекращено в течение десяти лет, отраслевые эксперты NetSource могут отследить его быстрее, чем кто-либо другой. Имея на складе сотни микросхем памяти и команду преданных своему делу специалистов по поиску, мы полностью оснащены для решения любых задач цепочки поставок.

Что такое интегральная схема памяти?

Интегральные схемы (ИС), также называемые микросхемами, представляют собой интегральные вычислительные компоненты, состоящие из миниатюрных резисторов, конденсаторов и транзисторов, размещенных на полупроводнике. Эти микросхемы могут быть как аналоговыми, так и цифровыми, и их можно использовать для любого количества вычислительных функций. I/C памяти используют изменения напряжения для хранения данных в компьютере, включая не только файлы и программы, но и временную информацию о состояниях обработки.

Эти микросхемы могут быть как аналоговыми, так и цифровыми, и их можно использовать для любого количества вычислительных функций. I/C памяти используют изменения напряжения для хранения данных в компьютере, включая не только файлы и программы, но и временную информацию о состояниях обработки.

I/C с цифровой памятью выполняют все эти функции через логические вентили, которые могут считывать и выражать только двоичный ввод. Поверхность чипа памяти покрыта массивами ячеек памяти, каждая из которых содержит конденсатор и один или несколько транзисторов. Каждая ячейка хранит один бит двоичных данных в зависимости от состояния ее схемы. Группа этих ячеек определяет адрес памяти, также называемый строкой слов, к которым компьютер обращается вместе, чтобы либо сохранить, либо получить порцию данных.

Современные микросхемы памяти могут хранить огромные объемы данных благодаря микроскопическим размерам их схем. Цифровая микросхема размером с горошину может разместить на своей поверхности сотни тысяч транзисторов, поэтому микросхема памяти стандартного размера может легко похвастаться миллионами параллельных цепей.

Как работает интегральная схема?

Конденсаторы в ячейке памяти хранят данные, а транзисторы активируют данные. Конденсатор может хранить только два значения в зависимости от того, заряжен он (1) или разряжен (0). В микросхемах динамической памяти, таких как микросхемы оперативной памяти (ОЗУ), эти значения можно легко изменить, но данные обычно теряются при отключении питания устройства. Данные на микросхемах постоянной памяти (ПЗУ) гораздо более стабильны и их труднее изменить.

Чтобы изменить значение бита данных, электрические сигналы могут нацеливаться на ячейку и изменять состояние заряда ее конденсатора, тем самым изменяя значение, хранящееся в адресе памяти. Электрические сигналы также могут считывать данные по определенной строке слов в зависимости от состояния конденсаторов. Если конденсатор содержит заряд, электрический сигнал вызовет изменение напряжения на соответствующих транзисторах. Последовательность активаций создает серию нулей и единиц, которые передают данные на компьютер.

I/C памяти от NetSource Technology

Правильный выбор I/C памяти может значительно повысить эффективность продукта и помочь уменьшить размер и вес. NetSource предлагает широкий спектр высокопроизводительных интегральных схем памяти, подходящих OEM-производителям и контрактным производителям из всех секторов промышленности. Наш каталог включает такие признанные линии, как:

- Контроллеры памяти Elpida. Дочерняя компания Micron, Elpida Memory, является ведущим производителем микросхем динамической памяти с произвольным доступом (DRAM). Продукция Elpida известна во всей отрасли своей превосходной скоростью и производительностью в тонком корпусе с низким энергопотреблением. Приложения включают персональные компьютеры, мобильные устройства и потребительские электронные товары, а также серверы и промышленную электронику.

- Мобильная память SK hynix. Микросхемы памяти SK hynix Mobile Memory, идеально подходящие для мобильных приложений, отличаются превосходной плотностью памяти и высокой пропускной способностью при эффективной работе с несколькими банками.

SK hynix — мировой лидер в производстве DRAM и полупроводников, предлагающий инновационные чипы для мирового компьютерного рынка.

SK hynix — мировой лидер в производстве DRAM и полупроводников, предлагающий инновационные чипы для мирового компьютерного рынка. - Чипы памяти для мобильных устройств Micron. Микросхемы памяти для мобильных устройств Micron предназначены для удовлетворения постоянно растущих потребностей рынка сверхтонких мобильных устройств. Micron специализируется на микросхемах DRAM с низким энергопотреблением (LPDRAM), которые сочетают в себе низкое энергопотребление и высокую производительность в различных операционных средах.

- Контроллеры памяти Winbond. Winbond — тайваньский производитель специализированной памяти DRAM с глобальным присутствием. Контроллеры памяти Winbond отличаются особой гибкостью, высокой плотностью размещения и возможностями для устройств с ограниченным пространством, выводами и питанием.

- Чипы памяти Samsung DRAM для мобильных устройств. Компания Samsung, являющаяся лидером в производстве мобильных устройств, также поставляет передовые чипы памяти для мобильных устройств производителям по всему миру.

Недавно они стали первой компанией, выпустившей 16-гигабайтную мобильную память DRAM с удвоенной скоростью передачи данных (LPDDR5) с низким энергопотреблением, которая обещает непревзойденную производительность для мобильных игр и видеозвонков.

Недавно они стали первой компанией, выпустившей 16-гигабайтную мобильную память DRAM с удвоенной скоростью передачи данных (LPDDR5) с низким энергопотреблением, которая обещает непревзойденную производительность для мобильных игр и видеозвонков.

В дополнение к продаже чипов памяти, мы также нанимаем специальную команду по закупкам, чтобы помочь клиентам, которым нужны редкие или устаревшие интегральные схемы памяти.

Доверьтесь NetSource для контроллеров памяти

На протяжении более двух десятилетий клиенты доверяют NetSource в отношении современных и устаревших электронных компонентов. Как поставщик, сертифицированный по стандарту ISO 9001:2015 и зарегистрированный в ITAR, мы гордимся нашими протоколами управления качеством и используем самые строгие процедуры проверки подлинности продуктов для защиты клиентов от подделок. Кроме того, мы зарекомендовали себя как эксперты по критическим дефицитам с глобальным охватом, поэтому вы можете доверять NetSource в приобретении именно тех компонентов, которые вам нужны, когда они вам нужны.