ПРЯМОЙ ЦИФРОВОЙ СИНТЕЗ

ПРЯМОЙ ЦИФРОВОЙ СИНТЕЗ (DDS)

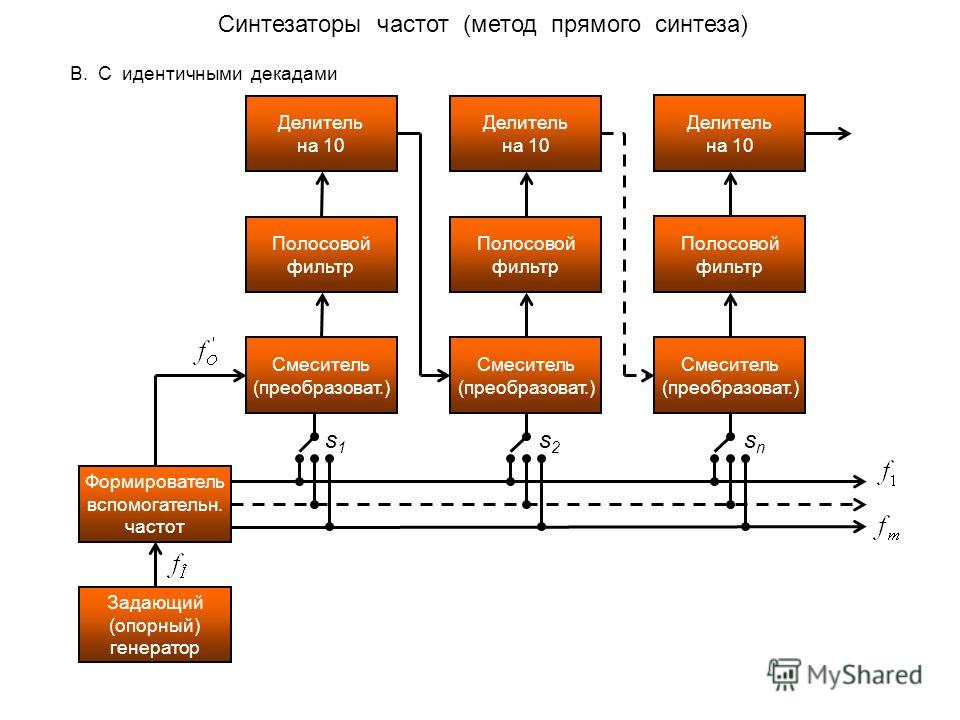

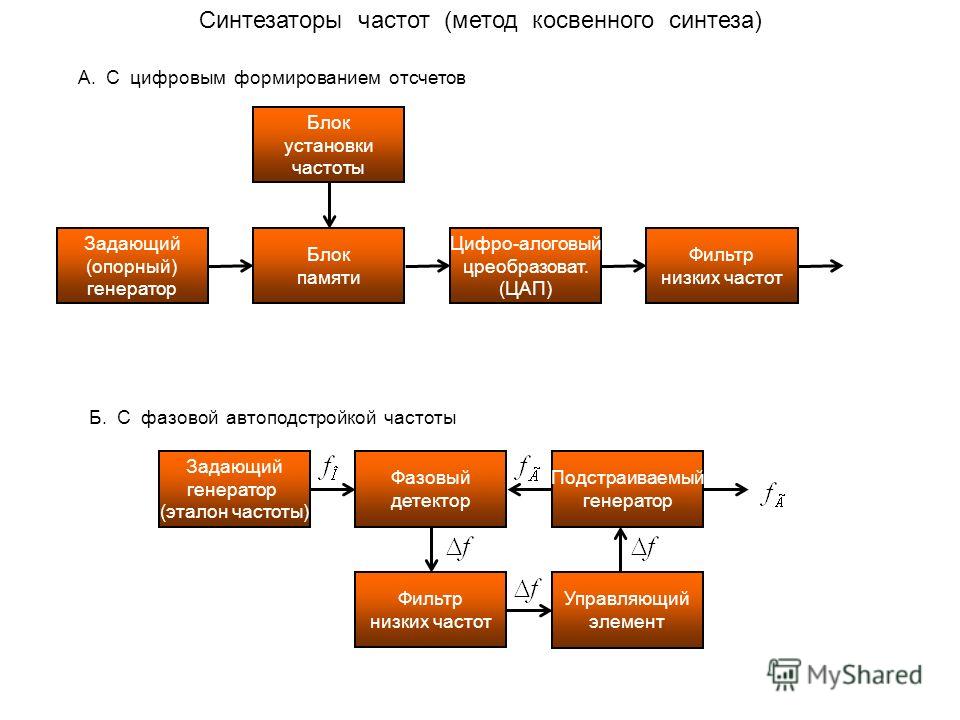

Частотные синтезаторы используется

для генерации некоторого множества

частот на одном или большем числе опорных

частот. Эти устройства используются в

течение десятилетий, особенно в

коммуникационных системах. Многие из

них основаны на переключении и смешивании

частотных выходов от группы кварцевых

генераторов. В основе других лежат

известные методы использования цепей

с фазовой автоподстройкой частоты

(ФАПЧ). Эта традиционная технология

представлена на рис.4.13. Опорная

фиксированная частота подается на один

из входов компаратора фазы. Другой вход

компаратора фазы подключается к делителю

частоты на N, на который, в свою очередь,

подается сигнал от генератора, управляемого

напряжением (ГУН). Наличие отрицательной

обратной связи приводит к тому, что

сигнал на выходе фильтра, включенного

в контур обратной связи, принимает такое

значение, которое делает выходную

частоту ГУН равной N-кратной опорной

частоте.

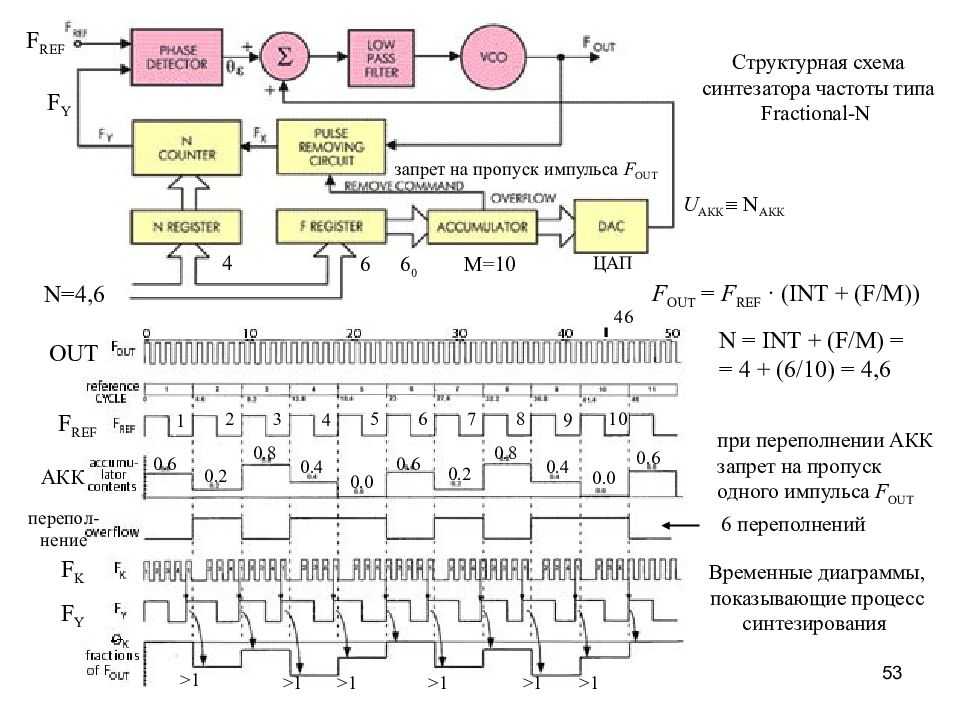

Рис. 4.13. Частотный синтез с использованием генераторов и цепей фазовой автоподстройки частоты (ФАПЧ)

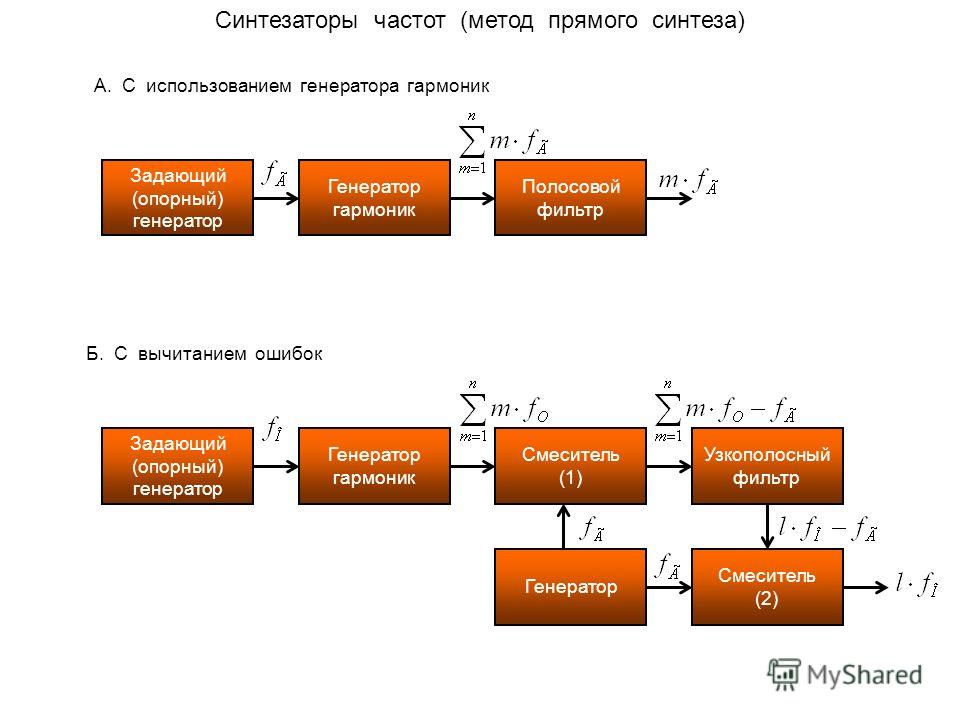

В связи с широким распространением

цифровых методов в измерительных и

коммуникационных системах, метод

генерации набора частот от источника

опорной частоты, реализуемый в цифровой

форме, развился в так называемый метод

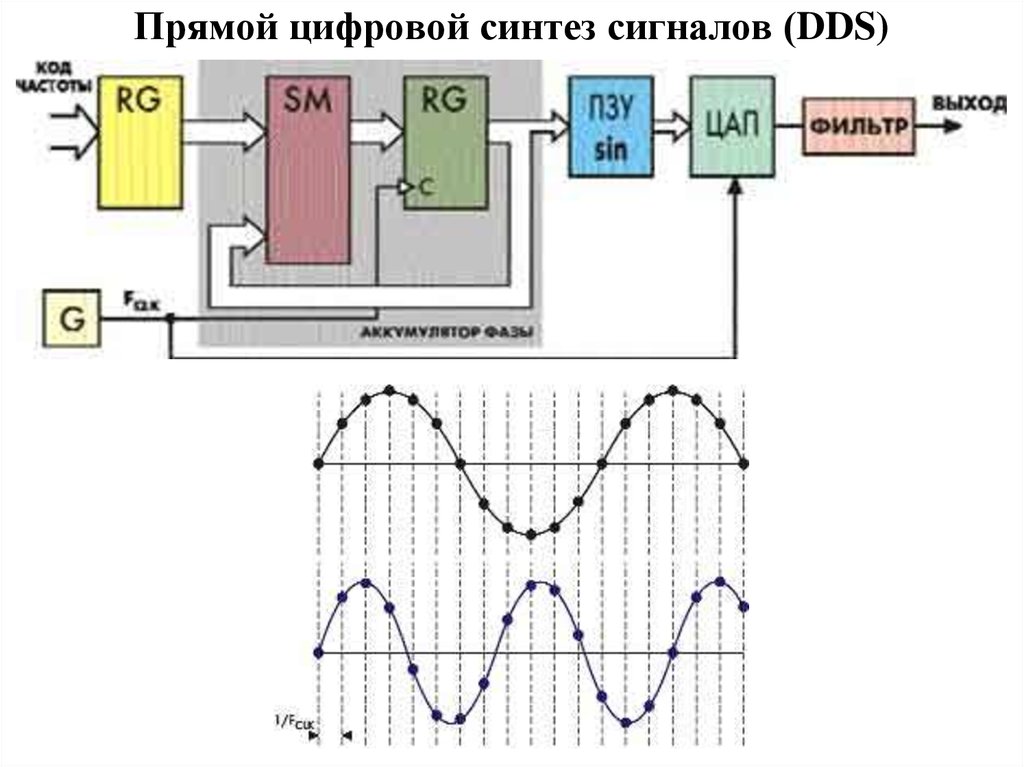

прямого цифрового синтеза (DDS). Основная

его архитектура представлена на рис.4.14.

В этой упрощенной модели, стабильный

генератор тактового сигнала управляет

программируемым ПЗУ (PROM), который хранит

один или большее целое число циклов

синусоидального сигнала (или другого

сигнала произвольной формы). По мере

того, как адресный счетчик проходит

через каждую ячейку памяти, соответствующая

цифровая амплитуда сигнала из каждой

ячейки подается на ЦАП, который, в свою

очередь, воспроизводит аналоговый

выходной сигнал.

Рис. 4.14. Система прямого цифрового синтеза (DDS)

Система прямого цифрового синтеза (DDS) отличается от ФАПЧ несколькими моментами. В связи с дискретной природой DDS должны быть рассмотрены все проблемы, присутствующие в процессе дискретизации: шум квантования, наложение спектров, фильтрация и т.д. Например, гармоники высокого порядка выходных частот ЦАП, попадая обратно в полосу Найквиста, больше не фильтруются, тогда как гармоники высокого порядка в выходном сигнале ФАПЧ-синтезаторов могут быть отфильтрованы.

Основная проблема этой простой DDS-системы

состоит в том, что выходная частота

может быть изменена только путем

изменения частоты задающего генератора

или посредством перепрограммирования

ПЗУ, что делает систему весьма негибкой.

На практике DDS-система осуществляет эту

основную функцию намного более гибким

и эффективным способом, используя

цифровую схему, называемую генератором

с цифровым управлением (Numerically Controlled

Oscillator, NCO). Блок-схема такой системы

представлена на рис.4.15.

Блок-схема такой системы

представлена на рис.4.15.

Рис. 4.15. Гибкая система прямого цифрового синтеза (DDS)

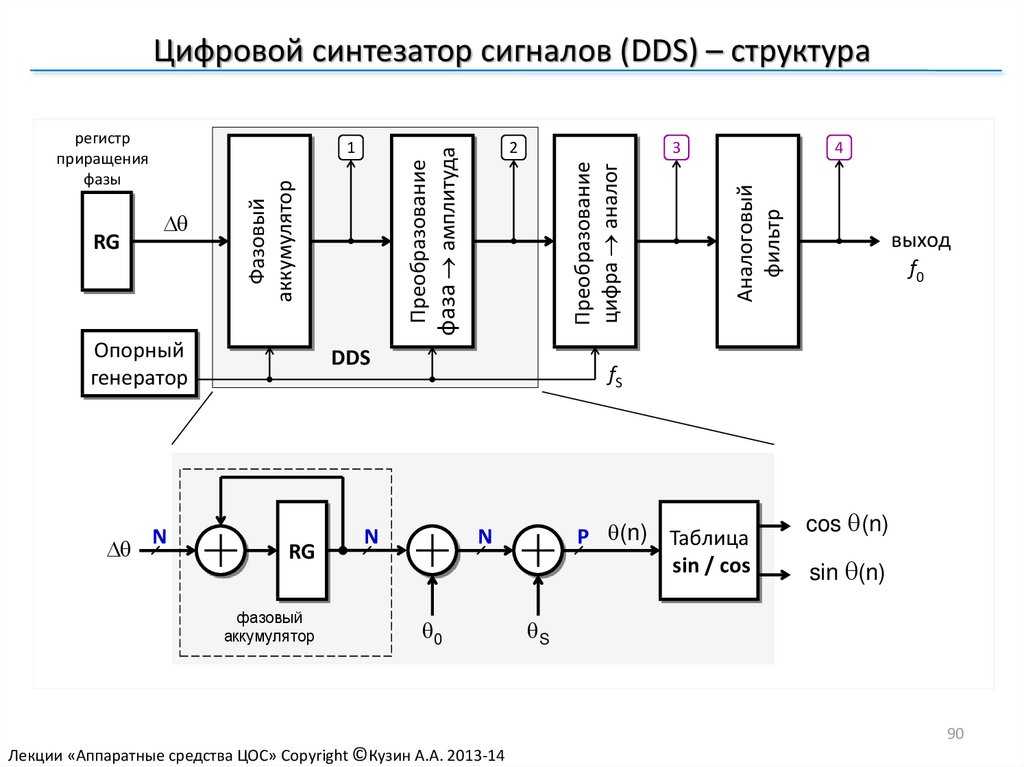

Сердцем системы является сумматор фазы, содержимое которого обновляется однократно за каждый тактовый цикл. Каждый раз при обновлении сумматора фазы цифровое число М, сохраненное в регистре приращения фазы (delta phase register), добавляется к числу в сумматоре фазы. Предположим, что число в delta-регистре равно 00…01 и что начальное содержимое сумматора фазы равно 00…00. Сумматор фазы обновляется значением 00…01 каждый тактовый цикл. Если сумматор является 32-разрядным, для возврата сумматора фазы в состояние 00…00 требуется 2 32 тактовых цикла (более 4 миллиардов), после чего цикл повторяется.

Усеченное значение выходного сигнала

сумматора фазы служит адресом для

таблицы задания синуса (или косинуса).

Каждый адрес в таблице соответствует

точке синусоидального сигнала с фазой

от 0° до 360°. Таблица поиска содержит

информацию, соответствующую цифровой

амплитуде для одного полного цикла

синусоидального сигнала (в действительности,

требуются только данные для 90°, потому

что данные о квадранте содержатся в

двух старших значащих разрядах). Таким

образом, таблица отображает фазу

синусоидального сигнала сумматора фазы

в виде значения цифровой амплитуды,

которое, в свою очередь, подается на

ЦАП.

Таблица поиска содержит

информацию, соответствующую цифровой

амплитуде для одного полного цикла

синусоидального сигнала (в действительности,

требуются только данные для 90°, потому

что данные о квадранте содержатся в

двух старших значащих разрядах). Таким

образом, таблица отображает фазу

синусоидального сигнала сумматора фазы

в виде значения цифровой амплитуды,

которое, в свою очередь, подается на

ЦАП.

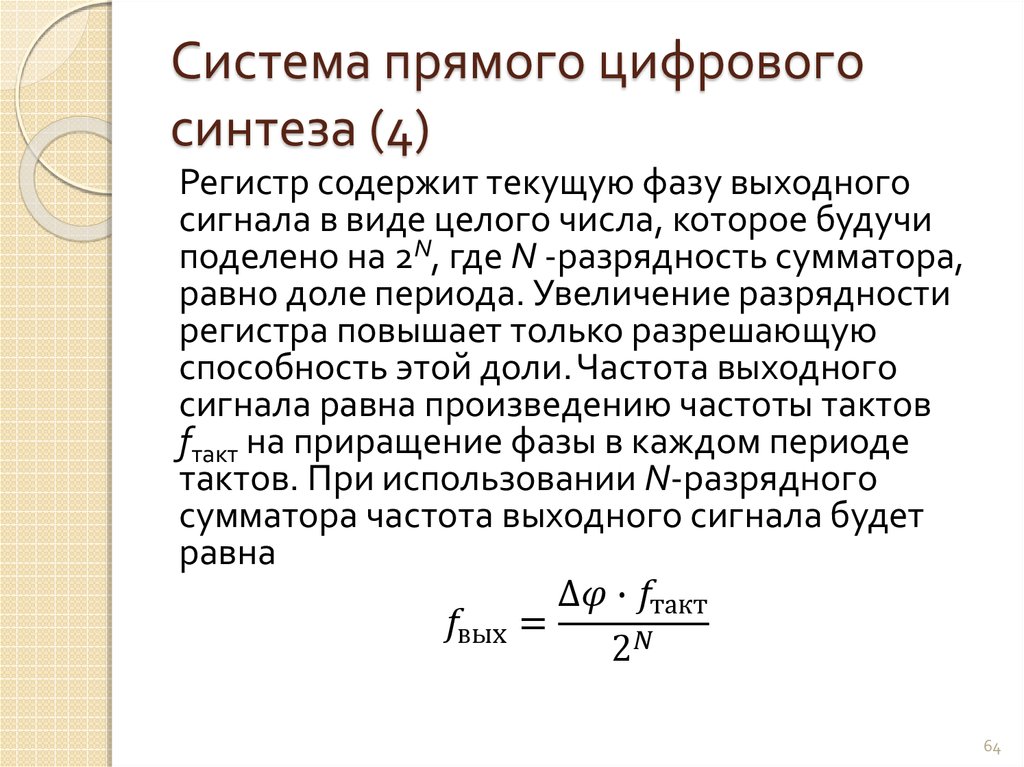

Рассмотрим случай для n=32 и M=1. Сумматор фазы проходит через каждое из 232 возможных значений выхода перед переполнением. Соответствующая частота выходного синусоидального сигнала равна частоте синхронизации, деленной на 232. Если M=2, то число в регистре сумматора фазы успевает дважды смениться, и выходная частота удваивается. Это можно обобщить следующим образом.

Для n-разрядного сумматора фазы (в

большинстве DDS-систем значение n лежит

в диапазоне от 24 до 32) существует 2n возможных значений фазы. Число М в

регистре приращения фазы представляет

собой величину, на которую текущее

значение фазы увеличивается в каждом

тактовом цикле.

Это уравнение известно как уравнение настройки DDS. Обратите внимание, что разрешающая способность системы по частоте равна fc/2n. Таким образом, для n=32 разрешающая способность больше, чем один к четырем миллиардам. В реальной DDS-системе не все разряды от сумматора фазы используются для выбора значения из таблицы, оставляются только первые 12-16 старших значащих разрядов (MSB), тогда как младшие разряды игнорируются. Это уменьшает размер таблицы и не ухудшает разрешающую способность по частоте. Усечение разрядности фазы только добавляет незначительное, но приемлемое количество фазового шума к окончательному выходному сигналу; тогда как большая часть выходных искажений возникает непосредственно в ЦАП.

Описанная выше базовая DDS-система

представляет чрезвычайно гибкое решение

с весьма высокой разрешающей способностью.

DDS-система AD9850 быстродействием 125MSPS

(рис.4.16) использует 32-разрядный сумматор

фазы, выход которого, перед тем как он

используется для адресации в таблице,

ограничивается 14-тью старшими разрядами.

На внутренний ЦАП подается окончательный

выходной 10-разрядный цифровой сигнал.

Рис. 4.16. CMOS-синтезатор DDS/ЦАП AD9850 с быстродействием 125 MSPS

Настройка частоты (входное слово регистра

приращения фазы) и значения загружаются

для фазовой модуляции в AD9850 в параллельном

или последовательном формате. Параллельный

формат подразумевает загрузку пяти

байтов. Первый байт управляет фазовой

модуляцией (5 разрядов), активизацией

выключения питания (1 разряд) и форматом

загрузки (2 разряда). В байтах 2-5 содержится

32-разрядное слово настройки частоты.

Максимальная частота обновления

управляющего регистра равна 23 МГц.

Последовательная загрузка AD9850 выполняется

с использования 40-разрядного

последовательного потока данных,

загружаемого через один вывод микросхемы.

Максимальная скорость (частота) обновления

управляющего регистра в режиме

последовательной загрузки равна 3 МГц.

Параллельный

формат подразумевает загрузку пяти

байтов. Первый байт управляет фазовой

модуляцией (5 разрядов), активизацией

выключения питания (1 разряд) и форматом

загрузки (2 разряда). В байтах 2-5 содержится

32-разрядное слово настройки частоты.

Максимальная частота обновления

управляющего регистра равна 23 МГц.

Последовательная загрузка AD9850 выполняется

с использования 40-разрядного

последовательного потока данных,

загружаемого через один вывод микросхемы.

Максимальная скорость (частота) обновления

управляющего регистра в режиме

последовательной загрузки равна 3 МГц.

Потребляемая мощность AD9850 составляет

380 мВт с однополярным источником питания

+5 В при максимальном быстродействии

125 MSPS. Устройство выпускается в

28-контактном корпусе для поверхностного

монтажа SSOP (Shrink Small Outline Package). Также в

качестве примера можно привести

устройства фирмы Analog Devices, предлагающей

системы прямого цифрового синтеза (DDS)

для разнообразных приложений. Семейство

AD983X представляет недорогие 10-разрядные

системы с частотами синхронизации до

50 MSPS. Семейство AD985x предлагает 10-разрядные

и 12-разрядные системы с синхронизации

до 300 MSPS и дополнительными функциями,

такими, как квадратурная и фазовая

модуляция, возможность режима импульсного

сигнала с ЧМ и программируемые,

интегрированные на кристалле умножители

частоты задающего генератора.

Семейство AD985x предлагает 10-разрядные

и 12-разрядные системы с синхронизации

до 300 MSPS и дополнительными функциями,

такими, как квадратурная и фазовая

модуляция, возможность режима импульсного

сигнала с ЧМ и программируемые,

интегрированные на кристалле умножители

частоты задающего генератора.

DEVELOPMENT OF DIGITAL FREQUENCY SYNTHESIZER PLD BASED FOR NQR PULSE FOURIER SPECTROMETER

Research article

Samila A.P.

Issue: № 12 (19), 2013

Published:

2014/01/16

Самила А.П.

Кандидат технических наук, Черновицкий национальный университетимени Юрия Федьковича, Украина

РАЗРАБОТКА ЦИФРОВОГО СИНТЕЗАТОРА ЧАСТОТ НА ПЛИС ДЛЯ ИМПУЛЬСНОГО ФУРЬЕ-РАДИОСПЕКТРОМЕТРА ЯКР

Аннотация

Разработан синтезатор частот на программируемой логической интегральной схеме с использованием метода прямого цифрового синтеза сигналов. Устройство испытывалось в составе формирователя последовательностей импульсов возбуждения сигнала спиновой индукции импульсного Фурье-радиоспектрометра ядерного квадрупольного резонанса. Диапазон рабочих частот составляет 1÷50 МГц а минимальная длительность формируемого радиоимпульса – 100 нс.

Диапазон рабочих частот составляет 1÷50 МГц а минимальная длительность формируемого радиоимпульса – 100 нс.

Ключевые слова: прямой цифровой синтез, ПЛИС, спектрометр ЯКР.

Samila A.P.

PhD in Engineering, Yuriy Fedkovych Chernivtsi National University, Ukraine

DEVELOPMENT OF DIGITAL FREQUENCY SYNTHESIZER PLD BASED FOR NQR PULSE FOURIER SPECTROMETER

Abstract

Frequency synthesizer designed for programmable logic device using the direct digital synthesis signal. The device was tested as a part of sequencer for pulse Fourier spectrometer of nuclear quadrupole resonance. Operating frequency range is 1 ÷ 50 MHz and the minimum duration of the formed pulse – 100 ns.

Keywords: direct digital synthesis, PLD, NQR spectrometer.

Формирование высокочастотных колебаний на основе метода прямого цифрового синтеза (Direct Digital Synthesizers или DDS) в последнее время находит широкое применения в радиоэлектронных устройствах и системах телекоммуникаций [1,2]. Прямой цифровой синтез – относительно новый метод синтеза частоты, появившийся в начале 70-х годов прошлого века. Однако, только в последнее время DDS уделяется пристальное внимание, что обусловлено повышением степени интеграции цифровых устройств позволяющее значительно снизить времена задержки прохождения сигналов. Объединение в одном чипе быстродействующего цифро-аналогового преобразователя (ЦАП) и DDS позволило получить весьма заманчивую альтернативу обычным синтезаторам на основе фазовой автоподстройки частоты (ФАПЧ). Интегральные однокристальные синтезаторы частоты (Complete DDS) широко используются в качестве источников колебаний несущих частот при разработке портативных систем связи, лабораторного и учебного оборудования. Кроме того, заслуживают внимания генераторы с числовым управлением без встроенного ЦАП – Numerically Controlled Oscillator (NCO), которые предназначены для построения высокоскоростных синтезаторов частоты (информационное вещание, медицинское оборудование, научно-исследовательские лаборатории, и др.

Прямой цифровой синтез – относительно новый метод синтеза частоты, появившийся в начале 70-х годов прошлого века. Однако, только в последнее время DDS уделяется пристальное внимание, что обусловлено повышением степени интеграции цифровых устройств позволяющее значительно снизить времена задержки прохождения сигналов. Объединение в одном чипе быстродействующего цифро-аналогового преобразователя (ЦАП) и DDS позволило получить весьма заманчивую альтернативу обычным синтезаторам на основе фазовой автоподстройки частоты (ФАПЧ). Интегральные однокристальные синтезаторы частоты (Complete DDS) широко используются в качестве источников колебаний несущих частот при разработке портативных систем связи, лабораторного и учебного оборудования. Кроме того, заслуживают внимания генераторы с числовым управлением без встроенного ЦАП – Numerically Controlled Oscillator (NCO), которые предназначены для построения высокоскоростных синтезаторов частоты (информационное вещание, медицинское оборудование, научно-исследовательские лаборатории, и др. ).

).

Предлагаемое разработчиками оборудование формирования импульсов возбуждения ядерной спиновой индукции для ядерных резонансных и релаксационных исследований обладает рядом недостатков. В частности, большинство из них исполнены в виде плат расширения персонального компьютера и требуют написания специализированного программного обеспечения, что накладывает ограничения на их мобильность [3]. Кроме того, в силу своей широкой функциональности, и соответственно, высокой цены такие устройства зачастую недоступны для большинства научных лабораторий.

В данной работе предложен цифровой синтезатор частот для импульсного Фурье-радиоспектрометра ядерного квадрупольного резонанса (ЯКР) с диапазоном 1÷50 МГц, который обеспечивает возможность работать с частотами наиболее актуальных с точки зрения исследований ядер изотопов 14N, 35Cl 63Cu, 69Ga, 71Ga, 113In, 115In и др.

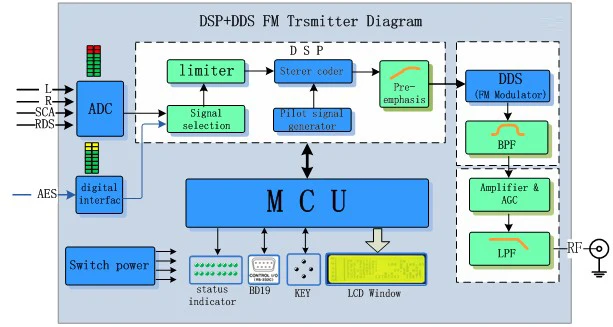

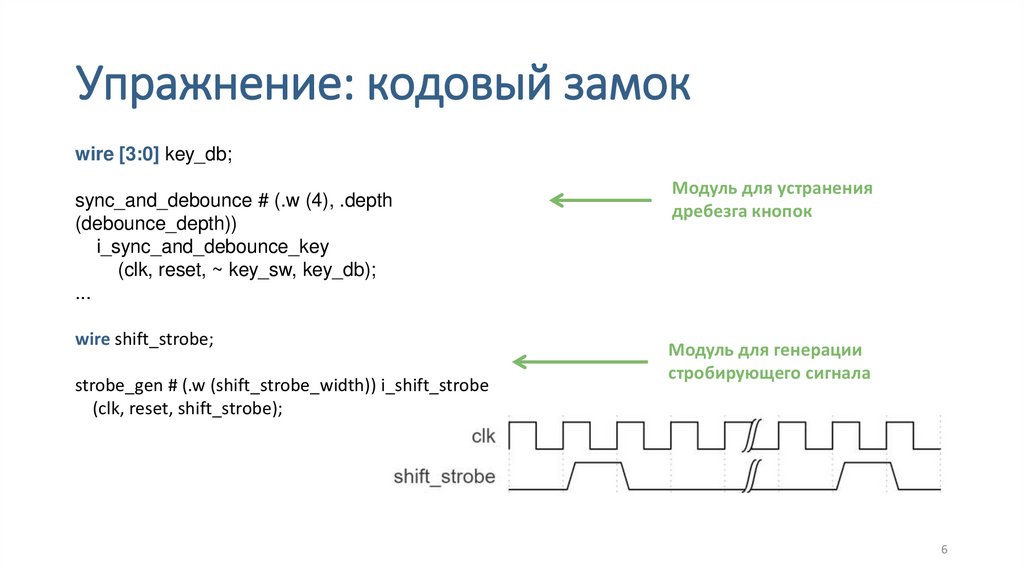

Структура предложенного синтезатора включает генератор с числовым управлением, постоянное запоминающее устройство (ПЗУ), фильтр нижних частот (ФНЧ), ЦАП и систему управления. В основе предложенной разработки лежит программированная логическая интегральная микросхема (ПЛИС) EP1C6Q240C8 [4] от фирмы Altera, использование которой позволило создать не только несущее колебание со строго заданной частотой и начальной фазой, но и гибкую систему формирования когерентных импульсов возбуждения сигналов ЯКР.

В основе предложенной разработки лежит программированная логическая интегральная микросхема (ПЛИС) EP1C6Q240C8 [4] от фирмы Altera, использование которой позволило создать не только несущее колебание со строго заданной частотой и начальной фазой, но и гибкую систему формирования когерентных импульсов возбуждения сигналов ЯКР.

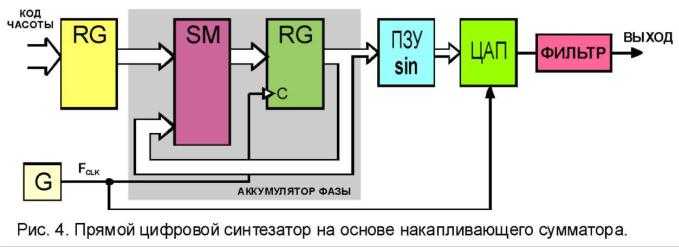

Рис. 1 – Цифровая часть синтезатора на основе ПЛИС

Цифровая часть синтезатора изображенного на рис. 1 построена средствами моделирования и разработки для сверхбольших интегральных схем и систем-на-кристалле от Altera [5]. Основой устройства является 48-битный аккумулятор фазы «altaccumulate0», формирующий линейно изменяющуюся последовательность кодов мгновенной фазы сигнала. Расчет табличных значений одного периода гармонического колебания, изменяющегося по закону y=sinx осуществлен в программной среде Origin Pro v8 [6] (рис. 2). Период колебания разбиваем на 210 8-битных отсчетов. Циклически повторяющиеся значения отсчетов выходного сигнала, записанные в таблицу ПЗУ «DDS_rom» реализуют формирование выходного сигнала DDS в виде периодической функции y(t)=A·sin(2πf·t+φ).

Модуль «PLL1» является программированной системой ФАПЧ, использование которой позволяет обеспечить формирование колебаний с частотой fclk=250 МГц при использовании внешнего тактового генератора работающего на частоте 50 МГц. Модули «phase_mux», «phase_adder» и «phase_reg» служат для осуществления двоичной фазовой манипуляции несущей частоты виходного сигнала DDS. Умножитель «mult 1» обеспечивает возможность ввода входного кода частоты непосредственно в виде числовой константы соответствующей предполагаемому числовому значению генерируемой частоты. Он умножает входной код частоты K1 на константу К2=11258999 задающую шаг перестройки синтезатора равный Δf=10 Гц.

Рис. 2 – Окно симуляции Waveform simcurve

Зависимость частоты сигнала fout на выходе генератора с числовым управлением зависит от опорной тактовой частоты fclk, разрядности аккумулятора фазы M и кода частоты К определяется следующим выражением [2]:

(1)

При этом шаг перестройки частоты не зависит от ее значения и равен:

(2)

В нашем случае рабочая частота накапливающего сумматора разрядностью М=48 бит равна fclk=250 МГц. Таким образом, шаг перестройки частоты будет составлять Δfout≈1×10-6 Гц. Следовательно, для формирования сигнала с частотой fout на вход «Fr_ctrl30[23..0]» синтезатора необходимо подать 24-битный код частоты, который рассчитывают с выражения:

Таким образом, шаг перестройки частоты будет составлять Δfout≈1×10-6 Гц. Следовательно, для формирования сигнала с частотой fout на вход «Fr_ctrl30[23..0]» синтезатора необходимо подать 24-битный код частоты, который рассчитывают с выражения:

(3)

Умножитель «AM_MUX» обеспечивает возможность регулировки амплитуды выходного сигнала DDS. Кодовое слово регулировки амплитуды разрядностью 8 бит подается на порт «Amp_ctrl[7..0]». Фазовая манипуляция осуществляется через порт «Fin_ctrl».

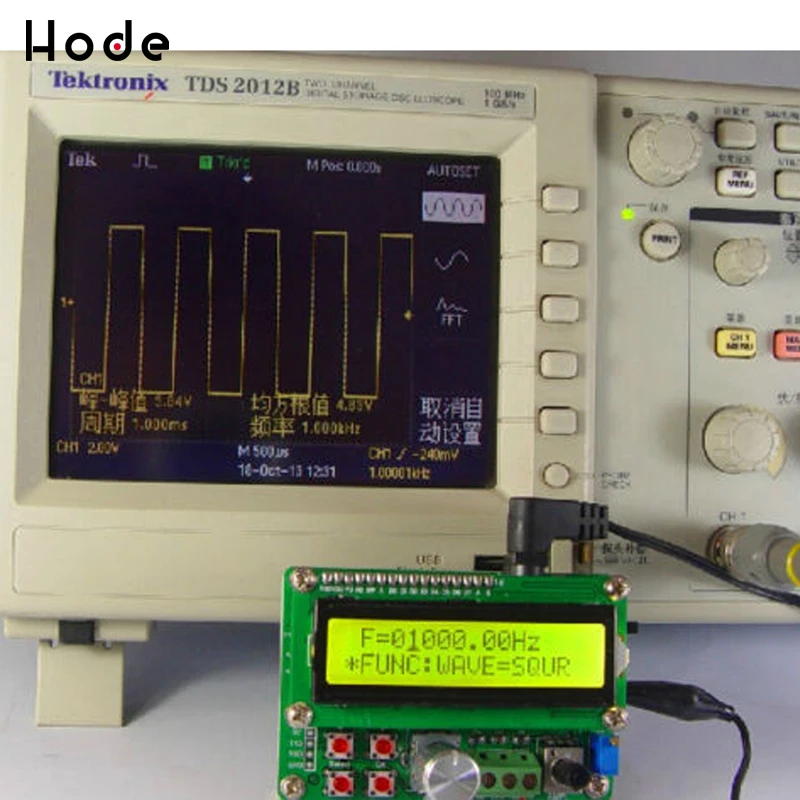

Цифро-аналоговое преобразование выходного сигнала осуществляется внешним ЦАП AD9708 с дальнейшей фильтрацией аналоговым ФНЧ. Согласование выходного сопротивления синтезатора с внешними устройствами осуществляется с использованием операционного усилителя MAX4450 с полосой пропускания 55 МГц при неравномерности АЧХ ±0,1 дБ и Rail-to-Rail выходом. Спектры выходного сигнала синтезатора для крайних частот рабочего диапазона приведены на рис. 3, а осциллограмма выходного напряжения на рис. 4, а.

3, а осциллограмма выходного напряжения на рис. 4, а.

Рис. 3 – Спектры выходного сигнала DDS: а – частота 1 МГц, б – частота 50 МГц

Предложенный синтезатор частот испытывался в составе формирователя последовательностей импульсов возбуждения сигнала спиновой индукции (ССИ). Отметим, что синтезатор и формирователь разработаны на одной ПЛИС, что обеспечивает минимальные задержки прохождения сигнала и соответственно возможность формирования последовательностей коротких радиоимпульсов (рис. 4, б). Значение длительности импульсов и паузы могут принимать заданные значения в диапазоне 0,1÷12 мкс и 0,1 мкс÷1 с соответственно.

Рис. 4 – Осциллограммы выходных сигналов DDS: а – непрерывная генерация (частота 50 МГц), б – работа в составе формирователя последовательности импульсов возбуждения ССИ (частота несущей 26,006 МГц)

Исследования показали, что параметры использованной ПЛИС не позволяют получить тактовые частоты для ЦАП более 250 МГц.![]() Для работы на более высоких частотах рассматривается разработка устройства на основе чипа семейства Altera Cyclone® V или Altera Stratix®. Это обеспечит возможность использовать цифро-аналоговые преобразователи со скоростью преобразования более 1 Гвыб/с.

Для работы на более высоких частотах рассматривается разработка устройства на основе чипа семейства Altera Cyclone® V или Altera Stratix®. Это обеспечит возможность использовать цифро-аналоговые преобразователи со скоростью преобразования более 1 Гвыб/с.

References

Основы прямых цифровых синтезаторов (DDS)

По мере распространения беспроводных устройств разработчики используют все более сложные и переменные формы сигналов для удовлетворения требований приложений с точки зрения скорости передачи данных, подавления помех, стоимости, занимаемой площади и низкого энергопотребления. Для этих сигналов требуются стабильные ВЧ-источники, которые можно настраивать по требованию и которые могут изменять частоту и фазу. При этом источники также должны обеспечивать высокую степень чистоты сигнала. Решение этой матрицы требований лежит в прямых цифровых синтезаторах (DDS).

DDS генерирует аналоговые сигналы с использованием цифровых методов, что позволяет использовать преимущества программируемости цифровых технологий, более высокий уровень интеграции и более низкую стоимость. Кроме того, DDS обеспечивает почти мгновенное изменение частоты или фазы, что делает его основным источником передовых методов цифровой модуляции, таких как частотная манипуляция (FSK) и расширение спектра, а также использование методов подавления помех, таких как скачкообразная перестройка частоты. В результате микросхемы DDS быстро заменяют или дополняют традиционные схемы фазовой автоподстройки частоты (ФАПЧ) и другие аналоговые источники ВЧ, при этом обеспечивая высокую стабильность и чистоту сигнала.

Кроме того, DDS обеспечивает почти мгновенное изменение частоты или фазы, что делает его основным источником передовых методов цифровой модуляции, таких как частотная манипуляция (FSK) и расширение спектра, а также использование методов подавления помех, таких как скачкообразная перестройка частоты. В результате микросхемы DDS быстро заменяют или дополняют традиционные схемы фазовой автоподстройки частоты (ФАПЧ) и другие аналоговые источники ВЧ, при этом обеспечивая высокую стабильность и чистоту сигнала.

В этой статье рассматриваются основы технологии DDS и описание микросхемы DDS. Затем будут представлены некоторые подходящие решения DDS IC и показано, как их эффективно применять.

Как работает прямой цифровой синтез

Цифровой синтез основан на накопителе фазы, который генерирует ряд цифровых состояний, значение которых линейно увеличивается, образуя числовую рампу. Этот сигнал делается периодическим и представляет собой мгновенную фазу выходного сигнала от нуля до 2p радиан. Это цифровой вход в справочную таблицу, которая преобразует числовое линейное изменение в синусоиду (рис. 1). Хотя наиболее распространенной формой выходного сигнала DDS является синусоида; рампы, треугольные волны и прямоугольные волны также легко генерируются.

Это цифровой вход в справочную таблицу, которая преобразует числовое линейное изменение в синусоиду (рис. 1). Хотя наиболее распространенной формой выходного сигнала DDS является синусоида; рампы, треугольные волны и прямоугольные волны также легко генерируются.

Рисунок 1: Прямой цифровой синтезатор основан на накопителе фазы, который генерирует мгновенную фазу сигнала. Справочная таблица обеспечивает преобразование фазы в амплитуду, которое применяется к цифро-аналоговому преобразователю, производя желаемый аналоговый выход после фильтрации. (Источник изображения: Digi-Key Electronics)

Вывод таблицы преобразования фазы в амплитуду отправляется на цифро-аналоговый преобразователь (ЦАП) и преобразуется в аналоговый сигнал, который чаще всего имеет синусоидальную форму. Поскольку вход в ЦАП представляет собой серию выборочных значений, выход имеет шаги квантования. Эти этапы создают спектральные изображения с частотой дискретизации в частотной области, кратной частоте, что нежелательно. Фильтр нижних частот, расположенный после ЦАП, подавляет эти нежелательные спектральные характеристики.

Фильтр нижних частот, расположенный после ЦАП, подавляет эти нежелательные спектральные характеристики.

Накопитель фазы

Накопитель фазы представляет собой счетчик по модулю N, который имеет 2 N цифровых состояния, которые увеличиваются для каждого входного импульса системных часов. Размер приращения зависит от значения настроечного слова М, применяемого к каскаду сумматора-аккумулятора. Слово настройки фиксирует размер шага приращения счетчика. Это определяет частоту выходного сигнала.

Аккумулятор фазы обычно имеет от 24 до 48 бит; при 24 битах 2 24 или 16 777 216 штатов. Это число представляет количество значений фазы от 0 до 2p радиан или достижимое приращение фазы. Для 24-битного накопителя фазы разрешение по фазе составляет 3,74 Е-7 радиан. Если используется аккумулятор фазы большего размера, приращение фазы становится еще меньше.

Один из способов визуализировать работу аккумулятора фазы — посмотреть на работу аккумулятора как на фазовое колесо (рис. 2).

2).

Рис. 2: Упрощенное представление работы фазового аккумулятора с 16 состояниями с использованием фазового колеса для визуализации того, как слово настройки влияет на выходную частоту DDS. (Источник изображения: Digi-Key Electronics)

Состояния аккумулятора являются периодическими и изображаются лежащими на окружности. Точки на кружке представляют все фазовые состояния аккумулятора. В данном случае для простоты аккумулятор имеет 16 состояний. Если слово настройки равно единице, как на верхней диаграмме, то приращение шага на каждом такте равно единице, и все состояния выбираются в течение всего периода.

Справа от фазового колеса проецируется аналоговый выход для каждого состояния. Поскольку это квантованное устройство, аналоговый выход сохраняет свое текущее состояние до тех пор, пока часы не переведут фазовое колесо в следующее состояние. Выходной сигнал состоит из одного цикла квантованной синусоиды, содержащей шестнадцать значений.

На нижней диаграмме значение слова настройки установлено равным двум. С этой настройкой выбирается любое другое состояние на фазовом колесе. Аналоговый выход теперь состоит из двух циклов, каждый из которых имеет восемь амплитуд, что в сумме дает шестнадцать состояний. Когда слово настройки установлено на два, выходная частота теперь вдвое превышает ранее полученное значение.

С этой настройкой выбирается любое другое состояние на фазовом колесе. Аналоговый выход теперь состоит из двух циклов, каждый из которых имеет восемь амплитуд, что в сумме дает шестнадцать состояний. Когда слово настройки установлено на два, выходная частота теперь вдвое превышает ранее полученное значение.

Выходная частота DDS устанавливается значением слова настройки и увеличивается пропорционально значению слова настройки. Частота дискретизации остается фиксированной на частоте системных часов, а время между выборками вывода остается постоянным. Выходная частота зависит от приращения слова настройки, так что чем больше значение слова настройки, тем меньше шагов в каждом выходном цикле, тем самым увеличивается частота. Слово настройки можно увеличивать до тех пор, пока не будет всего две выборки за цикл, что приводит выход DDS к частоте Найквиста, или половине тактовой частоты системы. Как правило, DDS ограничен конструкцией, чтобы всегда иметь выходную частоту ниже предела Найквиста.

Наряду с системной тактовой частотой выходная частота DDS также зависит от значения слова настройки и длины аккумулятора. Это выражается уравнением 1:

Уравнение 1

Где:

f out — выходная частота DDS

M — значение слова настройки

f c — тактовая частота системы N3

0 длина аккумулятора фазы

Выходной сигнал аккумулятора фазы, представляющий собой мгновенную фазу выходного сигнала, используется для управления преобразователем фазы в амплитуду. Преобразователь фазы в амплитуду выводит цифровое слово, значение которого представляет собой амплитуду синусоидального сигнала для входной фазы.

Обратите внимание, что количество битов, используемых для управления преобразователем фазы в амплитуду, меньше, чем количество битов, используемых для накопителя фазы. Это называется усечением фазы и используется для уменьшения площади кристалла и энергопотребления цифровых каскадов после накопителя фазы. Хотя это действительно вызывает некоторые паразитные спектральные компоненты, называемые шпорами усечения, они сведены к минимуму благодаря тщательному проектированию.

Причина использования выходного фильтра нижних частот

Сигналы, показанные на рис. 2, имеют большое количество гармоник из-за их ступенчатого характера. В результате требуется фильтр нижних частот для удаления этих спектральных гармоник, а также других паразитных частотных характеристик, возникающих в результате других процессов в DDS.

Например, выходной спектр DDS для устройства с тактовой частотой f c и выходной частотой менее f c /2 показан на рисунке 3. Выходной спектр показывает выходную спектральную линию, f из , а также его частоты изображения выше и ниже тактовой частоты, а также все его гармоники до и после третьей.

Рисунок 3: Спектральный вид DDS с системной тактовой частотой f c и выходной частотой f из , показывающие компоненты выходной частоты до третьей гармоники тактового сигнала. (Источник изображения: Analog Devices)

Диапазон выходных частот DDS составляет от 0 Гц до предела Найквиста при f c /2. Формирование sin(x)/x обусловлено квантованным сигналом во временной области, как показано на рисунке 2. Нули функции sin(x)/x появляются на тактовой частоте и на всех ее гармониках. Амплитудные поправки могут быть применены для отмены формирования sin(x)/x, чтобы улучшить неравномерность амплитуды во всем выходном диапазоне.

Формирование sin(x)/x обусловлено квантованным сигналом во временной области, как показано на рисунке 2. Нули функции sin(x)/x появляются на тактовой частоте и на всех ее гармониках. Амплитудные поправки могут быть применены для отмены формирования sin(x)/x, чтобы улучшить неравномерность амплитуды во всем выходном диапазоне.

ФНЧ с резкой отсечкой выше частотного диапазона ЦДС применяется для того, чтобы значительно уменьшить амплитуду спектральных составляющих выше Найквиста. Если диапазон частот DDS расширен до частоты Найквиста, то фильтру потребуется бесконечная крутая крутизна среза, чтобы исключить более низкую частоту изображения около тактовой частоты, которая перекрывает частоту Найквиста. Это одна из причин того, что частотный диапазон DDS редко расширяется до частоты Найквиста.

Проектирование с использованием коммерческих микросхем DDS

При выборе и использовании DDS необходимо учитывать многое. Во-первых, рассмотрим необходимый функционал для приложений; требуемый диапазон частот, амплитуда и диапазон смещения, форма волны, разрешение и возможности модуляции. Чистота сигнала обычно является фактором при выборе источника сигнала. Динамический диапазон без паразитных составляющих (SFDR), полное гармоническое искажение (THD) и фазовый шум являются ключевыми характеристиками, как и потребляемая мощность, особенно в мобильных приложениях.

Чистота сигнала обычно является фактором при выборе источника сигнала. Динамический диапазон без паразитных составляющих (SFDR), полное гармоническое искажение (THD) и фазовый шум являются ключевыми характеристиками, как и потребляемая мощность, особенно в мобильных приложениях.

Хорошим примером маломощного DDS является AD9834BRUZ-REEL7 компании Analog Devices (рис. 4). Это устройство управляется трехпроводным последовательным интерфейсом и потребляет всего 20 милливатт (мВт) от источника питания 3 В. Он может выводить синусоидальные, пилообразные и прямоугольные функции и имеет максимальную тактовую частоту 50 мегагерц (МГц), показанную на рисунке как цифровой тактовый вход MCLK. Основываясь на обсуждении Найквиста ранее, эта тактовая частота означает, что он может выводить сигналы с частотой до 25 МГц.

Рис. 4. Внутренняя функциональная схема маломощного DDS Analog Devices AD9834. Устройство потребляет 20 мВт от источника питания 3 В и может производить функции синусоидальной, пилообразной и прямоугольной волны до 25 МГц. (Источник изображения: Analog Devices)

(Источник изображения: Analog Devices)

Накопитель фазы имеет длину 28 бит, что дает разрешение по частоте 0,186 Гц при тактовой частоте 50 МГц. Фазовый шум также зависит от качества входа MCLK и показан как функция смещения от несущей (рис. 5). В случае с AD9834 фазовый шум составляет -120 дБн/Гц при смещении 1 кГц от несущей для F OUT 2 МГц и MCLK 50 МГц.

Рисунок 5: Фазовый шум зависит от качества MCLK и отображается как -120 дБн/Гц при смещении 1 кГц от несущей для F OUT 2 МГц и MCLK 50 МГц . (Источник изображения: Analog Devices)

Встроенный ЦАП имеет разрешение 10 бит, а узкополосный SFDR обычно лучше -78 дБ.

Особенности AD9834 включают двойной частотный и фазовый регистры для поддержки как частотной, так и фазовой модуляции. Кроме того, синусоидальную постоянную память (ПЗУ) можно обойти, чтобы управлять ЦАП, используя выход фазового аккумулятора для создания линейно изменяющейся функции. Бит знака доступен на выходном контакте для подачи прямоугольной волны для генерации тактового сигнала.

Чтобы упростить процесс проектирования, поставщики часто предоставляют хорошие инструменты выбора, упрощающие задачу. AD9834 DDS поддерживается ADIsimDDS от Analog Devices, интерактивным онлайн-инструментом проектирования, который позволяет разработчикам оценивать различные конфигурации, включая выходные частоты, слова настройки и эталонные часы (рис. 6).

Рис. 6. Интерактивный инструмент проектирования ADIsimDDS от Analog Devices позволяет разработчикам экспериментировать с различными конфигурациями DD и параметрами фильтрации. (Источник изображения: Analog Devices)

Программа ADIsimDDS начинается с выбора определенного продукта DDS, в данном случае AD9834. Пользователь вводит системную тактовую частоту и желаемую выходную частоту, и программа вычисляет слово настройки для фазового аккумулятора. Дисплей в частотной области показывает спектр выходного сигнала DDS, включая выходной сигнал, гармоники, изображения ЦАП, гармоники часов и изображения часов. К выходу DDS можно применить симулятор фильтра, чтобы увидеть влияние различных фильтров на выходной спектр.

К выходу DDS можно применить симулятор фильтра, чтобы увидеть влияние различных фильтров на выходной спектр.

Если конструкция требует более высокой производительности и частоты, Analog Devices AD9952YSVZ-REEL7 имеет максимальную тактовую частоту 400 МГц и может формировать синусоидальные сигналы до 200 МГц с более низким фазовым шумом и SFDR, указанным на уровне >80 дБ при 160 МГц. (смещение ±100 кГц) A OUT . При непосредственном сравнении с AD9834 его узкополосный SFDR обычно составляет -70 дБ на частоте 20 МГц, но, конечно, это зависит от частоты.

AD9952 не использует вход MCLK. Вместо этого он имеет встроенный тактовый генератор с соответствующим умножителем PLL, который может умножать тактовую частоту в 4–20 раз с использованием одного внешнего кристалла (рис. 7). Наличие собственных внутренних системных часов (до 400 MSPS) позволяет DDS достичь низкого фазового шума ≤ -120 дБн/Гц при смещении 1 кГц.

Рис. 7. AD9952 принимает входные данные внешнего кристалла и генерирует собственные внутренние системные часы, чтобы лучше контролировать условия, необходимые для более высокой производительности, такие как более низкий фазовый шум. (Источник изображения: Analog Devices)

(Источник изображения: Analog Devices)

AD9952 также имеет 32-битный фазовый аккумулятор глубины и 14-битный ЦАП. DDS управляется через последовательный интерфейс.

Для более широкого диапазона частот предлагается Analog Devices AD9957BSVZ-REEL, который поддерживает тактовую частоту до 1 гигагерца (ГГц) с выходной частотой до 400 МГц для расширенных коммуникационных приложений. Используя 32-битный фазовый аккумулятор и 14-битный высокоскоростной ЦАП, это устройство предназначено для использования в качестве квадратурного модулятора и генерирует как синфазные (I), так и квадратурные (Q) компоненты, управляемые восемью регистрами фазы/частоты. Они используются для создания квадратурно-модулированного потока данных на выходе. Дополнительный фильтр обратного SINC (sin(x)/x) доступен для компенсации обсуждавшегося ранее формирования sin(x)/x.

Это три примера коммерчески доступных интегральных схем DDS, охватывающих как простые, так и сложные задачи генерации сигналов.

Заключение

Поскольку перед разработчиками постоянно стоит задача улучшить производительность, размер, стоимость и энергопотребление беспроводной системы, DDS оказались хорошим вариантом. Они обеспечивают цифровую стабильность, гибкость и воспроизводимость генерации сигналов, предлагая несколько форм выходного сигнала и расширенные возможности модуляции, включая скачкообразную перестройку частоты и фазы. По мере того, как они становятся частью набора инструментов дизайнера, поставщики также упрощают их выбор и интеграцию за счет использования передовых инструментов, сокращающих процесс проектирования.

Отказ от ответственности: мнения, убеждения и точки зрения, выраженные различными авторами и/или участниками форума на этом веб-сайте, не обязательно отражают мнения, убеждения и точки зрения Digi-Key Electronics или официальную политику Digi-Key Electronics. .

Прямой цифровой синтез » Electronics Notes

Прямой цифровой синтез, DDS — это метод синтеза частоты, в котором используется форма волны, хранящаяся в ПЗУ

.

Учебные пособия по синтезатору частот Включает:

Основы синтезатора

PLL/непрямой синтезатор

PLL цифровой синтезатор

Аналоговый синтезатор с ФАПЧ

Многоконтурный синтезатор

Фракционный синтез азота

Фазовый шум синтезатора

Как спроектировать синтезатор с низким фазовым шумом

Прямой цифровой синтезатор, DDS

Прямой цифровой синтез, DDS, представляет собой метод синтеза частот, который становится все более распространенным.

DDS, прямой цифровой синтез использует подход, отличный от более распространенных методов косвенного синтеза частоты с использованием PLL, путем прямого синтеза формы волны из цифровой карты формы волны, хранящейся в памяти.

Используя таким образом цифровые методы, наряду с высокоскоростной логикой, прямой цифровой синтез обеспечивает мощную технику для создания точных сигналов, частота которых может быть изменена очень маленькими приращениями, обеспечивая при необходимости практически аналоговую или непрерывную настройку.

В течение многих лет прямые цифровые синтезаторы были ограничены по частоте скоростью логики. С повышением скорости увеличивается верхний предел частот для прямых цифровых синтезаторов.

Как работает DDS

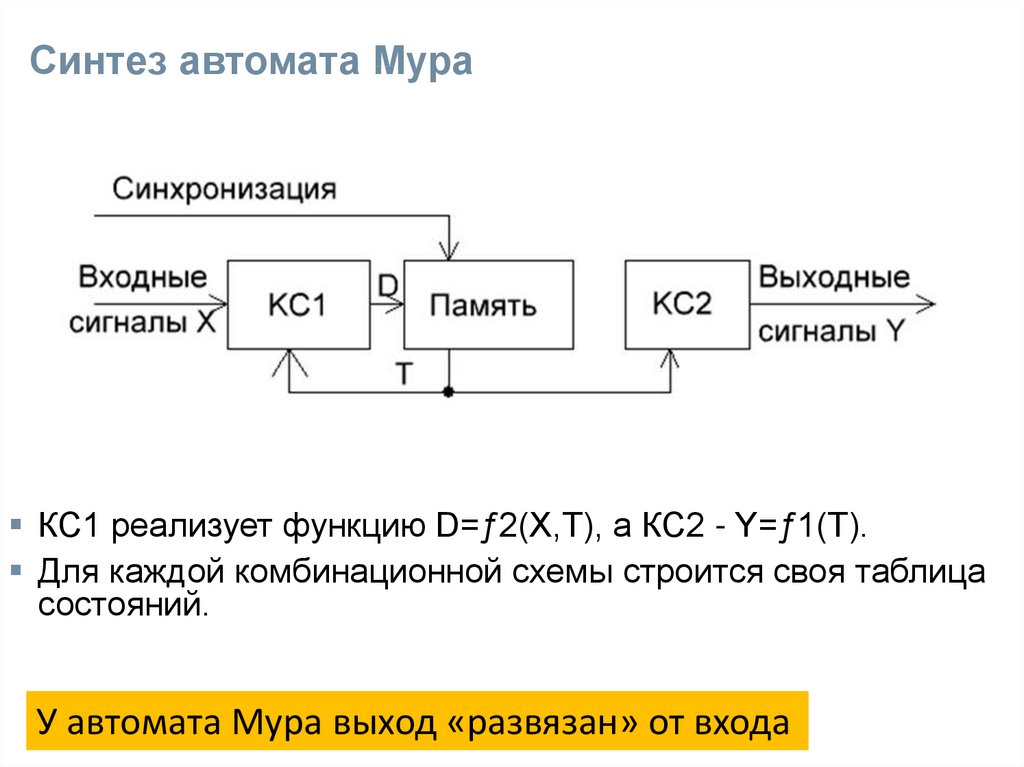

Как следует из названия, эта форма синтеза генерирует сигнал непосредственно с использованием цифровых технологий. Это отличается от того, как более знакомые непрямые синтезаторы используют петлю фазовой автоподстройки частоты в качестве основы своей работы.

Прямой цифровой синтезатор работает, сохраняя точки сигнала в цифровом формате, а затем вызывая их для создания сигнала. Скорость, с которой синтезатор формирует один сигнал, затем определяет частоту. Общая блок-схема показана ниже, но прежде чем рассматривать детали работы синтезатора, необходимо рассмотреть основную концепцию системы.

Операцию легче представить, посмотрев на то, как изменяется фаза в течение одного цикла сигнала. Это можно представить как фазу, протекающую по кругу. Поскольку фаза продвигается по кругу, это соответствует прогрессу в форме волны.

Поскольку фаза продвигается по кругу, это соответствует прогрессу в форме волны.

Синтезатор работает, сохраняя различные точки сигнала в цифровой форме и затем вызывая их для создания сигнала. Его работу можно объяснить более подробно, рассматривая сдвиг фазы по кругу, как показано на рисунке 2. Поскольку сдвиг фазы по кругу соответствует сдвигу формы сигнала, т. е. чем больше число, соответствующее фазе, тем больше точка находится вдоль формы волны. Последовательно увеличивая число, соответствующее фазе, можно двигаться дальше по циклу сигнала.

Цифровое число, представляющее фазу, хранится в аккумуляторе фаз. Число, хранящееся здесь, соответствует фазе и увеличивается через равные промежутки времени. Таким образом, он может быть отправлен, поскольку накопитель фазы в основном представляет собой форму счетчика. Когда он синхронизируется, он добавляет номер предустановки к уже сохраненному. Когда он заполняется, он сбрасывается и снова начинает отсчет с нуля. Другими словами, это соответствует достижению одного полного круга на фазовой диаграмме и повторному запуску.

Другими словами, это соответствует достижению одного полного круга на фазовой диаграмме и повторному запуску.

После определения фазы необходимо преобразовать ее в цифровое представление формы волны. Это достигается с помощью карты сигналов. Это память, в которой хранится число, соответствующее напряжению, необходимому для каждого значения фазы сигнала. В случае синтезатора такого типа это таблица преобразования синуса, поскольку требуется синусоидальная волна. В большинстве случаев память является либо постоянной памятью (ROM), либо программируемой постоянной памятью (PROM). Он содержит огромное количество точек на осциллограмме, гораздо больше, чем доступно в каждом цикле. Требуется очень большое количество точек, чтобы накопитель фазы мог увеличиваться на определенное количество точек для установки требуемой частоты.

Следующим этапом процесса является преобразование цифровых чисел, поступающих из таблицы преобразования синуса, в аналоговое напряжение. Это достигается с помощью цифро-аналогового преобразователя (ЦАП). Этот сигнал фильтруется для удаления любых нежелательных сигналов и усиливается для придания требуемого уровня по мере необходимости.

Это достигается с помощью цифро-аналогового преобразователя (ЦАП). Этот сигнал фильтруется для удаления любых нежелательных сигналов и усиливается для придания требуемого уровня по мере необходимости.

Настройка выполняется путем увеличения или уменьшения размера шага или приращения фазы между различными точками выборки. Большее приращение при каждом обновлении аккумулятора фазы будет означать, что фаза быстрее достигает значения полного цикла, и частота соответственно выше. Меньшие приращения значения аккумулятора фазы означают, что требуется больше времени для увеличения значения полного цикла и, соответственно, низкого значения частоты. Таким образом можно управлять частотой. Также видно, что изменения частоты можно производить мгновенно, просто изменяя значение приращения. Нет необходимости во времени установления, как в случае синтезатора на основе фазовой автоподстройки частоты.

Из этого видно, что существует конечная разница между одной частотой и другой, и что минимальная разница частот или разрешение по частоте определяется общим количеством точек, доступных в фазовом накопителе.