Справочник “Цифровые Интегральные Микросхемы”

Справочник “Цифровые Интегральные Микросхемы” [ Содержание ]2.4.2 Микросхемы типа ЛА, ЛИ

Чтобы рассмотреть схемотехнику, составим таблицу функций элементов И, И-НЕ для двух входов А и В (простейший вариант). Каждая переменная А и В моделируется электронным ключом, который можно замкнуть или разомкнуть. Если ключи соединены последовательно, то они работают согласно логике И: ток в цепи появится, если замкнуть оба ключа: и А и В. Если активными входными сигналами считать замыкание ключей А и В и назвать это событие логической 1, то, последовательно перебирая состояние этих ключей, составим таблицу входных и выходных данных для элементов И и И-НЕ.

| Логический элемент | Входные переменные | Выходная функция | ||

|---|---|---|---|---|

| А | B | И | НЕ-И | |

| 0 | 0 | 0 | ||

| 0 | 1 | 0 | 1 | |

| 1 | 0 | 0 | 1 | |

| 1 | 1 | 1 | 0 | |

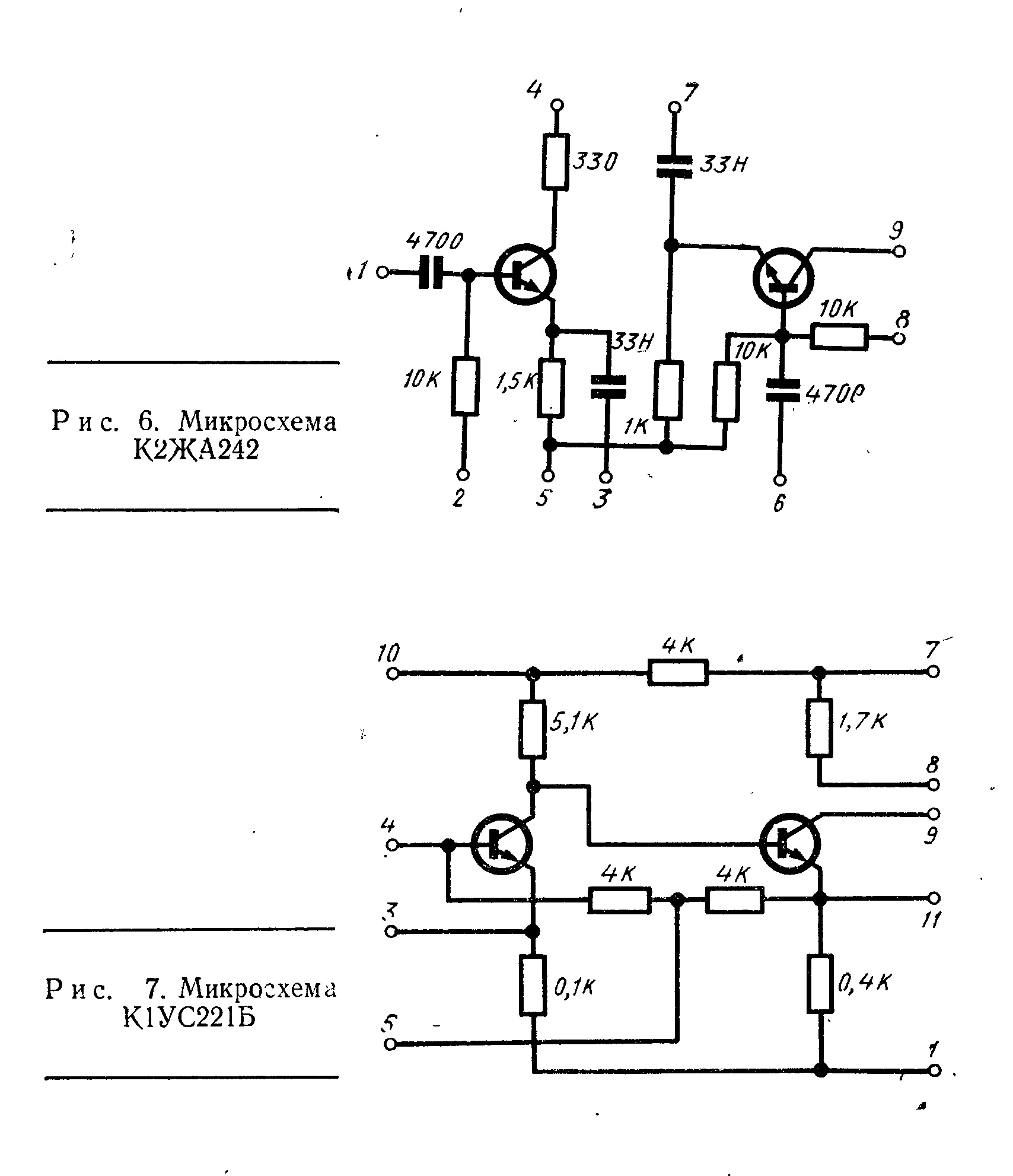

Рассмотрим способ реализации логической операции И-НЕ на элементах ТТЛ. На рис. 2.8, а приведена

принципиальная схема двухвходового логического элемента И-НЕ.

На рис. 2.8, а приведена

принципиальная схема двухвходового логического элемента И-НЕ.

Рис. 2.8.а. Принципиальная схема логического элемента.

Подавая от ключей S1 и S2 на входы А и В напряжение высокого В и низкого Н уровней, составим таблицу выходных уровней элемента.

| Вход | Выход Q(НЕ-И) | Вход | Выход Q(НЕ-И) | ||

|---|---|---|---|---|---|

| А | B | A | B | ||

| Н | Н | В | 0 | 0 | 1 |

| Н | В | В | 0 | 1 | 1 |

| В | Н | В | 1 | 0 | 1 |

| В | В | Н | 1 | 1 | 0 |

Напряжение низкого уровня Н появляется на выходе Q, когда

на обоих входах А и В присутствует высокое напряжение В. Условное графическое обозначение двухвходового логического

элемента показано на рис 2.8, в

Условное графическое обозначение двухвходового логического

элемента показано на рис 2.8, в

Рис 2.8.в. Условное обозначение элемента.

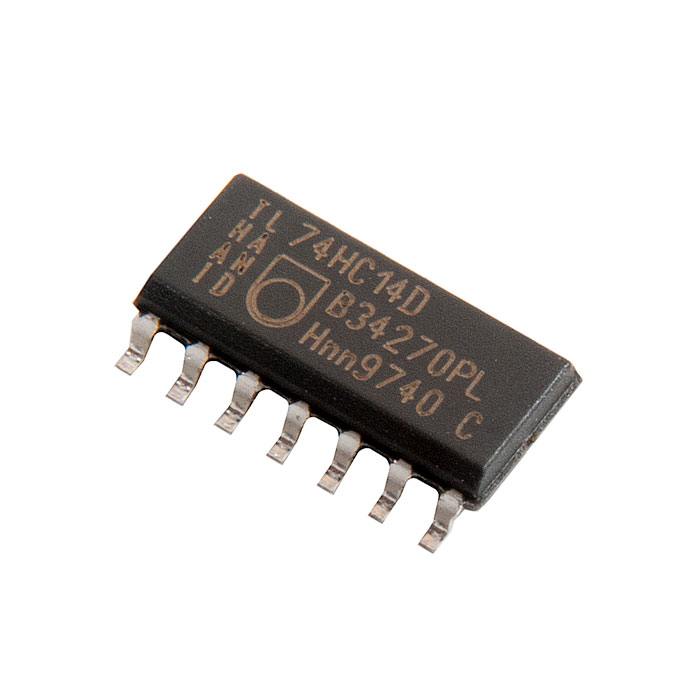

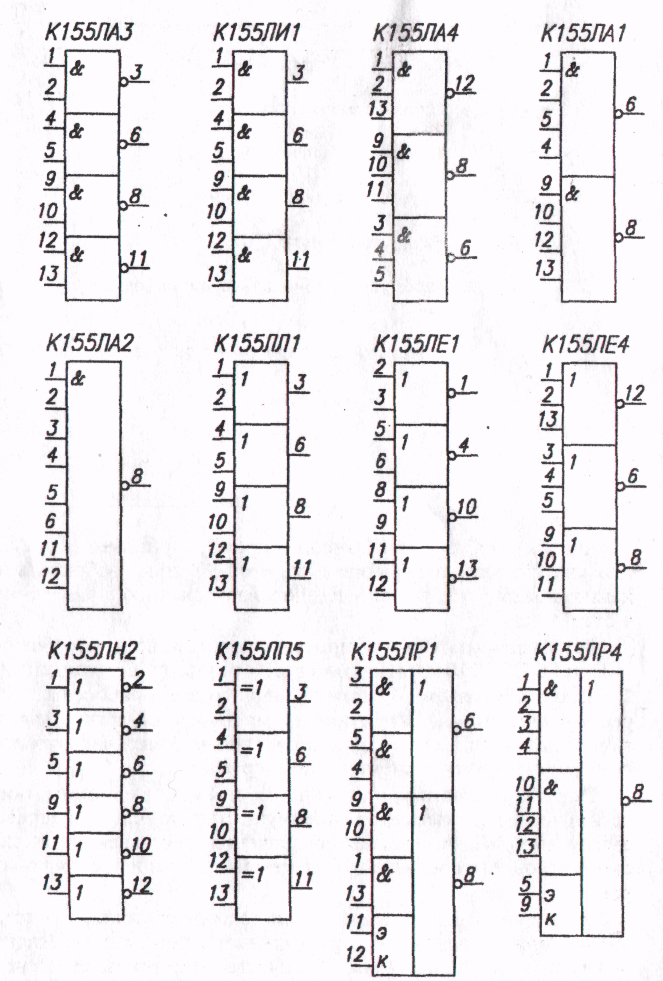

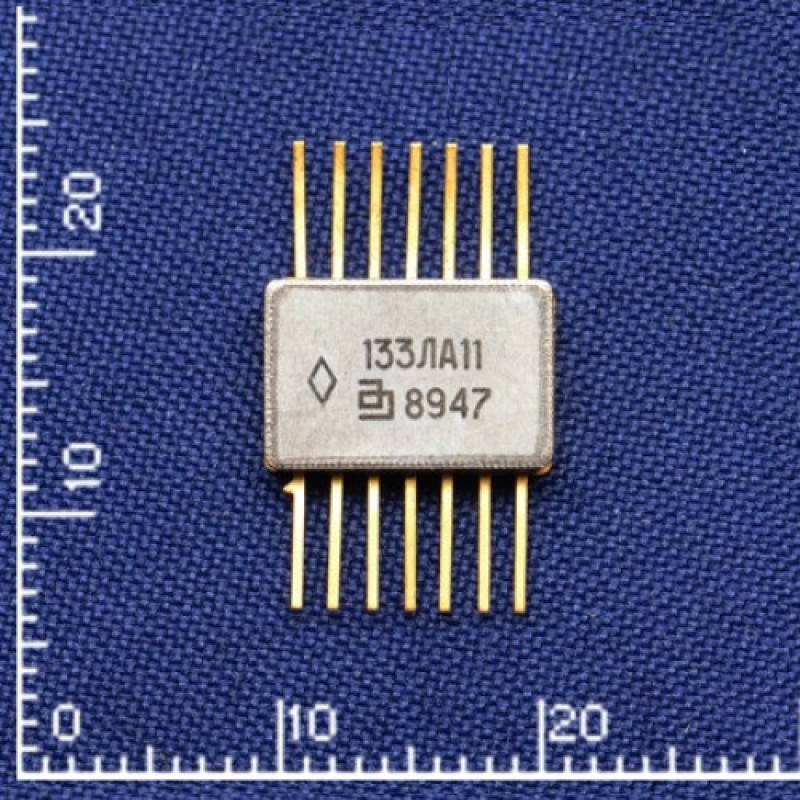

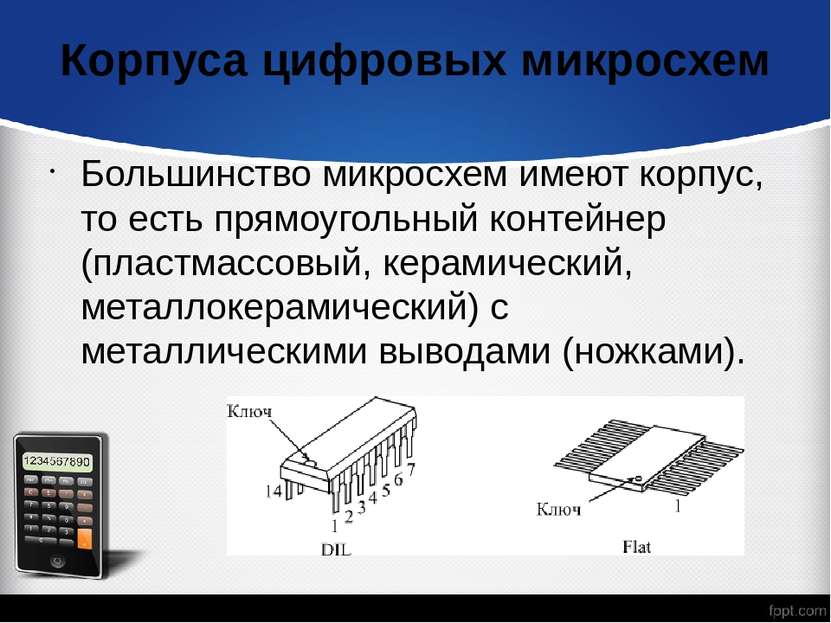

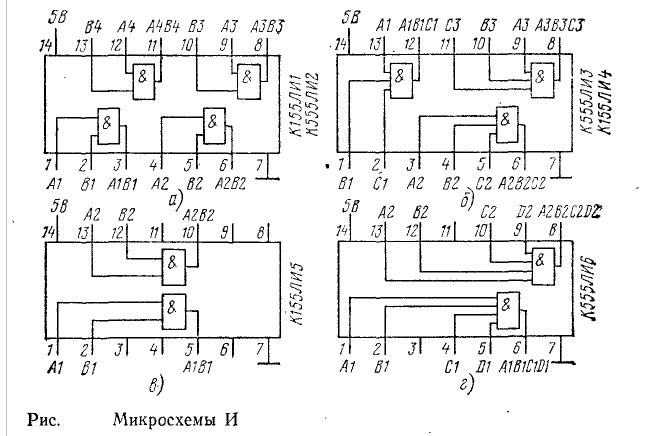

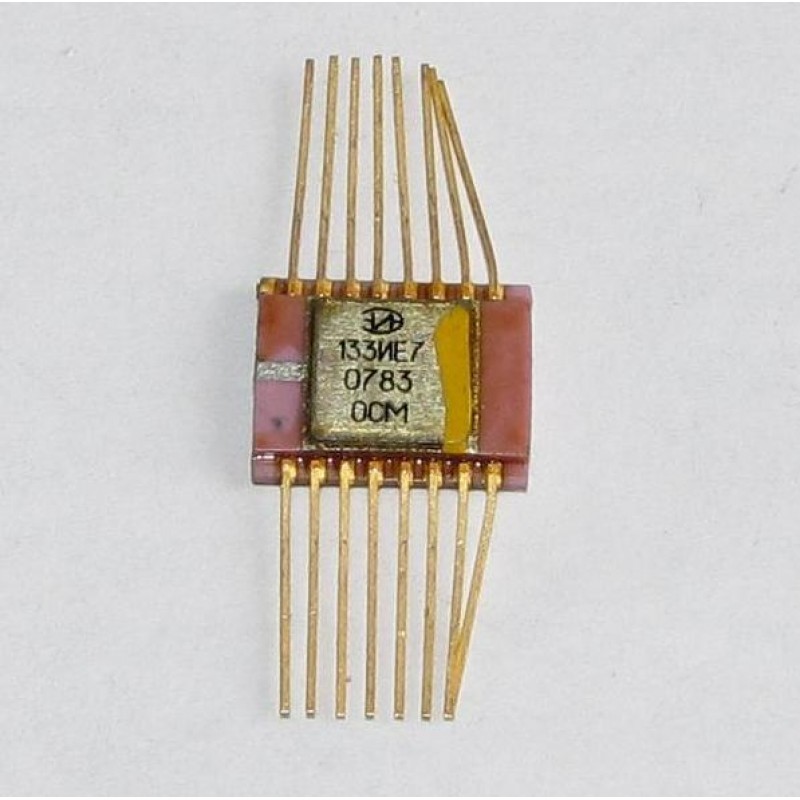

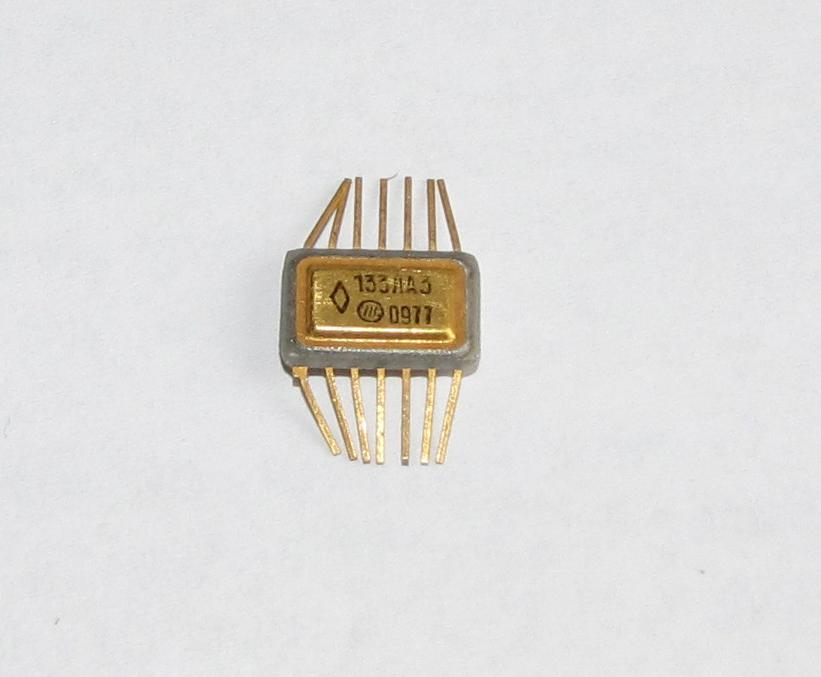

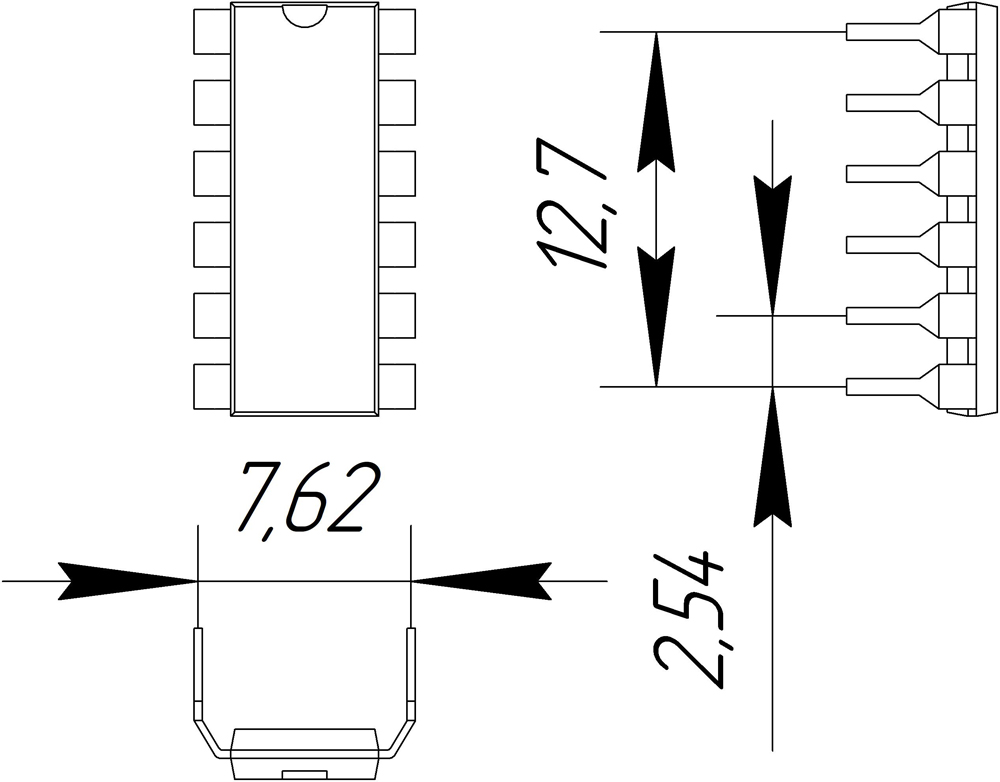

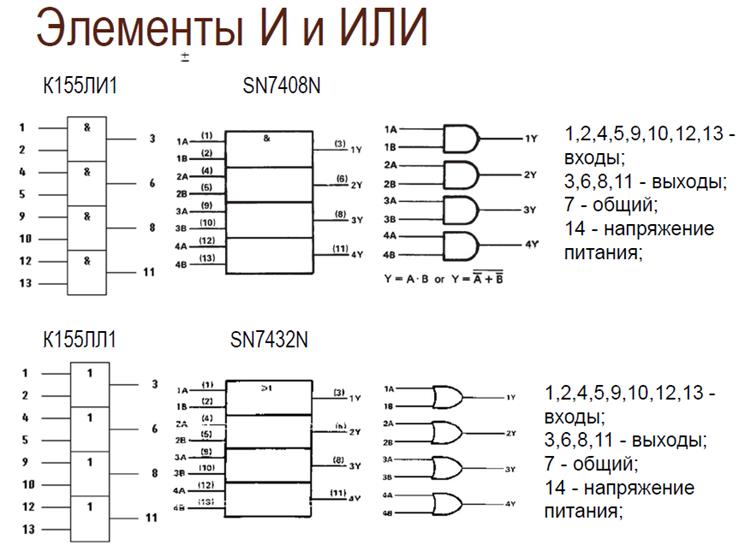

Среди простейших ИС ТТЛ преобладают элементы И, И-НЕ. Каждый из корпусов ИС типа ЛА и ЛИ содержит от двух до четырех логических элементов, а микросхемы ЛА2 и ЛА19 содержат по одному логическому элементу И-НЕ на восемь и двенадцать входов соответственно.

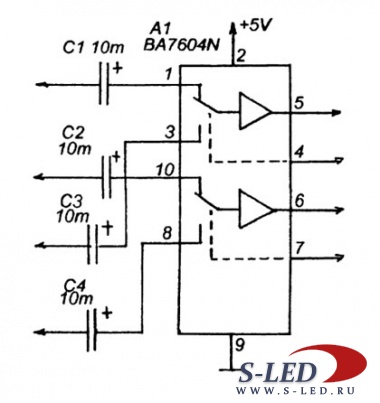

Цоколевки микросхем типа ЛА и ЛИ и их условные графические обозначения приведены на рис. 2.9, а основные параметры даны в табл. 2.3.

Рис 2.9. Условные обозначения и цоколевки микросхем ЛИ

Рис 2.9. Условные обозначения и цоколевки микросхем ЛА

Следует особо выделить группу микросхем, логические элементы которых имеют выходы с открытым коллектором (ЛА7…ЛА11, ЛА13. ЛА18), (ЛИ2, ЛИ4, ЛИ5). Схема двухвходового логического элемента И-НЕ с открытым коллектором показана на рис. 2.10, а.

Рис. 2.10а. Принципиальная схема логического элемента И-НЕ

Для формирования выходного перепада напряжения к выходу такого

элемента необходимо подключить внешний нагрузочный резистор Rн. Такие микросхемы применяются для обслуживания сегментов индикаторов,

зажигания ламп накаливания, светодиодов (рис. 2.10,б).

Такие микросхемы применяются для обслуживания сегментов индикаторов,

зажигания ламп накаливания, светодиодов (рис. 2.10,б).

Рис. 2.10б. Схема подключения ламп накаливания и светодиодов

При необходимости в схемах можно использовать элемент ТТЛ с двухтактным выходом. Для некоторых микросхем с открытым коллекторным выходом (ЛА11) нагрузку можно подключать к более высоковольтному источнику питания (рис. 2.10,в).

Рис. 2.10в. Схема подключения нагрузки к высоковольтному источнику

Такое включение необходимо для зажигания газоразрядных и электролюминесцентных индикаторов. Выходы с открытого коллектора используют для подключения обмоток реле.

Выходы нескольких элементов с открытым коллектором можно присоединять к общей нагрузке Rн (рис. 2.10, г).

Рис. 2.10г. Схема подключения нескольких элементов к общей нагрузке

Такое подключение позволяет реализовать логическую функцию И,

называемую «монтажное И». Схему (рис. 2.10. г) используют

для расширения числа входов логического элемента.

Следует помнить, что двухтактные выходы ТТЛ нельзя соединять параллельно, это приводит к токовой перегрузке одного из элементов.

Многовходовые составные логические элементы с открытым коллектором и общим сопротивлением нагрузки Rн реализуются наиболее просто, однако они не позволяют получить предельное быстродействие. Более лучший способ увеличения числа входов осуществляется с помощью специальной микросхемы-расширителя, имеющей дополнительные выводы коллектора и эмиттера фазоразделительного каскада VT2 (рис. 2.11). Одноименные вспомогательные выводы нескольких таких элементов можно объединять.

Рис. 2.11а. Принципиальная схема 2И-НЕ с дополнительными выводами коллектора и эмиттера.

Рис. 2.11б. Условное обозначение расширителя и способ соединения нескольких микросхем.

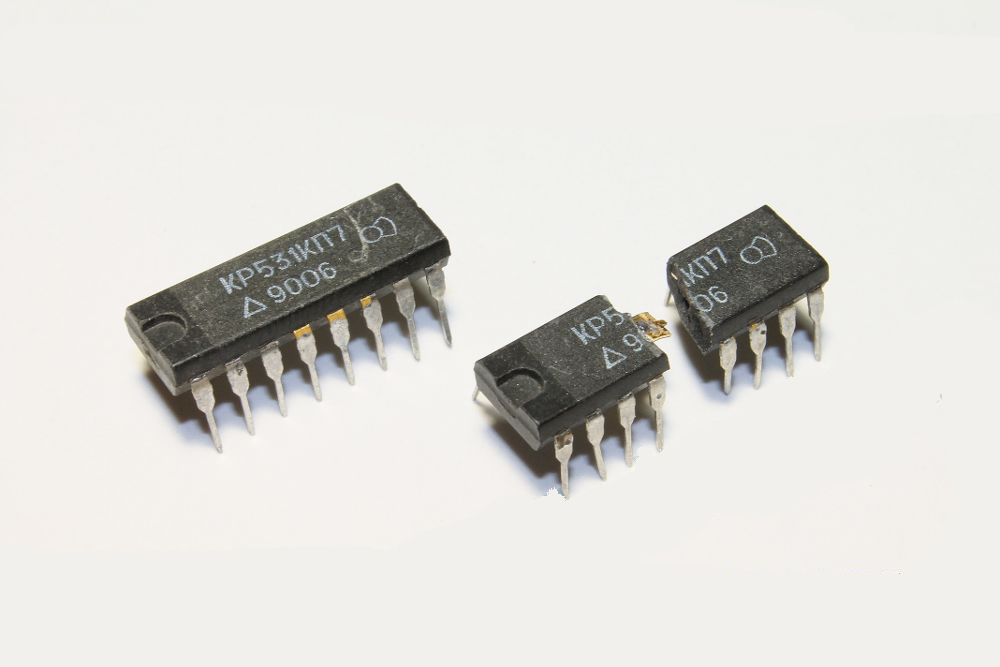

Микросхема К531ЛА16 (магистральный усилитель) может передавать данные в линию с сопротивлением 50 Ом.

Микросхемы ЛА17, ЛА19 – это логические элементы И-НЕ с

тремя состояниями на выходе, т.

Рис. 2.12. Принципиальная схема логического элемента с тремя состояниями на выходе.

Для этой цели в схему стандартного сложного инвертора ТТЛ вводится

дополнительный инвертор DDI и диод VD2. Если на этот вход /ЕО подать

от переключателя S1 напряжение высокого уровня – 1, то выходное

напряжение инвертора DD1 станет низким, т. е. катод диода VD2 будет

практически соединен с корпусом. Из-за этого коллектор транзистора

VT2 будет иметь нулевой потенциал, т. е. транзистор VT2 будет закрыт.

Транзисторы VT3 и VT4 будут находиться в режиме отсечки, т. е.

оба закрыты. Следовательно, выходной вывод как бы «висит» в воздухе,

микросхема переходит в состояние Z с очень большим выходным сопротивлением.

Если на вход ЕО подается разрешающий низкий уровень – О, то логический

элемент И-НЕ работает как в обычном режиме.

| Вход | Выход | ||

|---|---|---|---|

| /EO | I | /Y | |

| 0 | 0 1 | 1 0 | |

| 1 | 0 1 | Z | |

Такие логические элементы разработаны специально для обслуживания проводника шины данных. Если к такому проводнику присоединить много выходов, находящихся в состоянии Z, то они не будут влиять друг на друга. Активным передающим сигналом должен быть лишь один логический элемент, только от его выхода в проводник шины данных будет поступать информация. Следовательно, соединенные вместе выходы не должны быть одновременно активными.

Чтобы сигналом разрешения (низкий уревень – О) , подаваемым

на вход /EO, подключался к проводнику выход только одного

логического элемента, необходимо предусмотреть дополнительный

(защитный) временной интервал, т. е. переключать входы /ЕО

различных элементов с паузой. Сигналы разрешения, даваемые

выходам разных элементов, не должны

перекрываться.

е. переключать входы /ЕО

различных элементов с паузой. Сигналы разрешения, даваемые

выходам разных элементов, не должны

перекрываться.

Микросхема К531ЛА19-это 12-входовый логический элемент И-НЕ с дополнительным инверсным входом /ЕО. Сигнал появится на его выходе, если на вход /ЕО подано напряжение низкого уровня – О. Выход логического элемента перейдет в разомкнутое состояние Z, если на вход /ЕО подается напряжение высокого уровня. В состоянии Z элемент потребляет ток Iпот.z=25 мА. Время задержки перехода выхода к разомкнутому состоянию tзд.1z= 16 нс, время задержки перехода выхода tзд.0z= 12 нс (от напряжения низкого выходного уровня), при условии, что Сн = 15 пФ [1].

Микросхема 7453

7453

Описание

Микросхема 7453 (74H53) содержит логический элемент 4ИЛИ-НЕ с расширяющими входами. Входы этого элемента соединены с выходами четырех двухвходовых элементов И (серия 7453) или трех двухвходовых и одного трехвходового элементов И (серия 74H53).

Работа схемы

На выходе Q (серия 7453) формируется напряжение низкого уровня лишь в том случае, когда на входы А и В, или С и D, или Е и F, или G и Н подается напряжение высокого уровня.

Расширяющие входы микросхемы 7453 (74H53) должны оставаться открытыми, если они не используются.

Интегральная микросхема серии 74H53 содержит один логический элемент И с тремя входами, а также три логических элемента И с двумя входами.

В технической литературе эти логические микросхемы 74H53 иногда обозначаются как схемы AOI (И-ИЛИ с инвертированием). Такое обозначение не очень удачно, поскольку логический элемент ИЛИ и инвертор вместе образуют логический элемент ИЛИ-НЕ. Так как в данной схеме выход логического элемента ИЛИ не выведен отдельно, его выходной сигнал всегда инвертируется, то есть в каждом случае реализуется функция ИЛИ-НЕ.

Применение

Реализация логических функций И-НЕ, ИЛИ-НЕ.

Производится следующая номенклатура микросхем: 7453, 74H53.

| Тип микросхемы | 7453 |

|---|---|

| Время задержки прохождения сигнала, нс | 10,5 |

| Ток потребления, мА |

|

|

|||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

Логические элементы

В данной статье расскажем что такое логические элементы, рассмотрим самые простые логические элементы.

Любое цифровое устройство — персональный компьютер, или современная система автоматики состоит из цифровых интегральных микросхем (ИМС), которые выполняют определённые сложные функции. Но для выполнения одной сложной функции необходимо выполнить несколько простейших функций. Например, сложение двух двоичных чисел размером в один байт происходит внутри цифровой микросхемы называемой «процессор» и выполняется в несколько этапов большим количеством логических элементов находящихся внутри процессора. Двоичные числа сначала запоминаются в буферной памяти процессора, потом переписываются в специальные «главные» регистры процессора, после выполняется их сложение, запоминание результата в другом регистре, и лишь после результат сложения выводится через буферную память из процессора на другие устройства компьютера.

Процессор состоит из функциональных узлов: интерфейсов ввода-вывода, ячеек памяти – буферных регистров и «аккумуляторов», сумматоров, регистров сдвига и т.д. Эти функциональные узлы состоят из простейших логических элементов, которые, в свою очередь состоят из полупроводниковых транзисторов, диодов и резисторов. При конструировании простых триггерных и других электронных импульсных схем, сложные процессоры не применить, а использовать транзисторные каскады – «прошлый век». Тут и приходят на помощь – логические элементы.

При конструировании простых триггерных и других электронных импульсных схем, сложные процессоры не применить, а использовать транзисторные каскады – «прошлый век». Тут и приходят на помощь – логические элементы.

Логические элементы, это простейшие «кубики», составные части цифровой микросхемы, выполняющие определённые логические функции. При этом, цифровая микросхема может содержать в себе от одного, до нескольких единиц, десятков, …и до нескольких сотен тысяч логических элементов в зависимости от степени интеграции. Для того, чтобы разобраться, что такое логические элементы, мы будем рассматривать самые простейшие из них. А потом, наращивая знания, разберёмся и с более сложными цифровыми элементами.

Начнём с того, что единица цифровой информации это «один бит». Он может принимать два логических состояния – логический ноль «0», когда напряжение равно нулю (низкий уровень), и состояние логической единицы «1», когда напряжение равно напряжению питания микросхемы (высокий уровень).

Поскольку простейший логический элемент это электронное устройство, то это означает, что у него есть входы (входные выводы) и выходы (выходные выводы). И входов и выходов может быть один, а может быть и больше.

Для того, чтобы понять принципы работы простейших логических элементов используется «таблица истинности». Кроме того, для понимания принципов работы логических элементов, входы, в зависимости от их количества обозначают: Х1, Х2, … ХN, а выходы: Y1, Y2, … YN.

Функции, выполняемые простейшими логическими элементами, имеют названия. Как правило, впереди функции ставится цифра, обозначающая количество входов. Простейшие логические элементы всегда имеют лишь один выход.

Рассмотрим простейшие логические элементы

— «НЕ» (NOT) – функция отрицания (инверсии сигнала). Потому его чаще называют — «инвертор». Графически, инверсия обозначается пустым кружочком вокруг вывода элемента (микросхемы). Обычно кружок инверсии ставится у выхода, но в более сложных логических элементах, он может стоять и на входе. Графическое обозначение элемента «НЕ» и его таблица истинности представлены на рисунке слева.

Графическое обозначение элемента «НЕ» и его таблица истинности представлены на рисунке слева.

У элемента «НЕ» всегда один вход и один выход. По таблице истинности следует, что при наличии на входе элемента логического нуля, на выходе будет логическая единица. И наоборот, при наличии на входе логической единицы, на выходе будет логический ноль. Цифра «1» внутри прямоугольника обозначает функцию «ИЛИ», её принято рисовать и внутри прямоугольника элемента «НЕ», но это ровным счётом ничего абсолютно не значит.

Обозначение D1.1 означает, что D — цифровой логический элемент, 1 (первая) — номер микросхемы в общей схеме, 1 (вторая) — номер элемента в микросхеме. Точно также расшифровываются и другие логические элементы.

Часто, чтобы отличить цифровые микросхемы от аналоговых микросхем, применяют обозначения из двух букв: DD – цифровая микросхема, DA – аналоговая микросхема. В последующем, мы не будем заострять внимание на это обозначение, а вернёмся лишь тогда, когда это будет необходимым.

Самой распространённой микросхемой «транзисторно-транзисторной логики» (ТТЛ), выполняющей функцию «НЕ», является интегральная микросхема (ИМС) К155ЛН1, внутри которой имеется шесть элементов «НЕ». Нумерация выводов этой микросхемы показана справа.

— «И» (AND) – функция сложения (если на всех входах единица, то на выходе будет единица, в противном случае, если хотя бы на одном входе ноль, то и на выходе всегда будет ноль). В алгебре-логике элемент «И» называют «конъюнктор». Графическое обозначение элемента «2И» и его таблица истинности представлены слева.

Название элемента «2И» обозначает, что у него два входа, и он выполняет функцию «И». На схеме внутри прямоугольника микросхемы рисуется значок «&», что на английском языке означает «AND» (в переводе на русский — И).

По таблице истинности следует, что на выходе элемента «И» будет логическая единица только в одном случае — когда на обоих входах будет логическая единица. Если хотя бы на одном входе ноль, то и на выходе будет ноль.

Если хотя бы на одном входе ноль, то и на выходе будет ноль.

Самой распространённой микросхемой «транзисторно-транзисторной логики» (ТТЛ), выполняющей функцию «2И», является интегральная микросхема (ИМС) К155ЛИ1, внутри которой имеется четыре элемента «2И». Нумерация выводов этой микросхемы показана справа.

Для того, чтобы вам было понятнее что такое «2И», «3И», «4И», и т.д., приведу графическое обозначение и таблицу истинности элемента «3И».

По таблице истинности следует, что на выходе элемента «3И» будет логическая единица только в том случае — когда на всех трёх входах будет логическая единица. Если хотя бы на одном входе будет логический ноль, то и на выходе элемента также будет логический ноль. Самой распространённой микросхемой ТТЛ, выполняющей функцию «3И», является микросхема К555ЛИ3, внутри которой имеется три элемента «3И».

— «И-НЕ» (NAND) – функция сложения с отрицанием (если на всех входах единица, то на выходе будет ноль, в противном случае на выходе всегда будет единица). Графическое обозначение элемента «2И-НЕ» и его таблица истинности приведены слева.

Графическое обозначение элемента «2И-НЕ» и его таблица истинности приведены слева.

По таблице истинности следует, что на выходе элемента «2И-НЕ» будет логический ноль только в том случае, если на обоих входах будет логическая единица. Если хотя бы на одном входе ноль, то на выходе будет единица.

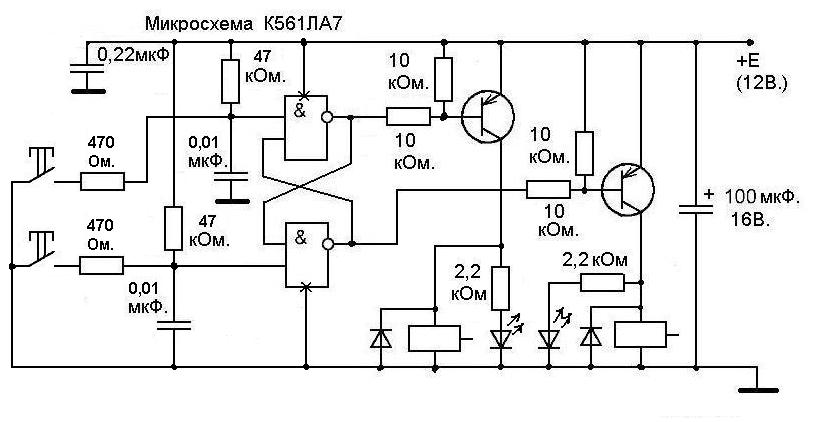

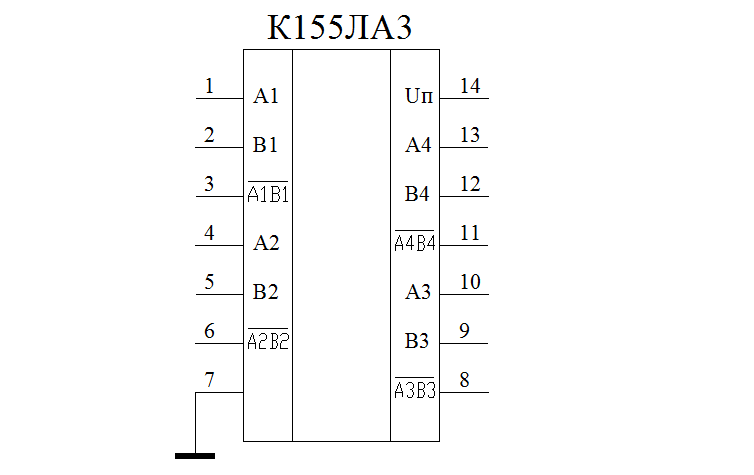

Самой распространённой микросхемой ТТЛ, выполняющей функцию «2И-НЕ», является ИМС К155ЛА3, а микросхемами КМОП (комплементарный металлооксидный полупроводник) – ИМС К561ЛА7 и К176ЛА7, внутри которых имеется четыре элемента «2И-НЕ». Нумерация выводов этих микросхем показана справа.

Сравнив таблицы истинности элемента «2И-НЕ» и элемента «2И» можно догадаться об эквивалентности схем:

Добавив к элементу «2И» элемент «НЕ» мы получили элемент «2И-НЕ». Так можно собрать схему, если нам необходим элемент «2И-НЕ», а у нас в распоряжении имеются только элементы «2И» и «НЕ».

И наоборот:

Добавив к элементу «2И-НЕ» элемент «НЕ» мы получили элемент «2И». Так можно собрать схему, если нам необходим элемент «2И», а у нас в распоряжении имеются только элементы «2И-НЕ» и «НЕ».

Аналогичным образом, путём соединения входов элемента «2И-НЕ» мы можем получить элемент «НЕ»:

Обратите внимание, что было введено новое в обозначении элементов – дефис, разделяющий правую и левую часть в названии «2И-НЕ». Этот дефис непременный атрибут при инверсии на выходе (функции «НЕ»).

— «ИЛИ» (OR) – функция выбора (если хотя бы на одном из входов – единица, то на выходе – единица, в противном случае на выходе всегда будет ноль). В алгебре-логике, элемент «ИЛИ» называют «дизъюнктор». Графическое обозначение элемента «2ИЛИ» и его таблица истинности приведены слева.

Самой распространённой микросхемой ТТЛ, выполняющей функцию «2ИЛИ», является ИМС К155ЛЛ1, внутри которой имеется четыре элемента «2ИЛИ». Нумерация выводов этой микросхемы показана справа.

Предположим, что нам в схеме необходим элемент, выполняющий функцию «2ИЛИ», но у нас есть в распоряжении только элементы «НЕ» и «2И-НЕ», тогда можно собрать схему, которая будет выполнять функцию «2ИЛИ»:

— «ИЛИ-НЕ» (NOR) – функция выбора (если хотя бы на одном из входов – единица, то на выходе – ноль, в противном случае на выходе всегда будет единица). Как вы поняли, элемент «ИЛИ-НЕ» выполняет функцию «ИЛИ», а потом инвертирует его функцией «НЕ».

Как вы поняли, элемент «ИЛИ-НЕ» выполняет функцию «ИЛИ», а потом инвертирует его функцией «НЕ».

Графическое обозначение элемента «2ИЛИ-НЕ» и его таблица истинности приведена слева.

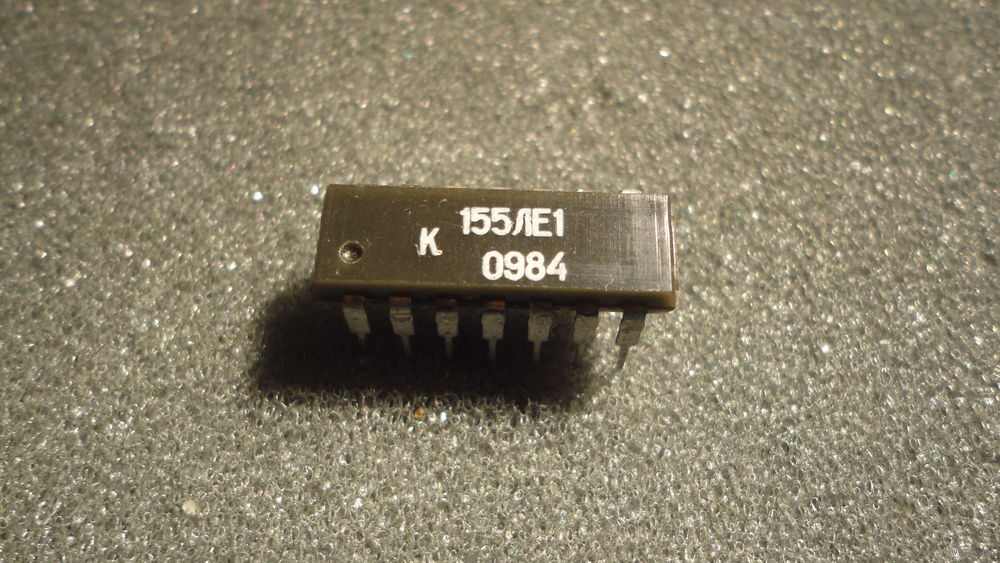

Самой распространённой микросхемой ТТЛ, выполняющей функцию «2ИЛИ-НЕ», является ИМС К155ЛЕ1, а микросхемами КМОП – К561ЛЕ5 и К176ЛЕ5, внутри которых имеется четыре элемента «2ИЛИ-НЕ». Нумерация выводов этих микросхем показана справа.

Предположим, что нам в схеме необходим элемент, выполняющий функцию «2ИЛИ-НЕ», но у нас есть в распоряжении только элементы «НЕ» и «2И-НЕ», тогда можно собрать следующую схему, которая будет выполнять функцию «2ИЛИ-НЕ»:

По аналогии с элементом «2И-НЕ», путём соединения входов элемента «2ИЛИ-НЕ» мы можем получить элемент «НЕ»:

— «Исключающее ИЛИ» (XOR) — функция неравенства двух входов (если на обоих входах элемента одинаковые сигналы, то на выходе – ноль, в противном случае на выходе всегда будет единица). Операция, которую он выполняет, часто называют «сложение по модулю 2».

Графическое обозначение элемента «Исключающее ИЛИ» и его таблица истинности приведены слева.

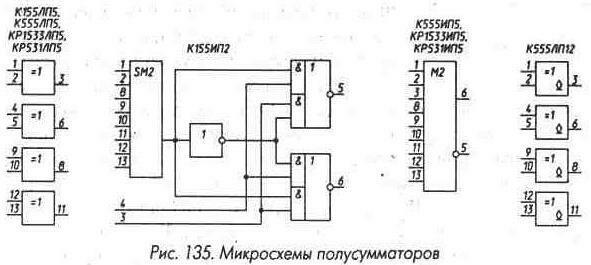

Самой распространённой микросхемой ТТЛ, выполняющей функцию «Исключающее ИЛИ», является ИМС К155ЛП5, а микросхемами КМОП – К561ЛП2 и К176ЛП2, внутри которых имеется четыре элемента «Исключающее ИЛИ». Нумерация выводов этих микросхем показана справа.

Предположим, что нам в схеме необходим элемент, выполняющий функцию «Исключающее ИЛИ», но у нас есть в распоряжении только элементы «2И-НЕ», тогда можно собрать следующую схему, которая будет выполнять функцию «Исключающее ИЛИ»:

В цифровой схемотехнике процессоров главная функция — «Суммирование двоичных чисел», поэтому сложный логический элемент – «Сумматор» является неотъемлемой частью арифметико-логического устройства любого, без исключения процессора. Составной частью сумматора является набор логических элементов, выполняющих функцию «Исключающее ИЛИ с переносом остатка». Что это такое? В соответствии с наукой «Информатика», результатом сложения двух двоичных чисел, две единицы одного разряда дают ноль, при этом формируется «единица переноса» в следующий старший разряд, который участвует в операции суммирования в старшем разряде. Для этого в схему добавляется ещё один вывод «переноса» — «Р».

Для этого в схему добавляется ещё один вывод «переноса» — «Р».

Графическое обозначение элемента «Исключающее ИЛИ с переносом» и его таблица истинности представлена слева.

Такая функция сложения одноразрядных чисел в простых устройствах обычно не используется, и как правило, интегрирована в состав одной микросхемы – сумматора, с минимальным количеством разрядов – четыре, для сложения четырехбитных чисел. По причине слабого спроса, промышленность таких логических элементов не выпускает. Поэтому, в случае необходимости, функцию «Исключающее ИЛИ с переносом» можно собрать по следующей схеме из элементов «2И-НЕ» и «2ИЛИ-НЕ», которая активно применяется как внутри простых сумматоров, так и во всех сложных процессорах (в том числе Pentium, Intel-Core, AMD и других, которые появятся в будущем):

Вышеперечисленные логические элементы выполняют статические функции, а на основе них строятся более сложные статические и динамические элементы (устройства): триггеры, регистры, счётчики, шифраторы, дешифраторы, сумматоры, мультиплексоры.

| Зарубежный | Отечественный | Описание | Другие аналоги |

|---|---|---|---|

| 00 | ЛА3 | 4×2И-НЕ | |

| 01 | ЛА8 | 4×2И-НЕ с открытым выходом L-типа | |

| 02 | ЛЕ1 | 4×2ИЛИ-НЕ | |

| 03 | ЛА9 | 4×2И-НЕ с открытым выходом L-типа | |

| 04 | ЛН1 | 6×НЕ | |

| 05 | ЛН2 | 6×НЕ с открытым выходом L-типа | |

| 06 | ЛН3 | 6×НЕ с высоковольтным открытым выходом L-типа | |

| 07 | ЛП9 ~ЛН4 | 6 буферов с высоковольтным открытым выходом L-типа | |

| 08 | ЛИ1 | 4×2И | |

| 09 | 4×2И с ОК | ||

| 10 | ЛА4 | 3×3И-НЕ | |

| 11 | ЛИ3 | 3×3И | |

| 12 | ЛА10 | 3×3И-НЕ с открытым выходом L-типа | |

| 13 | ТЛ1 | 2×4И-НЕ с триггерами Шмитта | |

| 14 | ТЛ2 | 6×НЕ с триггерами Шмитта | |

| 15 | ЛИ4 | 3×3И с ОК | |

| 16 | ЛН5 | 6×НЕ с высоковольтным открытым выходом L-типа | |

| 17 | ЛП4 | 6 буферов с высоковольтным выходом L-типа | |

| 18 | 2×4И-НЕ с триггерами Шмитта | ||

| 19 | 6×НЕ с триггерами Шмитта | ||

| 20 | ЛА1 | 2×4И-НЕ | |

| 21 | ЛИ6 | 2×4И | |

| 22 | ЛА7 | 2×4И-НЕ с открытым выходом L-типа | |

| 23 | ЛЕ2 | 2 элемента 4ИЛИ-НЕ со стробированием и расширением по ИЛИ | |

| 24 | 4×2И-НЕ gate gates with schmitt-trigger line-receiver inputs. | ||

| 25 | ЛЕ3 | 2 элемента 4ИЛИ-НЕ со стробированием | |

| 26 | ЛА11 | 4 элемента 2И-НЕ с высоковольтными открытыми выходами L-типа | |

| 27 | ЛЕ4 | 3×3ИЛИ-НЕ | |

| 28 | ЛЕ5 | 4 буферных элемента 2ИЛИ-НЕ | |

| 30 | ЛА2 | 8И-НЕ | |

| 31 | 6×delay elements | ||

| 32 | ЛЛ1 | 4×2ИЛИ | |

| 33 | 4 буферных элемента 2ИЛИ-НЕ с открытыми выходом L-типа | ||

| 34 | ЛИ9 | ||

| 36 | 4×2ИЛИ-НЕ (иная цоколёвка, нежели у 02) | ||

| 37 | ЛА12 | 4×2И-НЕ с высокой нагрузочной способностью | |

| 38 | ЛА13 | 4×2И-НЕ с открытым выходом L-типа и высокой нагрузочной способностью | |

| 39 | 4×2И-НЕ с высокой нагрузочной способностью | ||

| 40 | ЛА6 | 2×4И-НЕ с высокой нагрузочной способностью | |

| 41 | BCD to decimal decoder/Nixie tube driver | ||

| 42 | ИД6 | BCD to decimal decoder | |

| 43 | excess-3 to decimal decoder | ||

| 44 | excess-3-Gray code to decimal decoder | ||

| 45 | ИД24 | Высоковольтный двоично-десятичный дешифратор | |

| 46 | дешифратор-драйвер 7-сегм. индикатора с 30-вольтными открытыми выходами L-типа индикатора с 30-вольтными открытыми выходами L-типа | ||

| 47 | дешифратор-драйвер 7-сегм. индикатора с 15-вольтными открытыми выходами L-типа | ||

| 48 | дешифратор-драйвер 7-сегм. индикатора с внутренними подтяжками | ||

| 49 | дешифратор-драйвер 7-сегм. индикатора с открытыми выходами L-типа | ||

| 50 | ЛР1 | 2 элемента 2+2И-2ИЛИ-НЕ, один расширяем по ИЛИ | |

| 51 | ЛР11 | 2 элемента 2+2И-2ИЛИ-НЕ | |

| 52 | expandable 4-wide 2-input AND-OR gate | ||

| 53 | ЛР3 | Логический элемент 2+2+2+3И-4ИЛИ-НЕ, расширяемый по ИЛИ | |

| 54 | ЛР13 | 4-wide 2-input AND-OR-invert gate | |

| 55 | Логический элемент 4+4И-2ИЛИ-НЕ | ||

| (H)55 | ЛР4 | Логический элемент 4+4И-2ИЛИ-НЕ с возможностью расширения по ИЛИ | |

| 56 | 50:1 frequency divider | ||

| 57 | 60:1 frequency divider | ||

| 58 | 2+3И-ИЛИ | ||

| 59 | 2+3И-ИЛИ-НЕ | ||

| 60 | ЛД1 | 2 4-входовых расширителя по ИЛИ | |

| 61 | 3×3-input expander | ||

| 62 | 3-2-2-3AND-OR expander | ||

| 63 | 6 current sensing interface gates | ||

| 64 | ЛР9 | 4-2-3-2AND-OR-invert gate | |

| 65 | ЛР10 | 4-2-3-2 input AND-OR-invert gate with open collector output | |

| 68 | 2×4 bit decade counters | ||

| 69 | 2×4 bit binary counters | ||

| 70 | AND-gated positive edge triggered J-K flip-flop with preset and clear | ||

| (H)71 | AND-or-gated J-K master-slave flip-flop with preset | ||

| (L)71 | AND-gated R-S master-slave flip-flop with preset and clear | ||

| 72 | ТВ1 | JKMS-триггер с логикой 3И на входе, а также асинхронными сбросом и установкой | |

| 73 | 2×J-K flip-flop with clear | ||

| 74 | ТМ2 | 2 DCMS-триггера с записью по фронту со сбросом и установкой | |

| 75 | ТМ7 | 4 D-триггера с прямым и инверсным выходом | |

| 76 | ТК3 | 2 JK-триггера со сбросом и установкой | |

| 77 | ТМ5 | 4 D-триггера | |

| (H)78 | 2×positive pulse triggered J-K flip-flop with preset, common clock, and common clear (different pinout than 74L78 / 74LS78) | ||

| (L)78 | 2×positive pulse triggered J-K flip-flop with preset, common clock, and common clear | ||

| (LS)78 | 2×negative edge triggered J-K flip-flop with preset, common clock, and common clear | ||

| 79 | 2×D flip-flop | ||

| 80 | ИМ1 | Одноразрядный полный сумматор | |

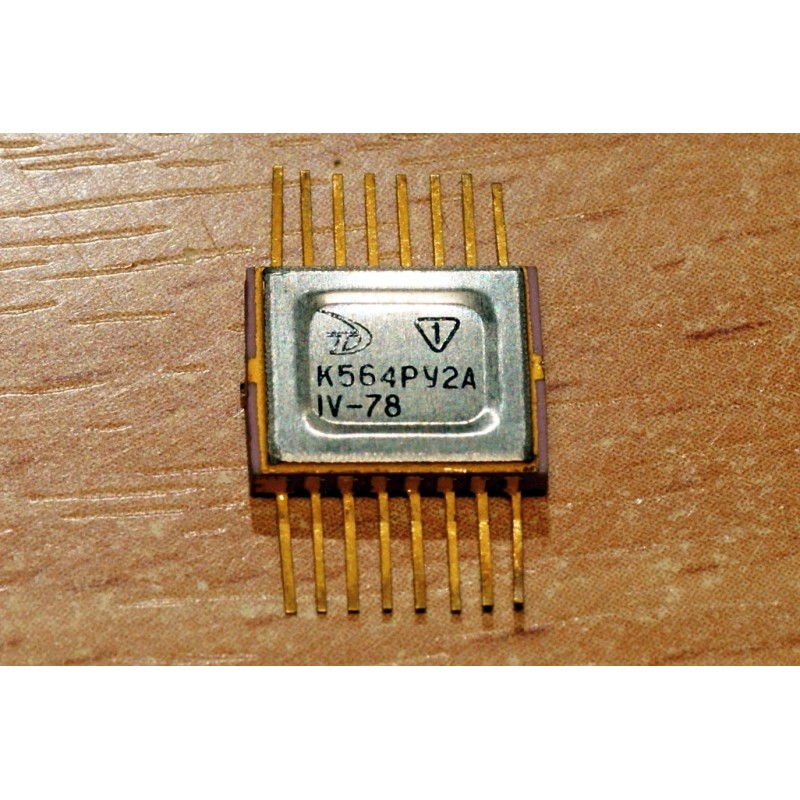

| 81 | РУ1 | Статическое ОЗУ со схемами управления 16×1 | |

| 82 | ИМ2 | 2-разрядный полный сумматор | |

| 83 | ИМ3 | 4-разрядный полный сумматор | |

| 84 | РУ3 | Статическое ОЗУ 4×4 | |

| 85 | СП1 | 4-разрядныя схема сравнения 2-х чисел | |

| 86 | ЛП5 | 4 2-входовых элемента исключающее ИЛИ | |

| 87 | 4-bit true/complement/zero/one element | ||

| 88 | 256-bit read-only memory | ||

| 89 | РУ2 | Статическое ОЗУ 16×4 | |

| 90 | ИЕ2 | Двоично-десятичный счётчик из двух секций (2×5) | |

| 91 | 8-bit shift register, serial In, serial out, gated input | ||

| 92 | ИЕ4 | Счётчик-делитель на 12 из двух секций (2×6) | |

| 93 | ИЕ5 | Двоичный счётчик 4 бита из двух секций (2×8) | |

| 94 | 4-bit shift register, 2×asynchronous presets | ||

| 95 | ИР1 | 4-разрядный сдвиговый регистр с параллельной загрузкой, параллельным выходом и последовательным входом | |

| 96 | 5-bit parallel-In/parallel-out shift register, asynchronous preset | ||

| 97 | ИЕ8 | Делитель частоты с переменным коэффициентом деления | |

| 98 | 4-bit data selector/storage register | ||

| 99 | 4-bit bidirectional universal shift register | ||

| 100 | ТК7 | 2 триггера | |

| 101 | AND-or-gated J-K negative-edge-triggered flip-flop with preset | ||

| 102 | AND-gated J-K negative-edge-triggered flip-flop with preset and clear | ||

| 103 | 2×J-K negative-edge-triggered flip-flop with clear | ||

| 104 | JKMS-триггер | ||

| 105 | JKMS-триггер | ||

| 106 | 2×J-K negative-edge-triggered flip-flop with preset and clear | ||

| 107 | ТВ6 | 2×J-K flip-flop with clear | |

| 107A | 2×J-K negative-edge-triggered flip-flop with clear | ||

| 108 | 2×J-K negative-edge-triggered flip-flop with preset, common clear, and common clock | ||

| 109 | ТВ15 | 2 JKMS-триггера с записью по фронту, инверсным входом K и асинхронным сбросом и установкой | |

| 110 | AND-gated J-K master-slave flip-flop with data lockout | ||

| 111 | 2×J-K master-slave flip-flop with data lockout | ||

| 112 | ТВ9 | 2×J-K negative-edge-triggered flip-flop with clear and preset | |

| 113 | ТВ10 | 2×J-K negative-edge-triggered flip-flop with preset | |

| 114 | ТВ11 | 2×J-K negative-edge-triggered flip-flop with preset, common clock and clear | |

| 116 | 2×4-bit latch with clear | ||

| 118 | 6×set/reset latch | ||

| 119 | 6×set/reset latch | ||

| 120 | 2×pulse synchronizer/drivers | ||

| 121 | АГ1 | Одновибратор с логическим элементом на входе | |

| 122 | retriggerable monostable multivibrator with clear | ||

| 123 | АГ3 | 2 одновибратора с повторным запуском | |

| 124 | ГГ1 | 2 генератора управляемые напряжением | |

| 125 | ЛП8 | 4 буфера с тремя состояниями на выходе и инверсным разрешением | |

| 126 | 4 буфера с прямым разрешением выхода | ||

| 128 | ЛЕ6 | 4×2ИЛИ-НЕ с магистральными усилителями | |

| 130 | 4×2И gate buffer with 30 v open collector outputs | ||

| 131 | 4×2И gate buffer with 15 v open collector outputs | ||

| 132 | ТЛ3 | 4×2И-НЕ с триггерам Шмитта | |

| 133 | 13И-НЕ gate | ||

| 134 | ЛА19 | 12И-НЕ gate with three-state output | |

| 135 | 4×exclusive-or/NOR gate | ||

| 136 | ЛЛ3 | 4×2искл. ИЛИ с открытым коллектором (стоком) ИЛИ с открытым коллектором (стоком) | |

| 137 | 3 to 8-line decoder/demultiplexer with address latch | ||

| 138 | ИД7 | 3 to 8-line decoder/demultiplexer | |

| 139 | ИД14 | 2 дешифратора / демультиплексора 2 в 4 | |

| 140 | ЛА6 | 2×4И-НЕ line driver | |

| 141 | ИД1 | Двоично-десятичный дешифратор с высоковольтными выходами для газоразрядных индикаторов | |

| 142 | decade counter/latch/decoder/driver for Nixie tubes | ||

| 143 | decade counter/latch/decoder/7-segment driver, 15 ma constant current | ||

| 144 | decade counter/latch/decoder/7-segment driver, 15 v open collector outputs | ||

| 145 | ИД10 | Двоично-десятичный дешифратор | |

| 147 | 10-line to 4-line priority encoder | ||

| 148 | ИВ1 | Приоритетный шифратор 8 в 3 | |

| 150 | КП1 | Мультиплексор на 16 каналов со стробированием | |

| 151 | КП7 | Мультиплексор на 8 каналов со стробированием | |

| 152 | КП5 | Мультиплексор на 8 каналов | |

| 153 | КП2 | Сдвоенный мультиплексор на 4 канала | |

| 154 | ИД3 | Дешифратор-демультиплексор 4 в 16 | |

| 155 | ИД4 | Сдвоенный дешифратор-демультиплексор 2 в 4 | |

| 156 | 2×2-line to 4-line decoder/demultiplexer with open collector outputs | ||

| 157 | 4×2-line to 1-line data selector/multiplexer, noninverting | ||

| 158 | 4×2-line to 1-line data selector/multiplexer, inverting | ||

| 159 | 4-line to 16-line decoder/demultiplexer with open collector outputs | ||

| 160 | ИЕ9 | Синхронный декадный счётчик с асинхронным сбросом | |

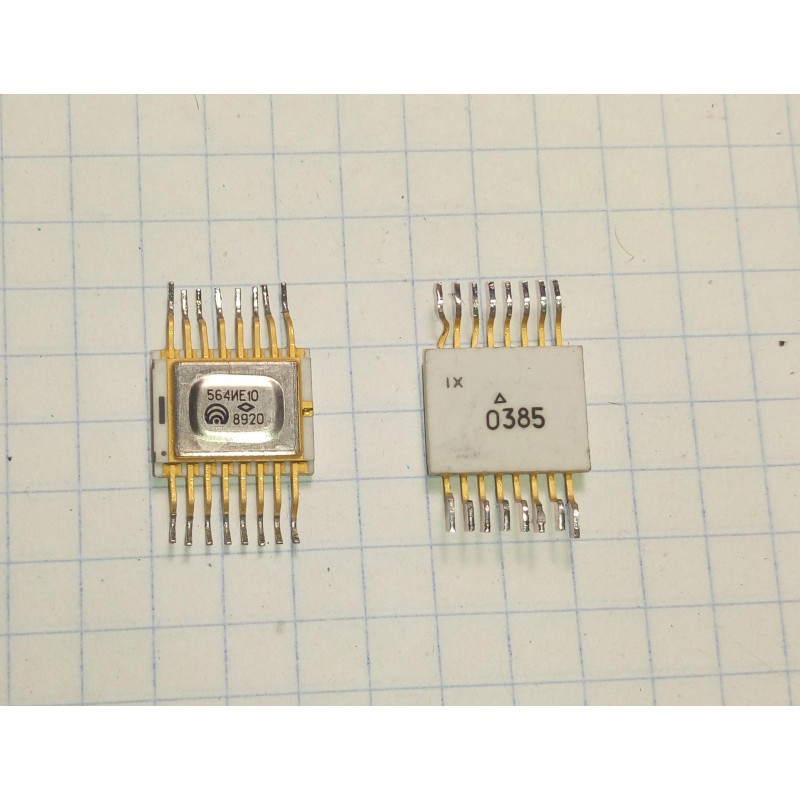

| 161 | ИЕ10 | Синхронный 4-разрядный двоичный счётчик с асинхронным сбросом | |

| 162 | synchronous 4-bit decade counter with synchronous clear | ||

| 163 | synchronous 4-bit binary counter with synchronous clear | ||

| 164 | ИР8 | 8-bit parallel-out serial shift register with asynchronous clear | |

| 165 | ИР9 | 8-bit serial shift register, parallel Load, complementary outputs | |

| 166 | parallel-Load 8-bit shift register | ||

| 167 | synchronous decade rate multiplier | ||

| 168 | ИЕ16 | synchronous 4-bit up/down decade counter | |

| 169 | ИЕ17 | synchronous 4-bit up/down binary counter | |

| 170 | ИР32 РП1 | Регистровый файл 4×4 с открытыми выходами L-типа | |

| 172 | РП3 | Многопортовая регистровая память с тремя состояниями на выходе 8×2 | |

| 173 | ИР15 | 4-разрядный регистр с тремя состояниями | |

| 174 | ТМ9 | 6×d flip-flop with common clear | |

| 175 | ТМ8 | 4×d edge-triggered flip-flop with complementary outputs and asynchronous clear | |

| 176 | presettable decade (bi-quinary) counter/latch | ||

| 177 | presettable binary counter/latch | ||

| 178 | 4-bit parallel-access shift register | ||

| 179 | 4-bit parallel-access shift register with asynchronous clear and complementary Qd outputs | ||

| 180 | ИП2 | 8(9)-разрядная схема контроля чётности / нечётности | |

| 181 | ИП3 | 4-разрядное арифметико-логическое устройство | |

| 182 | ИП4 | 4-разрядный схема ускоренного переноса | |

| 183 | 2×carry-save full adder | ||

| 184 | ПР6 | Преобразователь двоично-десятичного кода в двоичный | |

| 185 | ПР7 | Преобразователь двоичного кода в двоично-десятичный | |

| 186 | 512-bit (64×8) read-only memory with open collector outputs | ||

| 187 | РЕ21—24 | 1кбит ПЗУ (256×4) с открытыми выходами L-типа | |

| 188 | 256-bit (32×8) programmable read-only memory with open collector outputs | ||

| 189 | 64-bit (16×4) ram with inverting three-state outputs | ||

| 190 | synchronous up/down decade counter | ||

| 191 | synchronous up/down binary counter | ||

| 192 | ИЕ6 | Синхронный реверсивный декадный счётчик с параллельной загрузкой | |

| 193 | ИЕ7 | Синхронный реверсивный 4-разрядный двоичный счётчик с параллельной загрузкой | |

| 194 | ИР11 | 4-bit bidirectional universal shift register | |

| 195 | ИР12 | 4-bit parallel-access shift register | |

| 196 | ИЕ14 | Асинхронный двоично-десятичный счётчик с установкой | |

| 197 | ИЕ15 | Асинхронный 4-разрядный двоичный счётчик с установкой | |

| 198 | ИР13 | 8-разрядный двунаправденный сдвиговый регистр | |

| 199 | 8-bit bidirectional universal shift register with J-Not-K serial inputs | ||

| 200 | 256-bit ram with three-state outputs | ||

| 201 | 256-bit (256×1) ram with three-state outputs | ||

| 206 | 256-bit ram with open collector outputs | ||

| 209 | 1024-bit (1024×1) ram with three-state output | ||

| 210 | 8×buffer | ||

| 219 | 64-bit (16×4) ram with noninverting three-state outputs | ||

| 221 | 2×monostable multivibrator with schmitt trigger input | ||

| 222 | 16 by 4 synchronous FIFO memory with three-state outputs | ||

| 224 | 16 by 4 synchronous FIFO memory with three-state outputs | ||

| 225 | asynchronous 16×5 FIFO memory | ||

| 226 | 4-bit parallel latched bus transceiver with three-state outputs | ||

| 230 | 8×buffer/driver with three-state outputs | ||

| 232 | 4×NOR Schmitt trigger | ||

| 237 | 1-of-8 decoder/demultiplexer with address latch, active high outputs | ||

| 238 | 1-of-8 decoder/demultiplexer, active high outputs | ||

| 239 | 2×2-of-4 decoder/demultiplexer, active high outputs | ||

| 240 | АП3 | 8×buffer with Inverted three-state outputs | |

| 241 | АП4 | 8×buffer with noninverted three-state outputs | |

| 242 | ИП6 | 4×bus transceiver with Inverted three-state outputs | |

| 243 | ИП7 | 4×bus transceiver with noninverted three-state outputs | |

| 244 | 8×buffer with noninverted three-state outputs | ||

| 245 | АП6 | 8×bus transceiver with noninverted three-state outputs | |

| 246 | BCD to 7-segment decoder/driver with 30 v open collector outputs | ||

| 247 | BCD to 7-segment decoder/driver with 15 v open collector outputs | ||

| 248 | BCD to 7-segment decoder/driver with Internal Pull-up outputs | ||

| 249 | BCD to 7-segment decoder/driver with open collector outputs | ||

| 251 | КП15 | 8-line to 1-line data selector/multiplexer with complementary three-state outputs | |

| 253 | КП12 | 2×4-line to 1-line data selector/multiplexer with three-state outputs | |

| 255 | 2×4-bit addressable latch | ||

| 256 | 2×4-bit addressable latch | ||

| 257 | КП11 | Счетверёный мультиплексор на 2 канала с тремя состояниями на выходе | |

| 258 | КП14 | 4×2-line to 1-line data selector/mulitplexer with Inverted three-state outputs | |

| 259 | 8-bit addressable latch | ||

| 260 | ЛЕ7 | 2×5ИЛИ-НЕ gate | |

| 261 | ИП8 | 2-bit by 4-bit parallel binary multiplier | |

| 265 | 4×complementary output elements | ||

| 266 | 4×2-input XNOR gate with open collectoroutputs | ||

| 270 | 2048-bit (512×4) read only memory with open collector outputs | ||

| 271 | 2048-bit (256×8) read only memory with open collector outputs | ||

| 273 | 8-bit register with reset | ||

| 274 | 4-bit by 4-bit binary multiplier | ||

| 275 | 7-bit slice Wallace tree | ||

| 276 | 4×J-Not-K edge-triggered Flip-Flops with separate clocks, common preset and clear | ||

| 278 | 4-bit cascadeable priority registers with latched data inputs | ||

| 279 | ТР2 | 4×set-reset latch | |

| 280 | 9-bit odd/even Parity bit Generator/checker | ||

| 281 | 4-bit parallel binary accumulatOR | ||

| 283 | ИМ6 | 4-bit binary Full adder | |

| 284 | 4-bit by 4-bit parallel binary multiplier (low order 4 bits of product) | ||

| 285 | 4-bit by 4-bit parallel binary multiplier (high order 4 bits of product) | ||

| 287 | 1024-bit (256×4) programmable read-only memory with three-state outputs | ||

| 288 | 256-bit (32×8) programmable read-only memory with three-state outputs | ||

| 289 | 64-bit (16×4) RAM with open collector outputs | ||

| 290 | decade counter (separate divide-by-2 and divide-by-5 sections) | ||

| 291 | 4-bit universal shift register, binary up/down counter, synchronous | ||

| 292 | programmable frequency divider/digital timer | ||

| 293 | 4-bit binary counter (separate divide-by-2 and divide-by-8 sections) | ||

| 294 | programmable frequency divider/digital timer | ||

| 295 | ИР16 | 4-bit bidirectional register with three-state outputs | |

| 297 | digital phase-locked-loop filter | ||

| 298 | КП13 | 4×2-input multiplexer with storage | |

| 299 | ИР24 | 8-bit bidirectional universal shift/storage register with three-state outputs | |

| 301 | РУ6 | Статическое ОЗУ (256×1) с открытыми выходами L-типа | |

| 309 | 1024-bit (1024×1) random access memory with open collector output | ||

| 310 | 8×buffer with Schmitt trigger inputs | ||

| 314 | 1024-bit random access memory | ||

| 320 | crystal controlled oscillator | ||

| 322 | ИР28 | 8-bit shift register with sign extend, three-state outputs | |

| 323 | 8-bit bidirectional universal shift/storage register with three-state outputs | ||

| 324 | voltage controlled oscillator (OR crystal controlled) | ||

| 340 | 8×buffer with Schmitt trigger inputs and three-state inverted outputs | ||

| 341 | 8×buffer with Schmitt trigger inputs and three-state noninverted outputs | ||

| 344 | 8×buffer with Schmitt trigger inputs and three-state noninverted outputs | ||

| 348 | 8 to 3-line priority encoder with three-state outputs | ||

| 350 | 4-bit shifter with three-state outputs | ||

| 351 | 2×8-line to 1-line data selectors/multiplexers with three-state outputs and 4 common data inputs | ||

| 352 | 2×4-line to 1-line data selectors/multiplexers with inverting outputs | ||

| 353 | 2×4-line to 1-line data selectors/multiplexers with inverting three-state outputs | ||

| 354 | 8 to 1-line data selector/multiplexer with transparent latch, three-state outputs | ||

| 356 | 8 to 1-line data selector/multiplexer with edge-triggered register, three-state outputs | ||

| 358 | ИМ7 | ||

| 361 | bubble memory function timing generator | ||

| 362 | four-phase clock generator/driver | ||

| 365 | ЛП10 | 6 буферов с тремя состояниями на выходе и логикой ИЛИ-НЕ на входе разрешения | |

| 366 | ЛН6 | 6 инвертирующих буферов тремя состояниями на выходе и логикой ИЛИ-НЕ на входе разрешения | |

| 367 | ЛП11 | 6 буферов с тремя состояниями на выходе и двумя входами рарешения (4+2) | |

| 368 | 6 инвертирующих буферов тремя состояниями на выходе и двумя входами рарешения (4+2) | ||

| 370 | 2048-bit (512×4) read-only memory with three-state outputs | ||

| 371 | 2048-bit (256×8) read-only memory with three-state outputs | ||

| 373 | ИР22 | 8-разрядная защёлка с разрешением выхода | |

| 374 | ИР23 | 8-разрядный регистр с разрешением выхода | |

| 375 | 4×bistable latch | ||

| 376 | 4×J-Not-K flip-flop with common clock and common clear | ||

| 377 | ИР27 | 8-разрядный буферный регистр с разрешением записи | |

| 378 | 6-bit register with clock enable | ||

| 379 | 4-bit register with clock enable and complementary outputs | ||

| 380 | 8-bit multifunction register | ||

| 381 | ИК2 | 4-bit arithmetic logic unit/function generator with generate and propagate outputs | |

| 382 | 4-bit arithmetic logic unit/function generator with ripple carry and overflow outputs | ||

| 384 | ИП9 | ||

| 385 | ИМ7 | 4×4-bit adder/subtractor | |

| 386 | 4×2искл. ИЛИ ИЛИ | ||

| 387 | 1024-bit (256×4) programmable read-only memory with open collector outputs | ||

| 388 | 4-bit register with standard and three-state outputs | ||

| 390 | 2×4-bit decade counter | ||

| 393 | 2×4-bit binary counter | ||

| 395 | ИР25 | 4-bit universal shift register with three-state outputs | |

| 398 | 4×2-input mulitplexers with storage and complementary outputs | ||

| 399 | 4×2-input mulitplexer with storage | ||

| 408 | 8-bit parity tree | ||

| 412 | multi-mode buffered 8-bit latches with three-state outputs and clear | ||

| 423 | 2×retriggerable monostable multivibrator | ||

| 424 | two-phase clock generator/driver | ||

| 425 | 4×gates with three-state outputs and active low enables | ||

| 426 | 4×gates with three-state outputs and active high enables | ||

| 428 | system controller for 8080a | ||

| 438 | system controller for 8080a | ||

| 440 | 4×tridirectional bus transceiver with noninverted open collector outputs | ||

| 441 | 4×tridirectional bus transceiver with Inverted open collector outputs | ||

| 442 | 4×tridirectional bus transceiver with noninverted three-state outputs | ||

| 443 | 4×tridirectional bus transceiver with Inverted three-state outputs | ||

| 444 | 4×tridirectional bus transceiver with Inverted and noninverted three-state outputs | ||

| 448 | 4×tridirectional bus transceiver with Inverted and noninverted open collector outputs | ||

| 450 | 16-to-1 multiplexer with complementary outputs | ||

| 451 | 2×8-to-1 multiplexer | ||

| 452 | 2×decade counter, synchronous | ||

| 453 | 2×binary counter, synchronous | ||

| 453 | 4×4-to-1 multiplexer | ||

| 454 | 2×decade up/down counter, synchronous, preset input | ||

| 455 | 2×binary up/down counter, synchronous, preset input | ||

| 456 | NBCD (Natural binary coded decimal) adder | ||

| 460 | bus transfer switch | ||

| 461 | 8-bit presettable binary counter with three-state outputs | ||

| 462 | fiber-optic link transmitter | ||

| 463 | fiber-optic link receiver | ||

| 465 | 8×buffer with three-state outputs | ||

| 468 | 2×mos-to-ttL level converter | ||

| 470 | 2048-bit (256×8) programmable read-only memory with open collector outputs | ||

| 471 | 2048-bit (256×8) programmable read-only memory with three-state outputs | ||

| 472 | programmable read-only memory with open collector outputs | ||

| 473 | programmable read-only memory with three-state outputs | ||

| 474 | programmable read-only memory with open collector outputs | ||

| 475 | programmable read-only memory with three-state outputs | ||

| 481 | 4-bit slice processor elements | ||

| 482 | ВГ1 | 4-bit slice expandable control elements | |

| 484 | BCD-to-binary converter | ||

| 485 | binary-to-BCD converter | ||

| 490 | 2×decade counter | ||

| 491 | 10-bit binary up/down counter with limited preset and three-state outputs | ||

| 498 | 8-bit bidirectional shift register with parallel inputs and three-state outputs | ||

| 508 | 8-bit multiplier/divider | ||

| 520 | 8-bit comparator | ||

| 521 | 8-bit comparator | ||

| 526 | fuse programmable identity comparator, 16 bit | ||

| 527 | fuse programmable identity comparator, 8 bit + 4 bit conventional Identity comparator | ||

| 528 | fuse programmable Identity comparator, 12 bit | ||

| 531 | 8×transparent latch with 32 ma three-state outputs | ||

| 532 | 8×register with 32 ma three-state outputs | ||

| 533 | 8×transparent latch with inverting three-state Logic outputs | ||

| 534 | 8×register with inverting three-state outputs | ||

| 535 | 8×transparent latch with inverting three-state outputs | ||

| 536 | 8×register with inverting 32 ma three-state outputs | ||

| 537 | BCD to decimal decoder with three-state outputs | ||

| 538 | 1 of 8 decoder with three-state outputs | ||

| 539 | 2×1 of 4 decoder with three-state outputs | ||

| 540 | inverting 8×buffer with three-state outputs | ||

| 541 | non-inverting 8×buffer with three-state outputs | ||

| 558 | 8-bit by 8-bit multiplier with three-state outputs | ||

| 560 | 4-bit decade counter with three-state outputs | ||

| 561 | 4-bit binary counter with three-state outputs | ||

| 563 | 8-bit d-type transparent latch with inverting three-state outputs | ||

| 564 | 8-bit d-type edge-triggered register with inverting three-state outputs | ||

| 568 | decade up/down counter with three-state outputs | ||

| 569 | binary up/down counter with three-state outputs | ||

| 573 | 8-разрядная защёлка с разрешением выхода (иная цоколёвка, нежели 373) | ||

| 574 | 8-разрядный регистр с разрешением выхода (иная цоколёвка, нежели 374) | ||

| 575 | 8×D-type flip-flop with synchronous clear, three-state outputs | ||

| 576 | 8×D-type flip-flop with inverting three-state outputs | ||

| 577 | 8×D-type flip-flop with synchronous clear, inverting three-state outputs | ||

| 580 | 8×transceiver/latch with inverting three-state outputs | ||

| 589 | 8-bit shift register with input latch, three-state outputs | ||

| 590 | 8-bit binary counter with output registers and three-state outputs | ||

| 592 | 8-bit binary counter with input registers | ||

| 593 | 8-bit binary counter with input registers and three-state outputs | ||

| 594 | serial-in shift register with output registers | ||

| 595 | serial-in shift register with output latches | ||

| 596 | serial-in shift register with output registers and open collector outputs | ||

| 597 | serial-out shift register with input latches | ||

| 598 | shift register with input latches | ||

| 600 | dynamic memory refresh controller, transparent and burst modes, for 4K or 16K drams | ||

| 601 | dynamic memory refresh controller, transparent and burst modes, for 64K drams | ||

| 602 | dynamic memory refresh controller, cycle steal and burst modes, for 4K or 16K drams | ||

| 603 | dynamic memory refresh controller, cycle steal and burst modes, for 64K drams | ||

| 604 | 8×2-input multiplexer with latch, high-speed, with three-state outputs | ||

| 605 | 8×2-input mulitplexer with latch, high-speed, with open collector outputs | ||

| 606 | 8×2-input mulitplexer with latch, glitch-free, with three-state outputs | ||

| 607 | 8×2-input mulitplexer with latch, glitch-free, with open collector outputs | ||

| 608 | memory cycle controller | ||

| 610 | memory mapper, latched, three-state outputs | ||

| 611 | memory mapper, latched, open collector outputs | ||

| 612 | memory mapper, three-state outputs | ||

| 613 | memory mapper, open collector outputs | ||

| 620 | 8×bus transceiver, inverting, three-state outputs | ||

| 621 | 8×bus transceiver, noninverting, open collector outputs | ||

| 622 | 8×bus transceiver, inverting, open collector outputs | ||

| 623 | 8×bus transceiver, noninverting, three-state outputs | ||

| 624 | voltage-controlled oscillator with enable control, range control, two-phase outputs | ||

| 625 | 2×voltage-controlled oscillator with two-phase outputs | ||

| 626 | 2×voltage-controlled oscillator with enable control, two-phase outputs | ||

| 627 | 2 ГУН | ||

| 628 | voltage-controlled oscillator with enable control, range control, external temperature compensation, and two-phase outputs | ||

| 629 | 2×voltage-controlled oscillator with enable control, range control | ||

| 630 | ВЖ1 | 16-bit error detection and correction (EDAC) with three-state outputs | |

| 631 | 16-bit error detection and correction with open collector outputs | ||

| 632 | 32-bit error detection and correction | ||

| 638 | 8×bus transceiver with inverting three-state outputs | ||

| 639 | 8×bus transceiver with noninverting three-state outputs | ||

| 640 | 8×bus transceiver with inverting three-state outputs | ||

| 641 | 8×bus transceiver with noninverting open collector outputs | ||

| 642 | 8×bus transceiver with inverting open collector outputs | ||

| 643 | 8×bus transceiver with mix of inverting and noninverting three-state outputs | ||

| 644 | 8×bus transceiver with mix of inverting and noninverting open collector outputs | ||

| 645 | 8×bus transceiver | ||

| 646 | 8×bus transceiver/latch/multiplexer with noninverting three-state outputs | ||

| 647 | 8×bus transceiver/latch/multiplexer with noninverting open collector outputs | ||

| 648 | 8×bus transceiver/latch/multiplexer with inverting three-state outputs | ||

| 649 | 8×bus transceiver/latch/multiplexer with inverting open collector outputs | ||

| 651 | 8×bus transceiver/register with inverting three-state outputs | ||

| 652 | 8×bus transceiver/register with noninverting three-state outputs | ||

| 653 | 8×bus transceiver/register with inverting three-state and open collector outputs | ||

| 654 | 8×bus transceiver/register with noninverting three-state and open collector outputs | ||

| 658 | 8×bus transceiver with Parity, inverting | ||

| 659 | 8×bus transceiver with Parity, noninverting | ||

| 664 | 8×bus transceiver with Parity, inverting | ||

| 665 | 8×bus transceiver with Parity, noninverting | ||

| 668 | synchronous 4-bit decade Up/down counter | ||

| 669 | synchronous 4-bit binary Up/down counter | ||

| 670 | ИР26 | Регистровый файл 4×4 с тремя состояниями на выходе | |

| 671 | 4-bit bidirectional shift register/latch /multiplexer with three-state outputs | ||

| 672 | 4-bit bidirectional shift register/latch/multiplexer with three-state outputs | ||

| 673 | 16-bit serial-in serial-out shift register with output storage registers, three-state outputs | ||

| 674 | 16-bit parallel-in serial-out shift register with three-state outputs | ||

| 677 | 16-bit address comparator with enable | ||

| 678 | 16-bit address comparatOR with latch | ||

| 679 | 12-bit address comparatOR with latch | ||

| 680 | 12-bit address comparatOR with enable | ||

| 681 | 4-bit parallel binary accumulatOR | ||

| 682 | 8-bit magnitude comparator | ||

| 683 | 8-bit magnitude comparatOR with open collector outputs | ||

| 684 | 8-bit magnitude comparatOR | ||

| 685 | 8-bit magnitude comparatOR with open collector outputs | ||

| 686 | 8-bit magnitude comparatOR with enable | ||

| 687 | 8-bit magnitude comparatOR with enable | ||

| 688 | 8-bit equality comparatOR | ||

| 689 | 8-bit magnitude comparatOR with open collector outputs | ||

| 690 | three state outputs | ||

| 691 | 4-bit binary counter/latch/multiplexer with asynchronous reset, three-state outputs | ||

| 692 | 4-bit decimal counter/latch/multiplexer with synchronous reset, three-state outputs | ||

| 693 | 4-bit binary counter/latch/multiplexer with synchronous reset, three-state outputs | ||

| 694 | 4-bit decimal counter/latch/multiplexer with synchronous and asynchronous resets, three-state outputs | ||

| 695 | 4-bit binary counter/latch/multiplexer with synchronous and asynchronous resets, three-state outputs | ||

| 696 | 4-bit decimal counter/register/multiplexer with asynchronous reset, three-state outputs | ||

| 697 | 4-bit binary counter/register/multiplexer with asynchronous reset, three-state outputs | ||

| 698 | 4-bit decimal counter/register/multiplexer with synchronous reset, three-state outputs | ||

| 699 | 4-bit binary counter/register/multiplexer with synchronous reset, three-state outputs | ||

| 716 | programmable decade counter | ||

| 718 | programmable binary counter | ||

| 724 | voltage controlled multivibratOR | ||

| 740 | 8×buffer/Line driver, inverting, three-state outputs | ||

| 741 | 8×buffer/Line driver, noninverting, three-state outputs, mixed enable polarity | ||

| 744 | 8×buffer/Line driver, noninverting, three-state outputs | ||

| 748 | 8-входовой приортиетный шифратор | ||

| 779 | 8-bit bidirectional binary counter (3-state) | ||

| 783 | synchronous address mulitplexer | ||

| 790 | error detection and correction (EDAC) | ||

| 794 | 8-bit register with readback | ||

| 795 | 8×buffer with three-state outputs | ||

| 796 | 8×buffer with three-state outputs | ||

| 797 | 8×buffer with three-state outputs | ||

| 798 | 8×buffer with three-state outputs | ||

| 804 | 6×2И-НЕ drivers | ||

| 805 | 6×2ИЛИ-НЕ drivers | ||

| 808 | 6×2И drivers | ||

| 832 | 6×2ИЛИ drivers | ||

| 848 | 8 to 3-line priority encoder with three-state outputs | ||

| 873 | 8×transparent latch | ||

| 874 | 8×d-type flip-flop | ||

| 876 | 8×d-type flip-flop with inverting outputs | ||

| 878 | 2×4-bit d-type flip-flop with synchronous clear, noninverting three-state outputs | ||

| 879 | 2×4-bit d-type flip-flop with synchronous clear, inverting three-state outputs | ||

| 880 | 8×transparent latchwith inverting outputs | ||

| 882 | 32-bit lookahead carry generator | ||

| 888 | 8-bit slice processor | ||

| 926 | 4-digit counter/display driver | ||

| 935 | 3. 5-digit digital voltmeter (DVM) support chip for multiplexed 7-segment displays 5-digit digital voltmeter (DVM) support chip for multiplexed 7-segment displays | ||

| 936 | 3.75-digit digital voltmeter (DVM) support chip for multiplexed 7-segment displays | ||

| 1005 | 6×inverting buffer with open-collector output | ||

| 1035 | 6×noninverting buffers with open-collector outputs | ||

| 2960 | error detection and correction (EDAC) | ||

| 2961 | edac bus buffer, inverting | ||

| 2962 | edac bus buffer, noninverting | ||

| 2968 | dynamic memory controller | ||

| 2969 | memory timing controller for use with EDAC | ||

| 2970 | memory timing controller for use without EDAC | ||

| 4002 | 2×4ИЛИ-НЕ | ||

| 4015 | 2×4-bit shift registers | ||

| 4017 | 5-stage ÷10 Johnson counter | ||

| 4020 | 14-stage binary counter | ||

| 4024 | 7 stage ripple carry binary counter | ||

| 4028 | BCD to decimal decoder | ||

| 4040 | 12-stage binary ripple counter | ||

| 4046 | phase-locked loop and voltage-controlled oscillator | ||

| 4049 | 6 НЕ с буфером | ||

| 4050 | 6×buffer/converter (non-inverting) | ||

| 4051 | high-speed CMOS 8-channel analog mulitplexer/demultiplexer | ||

| 4052 | 2×4-channel analog multiplexer/demultiplexers | ||

| 4053 | 3×2-channel analog multiplexer/demultiplexers | ||

| 4059 | programmable divide-by-N counter | ||

| 4060 | 14-stage binary ripple counter with oscillator | ||

| 4066 | 4×bilateral switches | ||

| 4067 | 16-channel analog multiplexer/demultiplexer | ||

| 4075 | 3×3ИЛИ | ||

| 4078 | 8ИЛИ/ИЛИ-НЕ | ||

| 4094 | 8-bit three-state shift register/latch | ||

| 4316 | 4 аналоговых ключа | ||

| 4511 | Дешифратор 7-сегментного индикатора | ||

| 4520 | 2×4-разрядных двоичных счётчика | ||

| 4538 | 2×retriggerable precision monostable multivibrator | ||

| 7007 | 6 буферов | ||

| 7266 | 4×2искл. ИЛИ-НЕ ИЛИ-НЕ | ||

| 29841 | 10-bit bus-interface D-type latch with 3-state outputs | ||

| 40103 | presettable 8-bit synchronous down counter | ||

| 40105 | 4-bit by 16-word FIFO register | ||

| АП1 | Формирователь разрядной записи | ||

| АП5 | 2 формирователя сигналов с тремя состояниями | SN75113 | |

| ИД8 | Дешифратор для управления неполной матрицей 7 х 5 точек | ||

| ИД9 | Дешифратор для управления дискретной матрицей на светодиодах | ||

| ИД11 | Позиционный дешифратор 3 в 8 для управления светодиодной шкалой (1 точка) | ||

| ИД12 | Позиционный дешифратор 3 в 8 для управления светодиодной шкалой (2 точки) | ||

| ИД13 | Гистограммный дешифратор 3 в 8 для управления светодиодной шкалой | ||

| ИД15 | Дешифратор для управления линейной светоизлучающей шкалой красного цвета | ||

| ИЕ1 | Декадный счетчик с фазоимпульсным представлением информации | ||

| ИК1 | Аm25S05 | ||

| ИР17 | 12-разрядный регистр последовательного приближения | Am2504 | |

| ИР18 | Аm25S07 | ||

| ИР19 | Аm25S08 | ||

| ИР20 | Аm25S09 | ||

| ИР21 | Аm25S10 | ||

| ЛА18 | 2×2И-НЕ с мощным открытым выходом L-типа | SN75452 | |

| ЛД3 | 8-входовой расширитель по ИЛИ | ||

| ЛИ5 | 2×2И с мощным открытым выходом L-типа | SN75451 | |

| ЛЛ2 | Формирователь втекающего тока | SN75453 | |

| ЛП7 | Два логических элемента 2И-НЕ с общим входом и двумя мощными транзисторами | SN75450 | |

| ПП5 | Преобразователь двоичного кода в код семисегментного индикатора | ||

| РЕ3 | Программируемое ПЗУ емкостью 256 бит (32×8) | 82S23 | |

| РЕ4 | ПЗУ (2К×8) | 6275-1 | |

| РУ5 | Статическое ОЗУ со схемами разрядного и адресного управления (256×1) | 93410 | |

| РУ7 | Статическое ОЗУ (1024×1) со схемами управления | 93425А | |

| УД1 | ОУ широкого применения (неясно, как он попал в серию 155) | SN72709 | |

| ХЛ1 | Многофункциональный элемент для ЭВМ |

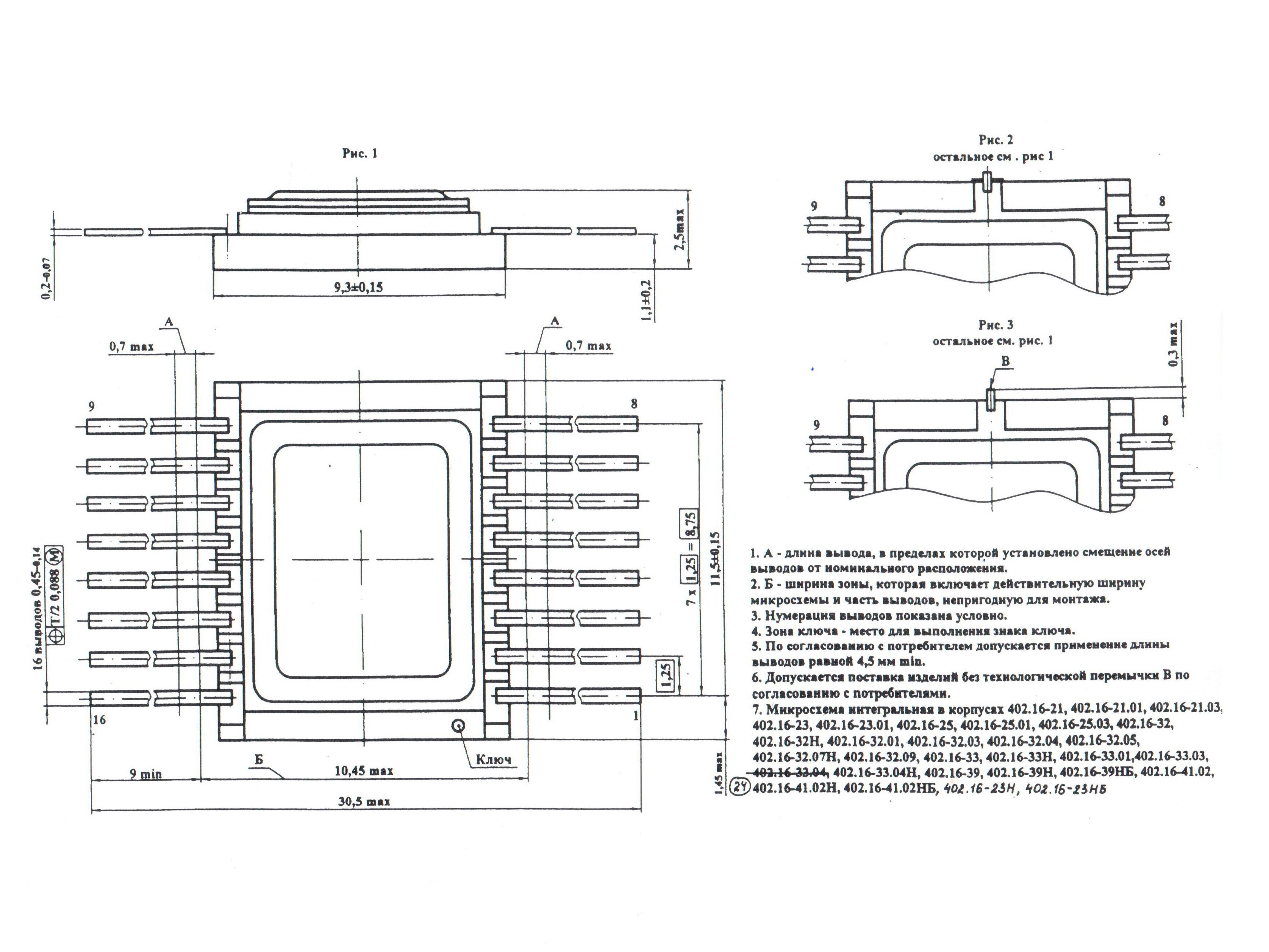

| Обозначение | Прототип | Функциональное назначение | Категория качества | Тип корпуса | ||

|---|---|---|---|---|---|---|

| 1554ТМ8ТБМ | 54AC175 | Четыре D-триггера с общими входами управления и сброса | ВП, ОСМ | 402. | ||

| 1554ТМ9ТБМ | 54AC174 | Шесть D-триггеров | ВП, ОСМ | 402.16-32 | ||

| 1554ТР2ТБМ | 54AC279 | Четыре R-S триггера | ВП, ОСМ | 402.16-32 | ||

| 1554КП12ТБМ | 54AC253 | Два селектора-мультиплексора 4-1 с тремя состояниями на выходе | ВП, ОСМ | 402. | ||

| 1554КП14ТБМ | 54AC258 | Четыре селектора-мультиплексора 2-1 с тремя состояниями и инверсией на выходе | ВП, ОСМ | 402.16-32 | ||

| 1554КП15ТБМ | 54AC251 | Селектор-мультиплексор 8-1 с тремя состояниями на выходе | ВП, ОСМ | 402.16-32 | ||

| 1554КП16ТБМ | 54AC157 | Четыре селектора-мультиплексора 2-1 | ВП, ОСМ | 402. | ||

| 1554КП18ТБМ | 54AC158 | Четыре селектора-мультиплексора 2-1 с инверсией на выходе | ВП, ОСМ | 402.16-32 | ||

| 1554ЛА1ТБМ | 54AC20 | Два логических элемента “4И-НЕ” | ВП, ОСМ | 401.14-5 | ||

| 1554ЛА2ТБМ | 54AC30 | Логический элемент “8И-НЕ” | ВП, ОСМ | 401. | ||

| 1554ЛА3ТБМ | 54AC00 | Четыре логических элемента “2И-НЕ” | ВП, ОСМ | 401.14-5 | ||

| 1554ЛА4ТБМ | 54AC10 | Три логических элемента”3И-НЕ” | ВП, ОСМ | 401.14-5 | ||

| 1554ЛЕ1ТБМ | 54AC02 | Четыре логических элемента “2ИЛИ-НЕ” | ВП, ОСМ | 401. | ||

| 1554ЛИ1ТБМ | 54AC08 | Четыре логических элемента “2И” | ВП, ОСМ | 401.14-5 | ||

| 1554ЛИ3ТБМ | 54AC11 | Три логических элемента “3И” | ВП, ОСМ | 401.14-5 | ||

| 1554ЛИ6ТБМ | 54AC21 | Два логических элемента “4И” | ВП, ОСМ | 401.14-5 | ||

| 1554ЛИ9ТБМ | 54AC34 | Шесть логических повторителей | ВП, ОСМ | 401. | ||

| 1554ЛЛ1ТБМ | 54AC32 | Четыре логических элемента “2ИЛИ” | ВП, ОСМ | 401.14-5 | ||

| 1554ЛН1ТБМ | 54AC04 | Шесть логических элементов “НЕ” | ВП, ОСМ | 401.14-5 | ||

| 1554ЛН2УБМ | TC7S04 | Единичный инвертор | ВП | 01.06.5221 | ||

| 1554ЛП5ТБМ | 54AC86 | Четыре двухвходовых логических элемента “Исключающее ИЛИ” | ВП, ОСМ | 401. | ||

| 1554ЛП8ТБМ | 54AC125 | Четыре буферных элемента с тремя состояниями на выходе | ВП, ОСМ | 401.14-5 | ||

| 1554ЛР11ТБМ | 54AC51 | Логические элементы “2-2И-2ИЛИ-НЕ” и “3-3И-2ИЛИ-НЕ” | ВП, ОСМ | 401.14-5 | ||

| 1554ЛР13ТБМ | 54AC54 | Логический элемент “3-2-2-3И-4ИЛИ-НЕ” | ВП, ОСМ | 401. | ||

| 1554СП1ТБМ | 54AC85 | Схема сравнения двух четырехразрядных чисел | ВП, ОСМ | 402.16-32 | ||

| 1554ТВ9ТБМ | 54AC112 | Два J-K триггера с управлением отрицательным фронтом по тактовому входу | ВП, ОСМ | 402.16-32 | ||

| 1554ТВ15ТБМ | 54AC109 | Два J-K триггера с управлением положительным фронтом по тактовому входу | ВП, ОСМ | 402. | ||

| 1554ТЛ2ТБМ | 54AC14 | Шесть инверторов Шмитта | ВП, ОСМ | 401.14-5 | ||

| 1554ТМ2ТБМ | 54AC74 | Два D-триггера с установкой и сбросом | ВП, ОСМ | 401.14-5 | ||

| 1554АП3ТБМ | 54AC240 | Два четырехканальных формирователя с тремя состояниями и инверсией на выходе | ВП, ОСМ | 4153. | ||

| 1554АП4ТБМ | 54AC241 | Два четырехканальных формирователя с тремя состояниями на выходе | ВП, ОСМ | 4153.20-6 | ||

| 1554АП5ТБМ | 54AC244 | Два четырехканальных формирователя с тремя состояниями на выходе | ВП, ОСМ | 4153.20-6 | ||

| 1554АП6ТБМ | 54AC245 | Восьмиканальный двунаправленный приемо-передатчик с тремя состояниями на выходе | ВП, ОСМ | 4153. | ||

| 1554ИД4ТБМ | 54AC155 | Сдвоенный дешифратор-демультиплексор 2-4 | ВП, ОСМ | 402.16-32 | ||

| 1554ИД7ТБМ | 54AC138 | Дешифратор-демультиплексор 3-8 с инверсией на выходе | ВП, ОСМ | 402.16-32 | ||

| 1554ИД14ТБМ | 54AC139 | Два дешифратора-демультиплексора 2-4 с инверсией на выходе | ВП, ОСМ | 402. | ||

| 1554ИЕ6ТБМ | 54AC192 | Четырехразрядный двоично-десятичный реверсивный счетчик | ВП, ОСМ | 402.16-32 | ||

| 1554ИЕ7ТБМ | 54AC193 | Четырехразрядный двоичный реверсивный счетчик | ВП, ОСМ | 402.16-32 | ||

| 1554ИЕ10ТБМ | 54AC161 | Четырехразрядный двоичный счетчик с асинхронной установкой в состояние ‘Логический 0’ | ВП, ОСМ | 402. | ||

| 1554ИЕ18ТБМ | 54AC163 | Четырехразрядный двоичный счетчик с синхронной установкой в состояние ‘Логический 0’ | ВП, ОСМ | 402.16-32 | ||

| 1554ИЕ19ТБМ | 54AC393 | Два четырехразрядных двоичных счетчика с индивидуальной синхронизацией и сбросом | ВП, ОСМ | 401.14-5 | ||

| 1554ИН1УБМ | VHC16245 | Два 8-канальных приемопередатчика с тремя состояниями на выходе | ВП | Н16. | ||

| 1554ИП5ТБМ | 54AC280 | Девятиразрядная схема контроля четности | ВП, ОСМ | 401.14-5 | ||

| 1554ИР22ТБМ | 54AC373 | Восьмиразрядный регистр, управляемый по уровню, с параллельным вводом-выводом данных, с тремя состояниями на выходе | ВП, ОСМ | 4153.20-6 | ||

| 1554ИР23ТБМ | 54AC374 | Восьмиразрядный регистр, управляемый по фронту, с параллельным вводом-выводом данных, с тремя состояниями на выходе | ВП, ОСМ | 4153. | ||

| 1554ИР24ТБМ | 54AC299 | Восьмиразрядный двунаправленный сдвиговый регистр с параллельным вводом-выводом, последовательным вводом информации, асинхронным сбросом и тремя состояниями на выходе | ВП, ОСМ | 4153.20-6 | ||

| 1554ИР35ТБМ | 54AC273 | Восьмиразрядный регистр, управляемый по фронту, с параллельным вводом-выводом данных, с входом установки | ВП, ОСМ | 4153.20-6 | ||

| 1554ИР37ТБМ | 54AC574 | Восьмиразрядный регистр, управляемый по фронту, с параллельным вводом-выводом данных, с тремя состояниями на выходе | ВП, ОСМ | 4153. | ||

| 1554ИР40ТБМ | 54AC533 | Восьмиразрядный регистр, управляемый по уровню, с параллельным вводом-выводом данных, с тремя состояниями и инверсией на выходе | ВП, ОСМ | 4153.20-6 | ||

| 1554ИР41ТБМ | 54AC534 | Восьмиразрядный регистр, управляемый по фронту, с параллельным вводом-выводом данных, с тремя состояниями и инверсией на выходе | ВП, ОСМ | 4153.20-6 | ||

| 1554КП2ТБМ | 54AC153 | Два селектора-мультиплексора 4-1 | ВП, ОСМ | 402. | ||

| 1554КП7ТБМ | 54AC151 | Селектор-мультиплексор 8-1 со стробированием | ВП, ОСМ | 402.16-32 | ||

| 1554КП11ТБМ | 54AC257 | Четыре селектора-мультиплексора 2-1 с тремя состояниями на выходе | ВП, ОСМ | 402.16-32 | ||

| 1554АП3Н4БМ | 54AC240 | Два 4-канальных формирователя с тремя состояниями и инверсией на выходе | ВП | Кристалл | ||

| 154АП4Н4БМ | 54AC241 | Два 4-канальных формирователя с тремя состояниями на выход | ВП | Кристалл | ||

| 1554АП5Н4БМ | 54AC244 | Два 4-канальных формирователя с тремя состояниями на выходе | ВП | Кристалл | ||

| 1554АП6Н4БМ | 54AC245 | 8-канальный двунаправленный приёмо-передатчик с тремя состояниями на выходе | ВП | Кристалл | ||

| 1554ИД4Н4БМ | 54AC155 | Сдвоенный дешифратор-демультиплексор 2-4 | ВП | Кристалл | ||

| 1554ИД7Н4БМ | 54AC138 | Дешифратор-демультиплексор 3-8 с инверсией на выходе | ВП | Кристалл | ||

| 1554ИД14Н4БМ | 54AC139 | Два дешифратора-демультиплексора 2-4 с инверсией на выходе | ВП | Кристалл | ||

| 1554ИЕ6Н4БМ | 54AC192 | 4-разрядный двоично-десятичный реверсивный счетчик | ВП | Кристалл | ||

| 1554ИЕ7Н4БМ | 54AC193 | 4-разрядный двоичный реверсивный счетчик | ВП | Кристалл | ||

| 1554ИЕ10Н4БМ | 54AC161 | 4-разрядный двоичный счетчик с асинхронной установкой в состояние “логический 0” | ВП | Кристалл | ||

| 1554ИЕ18Н4БМ | 54AC163 | 4-разрядный двоичный счетчик с синхронной установкой в состояние “логический 0” | ВП | Кристалл | ||

| 1554ИЕ19Н4БМ | 54AC393 | Два 4-разрядных двоичных счетчика с индивидуальной синхронизацией и сбросом | ВП | Кристалл | ||

| 1554ИН1Н4БМ | VHC16245 | Два 8-канальных приемопередатчика с тремя состояниями на выходе | ВП | Кристалл | ||

| 1554ИП5Н4БМ | 54AC280 | 9-разрядная схема контроля четности | ВП | Кристалл | ||

| 1554ИР22Н4БМ | 54AC373 | 8-разрядный регистр, управляемый по уровню, с параллельным вводом-выводом данных, с тремя состояниями на выходе | ВП | Кристалл | ||

| 1554ИР23Н4БМ | 54AC374 | 8-разрядный регистр, управляемый по фронту, с параллельным вводом-выводом данных, с тремя состояниями на выходе | ВП | Кристалл | ||

| 1554ИР24Н4БМ | 54AC299 | 8-разрядный двунаправленный сдвиговый регистр с параллельным вводом-выводом, последовательным вводом информации, асинхронным сбросом и тремя состояниями на выходе | ВП | Кристалл | ||

| 1554ИР35Н4БМ | 54AC273 | 8-разрядный регистр, управляемый по фронту, с параллельным вводом-выводом данных, с входом установки | ВП | Кристалл | ||

| 1554ИР37Н4БМ | 54AC574 | 8-разрядный регистр, управляемый по фронту, с параллельным вводом-выводом данных, с тремя состояниями на выходе | ВП | Кристалл | ||

| 1554ИР40Н4БМ | 54AC533 | 8-разрядный регистр, управляемый по уровню, с параллельным вводом-выводом данных, с тремя состояниями и инверсией на выходе | ВП | Кристалл | ||

| 1554ИР41Н4БМ | 54AC534 | 8-разрядный регистр, управляемый по фронту, с параллельным вводом-выводом данных, с тремя состояниями и инверсией на выходе | ВП | Кристалл | ||

| 1554КП2Н4БМ | 54AC153 | Два селектора-мультиплексора 4-1 | ВП | Кристалл | ||

| 1554КП7Н4БМ | 54AC151 | Селектор-мультиплексор 8-1 со стробированием | ВП | Кристалл | ||

| 1554КП11Н4БМ | 54AC257 | Четыре селектора-мультиплексора 2-1 с тремя состояниями на выходе | ВП | Кристалл | ||

| 1554КП12Н4БМ | 54AC253 | Два селектора-мультиплексора 4-1 с тремя состояниями на выходе | ВП | Кристалл | ||

| 1554КП14Н4БМ | 54AC258 | Четыре селектора-мультиплексора 2-1 с тремя состояниями и инверсией на выходе | ВП | Кристалл | ||

| 1554КП15Н4БМ | 54AC251 | Селектор-мультиплексор 8-1 с тремя состояниями на выходе | ВП | Кристалл | ||

| 1554КП16Н4БМ | 54AC157 | Четыре селектора-мультиплексора 2-1 | ВП | Кристалл | ||

| 1554КП18Н4БМ | 54AC158 | Четыре селектора-мультиплексора 2-1 с инверсией на выходе | ВП | Кристалл | ||

| 1554ЛА1Н4БМ | 54AC20 | Два логических элемента “4И-НЕ” | ВП | Кристалл | ||

| 1554ЛА2Н4БМ | 54AC30 | Логический элемент “8И-НЕ” | ВП | Кристалл | ||

| 1554ЛА3Н4БМ | 54AC00 | Четыре логических элемента “2И-НЕ” | ВП | Кристалл | ||

| 1554ЛА4Н4БМ | 54AC10 | Три логических элемента “3И-НЕ” | ВП | Кристалл | ||

| 1554ЛЕ1Н4БМ | 54AC02 | Четыре логических элемента “2ИЛИ-НЕ” | ВП | Кристалл | ||

| 1554ЛИ1Н4БМ | 54AC08 | Четыре логических элемента “2И” | ВП | Кристалл | ||

| 1554ЛИ3Н4БМ | 54AC11 | Три логических элемента “3И” | ВП | Кристалл | ||

| 1554ЛИ6Н4БМ | 54AC21 | Два логических элемента “4И” | ВП | Кристалл | ||

| 1554ЛИ9Н4БМ | 54AC34 | Шесть логических повторителей | ВП | Кристалл | ||

| 1554ЛЛ1Н4БМ | 54AC32 | Четыре логических элемента “2ИЛИ” | ВП | Кристалл | ||

| 1554ЛН1Н4БМ | 54AC04 | Шесть логических элементов “НЕ” | ВП | Кристалл | ||

| 1554ЛН2Н4БМ | TC7S04 | Единичный инвертор | ВП | Кристалл | ||

| 1554ЛП5Н4БМ | 54AC86 | Четыре двухвходовых логических элемента “Исключающее ИЛИ” | ВП | Кристалл | ||

| 1554ЛП8Н4БМ | 54AC125 | Четыре буферных элемента с тремя состояниями на выходе | ВП | Кристалл | ||

| 1554ЛР11Н4БМ | 54AC51 | Логические элементы “2-2И-2ИЛИ-НЕ” и “3-3И-2ИЛИ-НЕ” | ВП | Кристалл | ||

| 1554ЛР13Н4БМ | 54AC54 | Логический элемент “3-2-2-3И-4ИЛИ-НЕ” | ВП | Кристалл | ||

| 1554СП1Н4БМ | 54AC85 | Схема сравнения двух четырехразрядных чисел | ВП | Кристалл | ||

| 1554ТВ9Н4БМ | 54AC112 | Два J-K триггера с управлением отрицательным фронтом по тактовому входу | ВП | Кристалл | ||

| 1554ТВ15Н4БМ | 54AC109 | Два J-K с управлением положительным фронтом по такто-вому входу | ВП | Кристалл | ||

| 1554ТЛ2Н4БМ | 54AC14 | Шесть инверторов Шмитта | ВП | Кристалл | ||

| 1554ТМ2Н4БМ | 54AC74 | Два D-триггера с установкой и сбросом | ВП | Кристалл | ||

| 1554ТМ8Н4БМ | 54AC175 | Четыре D-триггера с общими входами управления и сброса | ВП | Кристалл | ||

| 1554ТМ9Н4БМ | 54AC174 | Шесть D-триггеров | ВП | Кристалл | ||

| 1554ТР2Н4БМ | 54AC279 | Четыре R-S триггера | ВП | Кристалл | ||

| 1594ЛИ1Н4 | 54ACT08 | Четыре логических элемента “2И” | ВП | Кристалл | ||

| Серия 1554У* | Комплект микросхем в мало-габаритных металлокерамических CLCC корпусах | CLCC корпуса 5119. 5121.20-А |

Элементы транзисторных логик: схемы, ТТЛ, ТТЛШ, КМОП

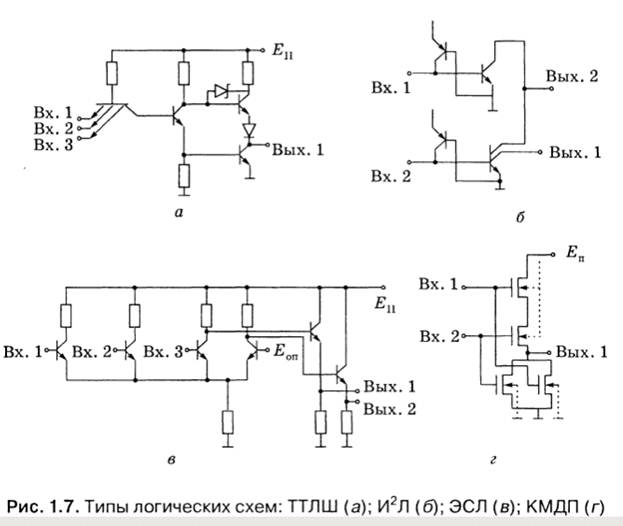

Для конкретной серии микросхем характерно использование типового электронного узла — базового логического элемента. Этот элемент является основой построения самых разнообразных цифровых электронных устройств.

Ниже рассмотрим особенности базовых логических элементов различных логик.

Элементы транзисторно-транзисторной логики

Характерной особенностью ТТЛ является использование многоэмиттерных транзисторов. Эти транзисторы сконструированы таким образом, что отдельные эмиттеры не оказывают влияния друг на друга. Каждому эмиттеру соответствует свой p-n-переход. В первом приближении многоэмиттерный транзисторможет моделироваться схемой на диодах (см. пунктир на рис. 3.27).

Васильев Дмитрий Петрович

Профессор электротехники СПбГПУ

Задать вопрос

Упрощенная схема ТТЛ-элемента приведена на рис. 3.27. При мысленной замене многоэмиттерного транзистора диодами получаем элемент диодно-транзисторной логики «И-НЕ». Из анализа схемы можно сделать вывод, что если на один из входов или на оба входа подать низкий уровень напряжения, то ток базы транзистора Т2 будет равен нулю, и на коллекторе транзистора Т2 будет высокий уровень напряжения.

3.27. При мысленной замене многоэмиттерного транзистора диодами получаем элемент диодно-транзисторной логики «И-НЕ». Из анализа схемы можно сделать вывод, что если на один из входов или на оба входа подать низкий уровень напряжения, то ток базы транзистора Т2 будет равен нулю, и на коллекторе транзистора Т2 будет высокий уровень напряжения.

Если на оба входа подать высокий уровень напряжения, то через базу Т2 транзистора будет протекать большой базовый ток и на коллекторе транзистора Т2 будет низкий уровень напряжения, т. е. данный элемент реализует функцию И-НЕ:

uвых= u1· u2. Базовый элемент ТТЛ содержит многоэмиттерный транзистор, выполняющий логическую операцию И, и сложный инвертор (рис. 3.28).

Если на один или оба входа одновременно подан низкий уровень напряжения, то многоэмиттерный транзистор находится в состоянии насыщения и транзистор Т2 закрыт, а следовательно, закрыт и транзистор Т4, т. е. на выходе будет высокий уровень напряжения.

е. на выходе будет высокий уровень напряжения.

Васильев Дмитрий Петрович

Профессор электротехники СПбГПУ

Задать вопрос

Если на обоих входах одновременно действует высокий уровень напряжения, то транзистор Т2 открывается и входит в режим насыщения, что приводит к открытию и насыщению транзистора Т4 и запиранию транзистора Т3, т. е. реализуется функция И-НЕ.

Для увеличения быстродействия элементов ТТЛ используются транзисторы с диодами Шоттки (транзисторы Шоттки).

Логические элементы ТТЛШ (на примере серии К555)

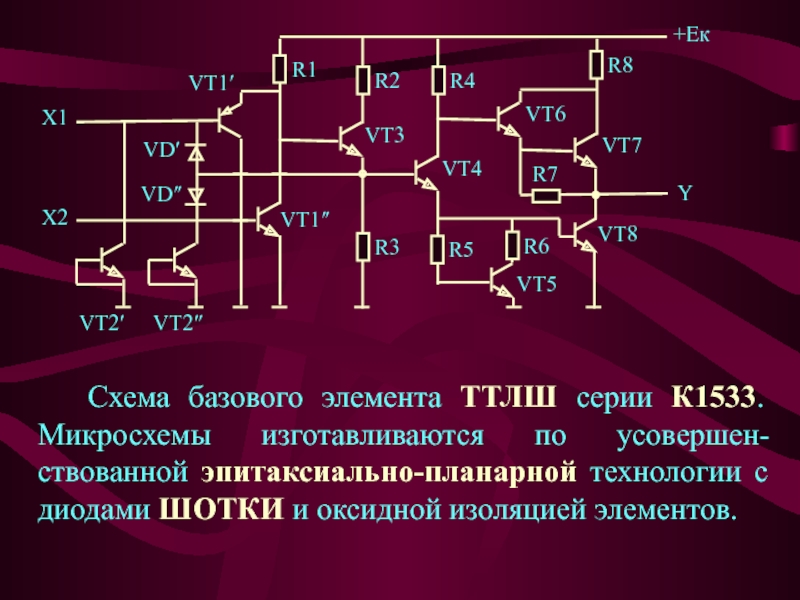

В качестве базового элемента серии микросхем К555 использован элемент И-НЕ. На рис. 3.29, а изображена схема этого элемента, а условное графическое обозначение транзистора Шоттки приведено на рис. 3.29, б.

Такой транзистор эквивалентен рассмотренной выше паре из обычного транзистора и диода Шоттки. ТранзисторVT4 — обычный биполярный транзистор.

Если оба входных напряжения uвх1и uвх2 имеют высокий уровень, то диодыVD3 и VD4 закрыты, транзисторы VT1,VT5 открыты и на выходе имеет место напряжение низкого уровня. Если хотя бы на одном входе имеется напряжение низкого уровня, то транзисторы VT1 и VT5 закрыты, а транзисторы VT3 и VT4 открыты, и на входе имеет место напряжение низкого уровня. Полезно отметить, что транзисторы VT3 и VT4 образуют так называемый составной транзистор (схему Дарлингтона).

Если хотя бы на одном входе имеется напряжение низкого уровня, то транзисторы VT1 и VT5 закрыты, а транзисторы VT3 и VT4 открыты, и на входе имеет место напряжение низкого уровня. Полезно отметить, что транзисторы VT3 и VT4 образуют так называемый составной транзистор (схему Дарлингтона).

Микросхемы ТТЛШ

Микросхемы ТТЛШ серии К555 характеризуются следующими параметрами:

- напряжение питания +5 В;

- выходное напряжение низкого уровня — не более 0,4 В;

- выходное напряжение высокого уровня — не менее 2,5 В;

- помехоустойчивость — не менее 0,3 В;

- среднее время задержки распространения сигнала — 20 нс;

- максимальная рабочая частота — 25 МГц.

Васильев Дмитрий Петрович

Профессор электротехники СПбГПУ

Задать вопрос

Микросхемы ТТЛШ обычно совместимы по логическим уровням, помехоустойчивости и напряжению питания с микросхемами ТТЛ. Время задержки распространения сигнала элементов ТТЛШ в среднем в два раза меньше по сравнению с аналогичными элементами ТТЛ.

Время задержки распространения сигнала элементов ТТЛШ в среднем в два раза меньше по сравнению с аналогичными элементами ТТЛ.

Особенности других логик

Основой базового логического элемента ЭСЛ является токовый ключ. Схема токового ключа (рис. 3.30) подобна схеме дифференциального усилителя.

Необходимо обратить внимание на то, что микросхемы ЭСЛ питаются отрицательным напряжением (к примеру, −4,5 В для серии К1500). На базу транзистора VT2 подано отрицательное постоянное опорное напряжение Uоп. Изменение входного напряжения uвх1 приводит к перераспределению постоянного тока iэ0, заданного сопротивлением Rэ между транзисторами, что имеет следствием изменение напряжений на их коллекторах.

Транзисторы не входят в режим насыщения, и это является одной из причин высокого быстродействия элементов ЭСЛ.

Микросхемы серий 100, 500 имеют следующие параметры:

- напряжение питания −5,2 В;

- потребляемая мощность — 100 мВт;

- коэффициент разветвления по выходу — 15;

- задержка распространения сигнала — 2,9 нс.

В микросхемах n-МОП и p-МОП используются ключи соответственно на МОП-транзисторах с n-каналом и динамической нагрузкой (рассмотрены выше) и на МОП-транзисторах с p-каналом.

В качестве примера рассмотрим элемент логики n-МОП, реализующий функцию ИЛИ-НЕ (рис. 3.31).

Он состоит из нагрузочного транзистора Т3 и двух управляющих транзисторов Т1 и Т2. Если оба транзистора Т1 и Т2 закрыты, то на выходе устанавливается высокий уровень напряжения. Если одно или оба напряжения u1и u2 имеют высокий уровень, то открывается один или оба транзистора Т1 и Т2 и на выходе устанавливается низкий уровень напряжения, т. е. реализуется функция uвых= u1 + u2.

Для исключения потребления мощности логическим элементом в статическом состоянии используются комплементарные МДП — логические элементы (КМДП или КМОП-логика). В микросхемах КМОП используются комплементарные ключи на МОП-транзисторах. Они отличаются высокой помехоустойчивостью. Логика КМОП является очень перспективной. Рассмотренный ранее комплементарный ключ фактически является элементом НЕ (инвертором).

Они отличаются высокой помехоустойчивостью. Логика КМОП является очень перспективной. Рассмотренный ранее комплементарный ключ фактически является элементом НЕ (инвертором).

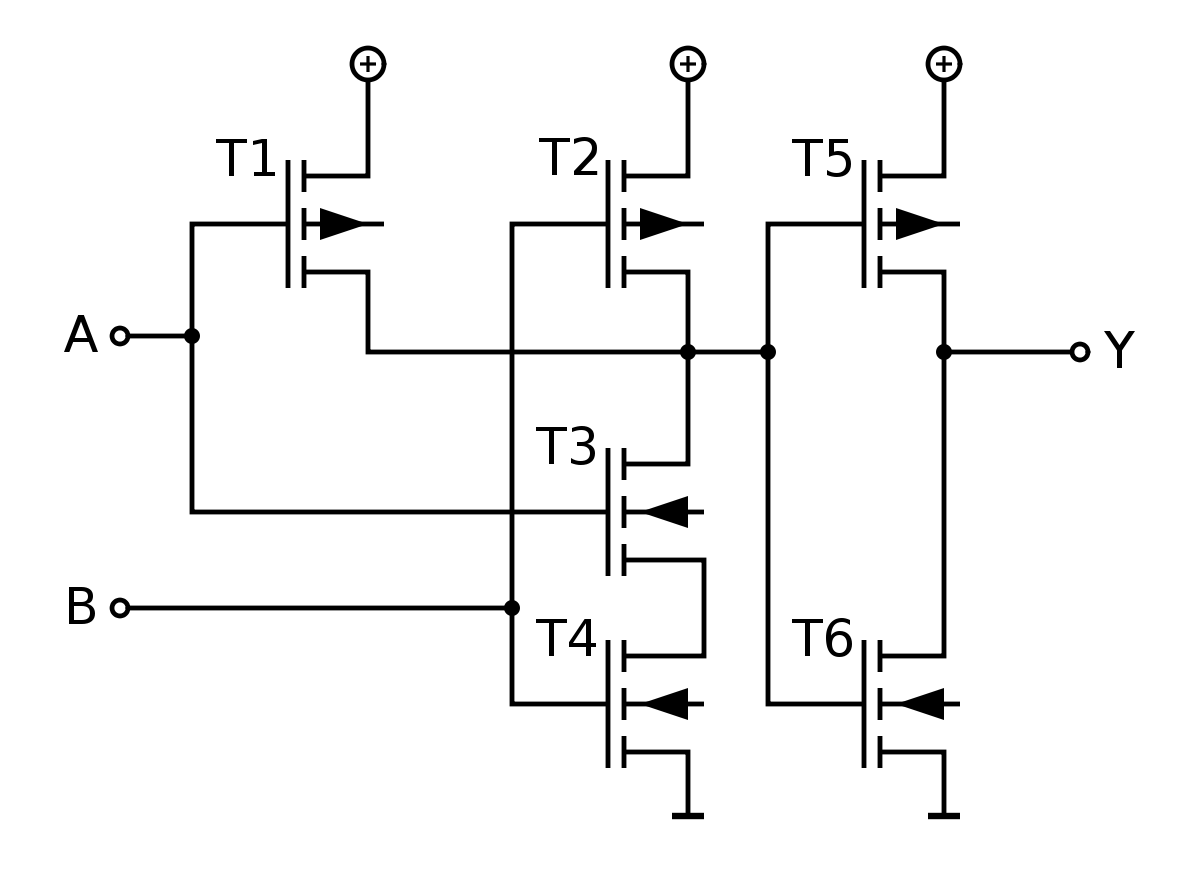

КМОП — логический элемент

Рассмотрим КМОП — логический элемент, реализующий функцию ИЛИ-НЕ (рис. 3.32).

Абрамян Евгений Павлович

Доцент кафедры электротехники СПбГПУ

Задать вопрос

Если входные напряжения имеют низкие уровни (u1и u2меньше порогового напряжения n-МОП-транзистора Uзи.порог.n), то транзисторы Т1 и Т2 закрыты, транзисторы Т3 и Т4 открыты и выходное напряжение имеет высокий уровень.

Если одно или оба входных напряжения u1и u2 имеют высокий уровень, превышающий Uзи.порог.n, то открывается один или оба транзистора Т1 и Т2, а между истоком и затвором одного или обоих транзисторов Т3 и Т4 устанавливается низкое напряжение, что приводит к запиранию одного или обоих транзисторов Т3 и Т4, а следовательно, на выходе устанавливается низкое напряжение.

Таким образом, этот элемент реализует функцию uвых= u1+u2 и потребляет мощность от источника питания лишь в короткие промежутки времени, когда происходит его переключение.