СВЧ делители частоты. Схемы. Описание. – Цифровая техника – СХЕМЫ – Статьи

Большинство частотомеров, собранных на микросхемах дискретной логики или микроконтроллерах, не позволяют измерять частоты выше 40…50 мГц. Для измерения частот выше этого значения необходимо использовать предварительный СВЧ делитель. Существует большое количество микросхем, на которых можно собрать такой предварительный делитель частоты, но, к сожалению, в магазинах их выбор довольно ограничен.

Это объясняется тем, что в новых серийных разработках частотомеров и другой измерительной техники используются микросхемы все большей и большей степени интеграции – однокристальные синтезаторы, частотомеры и др. Отдельно микросхемы делителей частоты используются относительно редко, поэтому их стоимость высока и они довольно дефицитны. Но, к счастью для радиолюбителей, выбор пока еще есть.Предлагается несколько вариантов схем делителей для СВЧ измерений. Определяющий критерий при выборе элементной базы – простота схемы и доступность комплектующих.

Конструктивно СВЧ делители частоты выполняются в виде выносного пробника, в качестве корпуса хорошо подходят металлические корпуса от внешних делителей напряжения, которые широко использовались в старых отечественных осциллографах.

Конструктивно СВЧ делители частоты выполняются в виде выносного пробника, в качестве корпуса хорошо подходят металлические корпуса от внешних делителей напряжения, которые широко использовались в старых отечественных осциллографах. Все схемы делителей частоты можно использовать совместно с частотомерами, описания которых есть на этом сайте. Сигнал с выхода делителя подается по кабелю длиной до 1 м на входной формирователь частотомера. Коэффициент деления учитывается в программе частотомера, поэтому на индикатор будет выводиться истинная частота измеряемого сигнала.

На этой страничке описано, как сделать СВЧ делитель частоты на микросхемах К193ИЕ2, К193ИЕ3, LB3500, SAB6456, TD6359, TD6380, TD6381, TD6382, TD7614.

Серия 193 была освоена отечественной промышленностью в девяностые годы прошлого века на основе разработок фирмы “Plessey Semiconductors”. Для предварительных делителей частоты можно использовать К193ИЕ2 и К193ИЕ3. Но эти отечественные микросхемы не полные аналоги импортных.

Отличия в данном случае в расположении выводов и особенностях подачи напряжения питания.

Отличия в данном случае в расположении выводов и особенностях подачи напряжения питания. Микросхема К193ИЕ2 является аналогом SP8685A, имеет диапазон рабочих частот от 40 до 500 мГц, коэффициент деления 10. Двойная амплитуда выходного напряжения около 0,8 В, чувствительность 100…200 мВ. Потребляемый ток около 50 мА. Схема делителя показана на рисунке.

К193ЕИ3 функциональный аналог SP8690. Схема ее включения имеет незначительные отличия от К193ИЕ2. Диапазон рабочих частот этого делителя несколько уже – от 30 до 200 мГц, но у него есть выход с TTL уровнями, сигнал с которого можно непосредственно, без входного формирователя, подать на логику частотомера. И потребляемый ток меньше – около 20 мА. Коэффициент деления равен10, чувствительность 100…200 мВ.

Хороший выбор для ВЧ делителя – микросхема LB3500 фирмы “Sanyo”. Согласно datasheet, диапазон рабочих частот 30…150 мГц, но имеющийся у меня экземпляр устойчиво работает до 350 мГц. Коэффициент деления 8, чувствительность 100 мВ, двойная амплитуда выходного сигнала 0,9 В.

Потребляемый ток около 20 мА. Простое и дешевое решение!

Потребляемый ток около 20 мА. Простое и дешевое решение! Особо следует отметить SAB6456 фирмы “Philips Semiconductors”. Это делитель с диапазоном рабочих частот от 70 до 1000 мГц. Потребляемый ток около 20 мА, а заявленная чувствительность 10мВ! Двойная амплитуда выходного сигнала 1 В. Коэффициент деления равен 64 или 256.

Как уже упоминалось, микросхемы делителей частоты малой степени интеграции постепенно снимаются с производства. Иногда проще и дешевле приобрести микросхему синтезатора частоты, чем микросхему делителя. К счастью для радиолюбителей, в некоторых типах синтезаторов разработчики предусмотрели тестовый режим, при котором на один из выводов микросхемы подается входной сигнал после делителя с фиксированным коэффициентом деления. Тестовый режим включается определенной комбинацией уровней напряжения на управляющих входах синтезатора.

Один из таких синтезаторов TD6359 фирмы “Toshiba”. Микросхема выпускается в корпусе DIP20. Схема делителя с ее использованием в тестовом режиме показана рисунке.

Диапазон рабочих частот 80…1000 мГц. Коэффициент деления 256, выход с открытым коллектором. Чувствительность около 100…200 мВ, но потребляемый ток довольно значительный – 60…80 мА.

Диапазон рабочих частот 80…1000 мГц. Коэффициент деления 256, выход с открытым коллектором. Чувствительность около 100…200 мВ, но потребляемый ток довольно значительный – 60…80 мА. Аналогичную схему включения и параметры имеют синтезаторы TD6380, TD6381 и TD6382, которые также можно использовать в схеме СВЧ делителей. Цоколевка для DIP корпусов TD6380P и TD6380N совпадает с TD6359.

Еще один синтезатор, который может работать в тестовом режиме как СВЧ делитель – это TD7614F “Toshiba”. Он выпускается в корпусе SOP20. Частотный диапазон 80…1300 мГц, чувствительность 100…200 мВ, потребляемый ток до 75 мА, двойная амплитуда выходного сигнала около 0,8 В. Коэффициент деления 128.

СВЧ делители частоты. Схемы. Описание.

Каталог радиолюбительских схем. ВЧ-делитель ДЛЯ ИЗМЕРЕНИЯ ЧАСТОТ

Каталог радиолюбительских схем. ВЧ-делитель ДЛЯ ИЗМЕРЕНИЯ ЧАСТОТВЧ-делитель ДЛЯ ИЗМЕРЕНИЯ ЧАСТОТ

В.ФЕДОРОВ,

г.Липецк.

В статье [1] описан делитель частоты, предназначенный для расширения измеряемого частотомером диапазона частот до 2,3 ГГц (коэффициент деления его равен 160, а не 16, как ошибочно указано в статье). На рис.1 изображена принципиальная схема делителя на 1000 для частотомера, позволяющего гарантированно регистрировать частоты до 5 ГГц.

Рис. 1.

Измеряемый сигнал через диоды VD1, VD2 (защищающие вход VT1 от перегрузки по напряжению) и ФВЧ L1-C2 с частотой среза около 50…60 МГц поступает на входной СВЧ-усилитель с коэффициентом усиления по мощности на частоте 5 ГГц — около 12 дБ, собранный на транзисторе VT1.

Усиленный сигнал подается на десятичный счетчик DD1 SP8910 фирмы “Mitel Semiconductor”. Счетчик представляет собой делитель на 10, работающий на любых частотах от нуля (постоянный уровень) до 5 ГГц (амплитуда сигнала на входе — около 200 мВ). В принципе, при увеличении уровня входного сигнала увеличивается также и максимальная регистрируемая частота (авторский экземпляр делителя успешно регистрировал частоту автогенератора, собранного на ЗП606В, при выходной мощности последнего 1,5 Вт и частоте 8 ГГц. Частота сравнивалась с результатом, полученным с эталонного частотомера).

Второй делитель на 10 собран на аналогичной микросхеме, а в качестве третьего делителя (также на 10) использована отечественная ТТЛШ-микросхема К531ИЕ2 (желательно выбрать экземпляр с fвx.max=80…100 МГц). Каскад на VT2 согласует выходное и я входное сопротивления делителей DD2, DD3 соответственно.

На выходе делителя установлены четыре элемента 2И (КР1533ЛИ1), которые распределяют сигнал между четырьмя контрольными выходами, один из которых (выход 4) соединяется со входом частотомера. При подаче на вывод 13 DD4 низкого ТТЛ-уровня запрещается прохождение сигнала на вход частотомера. Делитель питается от источника питания частотомера (+5 В).

Конструктивно делитель выполнен на двустороннем фольгированном фторопласте (ФАФ-4) толщиной 1 мм. Топология входных цепей изображена на рис.2.

Рис. 2.

От точности изготовления платы зависит работоспособность делителя в целом. Входные элементы — SMD-типа (в том числе DD1, DD2). Использование элементов с длинными выводами недопустимо. Делитель помещен в дюралюминиевый корпус. Катушка L1 — бескаркасная, имеет 8 витков провода ПЭВ-2 00,5 мм, намотана на оправке Ф0,5 мм. Разъем XW1 — СВЧ, типа SMA, XW2…XW4 — СЗ-50. Вместо DD2 допустимо применение другого делителя (fв>900 МГц) с коэффициентом деления, отличным от 10 (например, К193ИЕ8), с соответствующей переделкой печатной платы. Однако следует помнить, что такая доработка допустима лишь при использовании делителя с частотомером на основе микро-ЭВМ (для коррекции результата путем умножения на соответствующий коэффициент). В качестве С16…С18 используют КМ-6. Вместо VT1 можно применить ЗП324А (с соответствующим подбором R4), VT2 можно заменить на КТ306А или КТ316А.

Делитель помещен в дюралюминиевый корпус. Катушка L1 — бескаркасная, имеет 8 витков провода ПЭВ-2 00,5 мм, намотана на оправке Ф0,5 мм. Разъем XW1 — СВЧ, типа SMA, XW2…XW4 — СЗ-50. Вместо DD2 допустимо применение другого делителя (fв>900 МГц) с коэффициентом деления, отличным от 10 (например, К193ИЕ8), с соответствующей переделкой печатной платы. Однако следует помнить, что такая доработка допустима лишь при использовании делителя с частотомером на основе микро-ЭВМ (для коррекции результата путем умножения на соответствующий коэффициент). В качестве С16…С18 используют КМ-6. Вместо VT1 можно применить ЗП324А (с соответствующим подбором R4), VT2 можно заменить на КТ306А или КТ316А.

Налаживание делителя производится следующим образом. Отсоединяют С16 от DD2 и на него подают прямоугольные импульсы амплитудой 2,5 В и частотой 50…100 МГц. На одном из выходов DD4 частотомером фиксируют поделенную частоту (5… 10 МГц). Если таковая отсутствует, убеждаются в работоспособности VT2, DD3, DD4. Подбирают экземпляр DD3 (вместо этой микросхемы можно установить панельку), устойчиво работающий на частотах до 80… 100 МГц. Далее восстанавливают соединение с С16, аС12 отсоединяют от DD1 и подают на него синусоидальный сигнал амплитудой 2,5 В и частотой 700 МГц. На выходе делителя будут присутствовать импульсы частотой 7 МГц. Восстанавливают соединение с С12. Отсоединяют С7 от стока VT1 и подают на него синусоиду амплитудой 2,5 В и частотой 2 ГГц. На выходе делителя регистрируют колебания 2 МГц. Восстанавливают соединение с С7 и подают на вход XW1 сигнал амплитудой 50 мВ (2 ГГц). Частотомер должен устойчиво регистрировать эту частоту. Повышая входную частоту до 5 ГГц, убеждаются в надежности регистрации колебаний в широких пределах входных амплитуд. При работе пробником на частотах выше 2 ГГц необходимо учитывать согласование его входного сопротивления с сопротивлением измеряемых цепей.

Подбирают экземпляр DD3 (вместо этой микросхемы можно установить панельку), устойчиво работающий на частотах до 80… 100 МГц. Далее восстанавливают соединение с С16, аС12 отсоединяют от DD1 и подают на него синусоидальный сигнал амплитудой 2,5 В и частотой 700 МГц. На выходе делителя будут присутствовать импульсы частотой 7 МГц. Восстанавливают соединение с С12. Отсоединяют С7 от стока VT1 и подают на него синусоиду амплитудой 2,5 В и частотой 2 ГГц. На выходе делителя регистрируют колебания 2 МГц. Восстанавливают соединение с С7 и подают на вход XW1 сигнал амплитудой 50 мВ (2 ГГц). Частотомер должен устойчиво регистрировать эту частоту. Повышая входную частоту до 5 ГГц, убеждаются в надежности регистрации колебаний в широких пределах входных амплитуд. При работе пробником на частотах выше 2 ГГц необходимо учитывать согласование его входного сопротивления с сопротивлением измеряемых цепей.

Литература

1. Федоров В. СВЧ-делитель для частотомера. — Радиолюбитель, 2000, №3, с. 33.

33.

Радиолюбитель №4, 2001 г., с. 33.

мир электроники – Делитель частоты с меандром на выходе

категория

Электронные устройства

материалы в категории

А. ШИТОВ, г. Иваново

Журнал Радио 1998 год, номер 2

Все сказанное в [1] относительно деления частоты на три при сохранении “меандра” на выходе остается справедливым и при любом другом нечетном коэффициенте деления. Вместе с тем при малом численном значении этого коэффициента возможно значительное упрощение делителя частоты.

Описанные здесь делители частоты на три и на пять по быстродействию близки к используемым микросхемам. Делители работоспособны при любом начальном состоянии триггеров, поэтому далее для определенности предположим, что при включении питания триггеры окажутся в нулевом состоянии.

Схема делителя частоты на три, построенного на двух D-триггерах, показана на рис. 1, а поясняющие его работу диаграммы сигналов – на рис. 2.

2.

Фронт первого входного импульса переведет в состояние 1 триггер DD1.1. С приходом второго импульса в состояние 1 переключится и триггер DDI.2.

После спада второго импульса на обоих входах элемента DD2.1 будет низкий уровень, поэтому низкий уровень с выхода элемента вернет триггер DD1.1 в состояние 0. Фронт третьего входного импульса вернет в состояние 0 триггер DDI .2. Состояние триггера DD1.1 не изменится, поскольку во время плюсового перепада входного сигнала триггер остается заблокированным низким уровнем с выхода элемента DD2.1.

К приходу четвертого входного импульса делитель окажется в исходном состоянии.

Вместо элемента ИЛИ DD2.1 допустимо применить более распространенные И-НЕ. Схема такого варианта построения делителя изображена на рис. 3. Устройство практически не отличается от исходного (диаграммы сигналов соответствуют рис. 2). Для запрещения работы обоих делителей достаточно подать низкий уровень на вход S любого из триггеров.

Подобное соединение триггеров с обратной связью применимо для построения делителя частоты и с другими нечетными коэффициентами деления (2).

Первые три входных импульса поочередно переведут триггеры устройства в состояние 1. После спада третьего импульса низкий уровень с выхода элемента DD4.1 вернет в состояние 0 триггер DD1.1. С приходом четвертого импульса на выходе элемента DD2.1 будет низкий уровень и триггер DD1.2 перейдет в состояние 0. Такое же состояние примет и триггер DD3.1 под действием пятого счетного импульса. Далее цикл работы повторяется.

Все описанные устройства сохраняют скважность входных импульсов, если она равна 2. В ином случае скважность Qвых выходных импульсов будет равна:

Qвых=3Qвх(1+Qвx) и 50вх/(1+2СМ для делителей на три и пять соответственно (Qвx – скважность входного сигнала).

Такой схемотехнический подход применим для создания делителей и с большим коэффициентом деления. Но вряд ли это можно считать целесообразным из-за быстро растущего числа требуемых микросхем. Делитель частоты на семь и более следует строить по рекомендациям, данным в [1].

ЛИТЕРАТУРА

1. Шитов А. Делитель частоты на три с “меандром” на выходе. – Радио, 1996. №7. с. 51.52.

2. Горошков Б. И. Элементы радиоэлектронных устройств. – М.: Радио и связь, 1989, с. 136.

А. САМОЙЛЕНКО, г. Клин Московской обл.

В своей статье “Делитель частоты на три с “меандром” на выходе” (“Радио”, 1996, ╧ 7, с. 51, 52) А. Шитов описал два варианта делителя на три, сохраняющих “меандр” на выходе. Заметим, что в первом из них применены элементы трех микросхем (корпусов), во втором – четырех. Такая “расточительность” не всегда оправданна.

Предлагаю вариант такого же делителя (его структурная схема показана на рис. 7 в статье А. Иванова “Применение элемента ИСКЛЮЧАЮЩЕЕ ИЛИ” (“Радио”, 1985, ╧ 2, с. 37), но более экономного. В нем использованы “пол-корпуса” одной микросхемы и четверть другой. Схема делителя представлена на рис. 1, а временные диаграммы его работы – на рис. 2.

До момента t1 (а с учетом задержек -до t2) на выходе 2 счетчика DD2. 1 действует сигнал низкого уровня, элемент DD1.1 повторяет входную последовательность. В момент t2 на выходе 1 счетчика появляется высокий уровень (диаграмма 4). элемент DD1.1 ИСКЛЮЧАЮЩЕЕ ИЛИ становится инвертором и с момента t2 до t6 передает входную последовательность (диаграмма 1) с инверсией, а от t6 до t10 – снова без инверсии и т. д.

1 действует сигнал низкого уровня, элемент DD1.1 повторяет входную последовательность. В момент t2 на выходе 1 счетчика появляется высокий уровень (диаграмма 4). элемент DD1.1 ИСКЛЮЧАЮЩЕЕ ИЛИ становится инвертором и с момента t2 до t6 передает входную последовательность (диаграмма 1) с инверсией, а от t6 до t10 – снова без инверсии и т. д.

Таким образом, благодаря подаче на нижний по схеме вход элемента DD1.1 сигнала с выхода 2 счетчика элемент периодически инвертирует входную последовательность (диаграмма 2) и в течение интервала времени, содержащего три периода входной частоты, например, от t1 до t9, на каждые три одноименных фронта входной последовательности (диаграмма 1, моменты t1, t4, t7) вырабатывает четыре одноименных фронта (диаграмма 2, моменты t1, t3, t5, t7), которые, воздействуя на делитель частоты на 4, обеспечивают выполнение зависимости Fвых = Fвх/3 (диаграмма 4).

В описываемом делителе с выхода элемента DD1.1 можно снять сигнал с частотой 4Fвх/3, но период этом последовательности состоит из двух неравных по длительности импульсов (паузы одинаковы; диаграмма 2). Кроме этого, с выхода 1 счетчика DD2.1 можно получить сигнал с частотой 2Fвx/3 и скважностью 3.

Кроме этого, с выхода 1 счетчика DD2.1 можно получить сигнал с частотой 2Fвx/3 и скважностью 3.

Вместо счетчика DD2.1. используемого как делитель частоты на 4, при необходимости подойдет другой делитель на 4, выполненный, например, на другом двоичном счетчике или на двух последовательно включенных триггерах К561ТМ2 в счетном режиме.

Для сдвига выходного “меандра” на полпериода входной частоты достаточно подать выходной сигнал элемента DD1.1 на вход CP счетчика DD2.1. а его вход CN соединить с общим проводом.

Делитель позволяет также реализовать коэффициенты деления 7 или 15 при сохранении скважности выходного сигнала, равной 2. Для этого достаточно переключить нижний по схеме вход элемента DD1.1 к выходу 4 или 8 счетчика соответственно. С этих выходов снимают и выходной сигнал делителя.

Проверяют работоспособность делителя с помощью осциллографа либо частотомера. Для получения устойчивого изображения на экране осциллографа лучше засинхронизировать его внешним сигналом с одного из старших разрядов счетчика DD2. 1 (с выхода 4 или 8). Форма сигналов должна быть близкой к показанной на рис. 2. Импульс диаграммы 2 между моментами t1 и t2 очень узкий, и чтобы его увидеть, можно попробовать расфокусировать луч осциллографа.

1 (с выхода 4 или 8). Форма сигналов должна быть близкой к показанной на рис. 2. Импульс диаграммы 2 между моментами t1 и t2 очень узкий, и чтобы его увидеть, можно попробовать расфокусировать луч осциллографа.

При проверке частотомером измеряют частоту в точках 1 – 4 делителя и убеждаются в соответствии измеренных значений указанным на схеме.

Счетчики и делители частоты. Схема, описание

Вообщем в рамках свапа на J мотор решили что приборка останется от аккорда. Но возникает проблема с тахометром – на 6 цилиндрах на тахометр приходит 6 импульсов (т.к. 6 цилиндров). Соответственно тахометр врет.

Для решения проблемы требуется делитель частоты. Покопавшись удалось такой реализовать на рассыпухе. Вчера был проверен на машине – все ок. Ну пока еще подождем – от хози как новости будут. Может что неправильно будет работать.

UPD: Проверено на двух разных машинах – все ок.

Многие спросят, зачем делать внешнюю приблуду – можно ведь поколупаться в приборке и поправить цепи интегратора? Но далеко не во всех приборках есть интегрирующие цепи. Чаще стоит контроллер который считает импульсы за единицу времени и затем уже крутит стрелку – в таком случае надо правит прошивку, что не всегда возможно. Второй момент: а если Ваша приборка накрылась? Или Вы захотели вернуть все взад обратно? При наличии отдельной коробочки – просто убираем ее и все. Или просто меняем приборку. В случае когда лазили в приборку – надо снова в нее лезть.

Чаще стоит контроллер который считает импульсы за единицу времени и затем уже крутит стрелку – в таком случае надо правит прошивку, что не всегда возможно. Второй момент: а если Ваша приборка накрылась? Или Вы захотели вернуть все взад обратно? При наличии отдельной коробочки – просто убираем ее и все. Или просто меняем приборку. В случае когда лазили в приборку – надо снова в нее лезть.

В общих словах – нельзя просто взять и поделить частоту на 1.5 на рассыпухе (можно на МК сделать или на ПЛИС – но для авто, я предпочитаю простые схемы, которые не требовательны к питанию, температурному режиму и т.д.). Однако, никто не запрещает умножить на 2 и поделить на 3. Собственно данная схема этим и занимается. Настройки не требует – при исправных деталях работать начинает сразу.

Немножко о назначении цепочки FU1-VD1.

Микросхемы серии CD работают в диапазоне до 15В. Т.е. к бортовой сети их можно подключать без преобразователей. Однако, нормально работающая бортовая сеть выдает 14. 8 В (+/-), что прямо скажем – впритык. И скачков в ней хватает. По этой причине установлен сапрессор на 15В (VD1). Он становится закороткой при напряжениях выше 15В, таким образом гасит короткие всплески. А при длинных выходах за пределы диапазона еще и сожжет предохранитель.

8 В (+/-), что прямо скажем – впритык. И скачков в ней хватает. По этой причине установлен сапрессор на 15В (VD1). Он становится закороткой при напряжениях выше 15В, таким образом гасит короткие всплески. А при длинных выходах за пределы диапазона еще и сожжет предохранитель.

Не забываем, что предохранитель – чтобы от пожара защититься… А вот работоспособность устройства призван сохранить сапрессор.

Схема подключается к питанию (красный-черный проводники) и в разрыв провода между мозгом и приборкой.

Плату не привожу. Там до смешного все просто.

По заменам – CD4081 не стоит менять на советский аналог (К561ЛИ2 если память не изменяет, не захотела работать). CD4013 можно заменить на К561ТМ2 – это проверялось.

Резисторы/конденсаторы любые – лишь бы номиналы и тип сошлись.

Также хотел выложить осциллограммы работы:

Обратите внимание – скважность сигнала не теряется.

Наиболее часто для этого используют счетчики, хотя можно разделить частоту с помощью ждущего мультивибратора, ограничив число проходящих на выход импульсов. Пример такой схемы показан на рис. 1.60.

Пример такой схемы показан на рис. 1.60.

Рис. 1.60 Делитель частоты с использованием ждущего мультивибратора

Как только импульс входной частоты поступает на выход 5, ждущий мультивибратор D1.1, D1.3 запирает элемент D1.2 на время, определяемое резистором R1. Когда ждущий мультивибратор возвращается в исходное состояние, на выход поступает следующий импульс и цикл возобновляется. Схему можно усовершенствовать, заменив потенциометр полевым транзистором, что позволит управлять коэффициентом деления с помощью напряжения.

Рис. 1.61. Счетный триггер на логических элементах

Делитель на 2 можно собрать из простейших ЛЭ, рис. 1.61. Схемы делителей без использования RC-цепей имеют лучшую помехоустойчивость и болееширокий диапазон входной частоты сигнала. Основным элементом всех счетчиков является триггер с так называемым счетным входом, рис. 1.62.

Рис. 1.62. Делитель частоты на 2

Рис. 1.63. Делитель на 3

Таблица поясняет логику работы триггера 561ТМ2 в зависимости от управляющих сигналов (х – безразлично состояние на данном входе; состояние, когда на входах S и R микросхемы одновременно действует лог. “1”, является запрещенным).

“1”, является запрещенным).

Сигналы на входах | Состояние выхода | ||||

Рис. 1.64. а) Делитель на 10 на RS-триггерах; б) делитель на 10 на JK-триггерах

Рис. 1 65. Схема делителя на 60

Рис. 1. 66.

а) Универсальный реверсивный счетчик,

б) диаграмма напряжении микросхемы

Комбинационное включение триггеров позволяет получать счетчик с нужным коэффициентом деления входной частоты. На рис. 1.63. ..1.65 приведены примеры включения элементов микросхем для получения деления на 2, 3, 6, 10 и 60.

..1.65 приведены примеры включения элементов микросхем для получения деления на 2, 3, 6, 10 и 60.

Промышленность выпускает универсальные счетчики, которые в зависимости от управляющих сигналов могут переключаться по переднему или заднему фронту входного сигнала, а также менять направление счета (сложение или вычитание). В качестве примера приведена диаграмма работы двоичного четырехразрядного реверсивного счетчика на микросхеме 561ИЕ11, рис. 1.66.

Таблица истинности поясняет назначение управляющих сигналов и логику управления микросхемой (1 – лог. “1”; 0 – лог. “0”; х – состояние безразлично, т. е. 0 или 1). Счетчик предусматривает возможность загрузить по входам D1, D2, D4, D8 параллельный код.

Pис 1.67. Делитель на 1000

Для получения нужного коэффициента деления можно использовать микросхемы двоичных счетчиков, соединяя соответствующие выходы с помощью ЛЭ, рис. 1.67, или же применить счетчик с программируемым коэффициентом деления 564ИЕ15,

Книги и статьи | |

| / / |

Счетчики и делители частоты

Счетчики

импульсов – непременные узлы электронных

часов, микрокалькуляторов, частотомеров

и многих других приборов и устройств

цифровой техники. Основой их служат

триггеры со счетным входом. По логике

действия и функциональному назначению

счетчики импульсов подразделяют на

цифровые счетчики и делители частоты.

Первые из них обычно называют просто

счетчиками.

Основой их служат

триггеры со счетным входом. По логике

действия и функциональному назначению

счетчики импульсов подразделяют на

цифровые счетчики и делители частоты.

Первые из них обычно называют просто

счетчиками.

Простейшим одноразрядным счетчиком импульсов может быть JK-триггер и D-триггер, работающий в счетном режиме. Он считает входные импульсы по модулю 2-каждый импульс переключает триггер в противоположное состояние. Один триггер считает до двух, два соединенных последовательно считают до четырех, п триггеров-до 2n импульсов. Результат счета формируется в заданном коде, который может храниться в памяти счетчика или быть считанным другим устройством цифровой техники-дешифратором.

На рис. 1,а показана схема трехразрядного двоичного счетчика импульсов, построенного на JK-триггерax K155TB1.

Рис. 1 Трехразрядный двоичный счетчик

Смонтируйте

такой счетчик на макетной панели и к

прямым выходам триггеров подключите

светодиодные (или транзисторные – с

лампой накаливания) индикаторы, как это

делали ранее. Подайте от испытательного

генератора на вход С первого триггера

счетчика серию импульсов с частотой

следования 1 … 2 Гц и по световым сигналам

индикаторов постройте графики работы

счетчика.

Подайте от испытательного

генератора на вход С первого триггера

счетчика серию импульсов с частотой

следования 1 … 2 Гц и по световым сигналам

индикаторов постройте графики работы

счетчика.

Если в начальный момент все триггеры счетчика находились в нулевом состоянии (можно установить кнопочным выключателем SB1 “Уст.0”, подавая на вход R триггеров напряжение низкого уровня), то по спаду первого же импульса (рис. 1,б) триггер DD1 переключится в единичное состояние на его прямом выходе появится высокий уровень напряжения (рис. 1,в). Второй импульс переключит триггер DD1 в нулевое состояние, а триггер DD2-B единичное (рис. 45,г). По спаду третьего импульса триггеры DD1 и DD2 окажутся в единичном состоянии, а триггер DD3 все еще будет в нулевом. Четвертый импульс переключит первые два триггера в нулевое состояние, а третий- в единичное (рис. 1,д). Восьмой импульс переключит все триггеры в нулевое состояние. По спаду девятого входного импульса начнется следующий цикл работы трехразрядного счетчика импульсов.

Изучая графики, нетрудно заметить, что каждый старший разряд счетчика отличается от младшего удвоенным числом импульсов счета. Так, период импульсов на выходе первого триггера в 2 раза больше периода входных импульсов, на выходе второго триггера – в 4 раза, на выходе третьего триггера – в 8 раз. Говоря языком цифровой техники, такой счетчик работает в весовом коде 1-2-4. Здесь под термином “вес”имеется в виду объем информации, принятой счетчиком после установки его триггеров в нулевое состояние. В устройствах и приборах цифровой техники наибольшее распространение получили четырехразрядные счетчики импульсов, работающие в весовом коде 1-2-4-8.

Делители частоты считают входные импульсы до некоторого задаваемого коэффициентом счета состояния, а затем формируют сигнал переключения триггеров я нулевое состояние, вновь начинают счет входных импульсов до задаваемого коэффициента счета и т. д.

Для примера на рис. 2 показаны схема и графики работы делителя с коэффициентом счета 5, построенного на JK-триггерах.

Рис. 2 Схема и графики работы делителя

Здесь вам трехразрядный двоичный счетчик дополнен логическим элементом 2Й-НЕ DD4.1, который и задает коэффициент счета 5. Происходит это так. При первых четырех входных импульсах (после установки триггеров в нулевое состояние кнопкой SB1 “Уст. 0”) устройство работает как обычный двоичный счетчик импульсов. При этом на одном или обоих входах элемента DD4.1 действует низкий уровень напряжения, поэтому элемент находится в единичном состоянии.

По спаду же пятого импульса на прямом выходе первого и третьего триггеров, а значит, и на обоих входах элемента DD4.1 появляется высокий уровень напряжения, переключающий этот логический элемент а нулевое состояние. В этот момент на его выходе формируется короткий импульс низкого уровня, который через диод VD1 передается на вход R всех триггеров и переключает их в исходное нулевое состояние. С этого момента начинается следующий цикл работы счетчика.

Резистор R1 и диод VD1, введенные в этот счетчик, необходимы для того, чтобы исключить замыкание выхода элемента DD4.1 на общий провод.

Действие такого делителя частоты можете проверить, подавая на вход С первого его триггера импульсы, следующие с частотой 1… 2 Гц, и подключив к выходу триггера DD3 световой индикатор.

На практике функции счетчиков импульсов и делителей частоты выполняют специально разработанные микросхемы повышенной степени интеграции. В серии К155, например, это счетчики К155ИЕ1, К155ИЕ2, К155ИЕ4 и др. В радиолюбительских разработках наиболее широко используют микросхемы К155ИЕ1 и К155ИЕ2.

Условные графические обозначения этих микросхем-счетчиков с нумерацией их выводов показаны на рис. 3.

Рис. 3 Микросхемы-счетчики

Микросхему К155ИЕ1 (рис. 47,а) называют декадным счетчиком импульсов, т. е. счетчиком с коэффициентом счета 10. Он содержит четыре триггера, соединенных между собой последовательно. Выход (вывод 5) микросхемы – выход ее четвертого триггера. Устанавливают все триггеры в нулевое состояние подачей напряжения высокого уровня одновременно на оба входа R (выводы 1 и 2), объединенные по схеме элемента И (условный символ “&”). Счетные импульсы, которые должны иметь низкий уровень, можно подавать на соединенные вместе входы С (выводы 8 и 9), также объединенные по И. или на один из них, если в это время на втором будет высокий уровень напряжения. При каждом десятом входном импульсе на выходе счетчик формирует равный по длительности входному импульс низкого уровня.

Микросхема К155ИЕ2 (рис. 3,б) -двоично-десятичный четырехразрядный счетчик. В нем также четыре триггера, но первый из них имеет отдельные вход С1 (вывод 14) и отдельный прямой выход (вывод 12). Три других триггера соединены между собой так, что образуют делитель на 5.

Рис. 4 Делители частоты

При соединении выхода первого триггера (вывод 12) со входом С2 (вывод 1) цепи остальных триггеров микросхема становится делителем на 10 (рис. 4, а), работающем в коде 1-2-4-8, что и символизируют цифры у выходов графического обозначения микросхемы. Для установки триггеров счетчика в нулевое состояние подают на оба входа R0 (выводы 2 и 3) напряжение высокого уровня.

Два объединенных входа R0 и четыре разделительных выхода микросхемы К155ИЕ2 позволяют без дополнительных элементов строить делители частоты с коэффициентами деления от 2 до 10. Так, например, если соединить между собой выводы 12 и 1, 9 и 2, 8 и 3 (рис. 4,б), то коэффициент счета будет 6, а при соединении выводов 12 и 1, 11,. 2 и 3 (рис. 4,в) коэффициент счета станет 8. Эта особенность микросхемы К155ИЕ2 позволяет использовать ее и как двоичный счетчик импульсов, и как делитель частоты.

Читайте и пишите полезныеДеление частоты

Наиболее часто для этого используют счетчики, хотя можно разделить частоту с помощью ждущего мультивибратора, ограничив число проходящих на выход импульсов. Пример такой схемы показан на рис. 1.60. Как только импульс входной частоты поступает на выход 5, ждущий мультивибратор D1.1, D1.3 запирает элемент D1.2 на время, определяемое резистором R1. Когда ждущий мультивибратор возвращается в исходное состояние, на выход поступает следующий импульс и цикл возобновляется. Схему можно усовершенствовать, заменив потенциометр полевым транзистором, что позволит управлять коэффициентом деления с помощью напряжения.

Рис. 1.60 Делитель частоты с использованием ждущего мультивибратора

Делитель на 2 можно собрать из простейших ЛЭ, рис. 1.61. Схемы делителей без использования RC-цепей имеют лучшую помехоустойчивость и болееширокий диапазон входной частоты сигнала. Основным элементом всех счетчиков является триггер с так называемым счетным входом, рис. 1.62. Таблица 1.4

Таблица 1.4

Сигналы на входах | Состояние выхода | ||||

Рис. 1.62. Делитель частоты на 2

Рис. 1.63. Делитель на 3

Рис. 1.64. а) Делитель на 10 на RS-триггерах; б) делитель на 10 на JK-триггерах

поясняет логику работы триггера 561ТМ2 в зависимости от управляющих сигналов (х – безразлично состояние на данном входе; состояние, когда на входах S и R микросхемы одновременно действует лог. “1”, является запрещенным).

Комбинационное включение триггеров позволяет получать счетчик с нужным коэффициентом деления входной частоты. На рис. 1.63…1.65 приведены примеры включения элементов микросхем для получения деления на 2, 3, 6, 10 и 60.

Промышленность выпускает универсальные счетчики, которые в зависимости от управляющих сигналов могут переключаться по переднему или заднему фронту входного сигнала, а также менять направление счета (сложение или вычитание). В качестве примера приведена диаграмма работы двоичного четырехразрядного реверсивного счетчика на микросхеме 561ИЕ11, рис. 1.66.

Таблица истинности (табл. 1.5) поясняет назначение управляющих сигналов и логику управления микросхемой (1 – лог. “1”; 0 – лог. “0”; х – состояние безразлично, т. е. 0 или 1). Счетчик предусматривает возможность загрузить по входам D1, D2, D4, D8 параллельный код.

Рис. 1 65. Схема делителя на 60

Таблица 1.5

Для получения нужного коэффициента деления можно использовать микросхемы двоичных счетчиков, соединяя соответствующие выходы с помощью ЛЭ, рис. 1.67, или же применить счетчик с программируемым

коэффициентом деления 564ИЕ15, см. рис. 1.26.

Рис. 1. 66. а) Универсальный реверсивный счетчик,

б) диаграмма напряжении микросхемы

Pис 1.67. Делитель на 1000

Триггеры, выполненные на двух вентилях, как показано на рис. 8.47 и 8.50, обычно называют RS (от английских слов: ), или асинхронными триггерами. Посредством подачи соответствующего входного сигнала они могут быть установлены в то или иное состояние. -триггеры удобно использовать в схемах защиты от дребезга, а также во многих других случаях, однако более широкое применение получили триггеры, схема которых несколько отличается от рассмотренной. Вместо пары асинхронных входов они имеют один или два информационных входа и один тактирующий вход. В момент подачи тактирующего импульса выходное состояние триггера либо изменяется, либо остается прежним, в зависимости от того, какие сигналы действуют по информационным входам.

Рис. 8.51. Синхронизированный триггер.

Простейшая схема тактируемого триггера приведена на рис. 8.51. От рассмотренной выше схемы она отличается наличием двух вентилей («SET» и «RESET»). Легко проверить, что таблица истинности для этого триггера будет иметь вид

где – состояние выхода Q после подачи тактового импульса, а – до его поступления. Главное отличие схемы от предыдущей состоит в том, что входы S и R в этом случае должны рассматриваться как информационные и сигналы, присутствующие на этих входах в момент поступления тактового импульса, и определяют, что произойдет с выходом .

У этого триггера есть один недостаток. Дело в том, что изменение выходного состояния в соответствии со входными сигналами может происходить в течение всего отрезка времени, на котором тактовый импульс имеет высокий уровень. В этом смысле он еще подобен асинхронному -триггеру. Эта схема известна также под названием «прозрачный фиксатор», потому что выход «насквозь просматривает» вход в течение интервала действия тактового сигнала.

Всесторонние возможности триггерных схем раскроются после введения новых, нескольких отличных от рассмотренных конфигураций, которые представляют собой триггер типа «ведущий-ведомый» (двухступенчатый) и триггер, запускаемый по фронту.

Рис. 8.52. D-триггеры с запуском по фронту.

Триггеры типа «ведущий-ведомый» и триггеры, запускаемые по фронту.

Эти типы триггеров наиболее распространены. Информация, поступившая на входные линии этого триггера к моменту возникновения перехода или «фронта» тактового сигнала, определяет, каким будет состояние выхода в последующий интервал времени. Такие триггеры выпускаются в виде недорогих ИМС и всегда используются в этом виде, но для того чтобы понять, как они работают, имеет смысл рассмотреть их внутреннюю структуру. На рис. 8.52 показаны принципиальные схемы так называемых -триггеров. Информация, поступившая на -вход, передается на выход Q после подачи тактового импульса. Рассмотрим принципы действия триггера типа ведущий – ведомый (рис. 8.52, а). Если тактовый сигнал имеет высокий уровень, разрешается работа вентилей 1 и 2, через которые ведущий триггер (вентили 3 и 4) устанавливается в состояние, соответствующее -входу: . Вентили 5 и 6 закрыты, поэтому ведомый триггер (вентили 7 и 8) сохраняет свое предыдущее состояние. Когда тактовый сигнал перейдет в состояние низкого уровня, входы ведущего триггера отключатся от -входа, а входы ведомого подключатся к входу ведущего, в результате последний передаст свое состояние ведомому триггеру. После этого никакие изменения на выходе произойти не смогут, так как ведущий триггер заблокирован. С приходом следующего тактового сигнала ведомый триггер отключится от ведущего, а ведущий воспримет новое состояние входа.С точки зрения внешних сигналов триггер, срабатывающий по фронту, ведет себя точно также, однако внутри он работает по-другому. Принцип его действия нетрудно разобрать самостоятельно. Схема, показанная на рис. 8.52, б, представляет собой распространенный семейства ТТЛ, срабатывающий на положительном перепаде. В рассмотренном ранее триггере типа «ведущий-ведомый» данные на выход передавались по отрицательному перепаду тактового импульса.

Рис. 8.53. D- и JK-триггеры.

В номенклатуру стандартных ИМС, выпускаемых промышленностью, входят триггеры, срабатывающие как по одной, так и по другой полярности перепада. Кроме того, большинство триггеров имеют также асинхронные входы 5 и R. Они могут устанавливаться или сбрасываться как высоким, так и низким уровнем в зависимости от типа триггера. На рис. 8.53 показано несколько популярных триггеров. Стрелка обозначает динамический вход (срабатывание по фронту), а кружок – инверсию. Таким образом, изображенная на рисунке схема 74 представляет собой сдвоенный -триггер, который срабатывает по положительному перепаду и имеет асинхронные входы 5 и R, активные по низкому уровню. Схема 4013 представляет собой сдвоенный -триггер семейства КМОП, срабатывающий по положительному перепаду и имеющий асинхронные входы 5 и R, активные по высокому уровню. Интегральная схема 112 – это сдвоенный -триггер типа ведущий – ведомый, срабатывающий по отрицательному перепаду и имеющий асинхронные входы 5 и R, активные по низкому уровню.

JK-триггер.

По принципу действия JK-триггер аналогичен D-триггеру, но имеет два информационных входа. Его таблица истинности имеет вид:Если на входы поступают противоположные сигналы, то на очередном фронте тактового импульса выход Q воспроизводит значение -входа. Если оба входа J и К имеют низкий уровень, то состояние выхода не изменится. И наконец, если на обоих входах высокий уровень, триггер будет совершать «переброс» (менять свое состояние на каждом тактовом импульсе), т. е. работать в счетном режиме).

Предупреждение. Некоторые старые типы – триггеров представляют собой «ловушку для единиц». Этот термин вы не найдете ни в одной документации, он означает явление, которое может привести неосведомленного человека к весьма неприятным последствиям. Дело в том, что если на интервале, когда ведомый триггер открыт тактовым сигналом, вход J и К (или оба одновременно) на какой-то момент изменит свое состояние, а затем до окончания тактового сигнала вернется в исходное, то это кратковременное состояние триггер запомнит и в дальнейшем он будет вести себя так, как если бы это состояние сохранилось. В результате триггер может переброситься на следующем тактовом перепаде, даже если сигналы, действующие в момент этого перепада на входах J и К подтверждают предыдущее состояние. Это может привести, мягко говоря, к своеобразному поведению. Проблема возникает из-за того, что эти триггеры были сконструированы в предположении, что тактовый импульс имеет очень короткую длительность, в то время как в действительности тактирование всегда производится сигналом конечной длительности. Если используется триггер типа «ведущий-ведомый», следует соблюдать меры предосторожности, либо вообще избегать их, применяя более надежные триггеры, работающие по фронту. Две хорошие альтернативы, которые используют истинно запуск по фронту, это приборы 112 и 109. Оба представляют собой сдвоенные (два в одном корпусе) -триггеры с асинхронными 5- и -входами, активными по низкому уровню. Устройство 112 срабатывает по отрицательному фронту тактового сигнала, а устройство положительному. Схема 109 имеет интересную особенность, а именно, К-вход у него инверсный, поэтому иногда его называют JК-триггер с запретом.-входе всегда действует инверсия по отношению к текущему состоянию триггера. Частота сигнала на выходе в любом случае будет равна половине входной частоты.

Рис. 8.55. Время установления данных и время удержания.

Синхронизация информации и тактирование.

В связи с последней схемой возникает интересный вопрос: не получится ли так, что триггер не сможет переброситься, так как состояние -входа изменяется почти сразу же вслед за тактовым импульсом? Другими словами, не начнет ли схема сбиваться, если на ее входе происходят такие странные явления? Этот вопрос можно сформулировать и следующим образом: в какой точно момент по отношению к тактовому импульсу -триггер (или какой-нибудь другой) анализирует состояние своего входа? Ответ такой: для любого тактируемого устройства существует определенное «время установления» густ и «время удержания» . Для того чтобы схема работала правильно, информация должна поступать на вход не позднее чем за время до возникновения тактового перепада и оставаться неизменной по крайней мере в течение времени. Если сигнал на -входе изменяется на интервале времени удержания, то может возникнуть любопытный эффект, носящий название «метастабильное состояние», при котором триггер не может определить, в какое состояние он должен перейти. Об этом явлении мы вскоре еще упомянем.Рис. 8.56. 4-разрядный счетчик.

Деление на число, большее чем 2.

С помощью каскадного соединения счетных триггеров (выход Q каждого предыдущего триггера подключен к тактическому входу последующего) легко получить «делитель на , или двоичный счетчик. На рис. 8.56 показана схема четырехразрядного асинхронного счетчика и даны его временные диаграммы. Заметим здесь, что если выход Q каждого триггера непосредственно действует на тактовый вход следующего, срабатывание триггеров должно происходить по спаду (заднему фронту) сигнала на тактовом входе (показано кружком инверсии). Эта схема представляет собой счетчик – делитель на 16: на выходе последнего триггера формируются прямоугольные импульсы, следующие с частотой, равной 1/16 частоты входного тактового сигнала. Схема называется счетчиком, поскольку информация, присутствующая на четырех входах Q, может рассматриваться как -разрядное двоичное число, которое изменяется от 0 до 15, увеличиваясь на единицу с каждым входным импульсом.Этот факт отражает временная диаграмма на рис. 8.56.б, на которой СЗР означает «старший значащий разряд», МЗР – «младший значащий разряд», а изогнутые стрелки, облегчающие понимание, указывают, какими перепадами вызываются изменения сигналов.

Этот счетчик, как вы увидите в разд. 8.25, выполняет настолько важную функцию, что выпускается в виде большого числа модификаций, выполненных в виде однокристальных микросхем, включая такие форматы счета, как -разрядный, двоично-десятичный и многоцифровой. Соединяя эти счетчики каскадно и воспроизводя их содержимое с помощью цифрового индикатора (например, светодиодного) можно легко построить схему подсчета каких-либо событий. Если разрешить прохождение импульсов на вход счетчика в течение ровно 1 с, то получится счетчик частоты, который будет воспроизводить значение частоты путем подсчета числа периодов в секунду. В разд. 15.10 приводятся схемы этого простого, но очень полезного устройства. Промышленностью выпускаются однокристальные счетчики частоты, в состав которых входят дополнительно генератор, схемы управления и вывода на индикацию. Триггер такого устройства показан на рис. 8.71.

На практике простейшая схема каскадирования счетчиков посредством соединения каждого выхода Q со следующим тактовым входом имеет некоторые интересные проблемы, связанные с покаскадной задержкой распространения сигнала по цепочке триггеров. По этой причине лучше использовать схему, в которой один и тот же тактовый сигнал подается одновременно на все входы. В следующем разделе мы будем рассматривать эти синхронные тактируемые системы.

Делитель частоты – это… Что такое Делитель частоты?

электронное устройство, уменьшающее в целое число раз частоту подводимых к нему периодических колебаний. Д. ч. используют в Синтезаторах частоты, кварцевых и атомных часах, в телевизионных устройствах синхронизации генераторов развёрток, хронирующих устройствах Радиолокаторов и др. Для деления частоты применяют: электронный счётчик (см. Триггер), самовозбуждающийся генератор синусоидальных колебаний, регенеративное устройство, самовозбуждающийся генератор с устройством фазовой автоматической подстройки частоты (ФАПЧ), релаксационный генератор и др. В самовозбуждающемся генераторе синусоидальных колебаний деление осуществляется синхронизацией его частоты на субгармоническом колебании (См. Субгармонические колебания) частоты внешнего периодического сигнала с использованием явления захватывания частоты (См. Захватывание частоты). В регенеративном Д. ч. синусоидальных колебаний (рис.) на преобразователь частоты подаются периодический сигнал частоты f, подлежащей делению, и сигнал частоты (k – 1)․f/k (k — коэффициент деления), возникающий в цепи обратной связи только при подведении на вход Д. ч. напряжения преобразуемой частоты. На выходе преобразователя выделяется сигнал разностной частоты, равной f/k. В устройстве, состоящем из самовозбуждающегося генератора и ФАПЧ, фазовым детектором сравниваются частота гармонического колебания (См. Гармонические колебания) в k раз большая, чем основная частота колебаний генератора, и делимая частота. С выхода фазового детектора напряжение рассогласования, пропорциональное разности сравниваемых частот, подаётся на генератор и изменяет его основную частоту до тех пор, пока она не станет точно в k раз меньше делимой частоты. Для деления частоты повторения импульсных сигналов применяют Д. ч. на релаксационных генераторах (Мультивибраторах и Блокинг-генераторах), работающих в периодическом режиме с захватыванием частоты повторения импульсов на субгармоническом колебании или в ждущем режиме с периодом повторения импульсов большим в k раз. Практически k не превышает 10.Лит.: Фролкин В. Т., Импульсные устройства, 2 изд., М., 1966; Гоноровский И. С., Радиотехнические цепи и сигналы, ч. 2, М., 1967.

Ю. Б. Любченко.

Схема регенеративного делителя частоты. Прохождение сигнала в замкнутой цепи обратной связи показано пунктирными стрелками.

Делитель частоты на 10 для частотомера на 193ИЕ2.

Для расширения верхнего предела частотомера предлагаю собрать простой делитель частоты на микросхеме 193ИЕ2. Коэффициент деления данного делителя = 10, максимальная входная частота для 193ИЕ2 — 200 мгц. Т.е. с описанными ранее частотомерами этот делитель позволит измерять частоту до 200 мгц с разрешением в 100 гц.

Чувствительность делителя не менее 100 мв., это позволяет в большинстве случаев обойтись без специального входного формирователя. Выход делителя подключается к входу частотомера, входные цепи которого выполняют роль преобразователей уровня напряжения.

Принципиальная схема делителя.

Обо всех замеченных недостатках прошу сообщать по адресу [email protected]

Автор: А. Денисов г. Тамбов (RA3RBE)

Источник: http://ra3rbe.r3r.ru/divider.htm

ПОДЕЛИТЕСЬ С ДРУЗЬЯМИ

П О П У Л Я Р Н О Е:

- Простая схема электронной «массы» для автомобиля

- Простая УФ лампа своими руками

- Как заменить сенсорную панель своими руками?

Электронный выключатель «МАССЫ» для авто своими руками

Чтобы обезопасить свой автомобиль от случайного возгорания от короткого замыкания проводки на время стоянки, а также чтобы излишне не разряжать аккумулятор многие автолюбители устанавливают в своем автомобиле устройство для отключения «массы». С его помощью аккумулятор легко отсоединяется от бортовой электросети автомобиля. Не нужно каждый раз снимать клемму с АКБ. Иногда ставят такое устройство под руль в салоне авто и не нужно даже открывать капот.

Подробнее…

Решил я попытаться перейти на фоторезист и покрывать платы паяльной маской.

Соответственно всё это дело относится к работе с Ультрафиолетом.

Давненько валялись ультрафиолетовые светодиоды, решил я на них засветку фоторезиста сделать.

Подробнее…

Не работает или плохо работает сенсор в телефоне или планшете? Одна из частых неисправностей современных сенсорных устройств — повреждение сенсорного экрана. Его ещё называют «тачскрином», просто «тачем» или «сенсором». Не стоит отчаиваться — его можно заменить самому. Стоит такая панель не дорого, намного дешевле, чем покупать новый телефон.

Подробнее…

Популярность: 7 251 просм.

Делитель частоты для программного частотомера « схемопедия

При использовании программного частотомера и осциллографа измерение частот сигналов ограничено, как правило, границами частотного диапазона звуковой карты компьютера. Чтобы иметь возможность измерить частоты выше 20 кГц, а также посмотреть их форму и спектр на осциллографе, можно применить простейший делитель частоты. Проще всего его можно реализовать с помощью цифровых микросхем – десятичных счетчиков. Каждый такой счетчик выдает на соответствующем выходе сигнал, меньший входного по частоте в 10 раз. На рис.1 представлена схема такого делителя частоты. При использовании двух микросхем-счетчиков входной сигнал можно разделить на 10 два раза, то есть получить на выходе сигнал, частота которого будет меньше входного в 10 и 100 раз. Коммутация кратности деления частоты производится при помощи простого переключателя S1 на два положения.

В качестве счетчиков можно применить любые МС (десятичные счетчики), желательно КМОП-технологии, так как такие микросхемы некритичны к питающему напряжению и хорошо работают с разными уровнями сигналов, как цифровых, так и аналоговых. В приведенной схеме применены микросхемы К164ИЕ2, можно использовать и другие, функционально аналогичные, например К561ИЕ4, К 176ИЕ4……… Неиспользуемые входные и управляющие выводы микросхем следует соединить с общим проводом, как показано на схеме ( выводы 1,4,5,6,7,9), чтобы исключить возможность появления на них наведенного напряжения помех.

Конструкция делителя показана на фото ниже (прошу извинить за низкое разрешение картинки, в данный момент нет лучшего фото!). Схема собрана на печатной плате, на которой протравлены только контактные площадки под ножки микросхем. Все соединения сделаны одножильным проводом в изоляции, поскольку схема простая и соединений минимум.

Щуп делителя сделан из отрезка провода в экране. В качестве наконечника щупа можно использовать, например, тонкий гвоздь длиной 4 – 5 см. Провод паяется к гвоздю любым обычным припоем на таблетке аспирина (простого «советского»). Аспирин хорошо заменяет паяльную кислоту при пайке железа. Затем провод с наконечником-гвоздем можно вставить, например, в корпус пустой шариковой ручки.

Экран входного провода нужно соединить с общим проводником делителя ( минус питания). Питание на делитель можно подавать с устройства, частоту которого мы измеряем. Для этого концы проводов питания можно снабдить небольшими зажимами типа «крокодил». Выходной шнур с разъемом для входа звуковой карты компьютера также экранированный. Схема распайки разъема показана на рисунке.

Если брать питание с измеряемой схемы, то соединение с общим проводом обеспечится через минусовой питающий провод. Если же питание делителя отдельное, например от батареи типа «Крона», то следует соединить общий провод делителя с общим проводом измеряемой схемы отдельным проводником.

Для лучшего согласования входа делителя с измеряемой схемой и для уменьшения взаимного влияния можно на входе данного делителя добавить какой-либо простой согласующий каскад с как можно более высоким входным сопротивлением. Например такой:

Подстроечным резистором VR1 выставляют режим работы транзистора, чтобы не было ограничения («срезки») входного сигнала по амплитуде снизу и сверху (можно контролировать форму сигнала с помощью программного осциллографа на выходе делителя частоты). Транзистор – любой маломощный, например КТ315, КТ342, КТ3102….

Для наглядной демонстрации работы делителя ниже приводится скриншот, где измеряется ВЧ сигнал с частотой порядка 900 кГц (переключатель S1 в положении «1/100»). Показания частотомера в этом случае, естественно, нужно умножить на 100:

Автор: Андрей Барышев

Схема делителя частоты

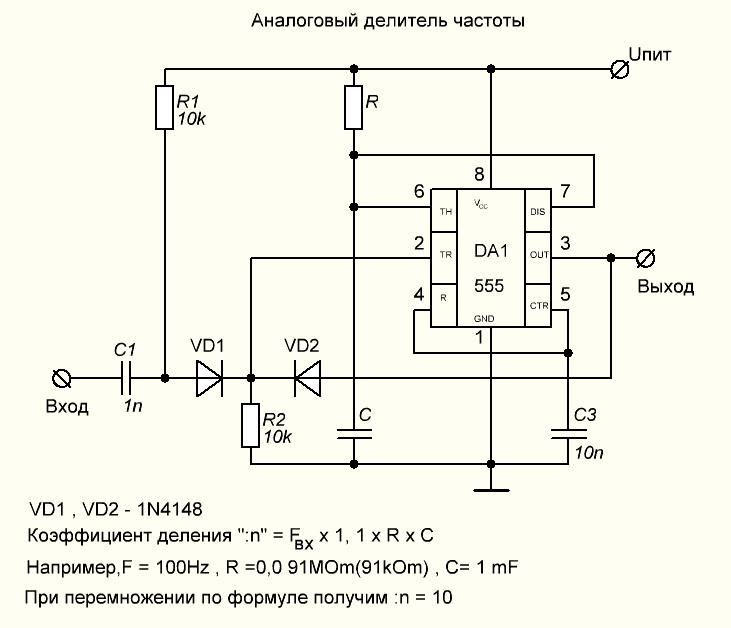

Цепи делителя частоты занимают важное место в цифровых логических схемах и некоторых схемах аналогового мультиплексирования, создание идеального делителя частоты – довольно сложная вещь, используя таймер IC 555 и декадный счетчик IC CD4017, мы можем создать простую и легкую в конструкции схему делителя частоты.

Мы знаем, что делители частоты делят любую входную частоту f на целое число n (f / n), следующая схема принимает входную частоту f и выдает выходную частоту как (f / 2), (f / 4) и (f / 6).Здесь микросхема таймера используется для генерации прямоугольного импульсного сигнала и может быть настроена на другую частоту с помощью переменного резистора. Выходной сигнал с точным разделением частоты снимается с вывода Q1 декадного счетчика.

Строительные и рабочие

Эта схема делителя частоты, состоящая из двух частей, одна является генератором входной частоты, а другая – схемой декадного счетчика / делителя. IC 555 сконфигурирован как нестабильный мультивибратор, синхронизирующий резистор (R1, R2) и переменный резистор VR1 подключены к синхронизирующему конденсатору C1, разрядный вывод 7 подключен между R1 и R2, затем пороговый вывод 6 и триггерный вывод 2 подключены между VR1 и C1.5V vcc приложено к контакту 8 смещения и контакту сброса 4, здесь контакт 5 управляющего напряжения подключен к земле через конденсатор C2 емкостью 0,1 мкФ. Выходной контакт 3 соединен с тактовым контактом декадного счетчика ic и LED1, этот светодиод показывает входную частоту.

IC 4017 принимает входную синхронизацию на выводе 14 и обеспечивает декадный выход от Q0 до Q9. Чтобы преобразовать это в делитель частоты, мы взяли выходной сигнал с контакта 2 и подключили к LED2 через R4, это будет визуально отображать выходную частоту посредством мигания.Контакт 13 активного низкого разрешения заземлен, а контакт 15 сброса подключен к трехпозиционному переключателю в направлении Q2 для выбора выхода F / 2, Q4 для выбора выхода F / 4 и Q6 для выбора выхода F / 6. Когда мы используем осциллограф на выходном контакте 2, мы можем получить разделенную выходную частоту.

Форма выходного сигнала

Первый сигнал представляет входную частоту (f) и выходную частоту (f / 2), (f / 4) и (f / 6) показывают результаты разделенной частоты.

Цепи делителя частоты: что нужно знать

Аналоговые и цифровые приложения требуют использования частотного разделения для настройки сигнала в соответствии с требованиями схемы.Для создания схемы делителя частоты можно использовать несколько подходов. Давайте посмотрим на некоторые из этих подходов.

Схема делителя частоты типа DКак следует из названия, в схемах этого типа используются триггеры d-типа. Для тех из вас, кто не знает, что такое триггер D-типа, вот его суть.

Триггер d-типа – это триггер, запускаемый по фронту, который изменяет свой выходной отклик только во время нарастающего фронта тактового сигнала.Функция запуска по фронту триггеров d-типа позволяет легко разделить входящие часы в 2 раза.

Выход из Q ’возвращается как вход, создавая петлю обратной связи. Входящий импульс служит часами для схемы делителя, заставляя данные отображаться как выходные.

Рассмотрим этот пример для понимания работы делителей тактовой частоты d-типа. Считайте, что первый вход часов равен «1». Это приводит к тому, что вход появляется в Q. Если Q = 1, то Q ’= 0. Этот Q ’снова подается на вход, однако к тому времени тактовый цикл возвращается к 0, сохраняя выход« 1 ».Выход изменится с 1 на 0 во время следующего нарастающего фронта тактового сигнала.

В течение двух тактовых циклов выход изменяется только один раз – выходная частота делится на 2.

555 Цепь делителя частотыНазван так из-за наличия трех подключенных внутри резисторов мощностью 5кВт; ИС используется в качестве схемы таймера для генерации сигналов с переменным коэффициентом заполнения от 50% до 100%.

Работа схемы начинается с генерации сигнала, за которым следует его частотное деление.

Уровень 555 генерирует входную частоту, регулируемую потенциометром. Сгенерированная частота далее переходит в 4017 IC. В зависимости от диапазона частотного деления вы можете подключить вывод сброса OF 555 IC к Q2, Q4 или другим выходным клеммам на 4017 IC.

Если вы подключили вывод сброса к Q2, ваш таймер 555 будет сбрасываться при каждом втором импульсе, разделив ваш тактовый сигнал на 2.

Ищете делители частоты?ADSANTEC предоставляет широкий спектр делителей тактовой частоты , которые делят ваш сигнал на 2, 4 или даже больше, в зависимости от вашего программирования.Мы предлагаем продукцию высочайшего качества с различными требованиями к частоте и мощности. В наш ассортимент входят АЦП, усилители, трансимпедансные усилители, фазовращатели и многое другое.

Свяжитесь с нами сегодня и закажите изделие, соответствующее требованиям вашей схемы!

Цепь программируемого целочисленного делителя частоты Характеристики делителя частоты- Широкий диапазон входных частот от 100 кГц до 18 ГГц

- Два каскадно программируемых делителя частоты 1–256 обеспечивают широкий диапазон коэффициентов деления, от 1 до 65536

- Два идентичных дифференциальных выхода позволяют подключать до четырех нагрузок

- Низкий фазовый шум ≤ -131 дБн / Гц при отстройке 1 кГц (13.3. Сигнал ГГц, коэффициент деления 14)

- Высокая SFDR ≥ 75 дБ

- Гибкое интерактивное управление с передней панели и программное управление с USB

- Контрольно-измерительные приборы

- Автоматизация испытаний

- Лабораторные испытания, прототип системы

G1182 – это программируемый целочисленный делитель частоты с низким уровнем шума, который покрывает широкий диапазон входных частот от 100 кГц до 18 ГГц.Имеет следующие функциональные блоки:

- Буферизованный дифференциальный вход, который принимает широкий диапазон сигналов от -6 дБм до +10 дБм

- Два последовательно подключенных малошумящих программируемых делителя частоты 1–256

- Буфер разветвления с двумя дифференциальными выходами, которые можно использовать как четыре несимметричных выхода, обеспечивая уровень выходного сигнала -2 дБм на каждом выходе

- Микроконтроллер с поддержкой USB, который управляет программированием делителя с передней панели и по USB-каналу.

Коэффициент деления отображается на 5-сегментном светодиодном дисплее на передней панели и может управляться интерактивно с помощью кнопок на передней панели. Управление делителем также может выполняться программным приложением через USB-соединение (полезно для автоматизированных приложений).

Рабочий цикл выходного сигнала составляет 50% при любом коэффициенте деления.

Благодаря низкому фазовому шуму, низкому джиттеру и высокому SFDR делитель может использоваться для прецизионных измерений в исследовательских и производственных средах.

Для наилучшей производительности, пожалуйста, закройте неиспользуемые входы и выходы заделкой на 50 Ом.

Для данной конструкции требуется один источник питания +12 В, 2 А постоянного тока.

Программируемый делитель частотыВы можете запрограммировать G1182 в интерактивном режиме с передней панели или программно через USB-соединение.

Программный API USB описан в отдельном документе.

На передней панели находится 5-значный светодиодный индикатор и три кнопки управления: «Режим», «+» и «-».

Кнопка «Mode» циклически переключает между тремя режимами управления:

- Регулировка соотношения полного делителя

- Регулировка соотношения делителя №1

- Регулировка соотношения делителя №2

В режиме управления соотношением Full Divider вы изменяете комбинированный коэффициент делителя обоих делителей в диапазоне от 1 до 65536. В этом режиме светодиодный индикатор показывает комбинированный коэффициент делителя. Этот режим выбирается по умолчанию при включении питания.

Поскольку два делителя 1–256 подключены последовательно, не все коэффициенты делителя в диапазоне 1–65536 можно установить.Например, если коэффициент делителя делится на простое число больше 256, такое соотношение делителя невозможно достичь. Микроконтроллер автоматически пропускает передаточные числа, которых невозможно достичь.

В режимах управления соотношением Divider # 1 и Divider # 2 вы изменяете коэффициент делителя отдельного делителя 1–256: # 1 или # 2. В этих режимах светодиодный индикатор показывает номер делителя (1 или 2), за которым следует тире, за которым следует коэффициент делителя или индивидуальный делитель.

Для наилучшей производительности микроконтроллер не позволит вам выбрать коэффициент делителя №1 меньше, чем коэффициент делителя №2, или коэффициент делителя №2 больше, чем коэффициент делителя №1. В случае такой попытки светодиодный индикатор покажет соответственно _ _ _ _ _ или ¯ ¯ ¯ ¯ ¯.

Кнопки «+» и «-» увеличивают и уменьшают выбранный коэффициент делителя. При однократном нажатии кнопки «+» или «-» коэффициент делителя изменяется на следующее или предыдущее доступное значение. При нажатии и удерживании более секунды коэффициент делителя начинает меняться с медленной скоростью.Когда вы продолжаете удерживать кнопку, коэффициент делителя начинает изменяться с большей скоростью.

Когда кнопки «+» и «-» нажимаются одновременно, они сбрасывают выбранный делитель на 1.

Выбранный коэффициент делителя автоматически сохраняется в энергонезависимой памяти и восстанавливается при включении питания.

Технические характеристики [1]

| Ввод | |||||

| Коэффициент деления 1 | Коэффициент деления ≥ 2 | ||||

| Диапазон частот | от 100 кГц до 16 ГГц | от 100 кГц до 18 ГГц | |||

| Входной уровень | ≤ 15 ГГц | -6… 10 дБм 0.3… 2В размах | ≤ 17 ГГц | -6… 10 дБм 0,3… 2 В размах | |

| 15… 16 ГГц | 0… 10 дБм 0,63… 2 В размах | 17… 18 ГГц | 0… 10 дБм 0,63… 2 В размах | ||

| Входное сопротивление | Несимметричный 50 Ом, дифференциальный 100 Ом | ||||

| Возвратные потери (тип.) | -8 дБ при 15 ГГц | ||||

| Коэффициент делителя | 1… 65536 [2] (достигается как комбинация двух последовательных делителей 1–256) | ||||

| Выход | |||||

| Выходной уровень | 0.5V p-p несимметричный | ||||

| Выходное сопротивление | 50 Ом несимметричный | ||||

| Рабочий цикл | 50% | ||||

| Возвратные убытки (тип.) | -10 дБ на 15 ГГц | ||||

| Время нарастания / спада (тип.) | ≤ 26 пс | ||||

| Уровень шума | |||||

| Фазовый шум [3] (тип., См. Рисунок 1) | 13.Вход 3 ГГц, коэффициент ÷ 1 [4] | -110 дБн при смещении 1 кГц | |||

| Вход 13,3 ГГц, коэффициент ÷ 14 | -131 дБн при смещении 1 кГц | ||||

| SFDR (тип., См. Рисунок 2, рисунок 3) | ≥ 75 дБ | ||||

| Электрические и механические | |||||

| Источник питания | + 12В, 2А постоянного тока | ||||

| Потребляемая мощность | 9 Вт | ||||

| Размеры | 8.3 дюйма (Ш) x 4,6 дюйма (Г) x 1,66 дюйма (В) 211 мм (Ш) x 117 мм (Г) x 42 мм (В) | ||||

| Передняя панель | Два входных разъема SMA Четыре выходных разъема SMA Выключатель питания с зеленым светодиодным индикатором включения 5-значный светодиодный индикатор соотношения деления 3 кнопки управления | ||||

| Задняя панель | Вход +12 В постоянного тока, (ответный штекер: внешний диаметр 5,5 мм, диаметр центрального контакта 2 мм) Разъем USB типа C | ||||

| Операционная среда | |||||

| Диапазон температур | от 0 до 50 ° C (от 32 до 122 ° F) | ||||

| Относительная влажность | от 10 до 90% без конденсации | ||||

| Положения | Разработан в соответствии с UL 60950, FCC Class B, CE безопасности и выбросов | ||||

[1] Технические характеристики могут быть изменены без предварительного уведомления

[2] Не все коэффициенты делителя можно установить: если коэффициент делится на простое число> 256, такое соотношение делителя недостижимо

[3] Фазовый шум увеличивается для входных сигналов с низкой скоростью нарастания.Для низкочастотных операций рекомендуется использовать входной сигнал с быстрым нарастанием / спадом (≥ 4 В / нс).

[4] Ограничено источником сигнала

Типичный фазовый шумВходной сигнал 13,3 ГГц, коэффициенты деления ÷ 1, ÷ 4 и ÷ 14

| Сдвиг частоты, Гц | Фазовый шум, дБн / Гц | ||

| ÷ 1 | ÷ 4 | ÷ 14 | |

| 10 Гц | -60 | -69 | -79 |

| 100 Гц | -86 | -96 | -108 |

| 1 кГц | -110 | -123 | -132 |

| 10 кГц | -112 | -124 | -134 |

| 100 кГц | -116 | -128 | -138 |

| 1 МГц | -138 | -145 | –150 |

| 10 МГц | -142 | -146 | –150 |

Рисунок 1

Типовой SFDR| Входной сигнал 14 ГГц, дел.отношение ÷ 2 | Входной сигнал 18 ГГц, дел. отношение ÷ 2 |

| Рисунок 2 | Рисунок 3 |

Делитель – обзор | Темы ScienceDirect

Делитель напряжения

Распространенный делитель напряжения (рис. 12.19) имеет выходное напряжение, которое составляет часть напряжения в

рис. 12.19. Делитель напряжения.

(12,46) I = VinR1 + R2

Выходное напряжение – это напряжение на R2, поэтому

(12.47) Vout = IR2 = (R2 · VinR1 + R2) = R2R1 + R2Vin

Мы можем создать эквивалент этой схемы по Тевенину, как показано на рис. 12.20.

Рис. 12.20. Делитель напряжения, эквивалентный Тевенину.

Мы знаем, что эквивалентное напряжение Тевенина равно

(12,48) VTH = напряжение холостого хода = VinR2R1 + R2

Кроме того, мы знаем, что эквивалентное сопротивление по Тевенину RTH равно

(12,49) RTH = VTHкороткое замыкание R2 · R1VIN = R1R2R1 + R2

Если мы добавим нагрузку на выход этой эквивалентной схемы, мы найдем

(12.50) Vout = VTHRLRTH + RL

Сопротивление нагрузки вызывает падение выходного сигнала делителя напряжения. Это важный фактор при проектировании измерительного оборудования. Мы должны убедиться, что сопротивление нагрузки очень велико по сравнению с сопротивлением источника RL≫Rsource. Равным образом сопротивление источника должно быть как можно меньшим; есть только несколько исключений, например, если сигнал является током, и в этом случае нам нужен небольшой входной импеданс.

Простой усилитель сигнала, построенный с использованием операционного усилителя

Поскольку неинвертирующий вход заземлен, а выход действует для выравнивания разницы между входами, инвертирующий вход также находится на земле (известной как виртуальная земля), как показано на Инжир.12.21. Как уже упоминалось, входы не потребляют ток, поэтому ток, протекающий через R1 и R2, одинаков. Следовательно,

Рис. 12.21. Инвертирующий усилитель.

(12,51) I = VoutR2 = −VinR1⇒VoutVin = −R2R1≡voltagegain

Неинвертирующий усилитель показан на рис. 12.22.

Рис. 12.22. Неинвертирующий усилитель.

Инвертирующий вход имеет напряжение

(12,52) Vinv = VoutR1R1 + R2

(12,53) Vin = Vinv⇒Vin = VoutR1R1 + R2

(12,54) VinVout = R1R1 + R2⇒VoutVin = R1 + R2R1 = 1 + R2R1

– коэффициент усиления неинвертирующего усилителя.

Важно отметить, что входной импеданс этой цепи теоретически бесконечен, а на практике очень высок (1012 Ом).

Дифференциальный усилитель

Существует множество приложений, в которых важная информация в сигнале содержится в присутствии значительного шума с относительно высокой амплитудой. Мы можем представить себе электрический сигнал мышцы, усиливающей речь в шумной среде. Информацию можно извлечь, если улучшить отношение сигнал / шум. Это можно сделать, записав сигнал из двух пространственно разных точек и удалив сигнал, который является общим для обеих.Усилители, которые мы видели до сих пор, имеют только один вход, поэтому нам нужно что-то другое (рис. 12.23 и 12.24).

Рис. 12.23. Работа дифференциального усилителя. Шум общий для обоих электродов; биопотенциал присутствует преимущественно в единице.

Источник: Томас Стоун, Измерение двигательной системы, Серия лекций по биомедицине, Бирмингемский университет, 2009 г.Рис. 12.24. Сигнал с синфазным шумом.

Источник: Томас Стоун, Паттерны мышечной активности при ходьбе после инсульта, докторская диссертация, 2006 г., Борнмутский университет.Операционный усилитель, рассмотренный ранее, по сути, является дифференциальным усилителем; разница между двумя входами отражается изменением выхода. Однако из-за огромных синфазных коэффициентов усиления операционного усилителя очень небольшие различия в напряжении между входными клеммами приводят к огромным колебаниям на выходе, поэтому он не может быть практичным прибором. Решение показано на рис. 12.25.

Рис. 12.25. Дифференциальный усилитель.

В этой цепи

(12.55) Vout = (V1-V2) R2R1

К сожалению, это не идеальное решение, поскольку V2 «видит» входное сопротивление R1 + R2, а V1 видит только входное сопротивление R1. Этот дисбаланс импеданса означает, что если бы мы приложили напряжение к одному выводу и заземлили бы другой, а не в обратном порядке, разные токи протекали бы через V2 и V1, тогда как в идеале они были бы одинаковыми. Это влияет на общий коэффициент отклонения, поскольку подобные сигналы не будут появляться и не будут отклоняться.

Коэффициент подавления синфазного сигнала (CMRR) определяется как

(12.56) CMRR = Adiff (VcmVout)

То есть это отношение общего сигнала, присутствующего на обоих терминалах (Vcm), и выходного сигнала (Vout), умноженное на дифференциальное усиление (Adiff). Можно определить логарифмическое выражение CMRR, подавления синфазного сигнала (CMR); вы также можете увидеть это выраженное в виде логарифмического члена CMR = 20log10CMRR.

CMR в дБ может быть определен в терминах усиления усилителя и n допусков резистора, Kr или полного дробного рассогласования.

(12,57) CMR = 20log10 (1 + R2R1nKr)

Можно видеть, что если использовались типичные значения резисторов, где допуски были порядка 0.1%, CMR будет очень низким.

Следует также отметить, что входные сопротивления упомянутых ранее входов действительно довольно низкие. Если мы вспомним, что случилось с сетью делителя напряжения, когда RL≯Rsource, мы увидим, что нам нужно поддерживать высокий входной импеданс, чтобы не вызывать уменьшение выходного сигнала делителя, который является сигналом, который мы пытаемся измерить. Следует отметить, что если сигнал действует как источник тока, верно обратное, и нам нужен небольшой входной импеданс.

Несоответствие между входными токами можно преодолеть путем введения буферных усилителей с единичным усилением (усиление = 1) на входы схемы (рис. 12.26). По сути, это обеспечивает очень высокий входной импеданс в цепи дифференциального усилителя; Поскольку операционные усилители обычно имеют очень высокое входное сопротивление, в идеале они не потребляют ток через свои входы. Буфер просто обеспечивает обратную связь выхода с неинвертирующим входом, который следует за инвертирующим входом; как таковой, он просто буферизует ввод.

Рис. 12.26. Дифференциальный усилитель с буферизованными входами.

Коэффициент усиления этого дифференциального усилителя устанавливается аналогично инвертирующему усилителю, за исключением того, что напряжение на неинвертирующем входе не заземлено. Таким образом, коэффициент усиления равен отношению R1 к R2; однако, чтобы изменить коэффициент усиления, мы должны помнить, что схема должна оставаться сбалансированной, и небольшие изменения в парах резисторов будут приводить к разному усилению на входах. Как мы решаем эти проблемы? Инструментальный усилитель – одно из решений.

Интернет-магазин делителей | Future Electronics

Дополнительная информация о делителях …

Что такое делитель?Делитель частоты – это схема, которая принимает входной сигнал частотного ребра и генерирует выходной сигнал с частотой fout, где fout = fin / n и «n» является целым числом. Делители частоты используются как для аналоговых, так и для цифровых приложений. Аналоговые делители частоты используются только на очень высоких частотах. Цифровые делители могут работать на частотах до десятков ГГц.

Типы разделителейСуществует много разных типов разделителей. В Future Electronics имеется множество наиболее распространенных типов, которые классифицируются по току питания, напряжению питания, частотному диапазону, типу корпуса и входной мощности. Параметрические фильтры на нашем веб-сайте могут помочь уточнить результаты поиска в зависимости от требуемых характеристик.

Наиболее распространенные значения тока питания – 4,5 мА, 5,3 мА и 30 мА. Также в наличии делители с током питания до 37 мА.Частота может варьироваться от 100 МГц до 5 ГГц, при этом наиболее распространенные размеры составляют 1 ГГц, 1,1 ГГц и 3 ГГц.

Делители от Future ElectronicsFuture Electronics предлагает полный набор программируемых дробных делителей от нескольких производителей, которые могут использоваться для таких схем, как ВЧ делитель частоты, схема цифрового делителя частоты, аналоговый делитель частоты, делитель частоты на 3 или любой чип делителя частоты. Просто выберите один из технических атрибутов разделителя ниже, и результаты поиска будут быстро сужены в соответствии с потребностями вашего конкретного применения разделителя.

Если у вас есть предпочтительный бренд, мы работаем с несколькими производителями, такими как California Eastern Lab, Micrel Semiconductor, Hittite Microwave, Murata или ON Semiconductor. Вы можете легко уточнить результаты поиска разделителей, щелкнув нужную марку разделителей ниже в нашем списке производителей.

Приложения для делителей:Делители частоты могут быть реализованы как для аналоговых, так и для цифровых приложений. Их можно использовать для улучшения характеристик оборудования для радиоэлектронного противодействия, систем связи и лабораторных приборов.Делители и умножители частоты являются ключевыми компонентами современных ВЧ- и СВЧ-систем. Их основное применение – синтез частот.

Выбор правильного делителя:Когда вы ищете правильные делители, с помощью параметрического поиска FutureElectronics.com вы можете фильтровать результаты по различным атрибутам: по току питания (3 мкА, 4,5 мА, 5,3 мА, 30 мА,…), напряжение питания (от 2,2 В до 5,7 В) и диапазон частот (от 100 МГц до 5 ГГц) и многие другие. Вы сможете найти подходящий чип для своей схемы или ВЧ делителя частоты, цифрового делителя частоты, аналогового делителя частоты, делителя частоты на 3 или любых схем делителя частоты.

Разделители в упаковке, готовой к производству или в количестве для НИОКРЕсли количество необходимых разделителей меньше целой катушки, мы предлагаем покупателям многие из наших программируемых разделителей в тюбиках, лотках или отдельных количествах, которые помогут вам избежать ненужный излишек.

Кроме того, Future Electronics предлагает клиентам уникальную программу таможенных складских запасов, которая предназначена для устранения потенциальных проблем, которые могут возникнуть из-за непредсказуемых поставок продуктов, содержащих необработанные металлы, и продуктов с длительным или нестабильным сроком поставки.Поговорите с ближайшим отделением Future Electronics и узнайте больше о том, как вы и ваша компания можете избежать возможного дефицита.

Делители частоты, предделители и счетчики

Некоторые файлы cookie необходимы для безопасного входа в систему, но другие необязательны для функциональной деятельности. Сбор наших данных используется для улучшения наших продуктов и услуг. Мы рекомендуем вам принять наши файлы cookie, чтобы обеспечить максимальную производительность и функциональность нашего сайта. Для получения дополнительной информации вы можете просмотреть сведения о файлах cookie.Узнайте больше о нашей политике конфиденциальности.

Принять и продолжить Принять и продолжитьФайлы cookie, которые мы используем, можно разделить на следующие категории:

- Строго необходимые файлы cookie:

- Это файлы cookie, которые необходимы для работы analog.com или определенных предлагаемых функций. Они либо служат единственной цели передачи данных по сети, либо строго необходимы для предоставления онлайн-услуг, явно запрошенных вами.

- Аналитические / рабочие файлы cookie:

- Эти файлы cookie позволяют нам выполнять веб-аналитику или другие формы измерения аудитории, такие как распознавание и подсчет количества посетителей и наблюдение за тем, как посетители перемещаются по нашему веб-сайту.Это помогает нам улучшить работу веб-сайта, например, за счет того, что пользователи легко находят то, что ищут.

- Функциональные файлы cookie:

- Эти файлы cookie используются для распознавания вас, когда вы возвращаетесь на наш веб-сайт. Это позволяет нам персонализировать наш контент для вас, приветствовать вас по имени и запоминать ваши предпочтения (например, ваш выбор языка или региона). Потеря информации в этих файлах cookie может сделать наши службы менее функциональными, но не помешает работе веб-сайта.

- Целевые / профилирующие файлы cookie:

- Эти файлы cookie записывают ваше посещение нашего веб-сайта и / или использование вами услуг, страницы, которые вы посетили, и ссылки, по которым вы переходили. Мы будем использовать эту информацию, чтобы сделать веб-сайт и отображаемую на нем рекламу более соответствующими вашим интересам. Мы также можем передавать эту информацию третьим лицам с этой целью.